Результат интеллектуальной деятельности: СХЕМА УПРАВЛЕНИЯ ЗАЩЕЛКИ НА ЭЛЕМЕНТАХ И-НЕ И СДВИГОВЫЙ РЕГИСТР ЗАЩЕЛКИ НА ЭЛЕМЕНТАХ И-НЕ

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ

[0001] Изобретение относится к области технологии жидкокристаллических дисплеев, и в частности, к схеме управления защелки на элементах И-НЕ и сдвиговому регистру защелки на элементах И-НЕ.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Технология схемы GOA (управление затвора на матрице) использует процесс подложек с активной матрицей обычного устройства жидкокристаллического дисплея для того, чтобы изготовить схему управления сканированием затвора на матричной подложке и тем самым достигнуть непрерывного режима управления сканированием. Схема GOA имеет преимущества в виде сниженной цены производства и конструкции с узкой рамкой, и поэтому используется для ряда устройств дисплея. Схеме GOA требуется иметь две основные функции: первая заключается в том, чтобы вводить управляющие сигналы затвора для управления затворными шинами в панели и тем самым включать множество TFT (тонкопленочных транзисторов) в области отображения, для того чтобы позволить шинам сканирования заряжать пиксели; и вторая является функцией сдвига регистра, так что когда вывод управляющего импульса n-ого затвора завершается, она вслед за этим выполняет вывод управляющего импульса (n+1)-го затвора при помощи управляющего тактового сигнала; и т.д.

[0003] Схема GOA включает в себя повышающую схему, схему управления повышением, понижающую схему, схему управления понижением и схему усиления для поднятия потенциала. В частности, повышающая схема в основном отвечает за вывод сигнала таймера, введенного в затвор тонкопленочного транзистора, в качестве управляющего сигнала устройства жидкокристаллического дисплея. Схема управления повышением отвечает за управление повышающей схемой таким образом, чтобы она включалась, и, как правило, подчиняется управлению сигналом, переданным от схемы GOA предшествующего уровня. Понижающая схема отвечает за быстрое понижение сигнала сканирования до низкого уровня напряжения после вывода сигнала сканирования, т.е. понижение потенциала затвора тонкопленочного транзистора до низкого уровня напряжения. Схема управления понижением отвечает за поддержание сигнала сканирования и сигнала повышающей схемы (как правило, называемого сигналом узла Q) в выключенном состоянии (т.е., предварительно устанавливает отрицательный потенциал) и, как правило, имеет две схемы поддержания понижения, которые работают поочередно. Схема усиления отвечает за поднятие потенциала на узле Q в очередной раз, для того чтобы гарантировать нормальный вывод G(N) повышающей схемы.

[0004] Различные схемы GOA могут использовать различные процессы производства. Процесс LTPS (низкотемпературный поликристаллический кремний) имеет преимущества в виде высокой мобильности электронов и проверенной технологии и, вследствие этого, в настоящее время широко используется небольшими и среднего размера устройствами дисплея. Процесс CMOS (комплементарная структура оксид металла - полупроводник) LTPS имеет преимущества в виде низких затрат энергии, высокой мобильности электронов и широкой устойчивости к помехам и т.д., и поэтому закономерно используется производителями панелей. Соответственно, имеется потребность разработки схемы GOA, соответствующей процессу CMOS LTPS.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] Соответственно, варианты осуществления изобретения обеспечивают схему управления защелки на элементах И-НЕ и сдвиговый регистр защелки на элементах И-НЕ, которые подходят для процесса CMOS и могут достигнуть низких затрат энергии и широкой устойчивости к помехам.

[0006] В частности, изобретение обеспечивает схему управления защелки на элементах И-НЕ, включающей в себя множество каскадно-соединенных схем сдвиговых регистров защелки на элементах И-НЕ. Каждая из схем сдвиговых регистров включает в себя схему управления передачей тактового сигнала и схему защелки на элементах И-НЕ. Схема управления передачей тактового сигнала выполнена с возможностью (т.е. сконструирована и приспособлена) запускаться при помощи первого тактового импульса тактового сигнала для передачи управляющего импульса предыдущего уровня схеме защелки на элементах И-НЕ, и затем управляющий импульс защелкивается схемой защелки на элементах И-НЕ, схема защелки на элементах И-НЕ дополнительно выполнена с возможностью запускаться при помощи последующего второго тактового импульса первого тактового сигнала для вывода управляющего импульса. Схема управления передачей тактового сигнала и схема защелки на элементах И-НЕ по отдельности запускаются передним фронтом сигнала. Схема защелки на элементах И-НЕ, по меньшей мере, включает в себя первый инвертор, первый элемент И-НЕ, второй элемент И-НЕ и третий элемент И-НЕ; вход первого инвертора электрически подключен к выходу схемы управления передачей тактового сигнала, первый вход первого элемента И-НЕ электрически подключен к выходу первого инвертора, второй вход первого элемента И-НЕ электрически подключен к выходу второго элемента И-НЕ, первый вход второго элемента И-НЕ электрически подключен ко входу первого инвертора, второй вход второго элемента И-НЕ электрически подключен к выходу первого элемента И-НЕ, выход второго элемента И-НЕ дополнительно электрически подключен к первому входу третьего элемента И-НЕ, и второй вход третьего элемента И-НЕ электрически подключен для приема тактового сигнала.

[0007] В варианте осуществления схема управления передачей тактового сигнала инвертирует фазу управляющего импульса в процессе передачи управляющего импульса.

[0008] В варианте осуществления схеме защелки на элементах И-НЕ дополнительно включает в себя схему многоступенчатого инвертора, электрически подключенную к выходу третьего элемента И-НЕ.

[0009] В варианте осуществления схема многоступенчатого инвертора включает в себя множество последовательно соединенных вторых инверторов.

[0010] В варианте осуществления количество множества вторых инверторов равно трем.

[0011] В варианте осуществления тактовые сигнала соседних схем сдвиговых регистров являются инвертированными по фазам относительно друг друга.

[0012] Изобретение дополнительно обеспечивает схему управления защелки на элементах И-НЕ, включающую в себя множество каскадно-соединенных схем сдвиговых регистров защелки на элементах И-НЕ. Каждая из схем сдвиговых регистров включает в себя схему управления передачей тактового сигнала и схему защелки на элементах И-НЕ. Схема управления передачей тактового сигнала выполнена с возможностью запускаться при помощи первого тактового импульса тактового сигнала для передачи управляющего импульса предыдущего уровня схеме защелки на элементах И-НЕ, и затем управляющий импульс защелкивается схемой защелки на элементах И-НЕ, схема защелки на элементах И-НЕ дополнительно выполнена с возможностью запускаться при помощи последующего второго тактового импульса первого тактового сигнала для вывода управляющего импульса.

[0013] В варианте осуществления схема управления передачей тактового сигнала и схема защелки на элементах И-НЕ по отдельности запускаются передним фронтом сигнала.

[0014] В варианте осуществления схема защелки на элементах И-НЕ, по меньшей мере, включает в себя первый инвертор, первый элемент И-НЕ, второй элемент И-НЕ и третий элемент И-НЕ; вход первого инвертора электрически подключен к выходу схемы управления передачей тактового сигнала, первый вход первого элемента И-НЕ электрически подключен к выходу первого инвертора, второй вход первого элемента И-НЕ электрически подключен к выходу второго элемента И-НЕ, первый вход второго элемента И-НЕ электрически подключен ко входу первого инвертора, второй вход второго элемента И-НЕ электрически подключен к выходу первого элемента И-НЕ, выход второго элемента И-НЕ дополнительно электрически подключен к первому входу третьего элемента И-НЕ, и второй вход третьего элемента И-НЕ электрически подключен для приема тактового сигнала.

[0015] В варианте осуществления схема управления передачей тактового сигнала выполнена с возможностью инвертирования фазы управляющего импульса в процессе передачи управляющего импульса.

[0016] В варианте осуществления схеме защелки на элементах И-НЕ дополнительно включает в себя схему многоступенчатого инвертора, электрически подключенную к выходу третьего элемента И-НЕ.

[0017] В варианте осуществления схема многоступенчатого инвертора включает в себя множество последовательно соединенных вторых инверторов.

[0018] В варианте осуществления количество множества вторых инверторов равно трем.

[0019] В варианте осуществления тактовые сигнала соседних схем сдвиговых регистров являются инвертированными по фазам относительно друг друга.

[0020] Изобретение также обеспечивает сдвиговый регистр защелки на элементах И-НЕ, включающий в себя схему управления передачей тактового сигнала и схему защелки на элементах И-НЕ. Схема защелки на элементах И-НЕ, по меньшей мере, включает в себя первый инвертор, первый элемент И-НЕ, второй элемент И-НЕ и третий элемент И-НЕ. Вход первого инвертора электрически подключен к выходу схемы управления передачей тактового сигнала, первый вход первого элемента И-НЕ электрически подключен к выходу первого инвертора, второй вход первого элемента И-НЕ электрически подключен к выходу второго элемента И-НЕ, первый вход второго элемента И-НЕ электрически подключен ко входу первого инвертора, второй вход второго элемента И-НЕ электрически подключен к выходу первого элемента И-НЕ, выход второго элемента И-НЕ дополнительно электрически подключен к первому входу третьего элемента И-НЕ.

[0021] В варианте осуществления схема защелки на элементах И-НЕ дополнительно включает в себя схему многоступенчатого инвертора, электрически подключенную к выходу третьего элемента И-НЕ.

[0022] При помощи вышеуказанных решений эффект, который может достигаться при помощи изобретения, заключается в том, что: схема управления защелки на элементах И-НЕ изобретения использует схему управления передачей тактового сигнала, запускаемую при помощи первого тактового импульса тактового сигнала для передачи управляющего импульса предыдущего уровня схеме защелки на элементах И-НЕ, и затем управляющий импульс защелкивается схемой защелки на элементах И-НЕ; дополнительно схема защелки на элементах И-НЕ запускается при помощи последующего второго тактового импульса первого тактового сигнала для вывода управляющего импульса. Соответственно, изобретение подходит для процесса CMOS и может достигнуть низких затрат энергии и широкой устойчивости к помехам.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0023] Для более ясного иллюстрирования технических решений различных вариантов осуществления настоящего изобретения, будут использоваться чертежи в описании вариантов осуществления, будет дано краткое описание ниже. Очевидным образом, чертежи в последующем описании представляют собой только некоторые варианты осуществления изобретения, средний специалист в данной области техники может получить другие чертежи, соответствующие этим проиллюстрированным чертежам, без творческих усилий.

На чертежах:

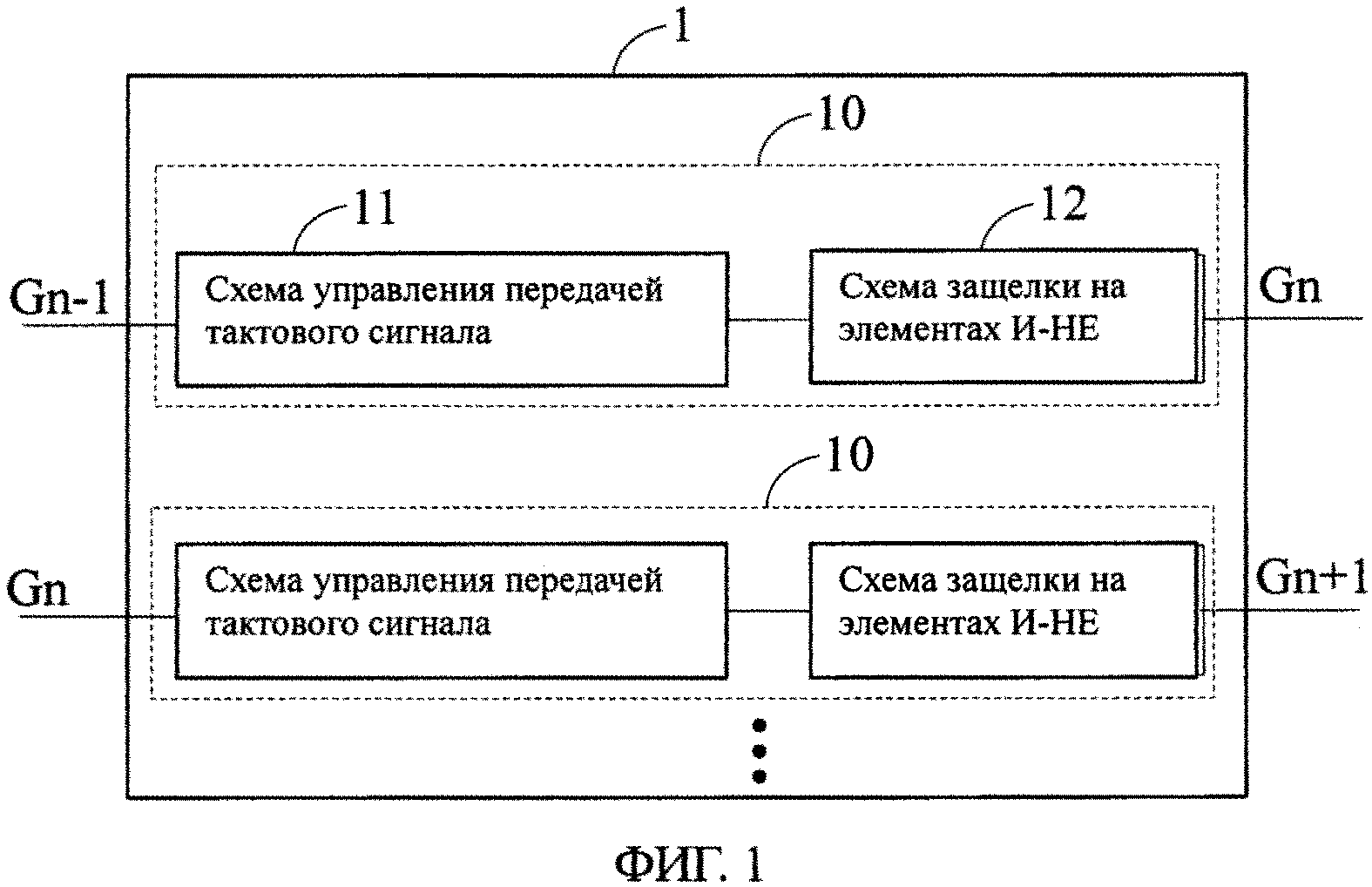

[0024] ФИГ. 1 представляет собой схематичный структурный вид схемы управления защелки на элементах И-НЕ варианта осуществления изобретения;

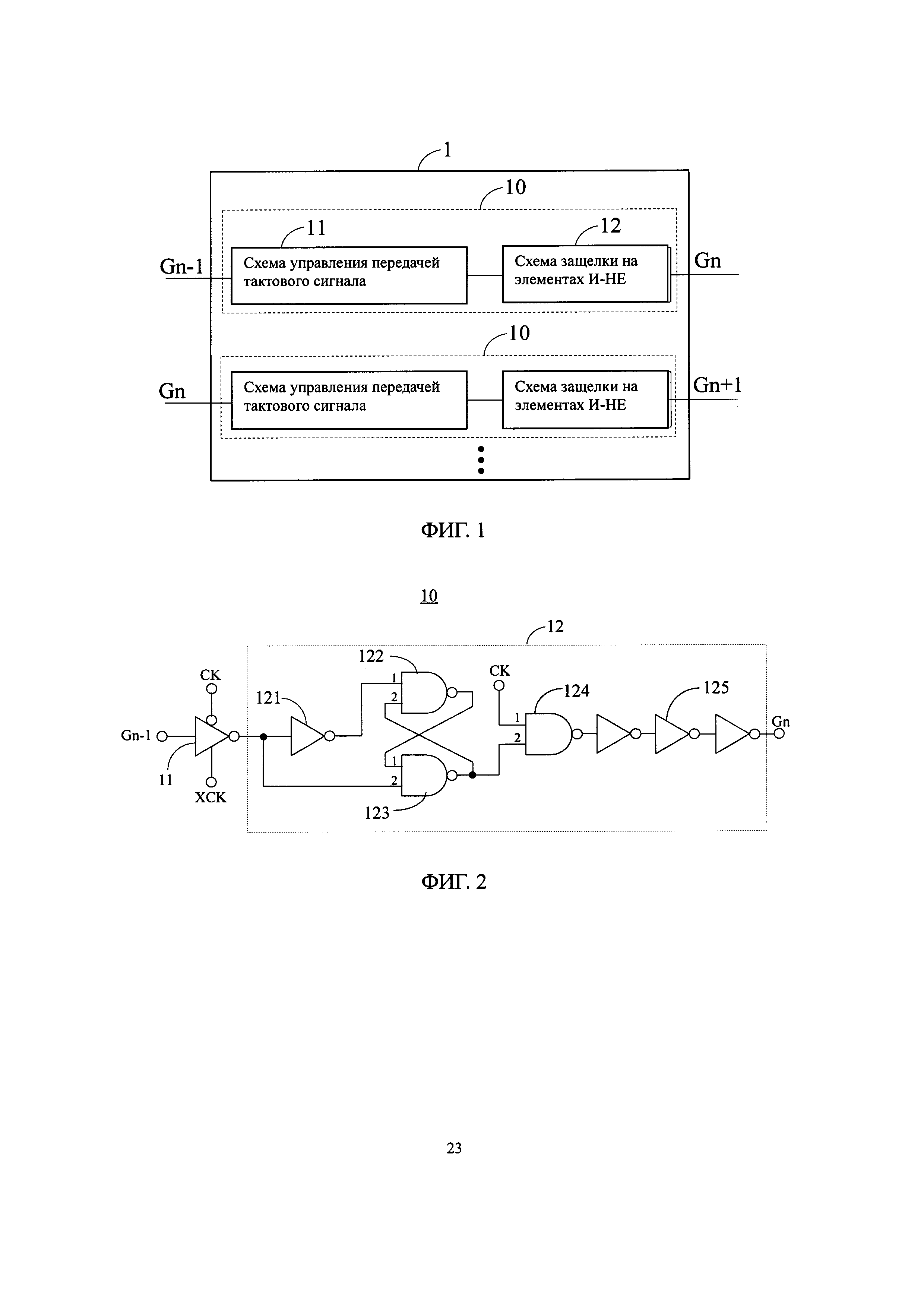

[0025] ФИГ. 2 представляет собой структурную схему сдвигового регистра, показанного на ФИГ. 1;

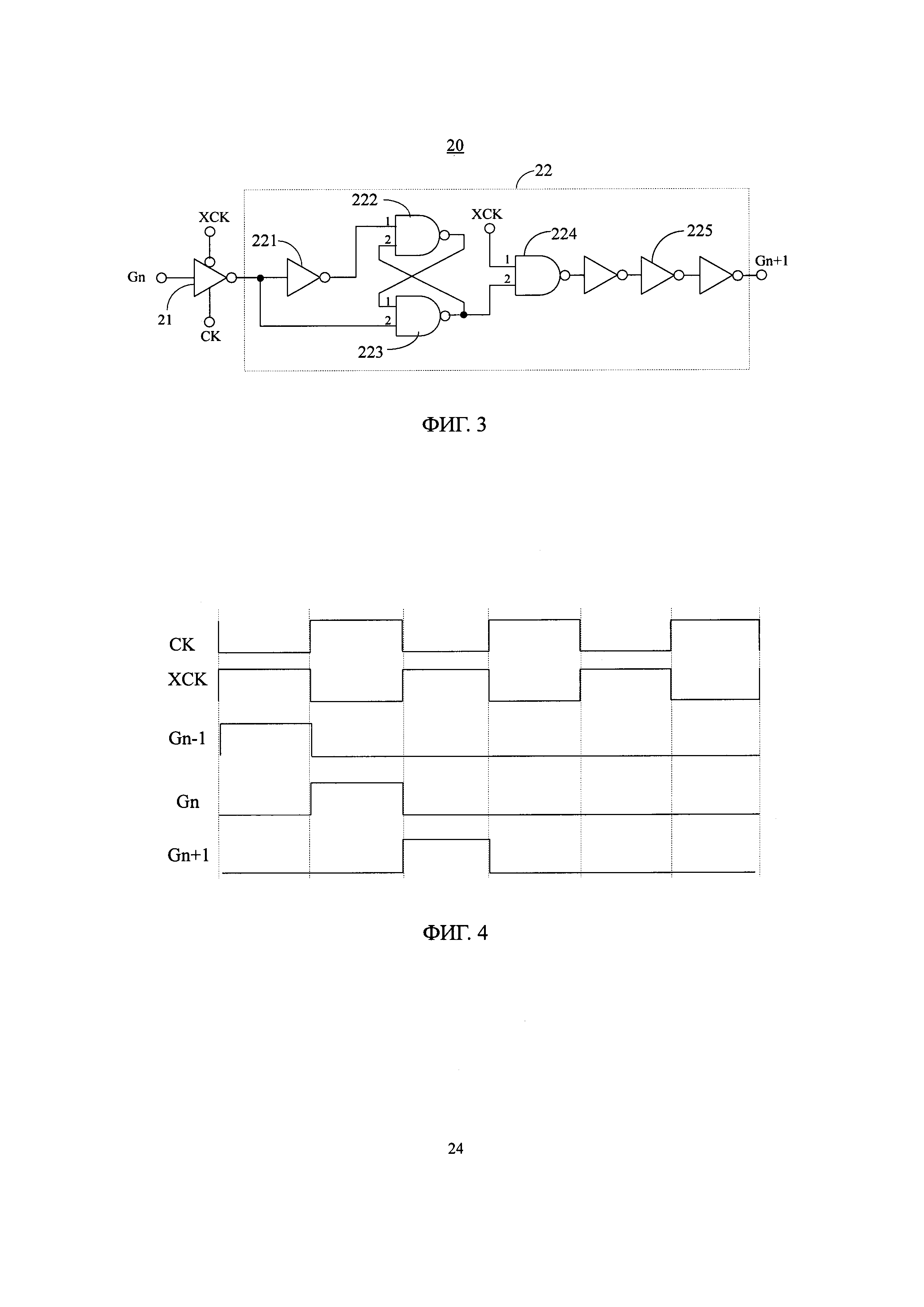

[0026] ФИГ. 3 представляет собой структурную схему сдвигового регистра второго варианта осуществления изобретения;

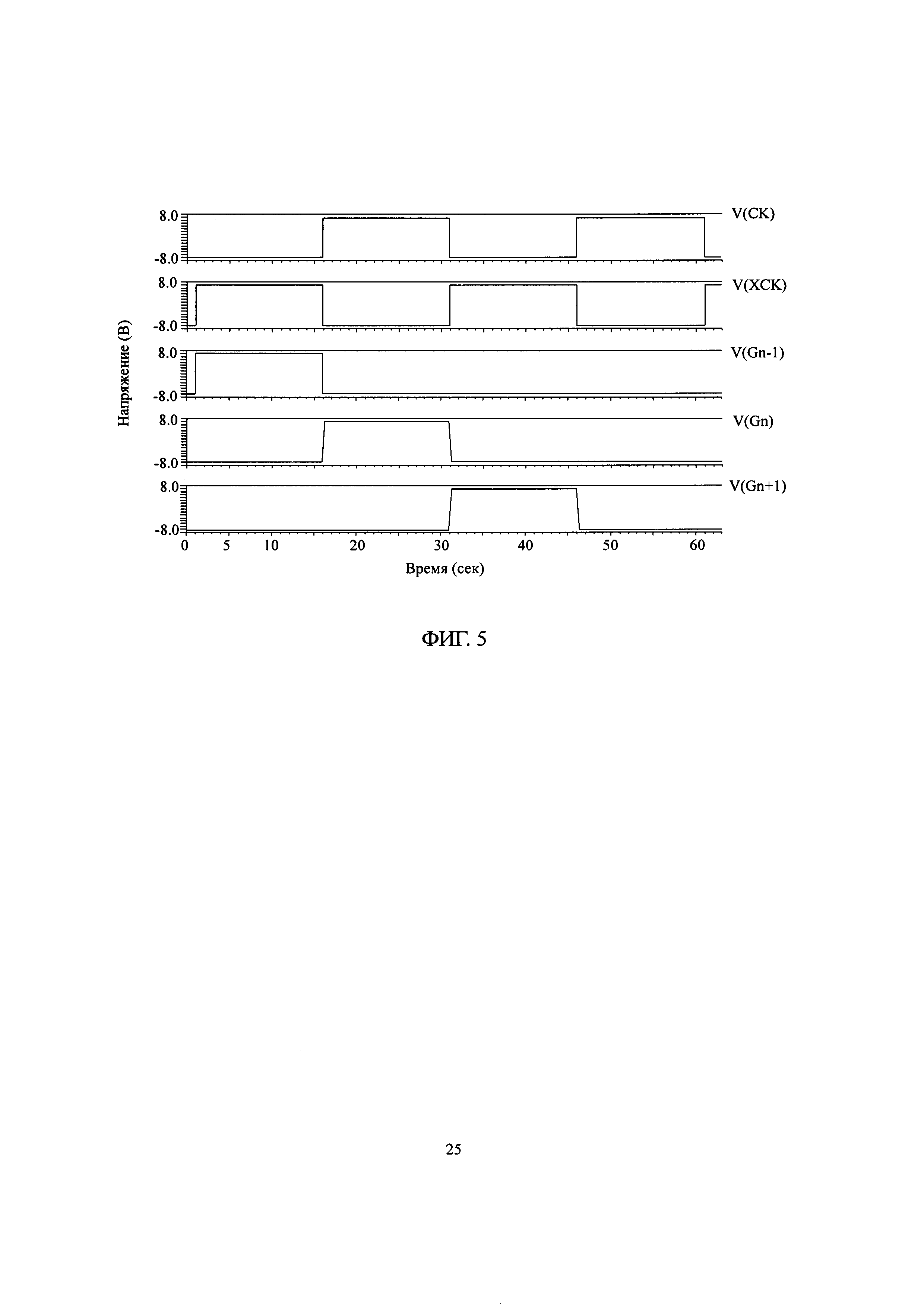

[0027] ФИГ. 4 представляет собой теоретическую временную диаграмму схемы управления защелки на элементах И-НЕ варианта осуществления изобретения; и

[0028] ФИГ. 5 представляет собой смоделированную временную диаграмму схемы управления защелки на элементах И-НЕ варианта осуществления изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0029] В последующем, со ссылкой на сопровождающие чертежи вариантов осуществления изобретения, технические решения в вариантах осуществления изобретения будут описаны ясно и полностью. Очевидным образом, варианты осуществления изобретения, описанные ниже, представляют собой только часть вариантов осуществления изобретения, но не все варианты осуществления. На основе описанных вариантов осуществления изобретения все другие варианты осуществления, полученные средним специалистом в данной области техники без творческих усилий, принадлежат объему защиты изобретения.

[0030] Ссылаемся на ФИГ. 1, которая представляет собой схематичный структурный вид схемы управления защелки на элементах И-НЕ варианта осуществления изобретения. Как показано на ФИГ. 1, управляющая схема 1, обеспеченная в этом варианте осуществления, включает в себя множество каскадно-соединенных схем 10 сдвиговых регистров защелки на элементах И-НЕ. Каждая из схем 10 сдвиговых регистров включает в себя схему 11 управления передачей тактового сигнала и схему 12 защелки на элементах И-НЕ, схема 11 управления передачей тактового сигнала запускается при помощи первого тактового импульса тактового сигнала для передачи управляющего импульса предыдущего уровня схеме 12 защелки на элементах И-НЕ, и затем управляющий импульс защелкивается схемой 12 защелки на элементах И-НЕ, и схема 12 защелки на элементах И-НЕ дополнительно запускается при помощи последующего второго тактового импульса тактового сигнала для вывода управляющего импульса. Схема 11 управления передачей тактового сигнала предназначена для инвертирования фазы управляющего импульса в ходе выполнения передачи управляющего импульса. Схема 11 управления передачей тактового сигнала и схема 12 защелки на элементах И-НЕ по отдельности запускаются передним фронтом сигнала. Этот вариант осуществления изобретения использует схему 11 управления передачей тактового сигнала для управления передачей сигнала между предыдущим и последующим уровнями и использует схему 12 защелки на элементах И-НЕ для защелкивания сигнала, и поэтому он подходит для процесса CMOS и может достигнуть низких затрат энергии и широкой устойчивости к помехам.

[0031] В более конкретном варианте осуществления, как показано на ФИГ. 2, схема 12 защелки на элементах И-НЕ, по меньшей мере, включает в себя первый инвертор 121, первый элемент И-НЕ 122, второй элемент И-НЕ 123 и третий элемент И-НЕ 124. Вход первого инвертора 121 электрически подключен к выходу схемы 11 управления передачей тактового сигнала, первый вход первого элемента И-НЕ 122 электрически подключен к выходу первого инвертора 123, второй вход первого элемента И-НЕ 122 электрически подключен к выходу второго элемента И-НЕ 123, первый вход второго элемента И-НЕ 123 электрически подключен ко входу первого инвертора 122, второй вход второго элемента И-НЕ 123 электрически подключен к выходу первого элемента И-НЕ 122, выход второго элемента И-НЕ 123 дополнительно электрически подключен к первому входу третьего элемента И-НЕ 124, второй вход третьего элемента И-НЕ 124 электрически подключен для приема тактового сигнала СК. Схема 12 защелки на элементах И-НЕ дополнительно включает в себя схему многоступенчатого инвертора, электрически подключенную к выходу элемента И-НЕ 124, для того чтобы расширить управляющую возможность управляющей схемы 1. Схема многоступенчатого инвертора включает в себя множество последовательно соединенных вторых инверторов 125. Преимущественно, количество вторых инверторов 125 равно трем.

[0032] Конкретный принцип работы схемы 10 сдвигового регистра заключается в следующем: когда первый тактовый импульс тактового сигнала СК находится на переднем фронте, схема 11 управления передачей тактового сигнала запускается для передачи управляющего импульса Gn-1 предыдущего уровня первому инвертеру 121. В процессе передачи управляющий импульс Gn-1 инвертируется по фазе. После этого управляющий импульс Gn-1 предыдущего уровня передается первому элементу И-НЕ 122 и второму элементу И-НЕ 123 через первый инвертор 121 и защелкивается перекрестно-подключенными первым элементом И-НЕ 122 и вторым элементом И-НЕ 123. Когда второй тактовый импульс тактового сигнала СК находится на переднем фронте, т.е. следующий тактовый импульс тактового сигнала СК находится на переднем фронте, запускается схема 12 защелки на элементах И-НЕ, управляющий импульс Gn-1 предыдущего уровня, запертый перекрестно-подключенными первым элементом И-НЕ 122 и вторым элементом И-НЕ 123, передается второму инвертеру 124 и затем передается затвору Gn последующего уровня. Схема 11 управления передачей тактового сигнала дополнительно включает в себя тактовый сигнал ХСК, причем тактовый сигнал ХСК и тактовый сигнал СК имеют инвертированные фазы.

[0033] В этом варианте осуществления изобретения тактовые сигналы соседних схем сдвиговых регистров являются взаимно-инвертированными по фазе. Со ссылкой на ФИГ. 3, схема 20 сдвигового регистра включает в себя схему 21 управления передачей тактового сигнала и схему 22 защелки на элементах И-НЕ. Схема 22 защелки на элементах И-НЕ, по меньшей мере, включает в себя первый инвертор 221, первый элемент И-НЕ 222, второй элемент И-НЕ 223 и третий элемент И-НЕ 224. Вход первого инвертора 221 электрически подключен к выходу схемы 21 управления передачей тактового сигнала, первый вход первого элемента И-НЕ 222 электрически подключен к выходу первого инвертора 221, второй вход первого элемента И-НЕ 222 электрически подключен к выходу второго элемента И-НЕ 223, первый вход второго элемента И-НЕ 223 электрически подключен ко входу первого инвертора 221, второй вход второго элемента И-НЕ 223 электрически подключен к выходу первого элемента И-НЕ 222, выход второго элемента И-НЕ 223 дополнительно электрически подключен к первому входу третьего элемента И-НЕ 224, второй вход третьего элемента И-НЕ 224 электрически подключен для приема тактового сигнала ХСК. Схема 22 защелки на элементах И-НЕ дополнительно включает в себя схему многоступенчатого инвертора, электрически подключенную к выходу третьего элемента И-НЕ 224, для того чтобы расширить управляющую возможность управляющей схемы 1. Схема многоступенчатого инвертора включает в себя множество последовательно соединенных вторых инверторов 225. Преимущественно, количество вторых инверторов 225 равно трем.

[0034] Конкретный принцип работы схемы 20 сдвигового регистра заключается в следующем: когда первый тактовый импульс тактового сигнала ХСК находится на переднем фронте, схема 21 управления передачей тактового сигнала запускается для передачи управляющего импульса Gn последующего уровня первому инвертеру 221. В процессе передачи управляющий импульс Gn последующего уровня инвертируется по фазе. После этого управляющий импульс Gn последующего уровня передается первому элементу И-НЕ 222 и второму элементу И-НЕ 223 через первый инвертор 221 и защелкивается перекрестно-подключенными первым элементом И-НЕ 222 и вторым элементом И-НЕ 223. Когда второй тактовый импульс тактового сигнала ХСК находится на переднем фронте, т.е. следующий тактовый импульс тактового сигнала ХСК находится на переднем фронте, запускается схема 22 защелки на элементах И-НЕ, управляющий импульс Gn последующего уровня, запертый перекрестно-подключенными первым элементом И-НЕ 222 и вторым элементом И-НЕ 223, передается второму инвертеру 224 и затем выдается в качестве управляющего импульса Gn+1 третьего уровня. Схема 21 управления передачей тактового сигнала дополнительно включает в себя тактовый сигнал СК, причем тактовый сигнал СК и тактовый сигнал ХСК имеют инвертированные фазы.

[0035] В этом варианте осуществления изобретения схема 10 сдвигового регистра и схема 20 сдвигового регистра находятся по соседству друг с другом. В реальном приложении, множество каскадно-соединенных схем сдвиговых регистров защелки на элементах И-НЕ в схеме 1 управления защелки на элементах И-НЕ могут разделяться на нечетные уровни и четные уровни, схема 10 сдвигового регистра может использоваться в качестве сдвигового регистра нечетного уровня, и схема 20 сдвигового регистра может использоваться в качестве сдвигового регистра четного уровня. Также может быть так, что вместо этого схема 20 сдвигового регистра используется в качестве сдвигового регистра нечетного уровня, и схема 10 сдвигового регистра используется в качестве сдвигового регистра четного уровня. Ссылаемся на ФИГ. 4, которая представляет собой теоретическую временную диаграмму схемы управления защелки на элементах И-НЕ варианта осуществления изобретения. Здесь схема 10 сдвигового регистра используется в качестве сдвигового регистра нечетного уровня, и схема 20 сдвигового регистра используется в качестве сдвигового регистра четного уровня. Как можно видеть на чертеже, тактовый сигнал СК и тактовый сигнал ХСК являются инвертированными по фазе. Когда тактовый сигнал СК находится на переднем фронте, управляющий импульс Gn-1 предыдущего уровня передается затвору последующего уровня, т.е. управляющий импульс Gn-1 предыдущего уровня меняется с высокого уровня напряжения на низкий уровень напряжения, и управляющий импульс Gn последующего уровня меняется с низкого уровня напряжения на высокий уровень напряжения, для управления соответствующим затвором. Когда тактовый сигнал ХСК находится на переднем фронте, управляющий импульс Gn последующего уровня передается затвору третьего уровня, т.е. управляющий импульс Gn последующего уровня меняется с высокого уровня напряжения на низкий уровень напряжения, и управляющий импульс Gn+1 третьего уровня меняется с низкого уровня напряжения на высокий уровень напряжения, для управления соответствующим затвором. ФИГ. 5 представляет собой смоделированную временную диаграмму управляющей схемы варианта осуществления изобретения. Со ссылкой на ФИГ. 5, координата по вертикали представляет собой напряжение, и координата по горизонтали представляет собой время. Как видно на чертеже, смоделированная временная диаграмма схемы управления защелки на элементах И-НЕ является такой же как и теоретическая временная диаграмма на ФИГ. 4.

[0036] Изобретение также обеспечивает сдвиговый регистр защелки на элементах И-НЕ. Конкретно, со ссылкой на ФИГ. 2, схема 10 сдвигового регистра защелки на элементах И-НЕ включает в себя схему 11 управления передачей тактового сигнала и схему 12 защелки на элементах И-НЕ. Схема 12 защелки на элементах И-НЕ, по меньшей мере, включает в себя первый инвертор 121, первый элемент И-НЕ 122, второй элемент И-НЕ 123 и третий элемент И-НЕ 124. Вход первого инвертора 121 электрически подключен к выходу схемы 11 управления передачей тактового сигнала, первый вход первого элемента И-НЕ 122 электрически подключен к выходу первого инвертора 123, второй вход первого элемента И-НЕ 122 электрически подключен к выходу второго элемента И-НЕ 123, первый вход второго элемента И-НЕ 123 электрически подключен ко входу первого инвертора 122, второй вход второго элемента И-НЕ 123 электрически подключен к выходу первого элемента И-НЕ 122, выход второго элемента И-НЕ 123 дополнительно электрически подключен к первому входу третьего элемента И-НЕ 124, второй вход третьего элемента И-НЕ 124 электрически подключен для приема тактового сигнала СК. Схема 12 защелки на элементах И-НЕ дополнительно включает в себя схему многоступенчатого инвертора, электрически подключенную к выходу третьего элемента И-НЕ 124, для того чтобы расширить управляющую возможность. Схема многоступенчатого инвертора включает в себя множество последовательно соединенных вторых инверторов 125. Преимущественно, количество вторых инверторов 125 равно трем.

[0037] Конкретный принцип работы схемы 10 сдвигового регистра заключается в следующем: когда первый тактовый импульс тактового сигнала СК находится на переднем фронте, схема 11 управления передачей тактового сигнала запускается для передачи управляющего импульса Gn-1 предыдущего уровня первому инвертеру 121. В процессе передачи управляющий импульс Gn-1 инвертируется по фазе. После этого управляющий импульс Gn-1 предыдущего уровня передается первому элементу И-НЕ 122 и второму элементу И-НЕ 123 через первый инвертор 121 и защелкивается перекрестно-подключенными первым элементом И-НЕ 122 и вторым элементом И-НЕ 123. Когда второй тактовый импульс тактового сигнала СК находится на переднем фронте, т.е. следующий тактовый импульс тактового сигнала СК находится на переднем фронте, запускается схема 12 защелки на элементах И-НЕ для передачи управляющего импульса Gn-1 предыдущего уровня, запертого перекрестно-подключенными первым элементом И-НЕ 122 и вторым элементом И-НЕ 123, второму инвертору 125 и затем передается затвору Gn последующего уровня через второй инвертор 125. Схема 11 управления передачей тактового сигнала дополнительно включает в себя тактовый сигнал ХСК, причем тактовый сигнал ХСК и тактовый сигнал СК имеют инвертированные фазы. В этом варианте осуществления изобретения могут использоваться множество сдвиговых регистров 10 для каскадного подключения друг с другом для формирования схемы управления защелки на элементах И-НЕ, используется схема 11 управления передачей тактового сигнала для управления передачей сигнала между предыдущим и последующим уровнями, и используется схема 12 защелки на элементах И-НЕ для защелкивания сигнала, и вследствие этого, он подходит для процесса CMOS и может достигнуть низких затрат энергии и широкой устойчивости к помехам.

[0038] Следует отметить, что управляющие импульсы, раскрытые изобретением, преимущественно представляют собой управляющие импульсы затвора.

[0039] Суммируя вышесказанное, схема управления защелки на элементах И-НЕ изобретения использует схему управления передачей тактового сигнала, запускаемую первым тактовым импульсом тактового сигнала для передачи управляющего сигнала предыдущего уровня схеме защелки на элементах И-НЕ, и управляющий импульс затем защелкивается схемой защелки на элементах И-НЕ; схема защелки на элементах И-НЕ дополнительно запускается последующим вторым тактовым импульсом тактового сигнала для вывода управляющего импульса. Соответственно, она подходит для процесса CMOS и может достигнуть низких затрат энергии и широкой устойчивости к помехам.

[0040] Принимая во внимание то, что изобретение описывалось применительно к тому, что в настоящее время считается наиболее практичными и предпочтительными вариантами осуществления, следует понимать, что изобретение не следует ограничивать раскрытыми вариантами осуществления. Напротив, предполагается, что оно охватывает различные модификации и аналогичные приспособления, входящие в состав сущности и объема прилагаемой формулы изобретения, которая должна отвечать требованиям широчайшей интерпретации, для того чтобы сосредоточить в себе все подобные модификации и аналогичные конструкции.