Результат интеллектуальной деятельности: СХЕМА УПРАВЛЕНИЯ ЗАТВОРОМ И РЕГИСТР СДВИГА

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к области технологии отображения и, в частности, к схеме управления затвором и регистру сдвига.

ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

[0002] Схема GOA (привода затвора на матрице) предназначена для создания схемы привода сканирования затвора на матричной подложке с использованием имеющегося в настоящее время процесса жидкокристаллической матрицы отображения для достижения способа управления сканированием строка за строкой. Он обладает достоинствами снижения себестоимости продукции и узкой конструкцией рамы и используется многими видами дисплеев. Схема GOA имеет две основные функции: одна - ввод импульса управления затвором для управления затворной шиной в панели и активация TFT (тонкопленочного транзистора) в области отображения для зарядки пикселя через затворную шину; вторая - для регистра сдвига, а так как вывод n-го импульса управления затвором выполнен, может быть выполнен вывод n+1-го импульса управления затвором с управлением тактовой синхронизацией и так далее.

[0003] Схема GOA содержит схему повышения, схему управления повышением, схему понижения, управление понижением и схему усиления, отвечающую за уровень дополнительного напряжения. В частности, схема повышения, в основном, отвечает за вывод входного тактового сигнала на затвор тонкопленочного транзистора в качестве управляющих сигналов жидкокристаллического дисплея. Схема управления повышением отвечает за активизацию схемы повышения и обычно функционирует посредством сигнала, переданного из схемы GOA на предыдущем этапе. Схема понижения отвечает за быстрое понижение сигнала сканирования на уровень низкого напряжения после вывода сигнала сканирования. То есть, уровень напряжения затвора тонкопленочного транзистора понижается до уровня низкого напряжения; схема удержания понижения отвечает за сохранение сигнала сканирования и сигнала схемы понижения (точка Q в общем) в выключенном состоянии (т.е. заданный отрицательный уровень напряжения) и, как правило, функционируют две схемы удержания понижения, поочередно. Схема усиления отвечает за второе усиление уровня напряжения точки Q для обеспечения нормального выхода G(N) схемы повышения.

[0004] Различные схемы GOA могут использовать различные процессы. Низкотемпературный поликремниевый (LTPS) процесс обладает преимуществами более высокой подвижности электронов и взаимной технологией, которая широко используется в небольших и средних дисплеях. Процесс LTPS CMOS (комплементарный металло-оксидный полупроводник) обладает преимуществами низкого потребления энергии, более высокой подвижности электронов и широким допускаемым диапазоном шума и, таким образом, постепенно используется производителями панелей. Поэтому необходимо разработать схему GOA, соответствующую процессу CMOS LTPS.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

[0005] Вариант осуществления настоящего изобретения предусматривает схему управления затвором и регистр сдвига, применимый к CMOS-процессу, и потребляемая мощность низкая, а допускаемый диапазон уровней шумов широкий.

[0006] Настоящее изобретение предусматривает схему управления затвором, содержащую множество схем регистра сдвига, которые соединены каскадом, и каждая из схем регистра сдвига содержит схему передачи команды управления тактовой синхронизацией и схему защелки на элементах ИЛИ-НЕ, причем схема передачи команды управления тактовой синхронизацией запускается первым тактовым импульсом тактового сигнала для передачи импульса управления затвором предыдущего этапа в схему защелки на элементах ИЛИ-НЕ, и схема защелки на элементах ИЛИ-НЕ выполняет функцию защелки, и схема защелки на элементах ИЛИ-НЕ дополнительно запускается вторым тактовым импульсом после первого тактового импульса для вывода импульса управления затвором; причем схема передачи команды управления тактовой синхронизацией и схема защелки на элементах ИЛИ-НЕ соответственно являются управляемыми по переднему фронту тактового импульса; схема защелки на элементах ИЛИ-НЕ, по меньшей мере, содержит первый инвертор, первый затвор ИЛИ-НЕ, второй затвор ИЛИ-НЕ и затвор И-НЕ, причем входной конец первого инвертора соединен с выходным концом схемы передачи команды управления тактовой синхронизацией, и первый входной конец первого затвора ИЛИ-НЕ соединен с выходным концом первого инвертора, а второй входной конец первого затвора ИЛИ-НЕ соединен с выходным концом второго затвора ИЛИ-НЕ, и первый входной конец второго затвора ИЛИ-НЕ соединен с входным концом первого инвертора, а второй входной конец второго затвора ИЛИ-НЕ соединен с выходным концом первого затвора ИЛИ-НЕ, а выходной конец второго затвора ИЛИ-НЕ дополнительно соединен с первый входным концом затвора И-НЕ, а второй входной конец затвора И-НЕ принимает тактовый сигнал.

[0007] Схема передачи команды управления тактовой синхронизацией инвертирует импульс управления затвором во время процесса передачи импульса управления затвором.

[0008] Схема защелки на элементах ИЛИ-НЕ дополнительно содержит многоступенчатую схему НЕ, соединенную с выходным концом затвора И-НЕ.

[0009] Многоступенчатая схема НЕ содержит множество последовательно включенных вторых инверторов.

[0010] Количество вторых инверторов равно трем.

[0011] Тактовые сигналы соседних регистров сдвига взаимно обратны.

[0012] Настоящее изобретение предусматривает схему управления затвором, содержащую множество схем регистра сдвига, которые соединены каскадом, и каждая из схем регистра сдвига содержит схему передачи команды управления тактовой синхронизацией и схему защелки на элементах ИЛИ-НЕ, причем схема передачи команды управления тактовой синхронизацией запускается первым тактовым импульсом тактового сигнала для передачи импульса управления затвором предыдущего этапа в схему защелки на элементах ИЛИ-НЕ, и схема защелки на элементах ИЛИ-НЕ выполняет функцию защелки, и схема защелки на элементах ИЛИ-НЕ дополнительно запускается вторым тактовым импульсом после первого тактового импульса для вывода импульса управления затвором.

[0013] Схема передачи команды управления тактовой синхронизацией и схема защелки на элементах ИЛИ-НЕ соответственно являются управляемыми по переднему фронту тактового импульса.

[0014] Схема защелки на элементах ИЛИ-НЕ, по меньшей мере, содержит первый инвертор, первый затвор ИЛИ-НЕ, второй затвор ИЛИ-НЕ и затвор И-НЕ, причем входной конец первого инвертора соединен с выходным концом схемы передачи команды управления тактовой синхронизацией, и первый входной конец первого затвора ИЛИ-НЕ соединен с выходным концом первого инвертора, а второй входной конец первого затвора ИЛИ-НЕ соединен с выходным концом второго затвора ИЛИ-НЕ, и первый входной конец второго затвора ИЛИ-НЕ соединен с входным концом первого инвертора, а второй входной конец второго затвора ИЛИ-НЕ соединен с выходным концом первого затвора ИЛИ-НЕ, а выходной конец второго затвора ИЛИ-НЕ дополнительно соединен с первый входным концом затвора И-НЕ, а второй входной конец затвора И-НЕ принимает тактовый сигнал.

[0015] Схема передачи команды управления тактовой синхронизацией инвертирует импульс управления затвором во время процесса передачи импульса управления затвором.

[0016] Схема защелки на элементах ИЛИ-НЕ дополнительно содержит многоступенчатую схему НЕ, соединенную с выходным концом затвора И-НЕ.

[0017] Многоступенчатая схема НЕ содержит множество последовательно включенных вторых инверторов.

[0018] Количество вторых инверторов равно трем.

[0019] Тактовые сигналы соседних регистров сдвига взаимно обратны.

[0020] Настоящее изобретение дополнительно предусматривает регистр сдвига, содержащий схему передачи команды управления тактовой синхронизацией и схему защелки на элементах ИЛИ-НЕ, и схема защелки на элементах ИЛИ-НЕ, по меньшей мере, содержит первый инвертор, первый затвор ИЛИ-НЕ, второй затвор ИЛИ-НЕ и затвор И-НЕ, причем входной конец первого инвертора соединен с выходным концом схемы передачи команды управления тактовой синхронизацией, и первый входной конец первого затвора ИЛИ-НЕ соединен с выходным концом первого инвертора, а второй входной конец первого затвора ИЛИ-НЕ соединен с выходным концом второго затвора ИЛИ-НЕ, и первый входной конец второго затвора ИЛИ-НЕ соединен с входным концом первого инвертора, а второй входной конец второго затвора ИЛИ-НЕ соединен с выходным концом первого затвора ИЛИ-НЕ, а выходной конец второго затвора ИЛИ-НЕ дополнительно соединен с первый входным концом затвора И-НЕ.

[0021] Схема защелки на элементах ИЛИ-НЕ дополнительно содержит многоступенчатую схему НЕ, соединенную с выходным концом затвора И-НЕ.

[0022] Многоступенчатая схема НЕ содержит множество последовательно включенных вторых инверторов.

[0023] Количество вторых инверторов равно трем.

[0024] В соответствии с вышеупомянутыми решениями преимущества настоящего изобретения заключаются в следующем: в схеме управления затвором согласно настоящему изобретению схема передачи команды управления тактовой синхронизацией запускается первым тактовым импульсом тактового сигнала для передачи импульса управления затвором предыдущего этапа в схему защелки на элементах ИЛИ-НЕ, и схема защелки на элементах ИЛИ-НЕ выполняет функцию защелки, и схема защелки на элементах ИЛИ-НЕ дополнительно запускается вторым тактовым импульсом после первого тактового импульса для вывода импульса управления затвором. Таким образом, оно применимо к CMOS-процессу, и потребляемая мощность низкая, а допускаемый диапазон уровней шумов широкий.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Чтобы более четко проиллюстрировать варианты осуществления настоящего изобретения, следующие чертежи будут кратко описаны в вариантах осуществления. Очевидно, что чертежи являются только некоторыми вариантами осуществления настоящего изобретения, обычный специалист в данной области техники может получить другие чертежи в соответствии с этими чертежами без творческих усилий. На чертежах:

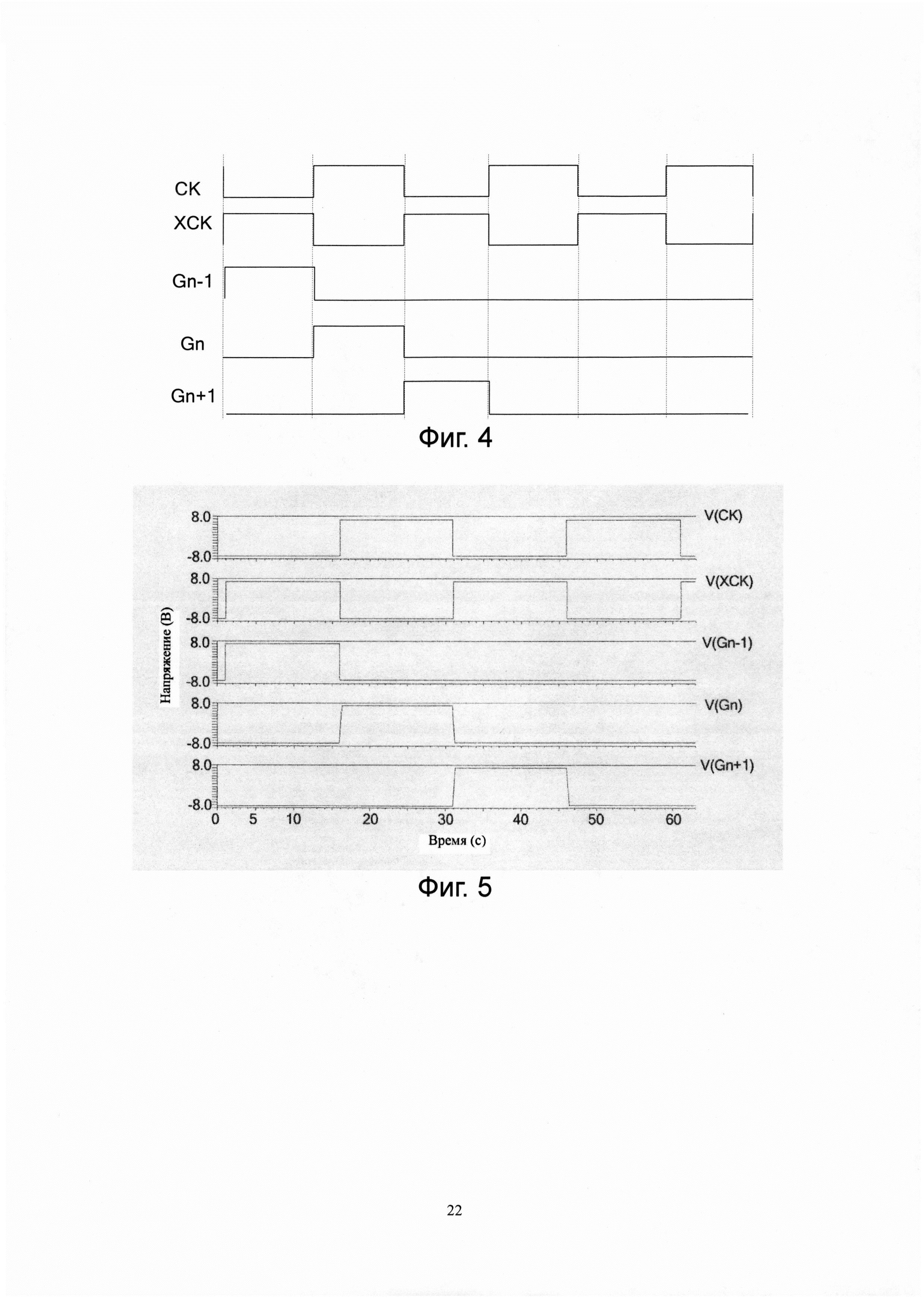

[0025] Фиг. 1 - структурная диаграмма схемы управления затвором в соответствии с вариантом осуществления настоящего изобретения;

[0026] Фиг. 2 - принципиальная схема регистра сдвига, показанного на фиг. 1;

[0027] Фиг. 3 - принципиальная схема регистра сдвига в соответствии со вторым вариантом осуществления настоящего изобретения;

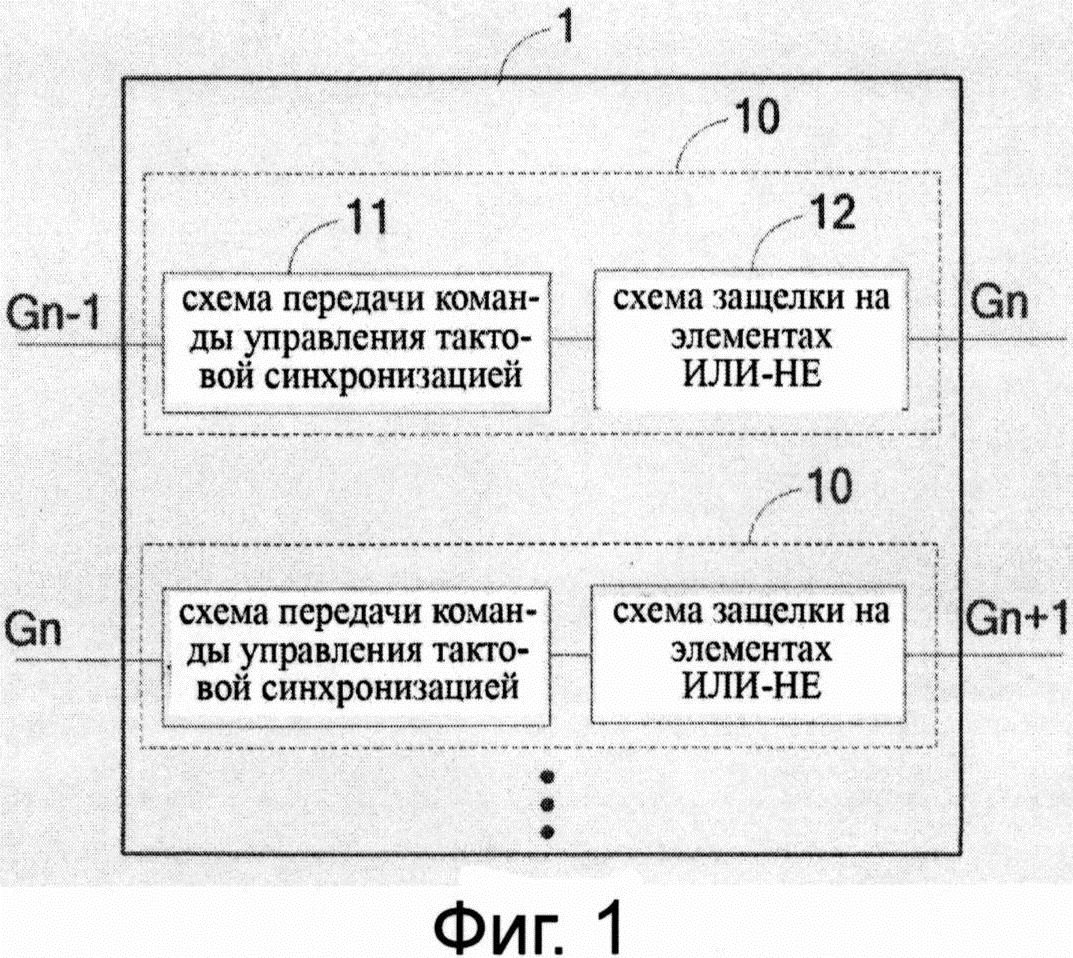

[0028] Фиг. 4 - диаграмма теоретической последовательности схемы управления затвором в соответствии с вариантом осуществления настоящего изобретения;

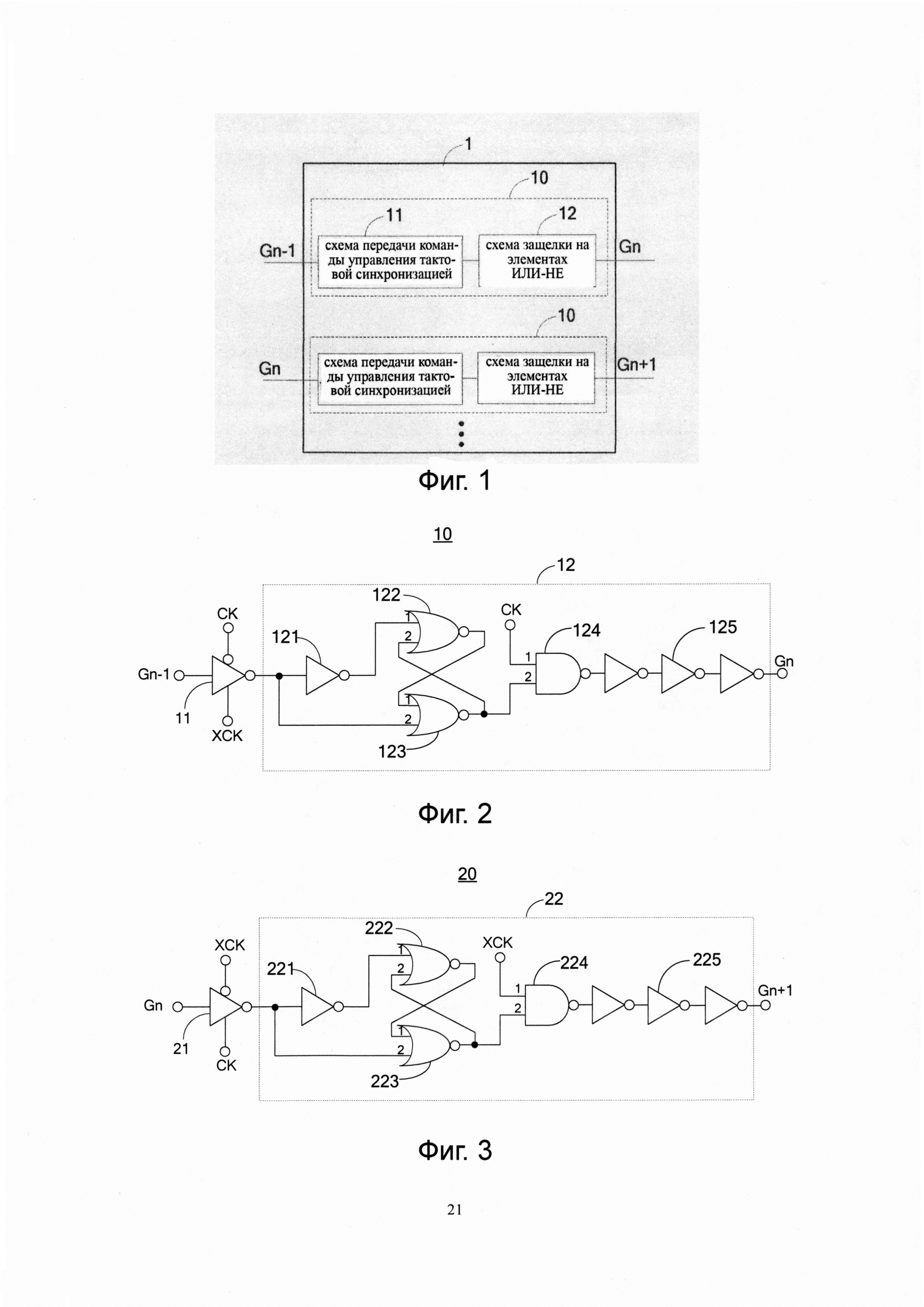

[0029] Фиг. 5 - диаграмма смоделированной последовательности схемы управления затвором в соответствии с вариантом осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

[0030] Варианты осуществления настоящего изобретения подробно описаны с техническими вопросами, конструктивными особенностями, достигнутыми целями и эффектами со ссылкой на прилагаемые чертежи следующим образом. Очевидно, что описанные варианты осуществления являются лишь частью вариантов осуществления настоящего изобретения, а не всеми вариантами осуществления. На основе вариантов осуществления настоящего изобретения все другие варианты осуществления, полученные обычным специалистом в данной области без творческих усилий, должны рассматриваться в пределах объема правовой охраны настоящего изобретения.

[0031] См. фиг. 1, фиг. 1 - структурная диаграмма схемы управления затвором в соответствии с вариантом осуществления настоящего изобретения. Как показано на фиг. 1, схема управления затвором 1, раскрытая в варианте осуществления настоящего изобретения, содержит множество схем регистра сдвига 10, которые соединены каскадом, и каждая из схем регистра сдвига 10 содержит схему передачи команды управления тактовой синхронизацией 11 и схему защелки на элементах ИЛИ-НЕ 12, причем схема передачи команды управления тактовой синхронизацией 11 запускается первым тактовым импульсом тактового сигнала для передачи импульса управления затвором предыдущего этапа в схему защелки на элементах ИЛИ-НЕ 12, и схема защелки на элементах ИЛИ-НЕ 12 выполняет функцию защелки, и схема защелки на элементах ИЛИ-НЕ 12 дополнительно запускается вторым тактовым импульсом после первого тактового импульса для вывода импульса управления затвором. Схема передачи команды управления тактовой синхронизацией 11 инвертирует импульс управления затвором во время процесса передачи импульса управления затвором. Между тем, схема передачи команды управления тактовой синхронизацией 11 и схема защелки на элементах ИЛИ-НЕ 12 соответственно являются управляемыми по переднему фронту тактового импульса. Вариант осуществления настоящего изобретения управляет передачей сигнала с предыдущего последнего этапа с помощью схемы передачи команды управления тактовой синхронизацией 11 и фиксирует сигнал с помощью схемы защелки на элементах ИЛИ-НЕ 12, которые применимы к CMOS-процессу, и потребляемая мощность низкая, а допускаемый диапазон уровней шумов широкий.

[0032] В конкретных вариантах осуществления, как показано на фиг. 2, схема защелки на элементах ИЛИ-НЕ 12, по меньшей мере, содержит первый инвертор 121, первый затвор ИЛИ-НЕ 122, второй затвор ИЛИ-НЕ 123 и затвор И-НЕ 124, причем входной конец первого инвертора 121 соединен с выходным концом схемы передачи команды управления тактовой синхронизацией 11, и первый входной конец первого затвора ИЛИ-НЕ 122 соединен с выходным концом первого инвертора 121, а второй входной конец первого затвора ИЛИ-НЕ 122 соединен с выходным концом второго затвора ИЛИ-НЕ 123, и первый входной конец второго затвора ИЛИ-НЕ 123 соединен с входным концом первого инвертора 121, а второй входной конец второго затвора ИЛИ-НЕ 123 соединен с выходным концом первого затвора ИЛИ-НЕ 122, а выходной конец второго затвора ИЛИ-НЕ 123 дополнительно соединен с первый входным концом затвора И-НЕ 124, а второй входной конец затвора И-НЕ 124 принимает тактовый сигнал CK. Схема защелки на элементах ИЛИ-НЕ 12 дополнительно содержит многоступенчатую схему НЕ, соединенную с выходным концом затвора И-НЕ для обеспечения возможности управления схемы управления затвором 1. Многоступенчатая схема НЕ содержит множество последовательно включенных вторых инверторов 124. Предпочтительно, количество вторых инверторов 124 равно трем.

[0033] Конкретный принцип работы схем регистра сдвига 10 следующий: когда первый тактовый импульс тактового сигнала CK находится на нарастающем фронте, схема передачи команды управления тактовой синхронизацией 11 запускается для передачи импульса управления затвором Gn-1 предыдущего этапа первому инвертору 121. Импульс управления затвором Gn-1 инвертируется во время процесса передачи, а затем передается на первый затвор ИЛИ-НЕ 122 и второй затвор ИЛИ-НЕ 123 через первый инвертор 121. Импульс управления затвором Gn-1 предыдущего этапа фиксируется первым затвором ИЛИ-НЕ 122 и вторым затвором ИЛИ-НЕ 123 пересекающегося соединения. Поскольку второй тактовый импульс тактового сигнала CK находится на нарастающем фронте, то есть следующий тактовый импульс тактового сигнала CK находится на нарастающем фронте, запускается схема защелки на элементах ИЛИ-НЕ 12, а импульс управления затвором Gn-1 предыдущего этапа, зафиксированный с помощью первого затвора ИЛИ-НЕ 122 и второго затвора ИЛИ-НЕ 123 пересекающегося соединения, передается во второй инвертор 124, а затем передается на затвор Gn последнего этапа через второй инвертор 124. Схема передачи команды управления тактовой синхронизацией 11 дополнительно содержит тактовый сигнал XCK, а тактовый сигнал XCK и тактовый сигнал CK являются обратными по фазе.

[0034] В вариантах осуществления настоящего изобретения тактовые сигналы смежных регистров сдвига взаимно обратны. См. фиг.3. Регистр сдвига 20 содержит схему передачи команды управления тактовой синхронизацией 21 и схему защелки на элементах ИЛИ-НЕ 22. Схема защелки на элементах ИЛИ-НЕ 22, по меньшей мере, содержит первый инвертор 221, первый затвор ИЛИ-НЕ 222, второй затвор ИЛИ-НЕ 223 и затвор И-НЕ 224, причем входной конец первого инвертора 221 соединен с выходным концом схемы передачи команды управления тактовой синхронизацией 21, и первый входной конец первого затвора ИЛИ-НЕ 222 соединен с выходным концом первого инвертора 221, а второй входной конец первого затвора ИЛИ-НЕ 222 соединен с выходным концом второго затвора ИЛИ-НЕ 223, и первый входной конец второго затвора ИЛИ-НЕ 223 соединен с входным концом первого инвертора 221, а второй входной конец второго затвора ИЛИ-НЕ 223 соединен с выходным концом первого затвора ИЛИ-НЕ 222, а выходной конец второго затвора ИЛИ-НЕ 223 дополнительно соединен с первый входным концом затвора И-НЕ 224, а второй входной конец затвора И-НЕ 224 принимает тактовый сигнал XCK. Схема защелки на элементах ИЛИ-НЕ 22 дополнительно содержит многоступенчатую схему НЕ, соединенную с выходным концом затвора И-НЕ для обеспечения возможности управления схемы управления затвором 1. Многоступенчатая схема НЕ содержит множество последовательно включенных вторых инверторов 224. Предпочтительно, количество вторых инверторов 224 равно трем.

[0035] Конкретный принцип работы схем регистра сдвига 20 следующий: когда первый тактовый импульс тактового сигнала XCK находится на нарастающем фронте, схема передачи команды управления тактовой синхронизацией 21 запускается для передачи импульса управления затвором Gn предыдущего этапа первому инвертору 221. Импульс управления затвором Gn предыдущего этапа инвертируется во время процесса передачи, а затем передается на первый затвор ИЛИ-НЕ 222 и второй затвор ИЛИ-НЕ 223 через первый инвертор 221. Импульс управления затвором Gn предыдущего этапа фиксируется первым затвором ИЛИ-НЕ 222 и вторым затвором ИЛИ-НЕ 223 пересекающегося соединения. Поскольку второй тактовый импульс тактового сигнала XCK находится на нарастающем фронте, то есть следующий тактовый импульс тактового сигнала XCK находится на нарастающем фронте, запускается схема защелки на элементах ИЛИ-НЕ 22, а импульс управления затвором Gn предыдущего этапа, зафиксированный с помощью первого затвора ИЛИ-НЕ 222 и второго затвора ИЛИ-НЕ 223 пересекающегося соединения, передается во второй инвертор 224, а затем передается на затвор Gn+1 третьего этапа через второй инвертор 224. Схема передачи команды управления тактовой синхронизацией 21 дополнительно содержит тактовый сигнал XCK, а тактовый сигнал XCK и тактовый сигнал CK являются обратными по фазе.

[0036] В вариантах осуществления настоящего изобретения регистры сдвига 10 и регистры сдвига 20 являются соседними. В практическом применении множество схем регистра сдвига, которые соединены каскадом в схеме управления затвором 1, можно разделить на нечетные ступени и четные ступени. Регистры сдвига 10 могут использоваться как регистры сдвига нечетных ступеней, а регистры сдвига 20 могут быть регистрами сдвига четных ступеней. Альтернативно, регистры сдвига 20 могут использоваться как регистры сдвига нечетных ступеней, а регистры сдвига 10 могут быть регистрами сдвига четных ступеней. См. фиг. 4. Фиг. 4 - диаграмма теоретической последовательности схемы управления затвором в соответствии с вариантом осуществления настоящего изобретения. Регистры сдвига 10 используются в качестве регистров сдвига нечетных ступеней, а регистры сдвига 20 являются регистрами сдвига четных ступеней. Как показано на чертеже, тактовый сигнал CK и тактовый сигнал XCK являются обратными по фазе. Поскольку тактовый сигнал CK находится на нарастающем фронте, импульс управления затвором Gn-1 предыдущего этапа передается на затвор последнего этапа, то есть импульс управления затвором Gn-1 предыдущего этапа меняется с уровня высокого напряжения на уровень низкого напряжения, а импульс управления затвором Gn последнего этапа меняется с уровня низкого напряжения на уровень высокого напряжения, чтобы управлять соответствующим затвором. Поскольку тактовый сигнал XCK находится на нарастающем фронте, импульс управления затвором Gn последнего этапа передается на затвор третьего этапа, то есть импульс управления затвором Gn последнего этапа меняется с уровня высокого напряжения на уровень низкого напряжения, а импульс управления затвором Gn+1 третьего этапа меняется с уровня низкого напряжения на уровень высокого напряжения, чтобы управлять соответствующим затвором. Фиг. 5 - диаграмма смоделированной последовательности схемы управления затвором в соответствии с вариантом осуществления настоящего изобретения. См. фиг. 5, ось Y - напряжение, а ось X - время. Как показано на чертеже, смоделированная последовательность схемы управления затвором такая же, как и теоретическая последовательность на фиг. 4.

[0037] Настоящее изобретение дополнительно предусматривает регистр сдвига, как показано на фиг. 2, регистр сдвига содержит схему передачи команды управления тактовой синхронизацией 11 и схему защелки на элементах ИЛИ-НЕ 12. Схема защелки на элементах ИЛИ-НЕ 12, по меньшей мере, содержит первый инвертор 121, первый затвор ИЛИ-НЕ 122, второй затвор ИЛИ-НЕ 123 и затвор И-НЕ 124, причем входной конец первого инвертора 121 соединен с выходным концом схемы передачи команды управления тактовой синхронизацией 11, и первый входной конец первого затвора ИЛИ-НЕ 122 соединен с выходным концом первого инвертора 121, а второй входной конец первого затвора ИЛИ-НЕ 122 соединен с выходным концом второго затвора ИЛИ-НЕ 123, и первый входной конец второго затвора ИЛИ-НЕ 123 соединен с входным концом первого инвертора 121, а второй входной конец второго затвора ИЛИ-НЕ 123 соединен с выходным концом первого затвора ИЛИ-НЕ 122, а выходной конец второго затвора ИЛИ-НЕ 123 дополнительно соединен с первый входным концом затвора И-НЕ 124, а второй входной конец затвора И-НЕ 124 принимает тактовый сигнал CK. Схема защелки на элементах ИЛИ-НЕ 12 дополнительно содержит многоступенчатую схему НЕ, соединенную с выходным концом затвора И-НЕ для обеспечения возможности управления. Многоступенчатая схема НЕ содержит множество последовательно включенных вторых инверторов 124. Предпочтительно, количество вторых инверторов 124 равно трем.

[0038] Конкретный принцип работы схем регистра сдвига 10 следующий: когда первый тактовый импульс тактового сигнала CK находится на нарастающем фронте, схема передачи команды управления тактовой синхронизацией 11 запускается для передачи импульса управления затвором Gn-1 предыдущего этапа первому инвертору 121. Импульс управления затвором Gn-1 инвертируется во время процесса передачи, а затем передается на первый затвор ИЛИ-НЕ 122 и второй затвор ИЛИ-НЕ 123 через первый инвертор 121. Импульс управления затвором Gn-1 предыдущего этапа фиксируется первым затвором ИЛИ-НЕ 122 и вторым затвором ИЛИ-НЕ 123 пересекающегося соединения. Поскольку второй тактовый импульс тактового сигнала CK находится на нарастающем фронте, то есть следующий тактовый импульс тактового сигнала CK находится на нарастающем фронте, запускается схема защелки на элементах ИЛИ-НЕ 12, а импульс управления затвором Gn-1 предыдущего этапа, зафиксированный с помощью первого затвора ИЛИ-НЕ 122 и второго затвора ИЛИ-НЕ 123 пересекающегося соединения, передается во второй инвертор 124, а затем передается на затвор Gn последнего этапа через второй инвертор 124. Схема передачи команды управления тактовой синхронизацией 11 дополнительно содержит тактовый сигнал XCK, а тактовый сигнал XCK и тактовый сигнал CK являются обратными по фазе. В вариантах осуществления настоящего изобретения, составляя схему управления затвором с множеством регистров сдвига 10, которые соединены каскадом, схемы соседних регистров сдвига управляются тактовыми сигналами, обратными по фазе. Передача сигнала предыдущего последнего этапа управляется с помощью схемы передачи команды управления тактовой синхронизацией 11, и сигнал фиксируется с помощью схемы защелки на элементах ИЛИ-НЕ 12, которые применимы к CMOS-процессу, и потребляемая мощность низкая, а допускаемый диапазон уровней шумов широкий.

[0039] В заключение, в схеме управления затвором согласно настоящему изобретению схема передачи команды управления тактовой синхронизацией запускается первым тактовым импульсом тактового сигнала для передачи импульса управления затвором предыдущего этапа в схему защелки на элементах ИЛИ-НЕ, и схема защелки на элементах ИЛИ-НЕ выполняет функцию защелки, и схема защелки на элементах ИЛИ-НЕ дополнительно запускается вторым тактовым импульсом после первого тактового импульса для вывода импульса управления затвором. Таким образом, она применима к CMOS-процессу, и потребляемая мощность низкая, а допускаемый диапазон уровней шумов широкий.

[0040] Вышеприведенное является только конкретными вариантами осуществления настоящего изобретения, объем настоящего изобретения не ограничивается этим, и для любых лиц, которые квалифицированы в данной области техники, изменения или замены, которые легко сделать, должны быть охвачены защищаемым объемом изобретения. Таким образом, защищаемый объем изобретения должен исходить из заявленных пунктов формулы изобретения.