Результат интеллектуальной деятельности: СХЕМА GOA И ЖИДКОКРИСТАЛЛИЧЕСКИЙ ДИСПЛЕЙ

Вид РИД

Изобретение

УРОВЕНЬ ТЕХНИКИ

Область техники

Изобретение относится к области техники жидкокристаллических дисплеев и, в частности, к схеме GOA (привода затвора на матрице) и жидкокристаллическому дисплею.

Предшествующий уровень техники

Среди дисплеев небольшого размера с высоким разрешением известно, что технология LTPS (низкотемпературного поликристаллического кремния) широко используется благодаря высокой мобильности и стабильности. Однако, низкая производительность дисплеев LTPS сильно озадачила производителей панелей. В связи с этим, испытание матрицы является необходимым и оперативным подходом для мониторинга каждого производственного процесса.

С развитием LTPS полупроводниковых тонкопленочных транзисторов из-за сверхвысокой подвижности носителей LTPS полупроводниковых тонкопленочных транзисторов соответствующие периферийные интегральные схемы для панелей стали центром внимания каждого. И многие люди целиком отдаются исследованиям смежных с Системой на панели (SOP) технологий, и это постепенно становится реальностью.

Хотя LTPS полупроводниковые тонкопленочные транзисторы имеют более высокую подвижность носителей, пороговое напряжение ниже (необычно около 0 вольт), а динамика пороговой области небольшая. В выключенном состоянии схемы GOA многие элементы работают около V или выше V. Это увеличивает сложность конструкции схемы LTPS GOA. Многие схемы управления сканированием, применяемые для полупроводников из аморфного кремния, не могут быть легко применены к LTPS TFT-LCD. Существуют некоторые функциональные проблемы. Это может напрямую привести к сбою в цепи IGZO GOA. Поэтому при проектировании схемы следует учитывать воздействие, оказываемое такими элементами на схему GOA.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Техническая проблема, решаемая, главным образом, настоящим изобретением, заключается в создании схемы GOA и жидкокристаллического дисплея, чтобы гарантировать, что шины сканирования в схеме GOA лучше заряжены для обеспечения нормальной работы для каждой точки в цепи.

Для решения вышеуказанной технической проблемы одно техническое решение, принятое настоящим изобретением, заключается в создании схемы GOA, схемы GOA для жидкокристаллического дисплея, схемы GOA, содержащей множество блоков GOА, блоков GOA N-го уровня, заряжающих горизонтальную шину сканирования N-го уровня в области отображения и содержащих схемы управления повышением N-го уровня, повышающие схемы N-го уровня, передаточные схемы N-го уровня, понижающие схемы N-го уровня и схемы удержания пониженного напряжения N-го уровня; причем повышающие схемы N-го уровня и схемы удержания пониженного напряжения N-го уровня подсоединяются соответственно к точке сигнала затвора N-го уровня и горизонтальной шине сканирования N-го уровня, схемы управления повышением N-го уровня, понижающие схемы N-го уровня и передаточные схемы N-го уровня подсоединяются к точке сигнала затвора N-го уровня; причем повышающие схемы N-го уровня включаются, когда точка сигнала затвора N-го уровня находится на уровне высокого напряжения, принимают первый тактовый сигнал и заряжают горизонтальные шины сканирования N-го уровня, когда первый тактовый сигнал находится на уровне высокого напряжения; причем передаточные схемы N-го уровня принимают второй тактовый сигнал, когда точка сигнала затвора N-го уровня находится на уровне высокого напряжения, и выводят схемы управления N-го уровня для управления работой блоков GOA (N+1)-го уровня; причем ширина импульса второго тактового сигнала больше, чем ширина импульса первого тактового сигнала; причем схемы удержания пониженного напряжения N-го уровня содержат: первый транзистор, имеющий затвор и сток, подсоединенные к постоянному току высокого напряжения; второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к постоянному току высокого напряжения, и исток, подсоединенный к первой общей точке; третий транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку первого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения; четвертый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, и сток, подсоединенный к общей точке; пятый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, и сток, подсоединенный к общей точке; шестой транзистор, имеющий затвор, подсоединенный к истоку четвертого транзистора, сток, подсоединенный к истоку пятого транзистора, и исток, подсоединенный к третьему постоянному току низкого напряжения; седьмой транзистор, имеющий затвор, подсоединенный к истоку четвертого транзистора, и исток, подсоединенный к третьему постоянному току низкого напряжения; восьмой транзистор, имеющий затвор и сток, подсоединенные к постоянному току высокого напряжения; девятый транзистор, имеющий затвор, подсоединенный к истоку восьмого транзистора, сток, подсоединенный к постоянному току высокого напряжения, и исток, подсоединенный к истоку пятого транзистора; десятый транзистор, имеющий затвор, подсоединенный к общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения; и одиннадцатый транзистор, имеющий затвор, подсоединенный к общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения; причем первый постоянный ток низкого напряжения больше второго постоянного тока низкого напряжения, а второй постоянный ток низкого напряжения больше третьего постоянного тока низкого напряжения; причем передаточные схемы N-го уровня содержат ускоряющие конденсаторы N-го уровня; причем ускоряющие конденсаторы N-го уровня подсоединены между точками сигнала затвора N-го уровня и горизонтальной шиной сканирования N-го уровня.

Для решения вышеуказанной технической проблемы другое техническое решение, принятое настоящим изобретением, заключается в создании схемы GOA, схемы GOA, содержащей множество блоков GOA, блоков GOA N-го уровня, заряжающих горизонтальную шину сканирования N-го уровня в области отображения, блоков GOA N-го уровня, содержащих схемы управления повышением N-го уровня, повышающие схемы N-го уровня, передаточные схемы N-го уровня, понижающие схемы N-го уровня и схемы удержания пониженного напряжения N-го уровня; причем повышающие схемы N-го уровня и схемы удержания пониженного напряжения N-го уровня подсоединяются соответственно к точке сигнала затвора N-го уровня и горизонтальной шине сканирования N-го уровня, схемы управления повышением N-го уровня, понижающие схемы N-го уровня и передаточные схемы N-го уровня подсоединяются к точке сигнала затвора N-го уровня; причем повышающие схемы N-го уровня включаются, когда точка сигнала затвора N-го уровня находится на уровне высокого напряжения, принимают первый тактовый сигнал и заряжают горизонтальные шины сканирования N-го уровня, когда первый тактовый сигнал находится на уровне высокого напряжения; причем передаточные схемы N-го уровня принимают второй тактовый сигнал, когда точка сигнала затвора N-го уровня находится на уровне высокого напряжения, и выводят передаточные сигналы N-го уровня для управления работой блоков GOA (N+1)-го уровня; причем ширина импульса второго тактового сигнала больше, чем ширина импульса первого тактового сигнала.

В одном варианте осуществления схемы удержания пониженного напряжения N-го уровня содержат: первый транзистор, имеющий затвор и сток, подсоединенные к постоянному току высокого напряжения; второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к постоянному току высокого напряжения, и исток, подсоединенный к первой общей точке; третий транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку первого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения; четвертый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, и сток, подсоединенный к общей точке; пятый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, и сток, подсоединенный к общей точке; шестой транзистор, имеющий затвор, подсоединенный к истоку четвертого транзистора, сток, подсоединенный к истоку пятого транзистора, и исток, подсоединенный к третьему постоянному току низкого напряжения; седьмой транзистор, имеющий затвор, подсоединенный к истоку четвертого транзистора, и исток, подсоединенный к третьему постоянному току низкого напряжения; восьмой транзистор, имеющий затвор и сток, подсоединенные к постоянному току высокого напряжения; девятый транзистор, имеющий затвор, подсоединенный к истоку восьмого транзистора, сток, подсоединенный к постоянному току высокого напряжения, и исток, подсоединенный к истоку пятого транзистора; десятый транзистор, имеющий затвор, подсоединенный к общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения; и одиннадцатый транзистор, имеющий затвор, подсоединенный к общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения; причем первый постоянный ток низкого напряжения больше второго постоянного тока низкого напряжения, а второй постоянный ток низкого напряжения больше третьего постоянного тока низкого напряжения.

В одном варианте осуществления схемы удержания пониженного напряжения N-го уровня содержат первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, пятый транзистор, шестой транзистор, девятый транзистор, десятый транзистор и одиннадцатый транзистор; причем затвор девятого транзистора подсоединен к общей точке.

В одном варианте осуществления схемы удержания пониженного напряжения N-го уровня содержат первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, шестой транзистор, седьмой транзистор, восьмой транзистор, девятый транзистор, десятый транзистор, и одиннадцатый транзистор; причем сток шестого транзистора и исток девятого транзистора подсоединены к истоку четвертого транзистора, а затвор шестого транзистора и затвор седьмого транзистора подсоединены к точке сигнала затвора N-го уровня.

В одном варианте осуществления схемы удержания пониженного напряжения содержат первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, шестой транзистор, девятый транзистор, десятый транзистор и одиннадцатый транзистор; причем затвор девятого транзистора подсоединен к затвору второго транзистора.

В одном варианте осуществления затвор девятого транзистора подсоединен к общей точке.

В одном варианте осуществления передаточные схемы N-го уровня содержат ускоряющие конденсаторы N-го уровня, причем ускоряющие конденсаторы N-го уровня подсоединены между точками сигнала затвора N-го уровня и горизонтальной шиной сканирования N-го уровня.

В одном варианте осуществления управляющие электроды понижающих схем N-го уровня являются входом с третьим тактовым сигналом; причем скважность первого тактового сигнала меньше 50%, а время пуска уровня высокого напряжения первого тактового сигнала является таким же, как и время пуска уровня высокого напряжения второго тактового сигнала; причем уровень высокого напряжения третьего тактового сигнала соответствует уровню низкого напряжения второго тактового сигнала, а уровень низкого напряжения третьего тактового сигнала соответствует уровню высокого напряжения второго тактового сигнала.

В одном варианте осуществления управляющие электроды понижающих схем N-го уровня являются входом с третьим тактовым сигналом; причем скважность первого тактового сигнала меньше 50%, а время окончания уровня высокого напряжения первого тактового сигнала является таким же, как и время окончания уровня высокого напряжения второго тактового сигнала; причем уровень высокого напряжения третьего тактового сигнала соответствует уровню низкого напряжения второго тактового сигнала, а уровень низкого напряжения третьего тактового сигнала соответствует уровню высокого напряжения второго тактового сигнала.

В отличие от существующей технологии положительные эффекты настоящего изобретения заключаются в том, что два тактовых сигнала, имеющих разную ширину импульса, вводятся в повышающие схемы N-го уровня и передаточные схемы N-го уровня, так что выходные сигналы могут быть отделены от передаточных сигналов. Поэтому уровень напряжения точки Q (N) повышается до лучшего уровня высокого напряжения. Задержка выходных сигналов снижается, и обеспечивается лучшая зарядка шин сканирования в схеме GOA для обеспечения нормальной работы для каждой точки в схеме.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеупомянутые и другие примерные аспекты, особенности и преимущества некоторых примерных вариантов осуществления настоящего изобретения будут более очевидны из последующего описания, взятого вместе с сопроводительными чертежами, на которых:

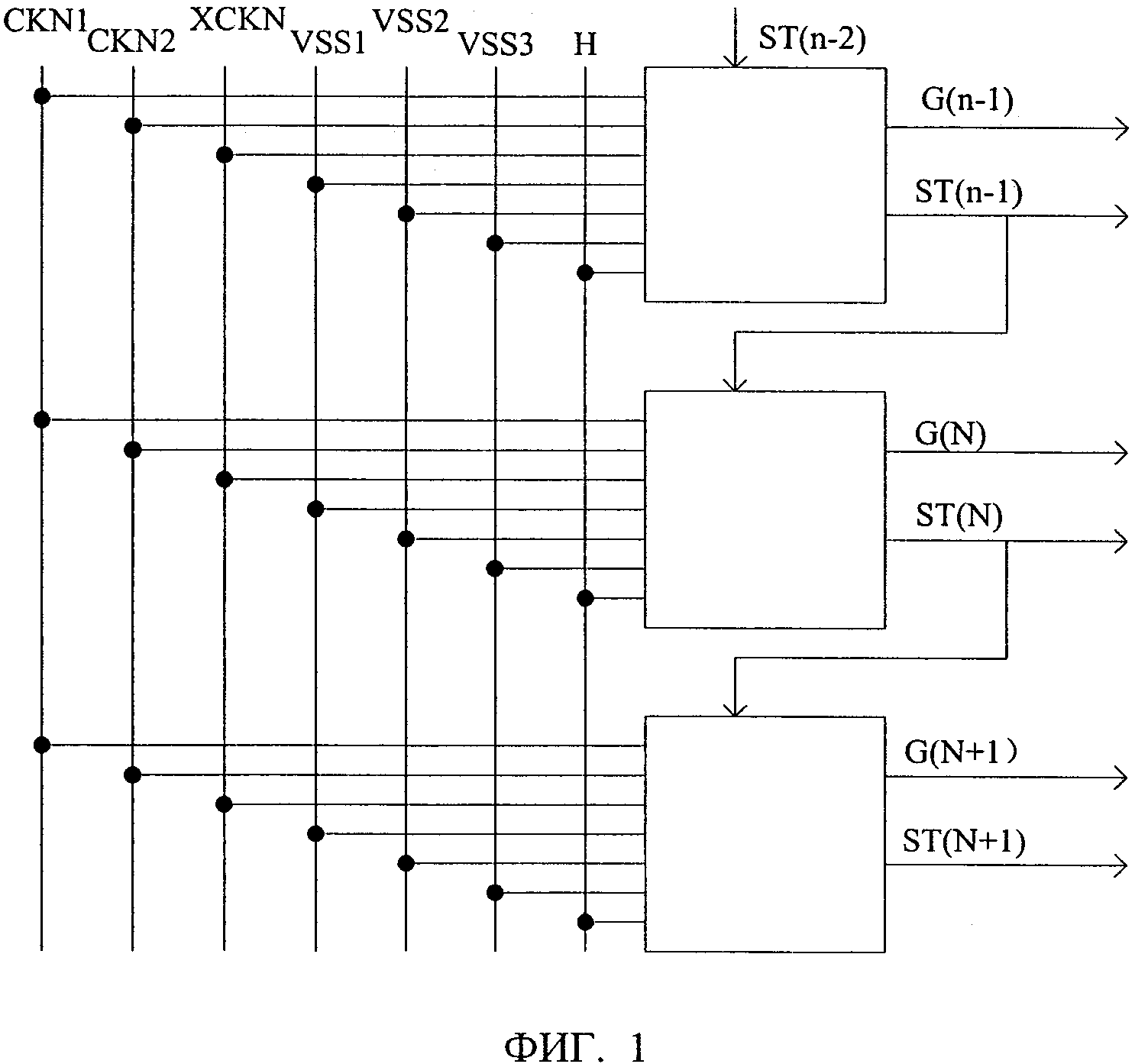

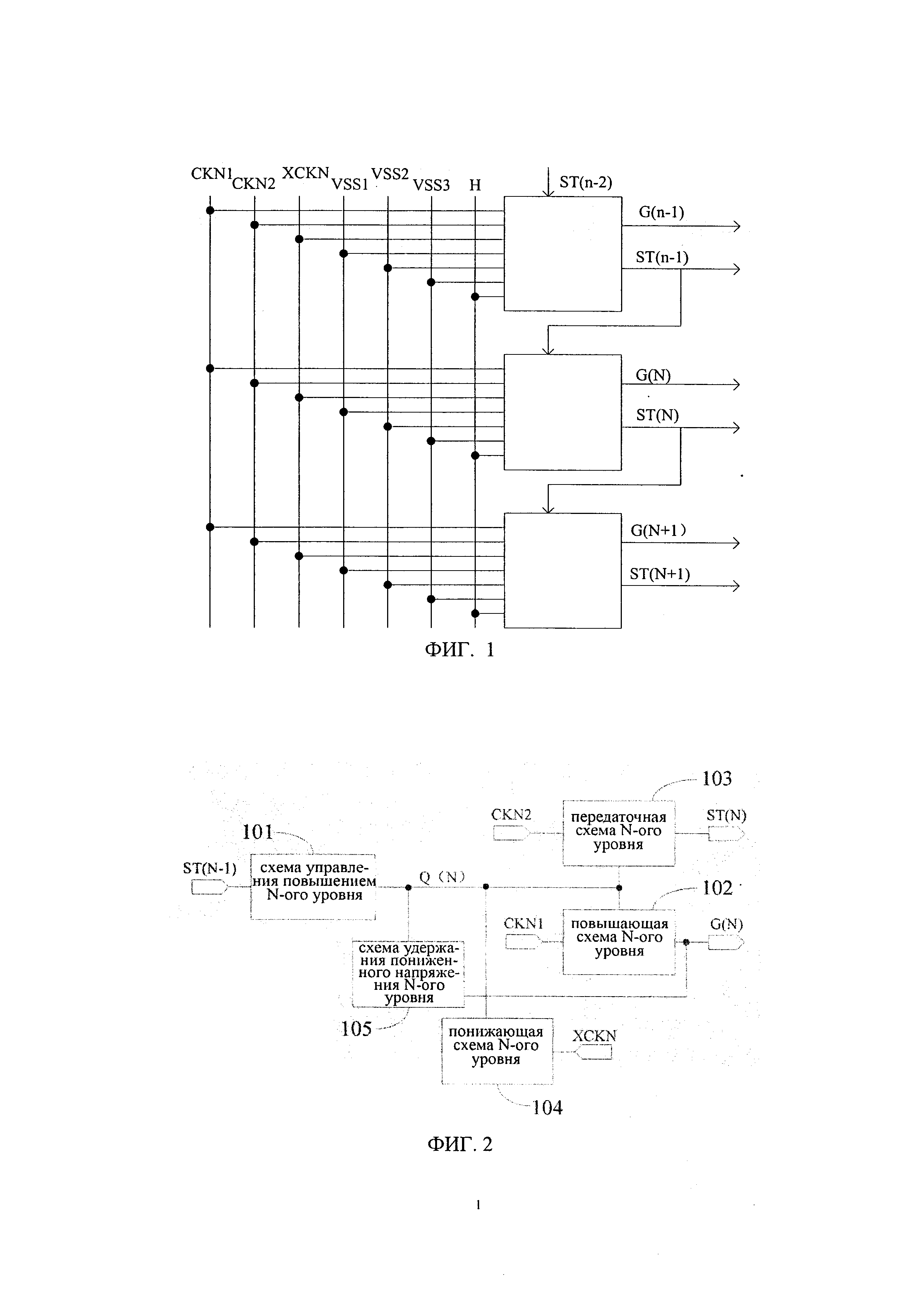

фиг. 1 - схематическая диаграмма каскадных блоков GOA первого варианта осуществления схемы GOA согласно изобретению;

фиг. 2 - схематическая диаграмма блока GOA первого варианта осуществления схемы GOA согласно изобретению;

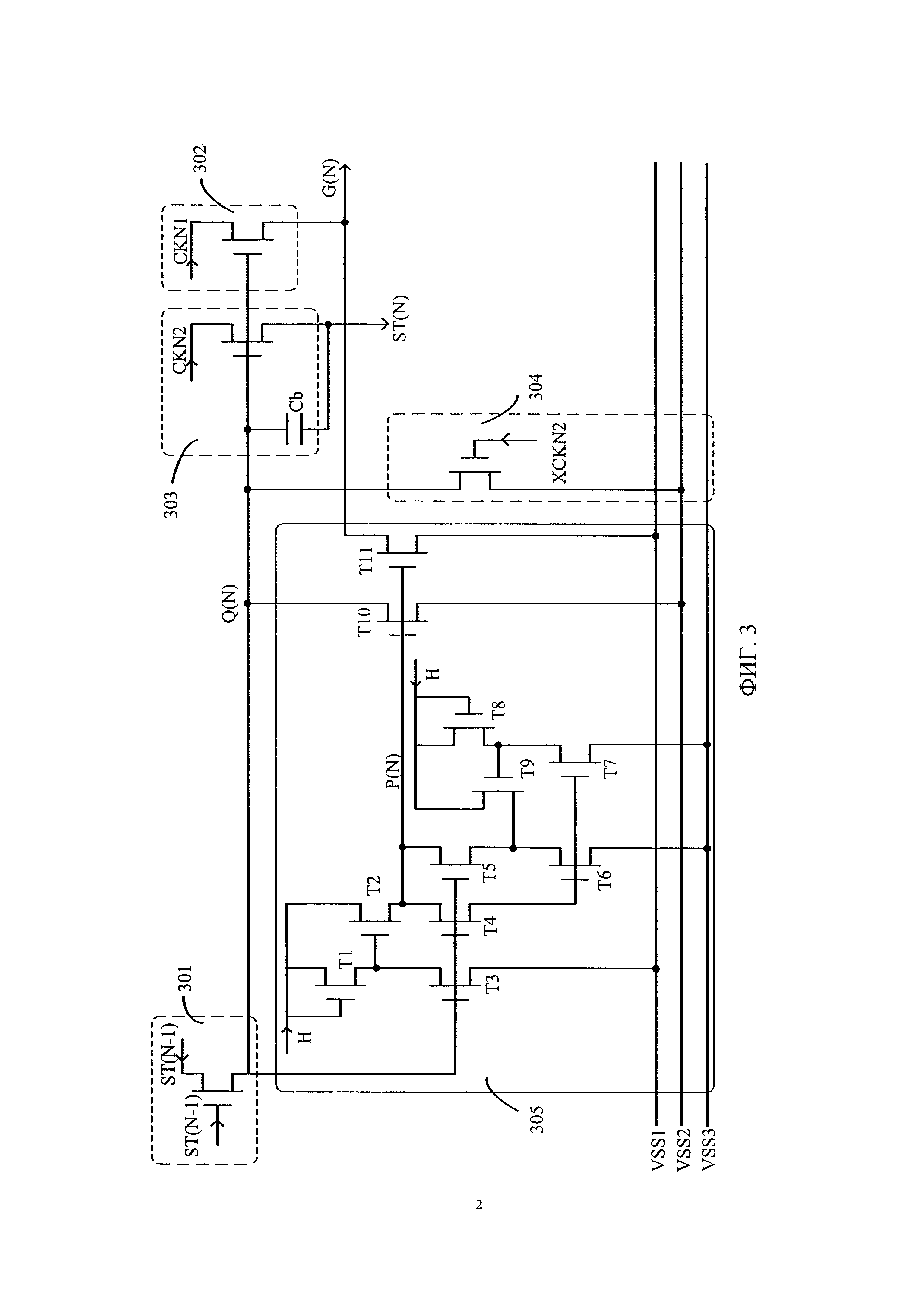

фиг. 3 - схематическая диаграмма, иллюстрирующая конкретное соединение схемы блока GOA второго варианта осуществления схемы GOA согласно изобретению;

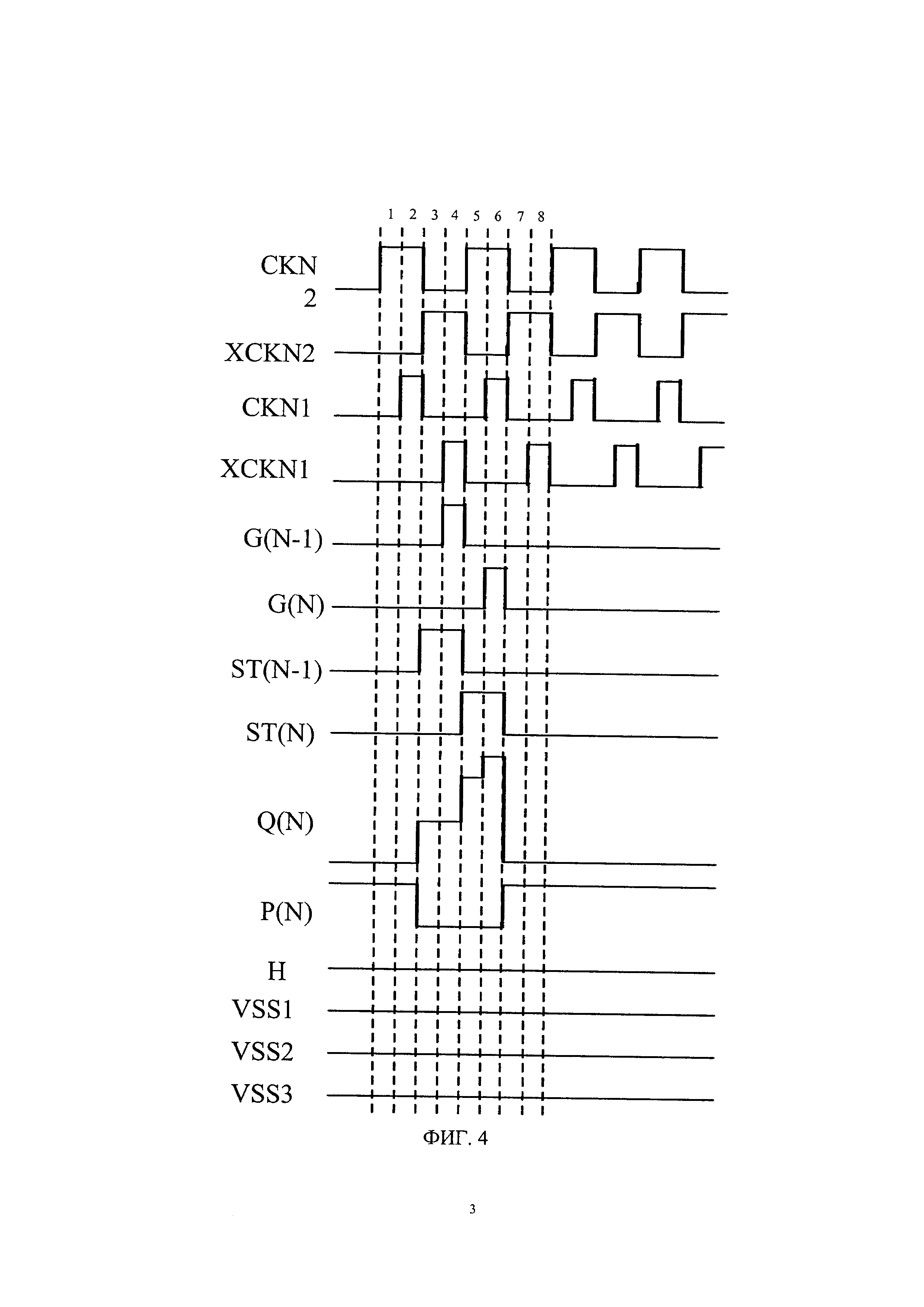

фиг. 4 - схема для первой временной диаграммы сигналов напряжения для каждой точки блока GOA второго варианта осуществления схемы GOA согласно изобретению;

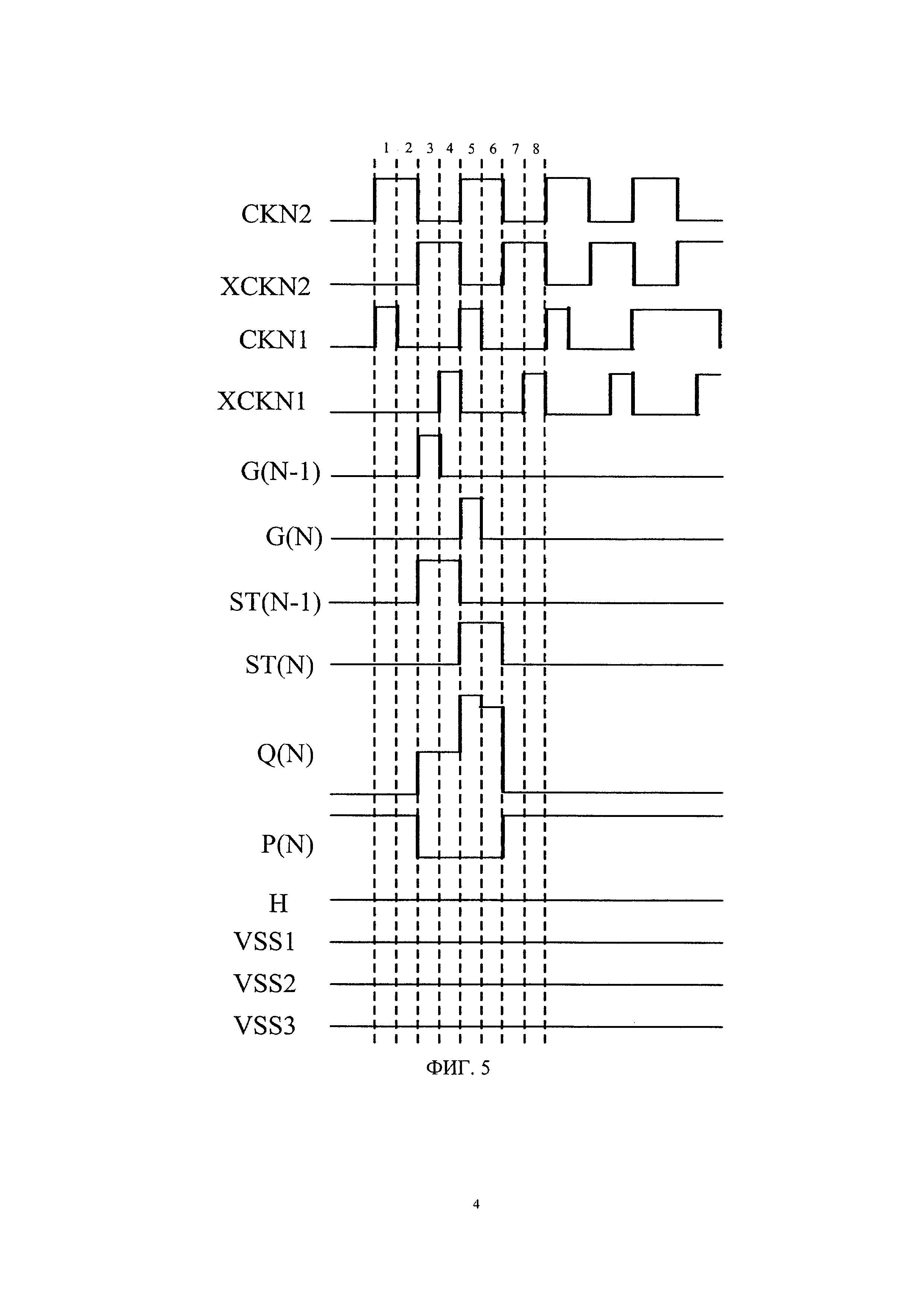

фиг. 5 - схема для второй временной диаграммы сигналов напряжения для каждой точки блока GOA второго варианта осуществления схемы GOA согласно изобретению;

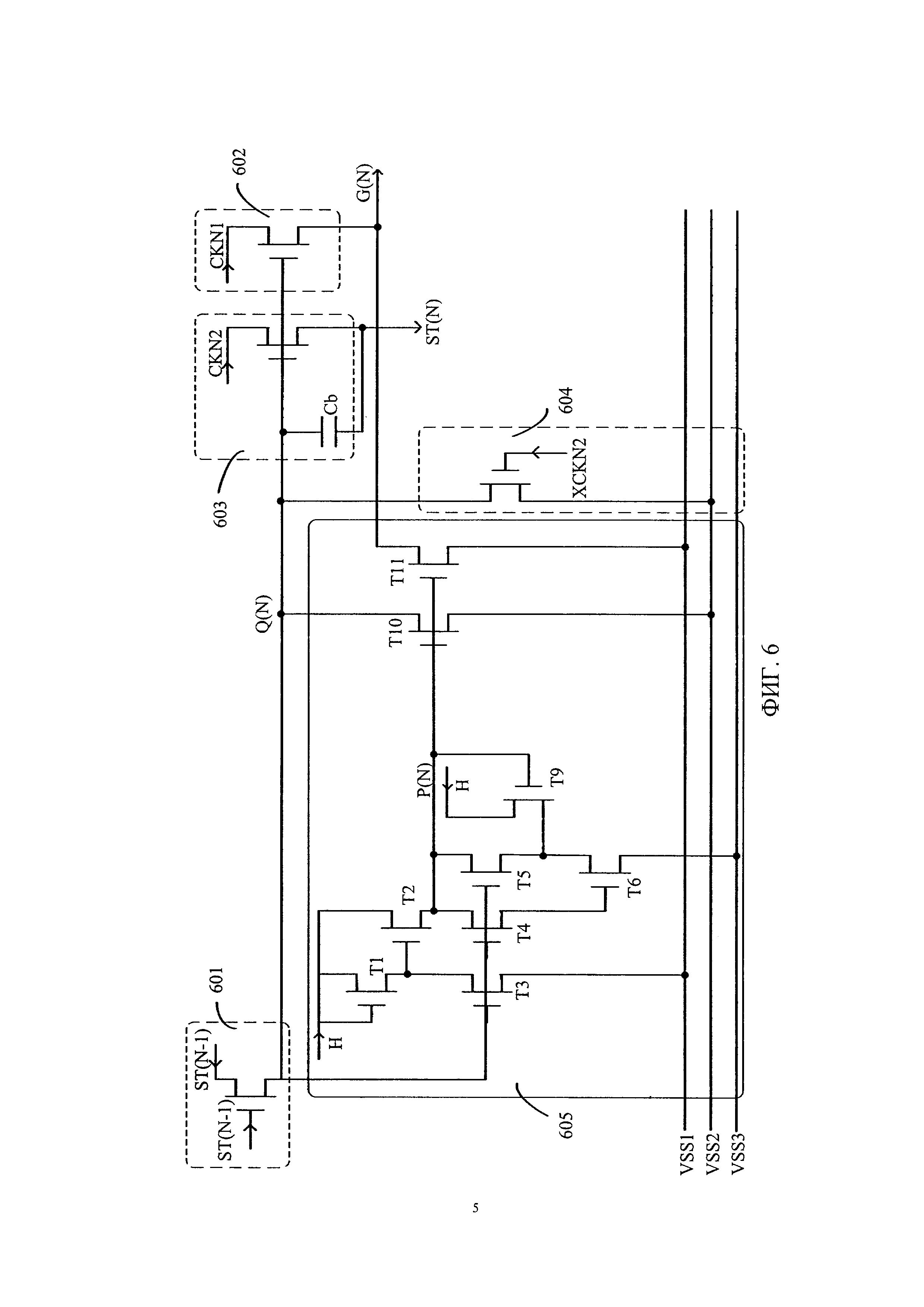

фиг. 6 - схематическая диаграмма, иллюстрирующая конкретное соединение схемы блока GOA третьего варианта осуществления схемы GOA согласно изобретению;

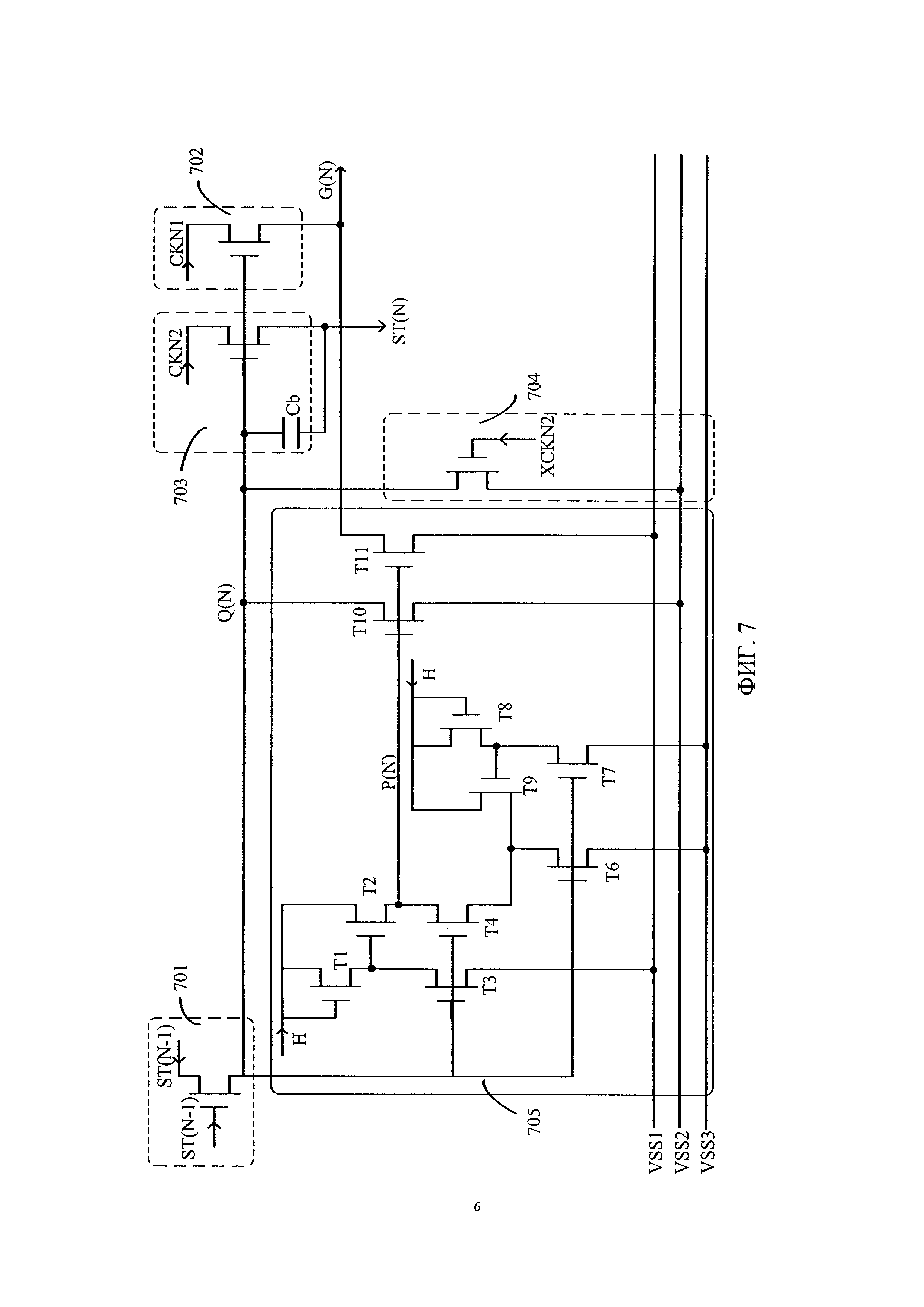

фиг. 7 - схематическая диаграмма, иллюстрирующая конкретное соединение схемы блока GOA четвертого варианта осуществления схемы GOA согласно изобретению;

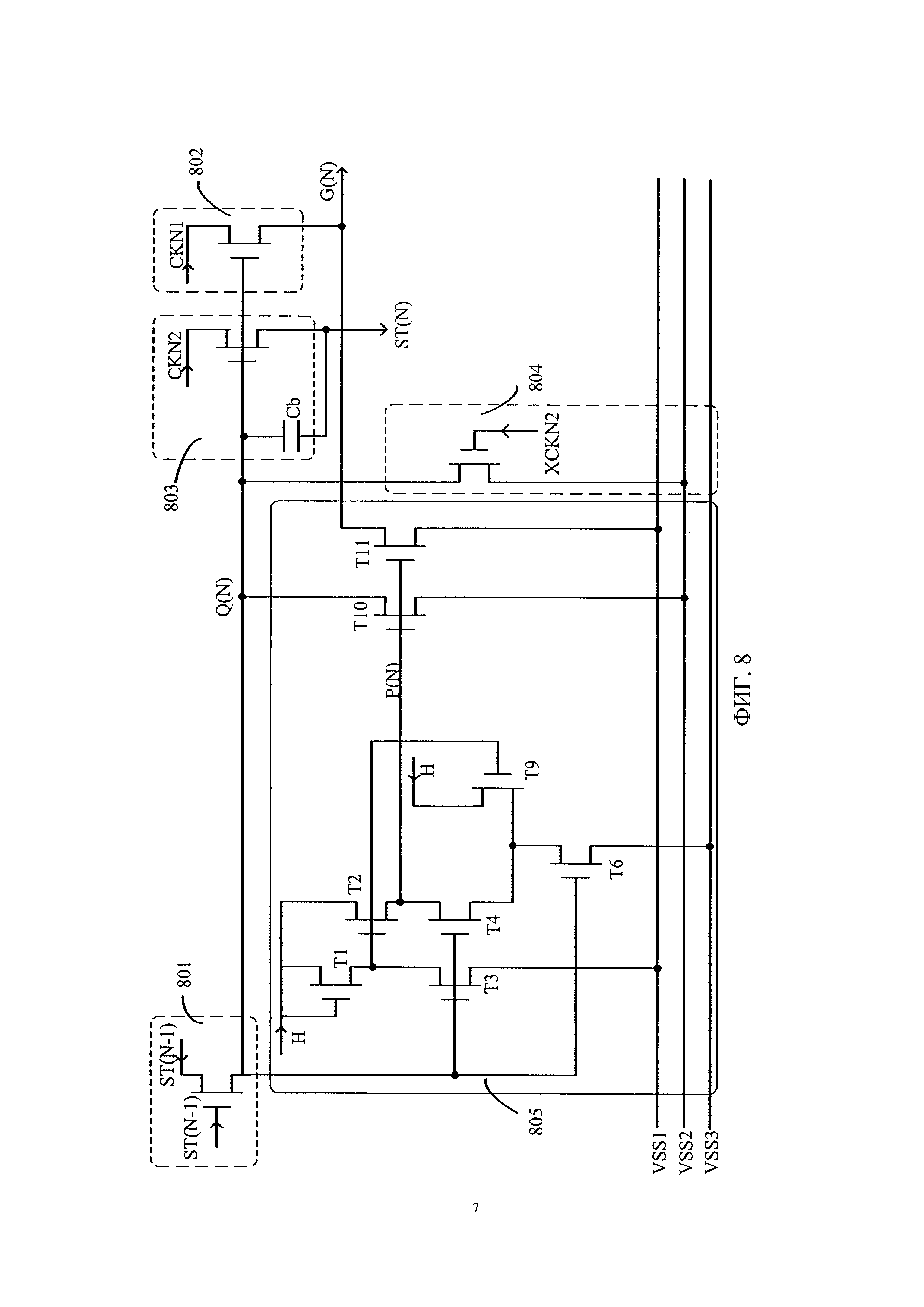

фиг. 8 - схематическая диаграмма, иллюстрирующая конкретное соединение схемы блока GOA пятого варианта осуществления схемы GOA согласно изобретению;

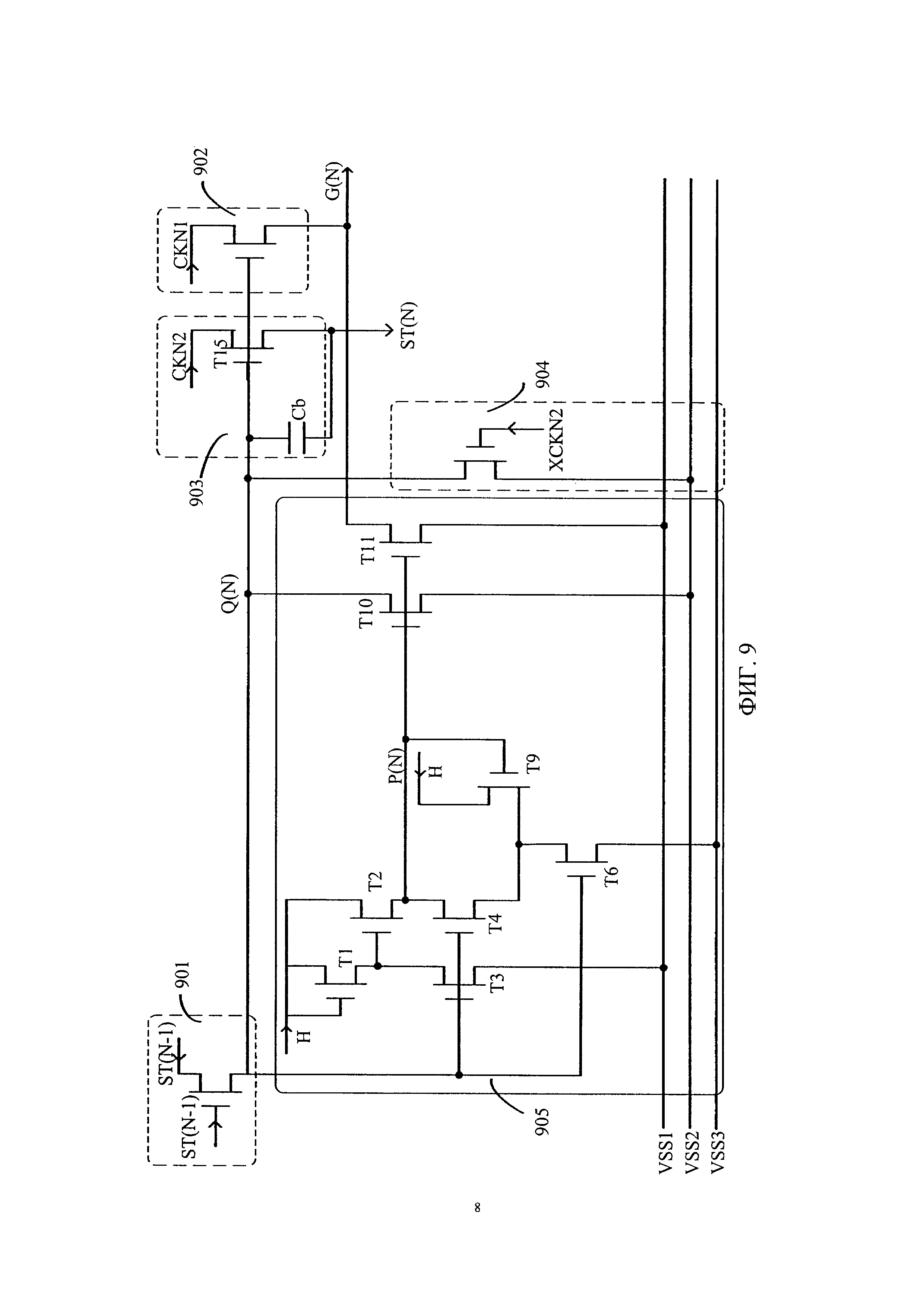

фиг. 9 - схематическая диаграмма, иллюстрирующая конкретное соединение схемы блока GOA шестого варианта осуществления схемы GOA согласно изобретению.

ПОДРОБНОЕ ОПИСАНИЕ

См. фиг.1, схематическую диаграмму каскадных блоков GOA первого варианта осуществления схемы GOA согласно изобретению. Схема GOA содержит множество блоков GOА. Блоки GOA N-го уровня заряжают горизонтальную шину сканирования N-го уровня G (N) в области отображения.

См. фиг. 2, схематическую диаграмму блока GOA первого варианта осуществления схемы GOA согласно изобретению.

Блоки GOA N-го уровня содержат схемы управления повышением N-го уровня 101, повышающие схемы N-го уровня 102, передаточные схемы N-го уровня 103, понижающие схемы N-го уровня 104 и схемы удержания пониженного напряжения N-го уровня 105. Повышающие схемы N-го уровня 102 и схемы удержания пониженного напряжения N-го уровня 105 подсоединяются соответственно к точке сигнала затвора N-го уровня Q(N) и горизонтальной шине сканирования N-го уровня G(N). Схемы управления повышением N-го уровня 101, понижающие схемы N-го уровня 104 и передаточные схемы N-го уровня 103 подсоединяются к точке сигнала затвора N-го уровня Q(N).

Повышающие схемы N-го уровня включаются, когда точка сигнала затвора N-го уровня Q(N) находится на уровне высокого напряжения, принимают первый тактовый сигнал CKN1 и заряжают горизонтальные шины сканирования N-го уровня G(N), когда первый тактовый сигнал CKN1 находится на уровне высокого напряжения. Передаточные схемы N-го уровня принимают второй тактовый сигнал CKN2, когда точка сигнала затвора N-го уровня Q(N) находится на уровне высокого напряжения, и выводят передаточные сигналы N-го уровня ST(N) для управления работой блоков GOA (N+1)-го уровня. Ширина импульса второго тактового сигнала CKN2 больше, чем ширина импульса первого тактового сигнала CKN1.

В частности, схемы управления повышением N-го уровня 101 включаются и повышают уровень напряжения точки сигнала затвора N-го уровня Q(N) до уровня высокого напряжения при приеме сигнала ST(N-1) уровня высокого напряжения, чтобы включить повышающие схемы N-го уровня 102 и передаточные схемы N-го уровня 103, так что повышающие схемы N-го уровня 102 и передаточные схемы N-го уровня 103 выводят соответственно первый тактовый сигнал CKN1 и второй тактовый сигнал CKN2. После вывода тактовых сигналов понижающие схемы N-го уровня 104 снижают уровень напряжения точки сигнала затвора N-го уровня Q(N) до уровня низкого напряжения. Схемы удержания пониженного напряжения N-го уровня 103 поддерживают уровень напряжения точки сигнала затвора N-го уровня Q(N) и горизонтальной шины сканирования N-го уровня G(N) на уровне низкого напряжения.

В отличие от существующей технологии, два тактовых сигнала, имеющих разную ширину импульсов, вводятся в повышающие схемы N-го уровня и передаточные схемы N-го уровня, так что выходные сигналы могут быть отделены от передаточных сигналов. Поэтому уровень напряжения точки Q(N) повышается до более высокого уровня высокого напряжения. Задержка выходных сигналов снижается, и лучшая зарядка шин сканирования в схеме GOA обеспечивается для обеспечения нормальной работы для каждой точки в цепи.

См. фиг. 3, схематическую диаграмму, иллюстрирующую конкретное соединение схемы блока GOA второго варианта осуществления схемы GOA согласно изобретению. Блоки GOA N-го уровня содержат схемы управления повышением N-го уровня 301, повышающие схемы N-го уровня 302, передаточные схемы N-го уровня 303, понижающие схемы N-го уровня 304 и схемы удержания пониженного напряжения N-го уровня 305. Повышающие схемы N-го уровня 302 и схемы удержания пониженного напряжения N-го уровня 305 подсоединяются соответственно к точке сигнала затвора N-го уровня Q(N) и горизонтальной шине сканирования N-го уровня G(N). Схемы управления повышением N-го уровня 301, понижающие схемы N-го уровня 304 и передаточные схемы N-го уровня 303 подсоединяются к точке сигнала затвора N-го уровня Q(N). Повышающие схемы N-го уровня 302 и передаточные схемы N-го уровня включаются, когда Q(N) находится на уровне высокого напряжения, и принимают соответственно первый тактовый сигнал CKN1 и второй тактовый сигнал CKN2 и выводят сигналы. Ширина импульса второго тактового сигнала CKN2 больше, чем ширина импульса первого тактового сигнала CKN1.

Схемы удержания пониженного напряжения N-го уровня 305 содержат:

первый транзистор Т1, имеющий затвор и сток, подсоединенные к постоянному току высокого напряжения Н; второй транзистор Т2, имеющий затвор, подсоединенный к истоку первого транзистора Т1, сток, подсоединенный к постоянному току высокого напряжения Н, и исток, подсоединенный к первой общей точке P(N); третий транзистор ТЗ, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня Q(N), сток, подсоединенный к истоку первого транзистора Т1, и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; четвертый транзистор Т4, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня Q(N), и сток, подсоединенный к общей точке P(N); пятый транзистор Т5, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня Q(N), и сток, подсоединенный к общей точке P(N); шестой транзистор Т6, имеющий затвор, подсоединенный к истоку четвертого транзистора Т4, сток, подсоединенный к истоку пятого транзистора Т5, и исток, подсоединенный к третьему постоянному току низкого напряжения VSS3; седьмой транзистор Т7, имеющий затвор, подсоединенный к истоку четвертого транзистора Т4, и исток, подсоединенный к третьему постоянному току низкого напряжения VSS3; восьмой транзистор Т8, имеющий затвор и сток, подсоединенные к постоянному току высокого напряжения Н; девятый транзистор Т9, имеющий затвор, подсоединенный к истоку восьмого транзистора Т8, сток, подсоединенный к постоянному току высокого напряжения Н, и исток, подсоединенный к истоку пятого транзистора Т5; десятый транзистор Т10, имеющий затвор, подсоединенный к общей точке P(N), сток, подсоединенный к точке сигнала затвора N-го уровня Q(N), и исток, подсоединенный ко второму постоянному току низкого напряжения VSS2; и одиннадцатый транзистор Т11, имеющий затвор, подсоединенный к общей точке P(N), сток, подсоединенный к горизонтальной шине сканирования N-го уровня G(N), и исток, подсоединенный ко второму постоянному току низкого напряжения VSS2. Первый постоянный ток низкого напряжения VSS1 больше второго постоянного тока низкого напряжения VSS2, а второй постоянный ток низкого напряжения VSS2 больше третьего постоянного тока низкого напряжения VSS3.

См. фиг. 4, схему для первой временной диаграммы сигналов напряжения для каждой точки блока GOA второго варианта осуществления схемы GOA согласно изобретению. На временной диаграмме сигналов XCKN2 вводится на управляющие электроды понижающих схем N-го уровня. Два периода второго тактового сигнала CKN2 берутся, например, для иллюстрации принципа работы.

В рабочей секции 1, поскольку передаточный сигнал ST(N-1) предыдущего этапа находится на уровне низкого напряжения, выключаются схема управления повышением N-го уровня 301 и передаточная схема N-го уровня. Т3, Т4 и Т5 также выключаются в это время. Однако, из-за того, что Т1 и Т2 включаются и вводится сигнал Н, общая точка P(N) находится на уровне высокого напряжения, так что Т10 и Т11 включаются, чтобы понизить соответственно уровень напряжения точки сигнала затвора N-го уровня Q(N) и горизонтальной шины сканирования N-го уровня G(N).

В рабочей секции 2 меняется только первый тактовый сигнал CKN1, а другие тактовые сигналы и передаточные сигналы не меняются. Однако, из-за того, что повышающие схемы N-го уровня выключаются, уровни напряжения других точек не меняются.

В рабочей секции 3 передаточный сигнал ST(N-1) предыдущего этапа находится на уровне высокого напряжения. Включены схемы управления повышением N-го уровня 301. Уровень напряжения точки сигнала затвора N-го уровня Q(N) повышается. Общая точка P(N) понижается до уровня низкого напряжения. Включены повышающие схемы N-го уровня 302 и передаточные схемы N-го уровня. G(N) и CKN1 являются одинаковыми. ST(N) и CKN2 являются одинаковыми.

В рабочей секции 4, из-за ускоряющего конденсатора Cb, точка сигнала затвора N-го уровня Q(N) продолжает поддерживать высокий уровень напряжения. G(N) и CKN1 являются одинаковыми. ST(N) и CKN2 являются одинаковыми.

В рабочей секции 5 второй тактовый сигнал CKN2 меняется на высокий уровень напряжения, и выводятся передаточные сигналы N-го уровня ST(N) уровня высокого напряжения. Уровень напряжения точки сигнала затвора N-го уровня Q(N) повышается до более высокого уровня через конденсатор Cb, чтобы обеспечить свободный выход для повышающих схем N-го уровня 302 и передаточных схем 303.

В рабочей секции 6 уровень напряжения точки сигнала затвора N-го уровня Q(N) повышается до еще более высокого уровня. CKN1 переходит на уровень высокого напряжения. Горизонтальная шина сканирования N-го уровня G(N) успешно выдает сигнал уровня высокого напряжения.

В рабочей секции 7 XCKN2 переходит на уровень высокого напряжения. Уровень напряжения точки сигнала затвора N-го уровня Q(N) снижается. Повышающие схемы N-го уровня 302 и передаточные схемы N-го уровня 303 выключены. Горизонтальная шина сканирования N-го уровня G(N) и передаточный сигнал ST(N) находятся на уровне низкого напряжения.

В рабочей секции 8 уровень напряжения каждой точки аналогичен уровню в рабочей секции 7. Каждый вывод поддерживается на уровне низкого напряжения.

В вышеописанном варианте осуществления третий тактовый сигнал XCNK2 вводится на управляющие электроды понижающих схем N-го уровня.

Скважность первого тактового сигнала CKN1 меньше 50%, а время пуска уровня высокого напряжения первого тактового сигнала CKN1 является таким же, как и время пуска уровня высокого напряжения второго тактового сигнала CKN2; причем уровень высокого напряжения третьего тактового сигнала XCNK2 соответствует уровню низкого напряжения второго тактового сигнала CKN2, а уровень низкого напряжения третьего тактового сигнала XCNK2 соответствует уровню высокого напряжения второго тактового сигнала CKN2.

См. фиг. 5, схему для второй временной диаграммы сигналов напряжения для каждой точки блока GOA второго варианта осуществления схемы GOA согласно изобретению.

Вторая временная диаграмма аналогична первой временной диаграмме. Разница заключается в том, что фаза первого тактового сигнала CKN1 сдвигается влево на 1/4 периода, так что уровень напряжения точки сигнала затвора N-го уровня Q(N) немного уменьшается. Горизонтальная шина сканирования N-го уровня G(N) выводит сигналы в рабочей секции 5.

В вышеописанном варианте осуществления третий тактовый сигнал XCNK2 вводится на управляющие электроды понижающих схем N-го уровня. Скважность первого тактового сигнала меньше 50%, а время окончания уровня высокого напряжения первого тактового сигнала CKN1 является таким же, как и время окончания уровня высокого напряжения второго тактового сигнала CKN2; причем уровень высокого напряжения третьего тактового сигнала XCNK2 соответствует уровню низкого напряжения второго тактового сигнала CKN2, а уровень низкого напряжения третьего тактового сигнала XCNK2 соответствует уровню высокого напряжения второго тактового сигнала CKN2.

Конечно, время пуска и время окончания уровня высокого напряжения первого тактового сигнала CKN1 могут не быть такими же, как время пуска и время окончания уровня высокого напряжения второго тактового сигнала CKN2. Интервал уровня высокого напряжения первого тактового сигнала CKN1 может находиться в интервале уровня высокого напряжения второго тактового сигнала CKN2.

См. фиг. 6, схематическую диаграмму, иллюстрирующую конкретное соединение схемы блока GOA третьего варианта осуществления схемы GOA согласно изобретению. Разница между этим вариантом осуществления и вторым вариантом осуществления заключается в том, что схемы удержания пониженного напряжения N-го уровня 605 не содержат седьмого транзистора Т7 и восьмого транзистора Т8. Затвор девятого транзистора Т9 подсоединен к общей точке P(N). Вариант осуществления убирает два тонкопленочных транзистора, и схема упрощается. Потребляемая мощность снижается.

См. фиг. 7, схематическую диаграмму, иллюстрирующую конкретное соединение схемы блока GOA четвертого варианта осуществления схемы GOA согласно изобретению. Разница между этим вариантом осуществления и третьим вариантом осуществления заключается в том, что схемы удержания пониженного напряжения N-го уровня 705 не содержат пятого транзистора Т5. Сток шестого транзистора Т6 и исток девятого транзистора Т9 подсоединены к истоку четвертого транзистора Т4, а затвор шестого транзистора Т6 и затвор седьмого транзистора Т7 подсоединены к точке сигнала затвора N-го уровня Q(N).

См. фиг. 8, схематическую диаграмму, иллюстрирующую конкретное соединение схемы блока GOA пятого варианта осуществления схемы GOA согласно изобретению. Разница между этим вариантом осуществления и четвертым вариантом осуществления заключается в том, что схемы удержания пониженного напряжения N-го уровня 805 не содержат седьмого транзистора Т7 и восьмого транзистора Т8. Затвор девятого транзистора Т9 подсоединен к затвору второго транзистора Т2. В этом варианте осуществления существующие ключевые точки схемы являются сигналами для уменьшения соединения сигналов постоянного тока высокого напряжения Н, и, таким образом, схема упрощается.

См. фиг. 9, схематическую диаграмму, иллюстрирующую конкретное соединение схемы блока GOA шестого варианта осуществления схемы GOA согласно изобретению. Этот вариант осуществления является вариантом пятого варианта осуществления. Принцип аналогичен.

В различных вариантах осуществления, упомянутых выше, ускоряющий конденсатор Cb в передаточных схемах N-го уровня может быть удален.

В первом варианте осуществления жидкокристаллического дисплея настоящего изобретения жидкокристаллический дисплей содержит схемы GOA различных вариантов осуществления, упомянутых выше.

Хотя настоящее изобретение проиллюстрировано и описано со ссылкой на конкретные варианты осуществления, специалисты в данной области поймут, что многие варианты и модификации легко достижимы без отступления от его сущности и объема, как определено прилагаемой формулой изобретения и ее юридическими эквивалентами.