Результат интеллектуальной деятельности: КОРПУСИРОВАННАЯ ИНТЕГРАЛЬНАЯ СХЕМА, СОДЕРЖАЩАЯ СОЕДИНЕННЫЙ ПРОВОЛОЧНЫМИ ПЕРЕМЫЧКАМИ МНОГОКРИСТАЛЬНЫЙ ПАКЕТ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Варианты настоящего изобретения в общем относятся к области интегральных схем и, более конкретно, к корпусированной интегральной схеме, содержащей соединенный проволочными перемычками многокристальный пакет.

Уровень техники

Плотность размещения вводов/выводов кристаллов интегральных схем, таких как процессоры, постоянно растет, тогда как размеры этих кристаллов уменьшаются. В такой ситуации может быть желательно уменьшить длины соединений между кристаллами в корпусированной многокристальной схеме и сохранить при этом небольшой коэффициент формы, но это создает проблемы с точки зрения технологии.

Приведенное здесь описание имеет целью в общем представить контекст настоящего изобретения. Если здесь не указано иначе, материалы, описываемые в этом разделе, не являются изложением известного состояния техники применительно к Формуле изобретения и не считаются характеристиками этого известного состояния только в результате включения этих материалов в настоящий раздел.

Краткое описание чертежей

Варианты будут легко понятны из следующего подробного описания в сочетании с прилагаемыми чертежами. Для улучшения описания подобные цифровые позиционные обозначения присвоены подобным структурным элементам. Варианты настоящего изобретения иллюстрированы примерами и, не в качестве ограничений, изображениями на прилагаемых чертежах. Если четко не указано иное, эти чертежи выполнены не в масштабе.

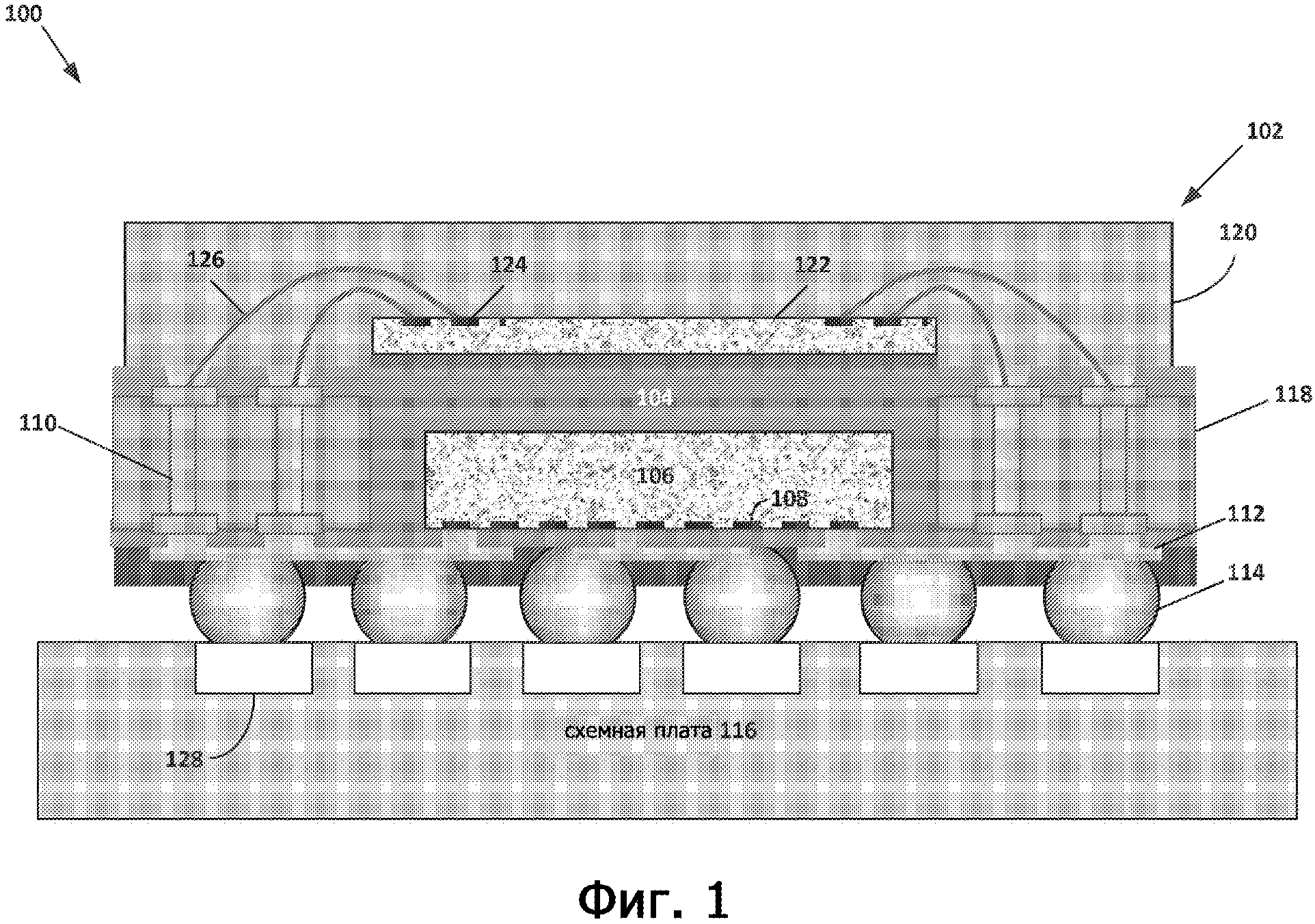

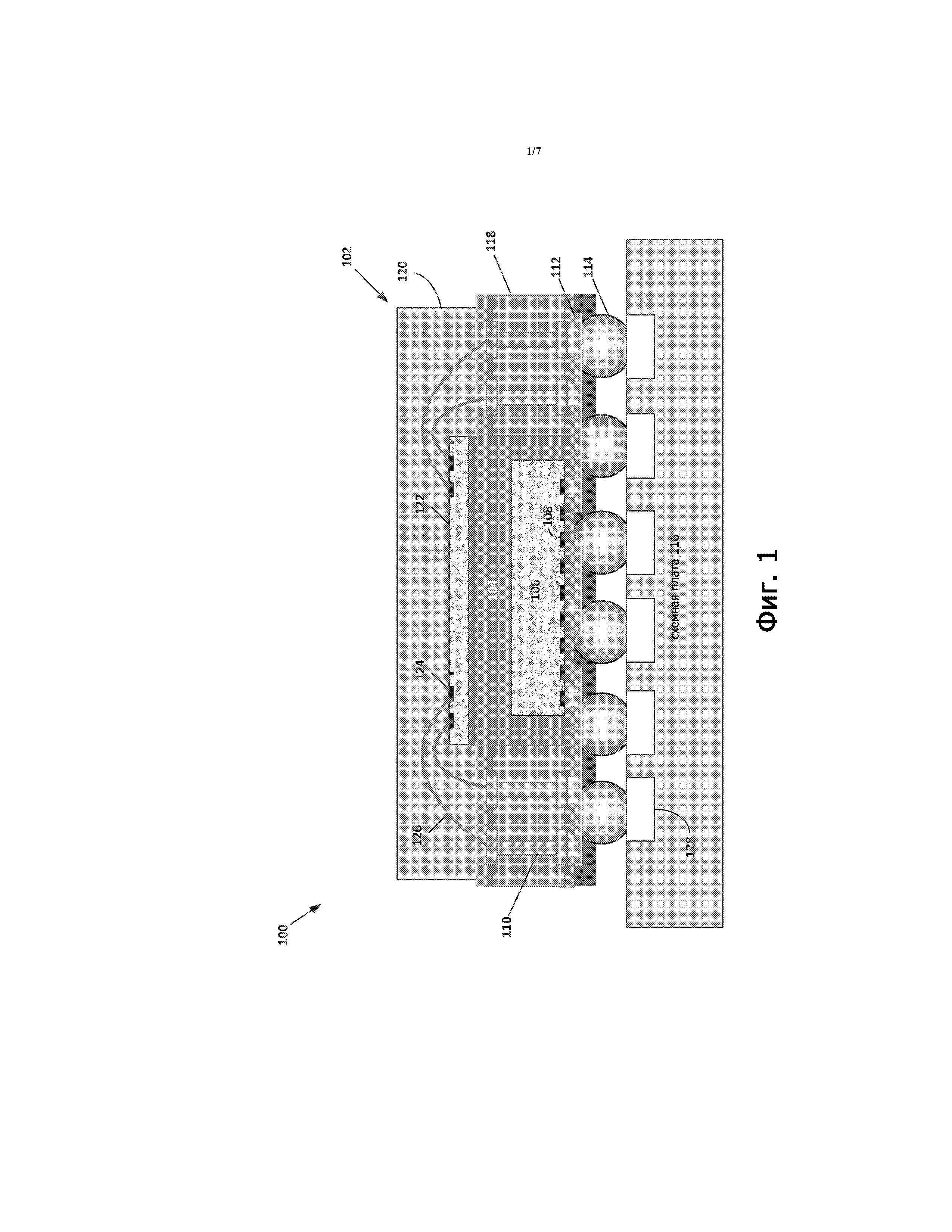

Фиг. 1 упрощенно иллюстрирует вид сбоку в разрезе примера сборки интегральной схемы (IC), представляющей собой корпусированную интегральную схему, имеющую соединенный проволочными перемычками многокристальный пакет.

Фиг. 2 представляет иллюстративную логическую схему процесса изготовления корпусированной интегральной схемы согласно некоторым вариантам настоящего изобретения.

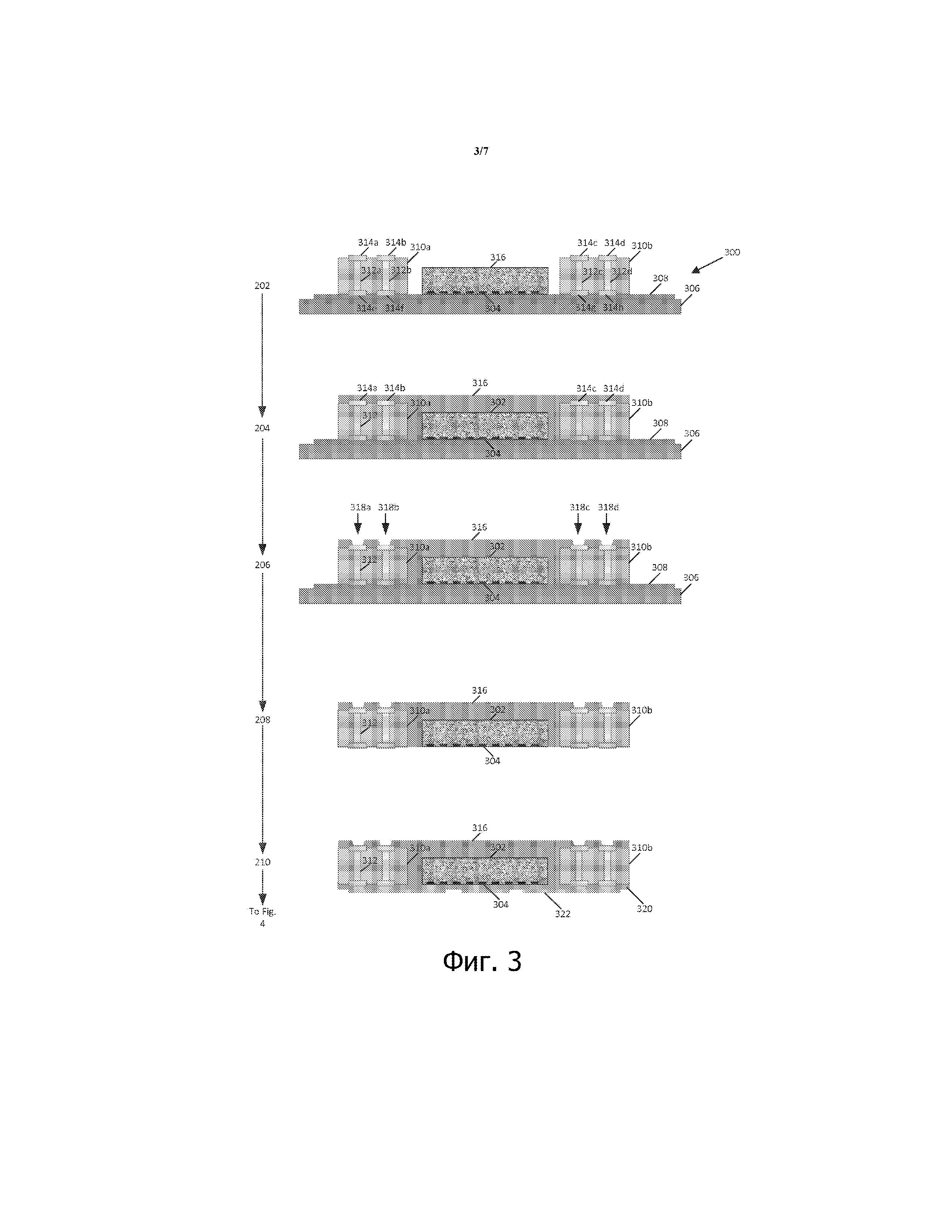

Фиг. 3 – 4 показывают иллюстративный вид сбоку в разрезе для представления выбранных операций, иллюстрирующих этапы процесса изготовления корпусированной интегральной схемы, согласно некоторым вариантам настоящего изобретения.

Фиг. 5 упрощенно иллюстрирует вид сбоку в разрезе примера сборки интегральной схемы с соединительными структурами на уровне корпуса согласно различным вариантам настоящего изобретения.

Фиг. 6 упрощенно иллюстрирует вид сбоку в разрезе примера сборки интегральной схемы, имеющей соединительные структуры на уровне корпуса и третий кристалл, расположенный на перераспределительном слое (RDL), согласно различным вариантам настоящего изобретения.

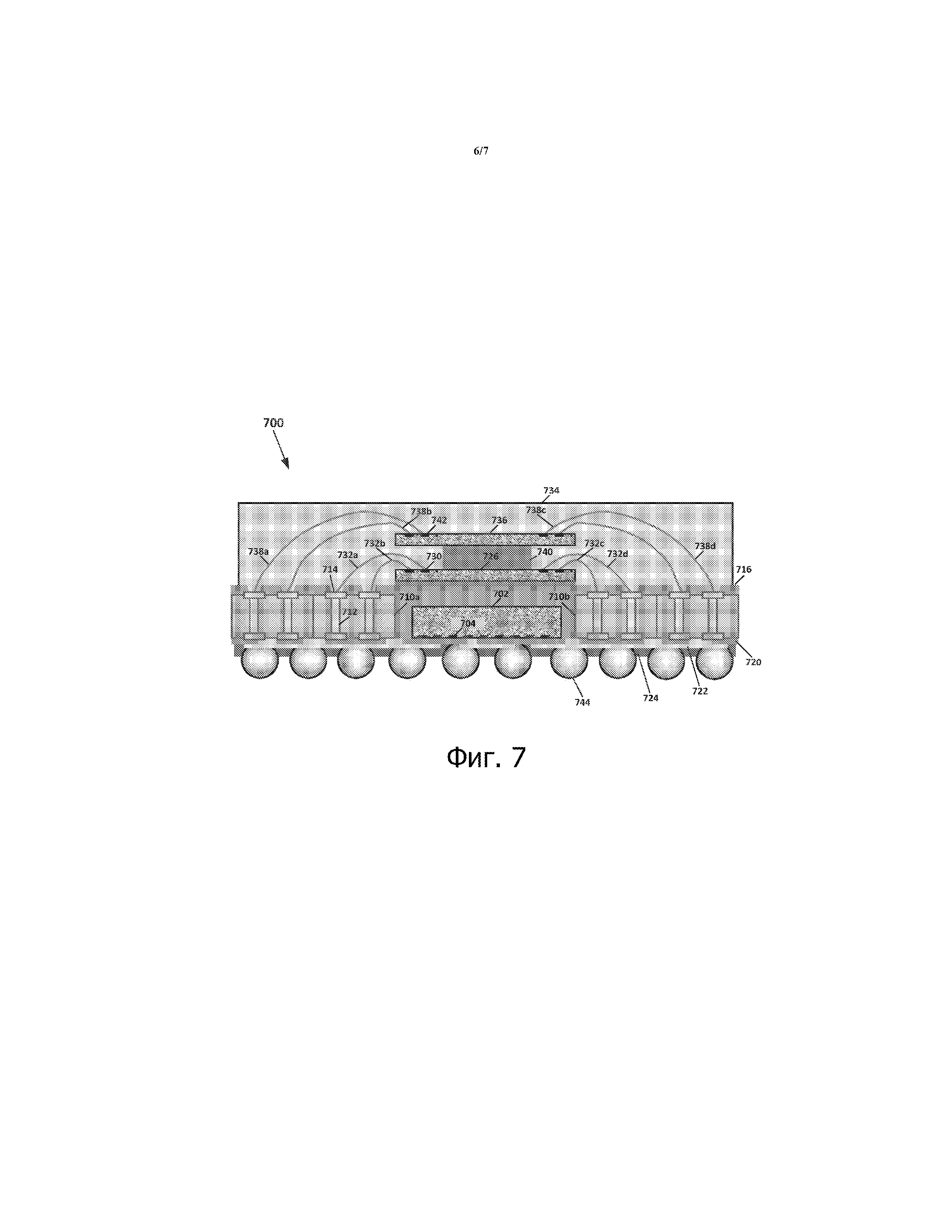

Фиг. 7 упрощенно иллюстрирует вид сбоку в разрезе примера сборки интегральной схемы, имеющей дополнительный кристалл, установленный в пакет и соединенный проволочными перемычками, согласно различным вариантам настоящего изобретения.

Фиг. 8 упрощенно иллюстрирует компьютерное устройство, содержащее корпусированную интегральную схему, согласно различным вариантам настоящего изобретения.

Осуществление изобретения

Варианты настоящего изобретения описывают конфигурации корпусированной интегральной схемы (IC), содержащей соединенный проволочными перемычками многокристальный пакет. В последующем описании различные аспекты иллюстративных вариантов будут рассмотрены с использованием терминов, обычно применяемых специалистами в рассматриваемой области, чтобы сообщить существо своих работ другим специалистам в этой области. Однако специалистам в рассматриваемой области должно быть ясно, что варианты настоящего изобретения могут быть практически осуществлены с использованием только некоторых из описываемых аспектов. В настоящем разъяснении приведены конкретные числа, материалы и конфигурации для обеспечения полного понимания иллюстративных вариантов. Однако специалистам в рассматриваемой области также должно быть ясно, что варианты настоящего изобретения могут быть практически осуществлены и без указанных конкретных подробностей. В других случаях, хорошо известные признаки опущены или упрощены с целью не затенять иллюстративные варианты реализации.

В последующем подробном описании ссылки сделаны на прилагаемые чертежи, которые составляют часть настоящего описания, где подобные цифровые позиционные обозначения присвоены подобным компонентам и где показано на иллюстративных вариантах, как предмет настоящего изобретения может быть практически осуществлен. Следует понимать, что могут быть использованы и другие варианты, а также могут быть сделаны структурные или логические изменения, не отклоняясь от объема настоящего изобретения. Поэтому последующее подробное описание не следует рассматривать в ограничительном смысле, так что объем этих вариантов определен прилагаемой формулой изобретения и ее эквивалентами.

В целях настоящего изобретения фраза «A и/или B» означает (A), (B) или (A и B). В целях настоящего изобретения фраза «A, B и/или C» означает (A), (B), (C), (A и B), (A и C), (B и C) или (A, B и C).

Описание может использовать термины на основе перспективы, такие как верх/низ, в/из, над/под и т.д. Такие характеристики применяются просто для способствования обсуждению и не предназначены для ограничения применения описываемых здесь вариантов какой-либо конкретной ориентацией.

Описание может использовать фразы «в одном из вариантов» или «в вариантах», каждая из которых может ссылаться на один и тот же или несколько разных вариантов. Кроме того, термины «содержащий», «включающий», «имеющий» и другие подобные термины, как они используются здесь применительно к вариантам настоящего изобретения, являются синонимами.

Здесь может быть использован термин «соединен с» вместе с его производными. Термин «соединенные» может иметь одно или несколько из следующих значений. Термин «соединенные» может означать, что два или более элементов находятся в прямом физическом или электрическом контакте. Однако термин «соединенные» может также означать, что два или более элементов могут не иметь прямого контакта один с другим, но тем не менее могут кооперироваться или взаимодействовать один с другим, и может также означать, что имеются один или несколько других элементов, связанных или присоединенных между элементами, которые названы соединенными один с другим. Термин «прямо соединенные» может означать, что два или несколько элементов находятся в непосредственном контакте.

В различных вариантах фраза «первый элемент, созданный, нанесенный или иным способом расположенный на втором элементе» может означать, что первый элемент создан, нанесен или расположен (помещен) на втором элементе, и что по меньшей мере часть первого элемента может быть в прямом, непосредственном контакте (например, в прямом физическом и/или электрическом контакте) или непрямом контакте (например, с наличием одного или нескольких других элементов между первым элементом и вторым элементом) по меньшей мере с частью второго элемента.

Как используется здесь, термин «модуль» может относиться к, быть частью или включать специализированную интегральную схему (ASIC), электронную схему, систему на кристалле (SoC), процессор (совместно используемый, выделенный или группу процессоров) и/или запоминающее устройство (совместно используемое, выделенное или группу запоминающих устройств), выполняющие одну или несколько программ загружаемого или встроенного программного обеспечения, схему комбинаторной логики и/или другие подходящие аппаратные компоненты, обеспечивающие выполнение описываемых функций

Фиг. 1 упрощенно иллюстрирует вид сбоку в разрезе примера интегральной схемы (IC) в сборе, представляющей собой корпусированную интегральную схему 102, электрически и физически соединенную со схемной платой 116, согласно вариантам настоящего изобретения. В различных вариантах корпусированная интегральная схема (IC) 102 может содержать один или несколько кристаллов интегральных схем (например, первый кристалл 106). Первый кристалл 106 может быть по меньшей мере частично погружен в первый герметизирующий слой 104. Этот первый кристалл 106 может содержать несколько соединительных структур на уровне кристалла (например, соединительную структуру 108 на уровне кристалла), которые могут быть расположены на первой стороне первого герметизирующего слоя 104.

Корпусированная интегральная схема (IC) 102 может также содержать несколько электрических маршрутных элементов (например, электрический маршрутный элемент 110), по меньшей мере частично погруженных в первый герметизирующий слой 104. Эти несколько электрических маршрутных элементов могут быть конфигурированы для маршрутизации электрических сигналов между второй стороной первого герметизирующего слоя 104 и первой стороной этого первого герметизирующего слоя 104, противоположной первой стороне, как можно видеть. В некоторых вариантах электрические маршрутные элементы могут, как это изображено на чертежи, представлять собой сквозные штырьки, выполненные в толще электроизоляционного материала (например, электроизоляционного материала 118). Совокупность таких электроизоляционных материалов может содержать кремний, керамику, полимер или какой-либо другой подходящий материал, где эти материалы могут содержать или не содержать наполнитель (например, наполнитель из оксида кремния или какой-либо другой подходящий наполнитель).

Корпусированная IC 102 может дополнительно содержать второй кристалл 122 интегральной схемы, расположенный на второй стороне первого герметизирующего слоя 104 и по меньшей мере частично погруженный во второй герметизирующий слой 120. Второй кристалл 122 интегральной схемы может также иметь вторую группу из нескольких соединительных структур на уровне кристалла (например, соединительную структуру 124 на уровне кристалла). Несколько соединительных структур второй группы на уровне кристалла могут быть электрически соединены с электрическими маршрутными элементами посредством проволочных перемычек (например, проволочной перемычкой 126).

В некоторых вариантах корпусированная IC 102 может содержать перераспределительный слой 112. Этот перераспределительный слой 112 может быть конфигурирован для электрического соединения кристалла 106 и кристалла 122, посредством электрических маршрутных элементов, с одной или несколькими соединительными структурами на уровне корпуса (например, припойными шариковыми выводами 114). Эти соединительные структуры на уровне корпуса могут быть конфигурированы для электрического и физического соединения корпусированной IC 102 со схемной платой 116. Корпусированная IC 102 может быть соединена со схемной платой 116 в соответствии с несколькими подходящими конфигурациями, включая эластомерную конфигурацию или какую-либо другую подходящую конфигурацию. Хотя здесь показаны припойные шариковые выводы 114, соединительные структуры на уровне корпуса могут представлять собой столбики или другие подходящие структуры вместо или в дополнение к припойным шариковым выводам, которые могут электрически соединять корпусированную IC 102 со схемной платой 116 через одну или несколько контактных площадок (например, контактную площадку 128), расположенных на схемной плате. Корпусированная IC 102 может представлять собой дискретный кристалл (чип) из полупроводникового материала и может в некоторых вариантах содержать или быть частью процессора, запоминающего устройства или специализированной схемы. В некоторых вариантах корпусированная IC 102 может представлять собой корпусированный прибор, изготовленный по технологии встроенных приборов с матрицей шариковых выводов на уровне пластины (eWLB).

Схемная плата 116 может содержать электрические маршрутные элементы, конфигурируемые для маршрутизации электрических сигналов к и от корпусированной IC 102. К таким электрическим маршрутным элементам могут относиться, например, дорожки на одной или нескольких поверхностей схемной платы и/или внутренние маршрутные элементы, такие как, например, канавки, сквозные отверстия или другие соединительные структуры, через которые происходит маршрутизация электрических сигналов.

Схемная плата 116 может представлять собой печатную плату (PCB), выполненную из электроизоляционного материала, такого как слоистый материал на основе эпоксидной смолы. Например, схемная плата 116 может содержать электроизоляционные слои, выполненные из таких материалов, как, например, политетрафторэтилен, материалы на основе хлопковой бумаги с пропиткой фенольной смолой, такие как Замедлитель пламени (Flame Retardant 4 (FR-4)), FR-1, бумаги на основе хлопковой бумаги и эпоксидной смолы, такие как CEM-1 или CEM-3, или тканые стекловолокнистые материалы, ламинированные один на другом с использованием препрега из эпоксидной смолы. Схемная плата 116 в других вариантах может быть изготовлена из других подходящих материалов. В некоторых вариантах схемная плата 116 может представлять собой материнскую плату (например, материнскую плату 802, показанную на фиг. 8).

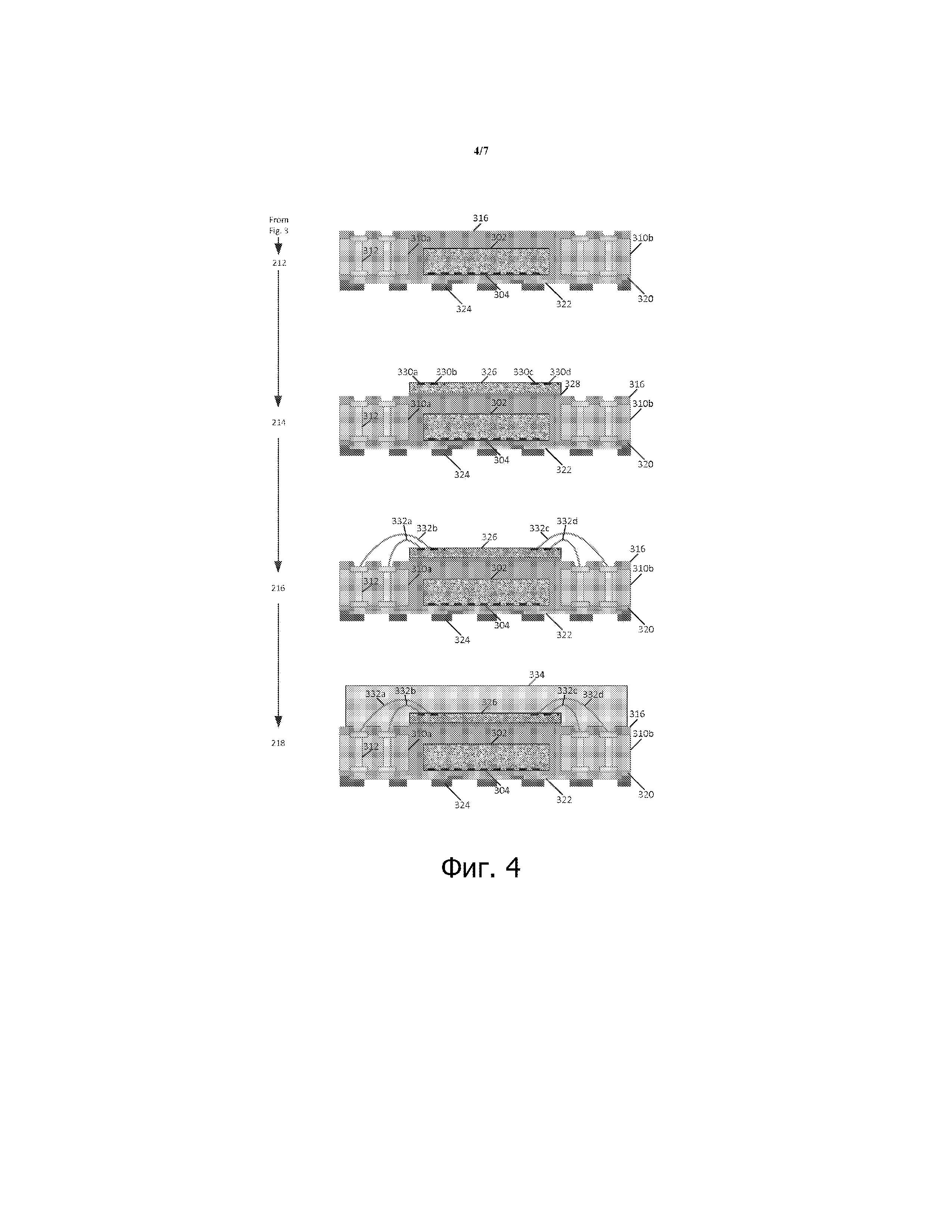

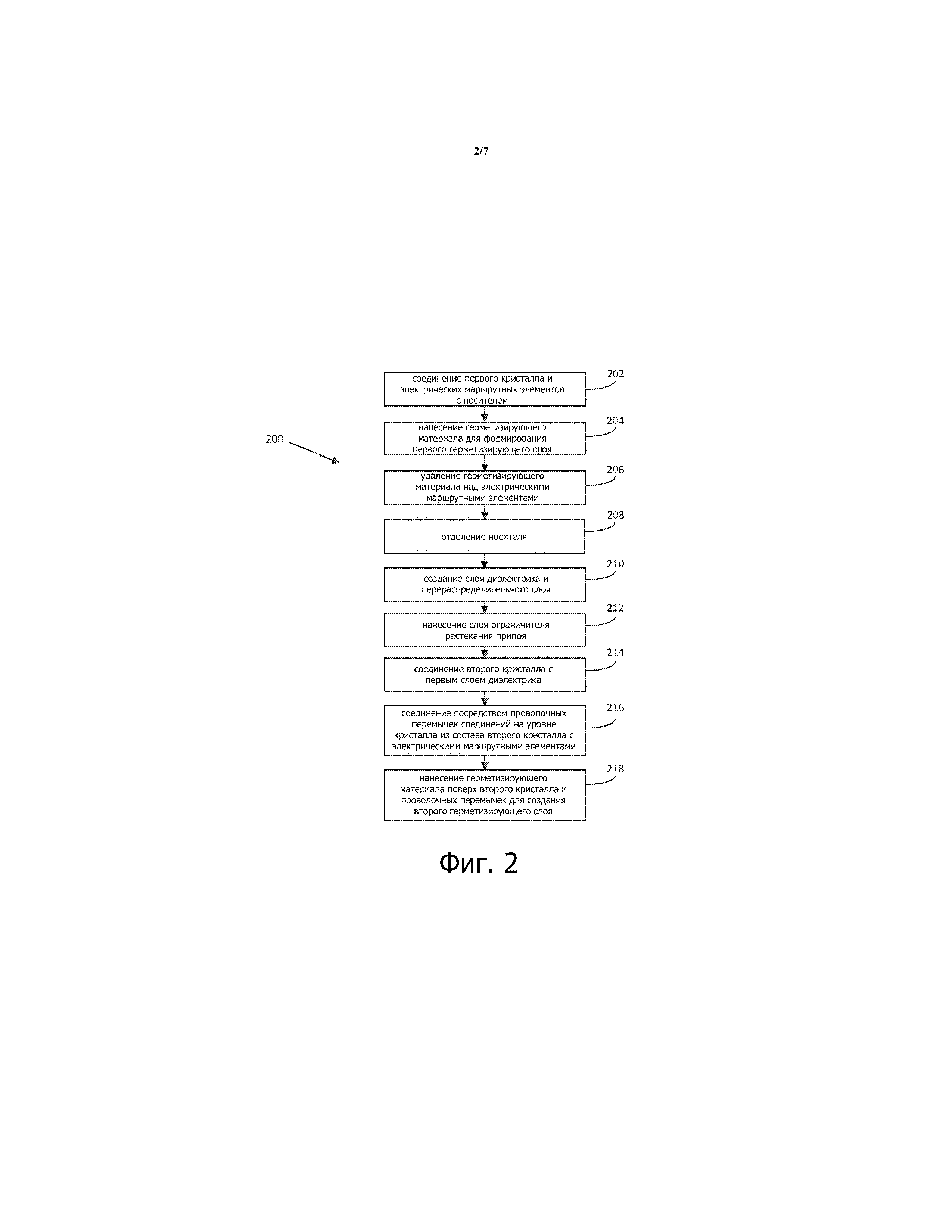

Фиг. 2 иллюстрирует способ 200 изготовления корпусированной интегральной схемы (IC) применительно к иллюстративной корпусированной IC (например, корпусированной интегральной схеме (IC) 102, показанной на фиг. 1) согласно различным вариантам настоящего изобретения. Фиг. 3 – 4 представляют виды сбоку в разрезе для иллюстраций выбранных операций, иллюстрирующих этапы процесса 200 изготовления корпусированной IC, согласно иллюстративному варианту. Поэтому фиг. 2-4 будут рассмотрены в связи один с другими. В помощь этому описанию операции, изображенные на фиг. 2, обозначены стрелками, показывающими переход от одного этапа к другому на фиг. 3 и 4. Кроме того, на иллюстрациях операций, представленных на фиг. 3-4, проставлены не все цифровые позиционные обозначения, чтобы не усложнять чертежи.

Способ 200 изготовления IC может начинаться с блока 202, где активная сторона первого кристалла 302 может быть соединена с носителем 306. Это может быть сделано с использованием ленты или клея (например, клея 308), нанесенного на носитель 306. Как показано на чертеже, на активной стороне кристалла 302 могут располагаться несколько соединительных структур на уровне кристалла (например, соединительных структур 304 на уровне кристалла). В некоторых вариантах с носителем 306 могут быть также соединены несколько электрических маршрутных элементов 312a-312d, в дальнейшем совместно именуемых электрическими маршрутными элементами 312. В таких вариантах указанные несколько электрических маршрутных элементов могут представлять собой, как показано на чертеже, сквозные штырьки, выполненные в сквозных отверстиях, созданных в электроизоляционном материале 310a и 310b. Этот электроизоляционный материал может представлять собой какой-либо подходящий материал, включая, не ограничиваясь этим, кремний, керамику, полимерный материал, стекло и т.п. Указанные электрические маршрутные элементы могут, в некоторых вариантах, иметь несколько контактных площадок 314a-h, расположенных на каждом конце электрических маршрутных элементов 312a-d. В некоторых вариантах по меньшей мере на контактных площадках 314a-d могут быть созданы поверхности, обеспечивающие монтаж проволочных перемычек. Такие поверхности для монтажа проволочных перемычек могут содержать никель, золото или какой-либо другой подходящий материал или сочетание таких материалов. В других вариантах электрические маршрутные элементы могут быть созданы посредством отдельных процедур после формирования первого герметизирующего слоя 316, обсуждаемого ниже со ссылками на блок 204. Такие электрические маршрутные элементы могут быть выполнены из электропроводного материала (например, меди).

В блоке 204 для формирования первого герметизирующего слоя 316 может быть осажден герметизирующий материал. В некоторых вариантах такой герметизирующий материал может представлять собой литьевой компаунд (например, эпоксидную смолу). В таких вариантах первый герметизирующий слой 316 может быть выполнен, например, способом прямого прессования. Как показано на чертеже, первый герметизирующий слой 316 может герметизировать по меньшей мере часть первого кристалла 302 и электрические маршрутные элементы 312.

В некоторых вариантах первый герметизирующий слой 316 может также герметизировать контактные площадки 314a-d. В таких вариантах в блоке 206 какой-либо герметизирующий материал, который мог быть нанесен поверх контактных площадок 314a-d, может быть удален для образования пустот 318a-d. Это может быть сделано посредством сверления (например, лазерного «сверления»), шлифования, травления и т.п. В вариантах, использующих лазерное «сверление», такое лазерное воздействие может вызвать деградацию или разрушение покрытия для монтажа проволочных перемычек, нанесенного на контактные площадки 314a-d. В таких вариантах покрытие на поверхность (например, никель, золото или какой-либо другой подходящий материал) может быть нанесено после лазерного «сверления». Такое поверхностное покрытие может быть нанесено, например, посредством химического восстановления.

В блоке 208, носитель 306 может быть отделен от первого герметизирующего слоя 316. В некоторых вариантах, обсуждавшиеся выше процедуры могут быть осуществлены отдельно от процедур, описываемых далее. В таких вариантах процедура может начинаться с создания сборки с корпусированной IC аналогично сборке, создаваемой в ходе описанного выше процесса. В таких вариантах поверх сборки с корпусированной IС может быть нанесен пассивационный слой для предотвращения оксидирования или загрязнения каких-либо открытых металлических элементов, таких как контактные площадки 314a-h и несколько соединений первого кристалла 302 на уровне этого кристалла. Такой пассивационный слой может быть нанесен способом ламинирования, печати или центробежным способом на центрифуге, например. После нанесения пассивационного слоя в этом пассивационном слое могут быть созданы пустоты (например, посредством фотолитографии) для осуществления процедур, описываемых ниже.

В блоке 210 может быть создан слой 320 диэлектрик. Такой слой диэлектрика может, в некоторых вариантах, представлять собой пассивационный слой, обсуждавшийся выше применительно к блоку 208. Кроме того на поверхности слоя 320 диэлектрика может быть выполнен перераспределительный слой (RDL) 322. Слой RDL 320 может обеспечить отведение и перераспределение сигнала от соединений на уровне кристалла (например, соединения 304 на уровне кристалла) и от электрических маршрутных элементов 312. Хотя на чертеже показан только один слой RDL, должно быть понятно, что могут быть созданы и дополнительные слои RDL и соответствующие слои диэлектрика в зависимости от конкретного применения и конструкции, требованиям которых должна удовлетворять полученная в результате корпусированная IC. В блоке 212, переходя к фиг. 4, может быть создан слой 324 ограничителя растекания припоя и в этом слое может быть выполнен заданный рисунок. Такой ограничительный слой может быть выполнен, например, способом фотолитографии.

В блоке 214 обратная сторона второго кристалла 326 может быть соединена со второй стороной первого герметизирующего слоя 316, противоположной слою RDL 322, как можно видеть. Это может быть сделано, например, с использованием ленты или клея (например, клея 328). В различных вариантах второй кристалл 326 может иметь несколько соединений 330a-330d на уровне кристалла, расположенных на поверхности кристалла. Как используется здесь, обратной стороной кристалла является сторона кристалла, на которой нет соединений на уровне кристалла.

В блоке 216, соединения 330a-330d на уровне кристалла в составе второго кристалла 326 могут быть соединены соответствующими проволочными перемычками 332a-332d с электрическими маршрутными элементами 312. Эти электрические маршрутные элементы 312 могут осуществлять маршрутизацию электрических сигналов между вторым кристаллом 326 и слоем RDL. Проволочные перемычки 332a-d могут быть выполнены из какого-либо подходящего материала, включая, не ограничиваясь этим, алюминий, медь, серебро, золото и т.п., и могут также представлять собой многослойные проволочки (например, проволочки с покрытием). Такие проволочные соединения могут быть выполнены с применением какой-либо обычной технологии монтажа проволочных перемычек. В некоторых вариантах на верхнюю поверхность второго кристалла 326 могут быть установлены один или несколько дополнительных кристаллов. В таких вариантах между каждым кристаллом и предшествующим кристаллом может быть помещен разделитель, чтобы можно было вывести проволочные перемычки (например, проволочки 332a-d) из-под кристалла. Такое варианты обсуждается ниже более подробно со ссылками на фиг. 7. В блоке 218 поверх второго кристалла и проволочек 330a-330d может быть нанесен дополнительный герметизирующий материал для образования второго герметизирующего слоя 334 и для защиты конфигурации проволочных перемычек. На фиг. 5-7 показаны различные варианты корпусированных IC, которые могут быть изготовлены в соответствии с описанными выше процедурами.

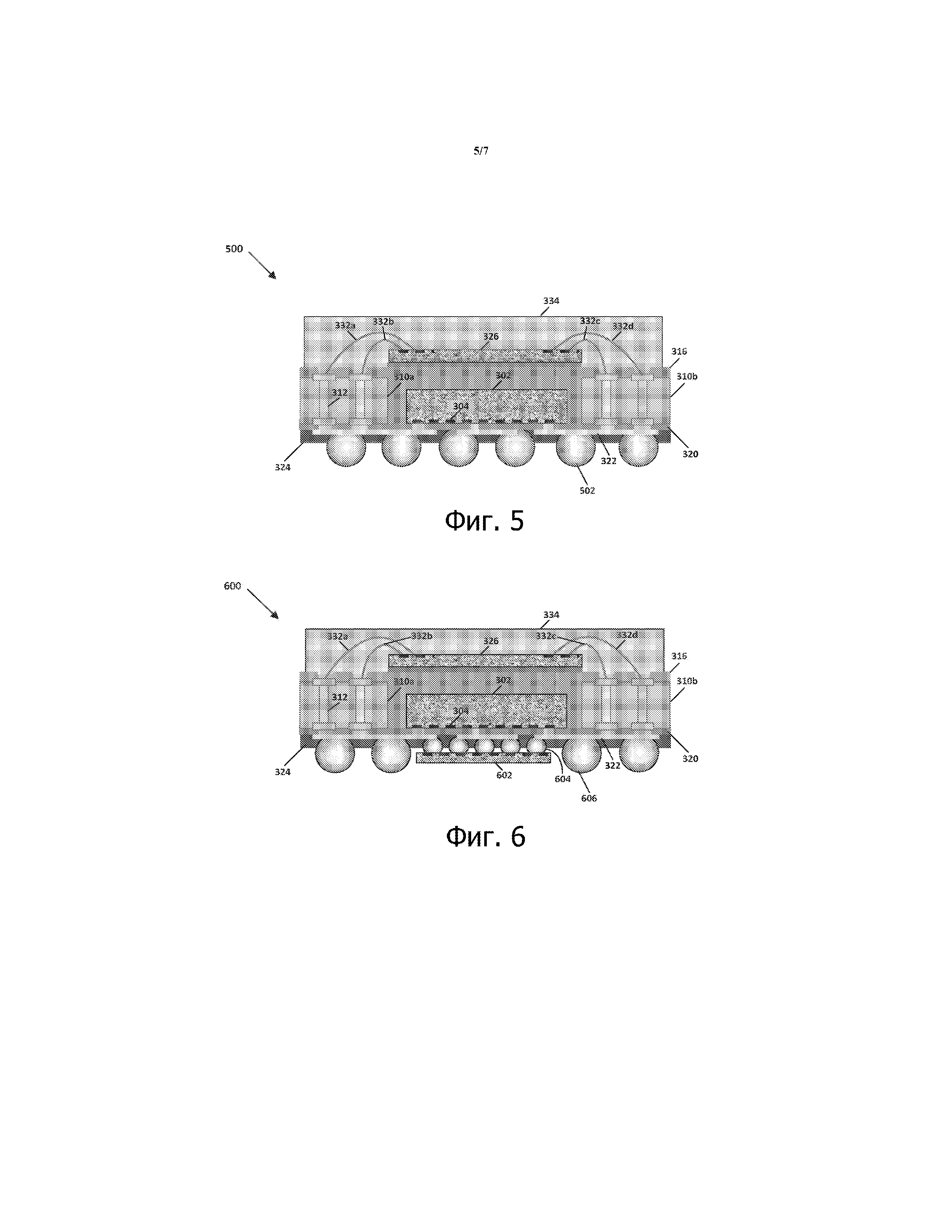

Фиг. 5 упрощенно иллюстрирует вид сбоку в разрезе примера корпусированной интегральной схемы (IC) 500, имеющей соединительные структуры на уровне корпуса, согласно различным вариантам настоящего изобретения. Как показано на чертеже, исходным пунктом для фиг. 5 может быть сборка с корпусированной интегральной схемой (IC), изготовленная посредством процесса, описанного выше со ссылками на фиг. 2-4. На фиг. 5, однако, соединения на уровне корпуса (например, припойные шариковые выводы 502) могут быть расположены на слое RDL. Хотя здесь показаны припойные шариковые выводы, соединительные структуры на уровне корпуса могут представлять столбики или какие-либо другие подходящие структуры вместо или в дополнение к припойным шариковым выводам. Эти соединительные структуры на уровне корпуса могут быть конфигурированы для электрического соединения корпусированной IC 500 со схемной платой (например, схемной платой 116, показанной на фиг. 1).

Фиг. 6 упрощенно иллюстрирует вид сбоку в разрезе примера корпусированной интегральной схемы (IC) 600, имеющей соединительные структуры на уровне корпуса (например, припойные шариковые выводы 606) и третий кристалл 602, встроенный в эту схему, согласно различным вариантам настоящего изобретения. Как показано на чертеже, исходным пунктом для фиг. 6 может быть сборка с корпусированной интегральной схемой (IC), изготовленная посредством процесса, описанного выше со ссылками на фиг. 2-4. На фиг. 6, однако, соединения на уровне корпуса (например, припойные шариковые выводы 606) могут быть расположены на слое RDL. Кроме того, третий кристалл 602 был соединен со сборкой корпусированных IC посредством соединительных структур 604. Хотя здесь показаны припойные шариковые выводы, соединительные структуры на уровне корпуса могут представлять столбики или какие-либо другие подходящие структуры вместо или в дополнение к припойным шариковым выводам. Эти соединения на уровне корпуса могут быть конфигурированы для электрического соединения корпусированной IC 600 со схемной платой (например, схемной платой 116, показанной на фиг. 1). Как можно видеть, суммарная толщина третьего кристалла 602 и соединительных структур 604 меньше толщины индивидуальных соединительных структур на уровне корпуса. Это может позволить расположить третий кристалл 602 в той же плоскости, где находятся несколько соединительных структур на уровне корпуса.

Фиг. 7 упрощенно иллюстрирует вид сбоку в разрезе примера корпусированной интегральной схемы (IC) 700, имеющей дополнительный кристалл 702, установленный сверху на кристалле 326. Как показано на чертеже, корпусированная IC 700 может содержать первый кристалл 702 и несколько электрических маршрутных элементов (например, электрических маршрутных элементов 712), по меньшей мере частично погруженных в первый герметизирующий слой 716. Этот первый герметизирующий слой 716 может быть, например, выполнен из литьевого компаунда. В некоторых вариантах указанные несколько электрических маршрутных элементов могут, как показано, представлять собой сквозные штырьки, выполненные в электроизоляционном материале 710a и 710b. Такой электроизоляционный материал может представлять собой, не ограничиваясь этим, кремний, керамику, полимер и т.п. Указанные электрические маршрутные элементы могут, в некоторых вариантах, иметь несколько контактных площадок (например, контактных площадок 714), расположенных на каждом конце индивидуальных электрических маршрутных элементов. В некоторых вариантах на верхних контактных площадках (например, контактных площадках 714) могут быть созданы поверхности, обеспечивающие монтаж проволочных перемычек. Такие поверхности для монтажа проволочных перемычек могут содержать никель, золото или какой-либо другой подходящий материал или сочетание таких материалов. Такие электрические маршрутные элементы могут быть выполнены из какого-либо электропроводного материала (например, меди).

Корпусированная IC 700 может также содержать перераспределительный слой (RDL) 722. Слой RDL может быть расположен на поверхности слоя диэлектрика 720 и может обеспечить отведение и перераспределение сигнала от соединений на уровне кристалла (например, соединения 704 на уровне кристалла) и от нескольких электрических маршрутных элементов (например, электрических маршрутных элементов 712). Хотя на чертеже показан только один слой RDL, должно быть понятно, что могут быть созданы и дополнительные слои RDL и соответствующие слои диэлектрика в зависимости от конкретного применения и конструкции, требованиям которых должна удовлетворять полученная в результате корпусированная интегральная схем (IC). На поверхности слоя RDL может быть создан слой 724 ограничителя растекания припоя, а в отверстиях этого слоя 724 ограничителя растекания припоя могут быть расположены несколько соединений на уровне корпуса (например, соединений 744 на уровне корпуса).

Корпусированная IC 700 может также содержать второй кристалл 726, который может быть соединен с поверхностью первого герметизирующего слоя 716. Это может быть сделано, например, с использованием ленты или клея (например, клея 728). В различных вариантах второй кристалл 726 может иметь несколько соединений на уровне кристалла (например, соединений на уровне кристалла 730) расположенных на поверхности кристалла. Соединения на уровне кристалла в составе второго кристалла 726 могут быть, как показано на чертеже, соединены соответствующими проволочными перемычками 732a-732d с первой подгруппой электрических маршрутных элементов через соответствующую подгруппу из нескольких контактных площадок. Указанные электрические маршрутные элементы могут осуществлять маршрутизацию электрических сигналов между вторым кристаллом 726 и слоем RDL 722. Проволочные перемычки 732a-d могут быть выполнены из какого-либо подходящего материала, включая, не ограничиваясь этим, алюминий, медь, серебро, золото и т.п. Такие проволочные соединения могут быть выполнены с применением какой-либо обычной технологии монтажа проволочных перемычек. В некоторых вариантах на верхнюю поверхность второго кристалла 726 могут быть установлены один или несколько дополнительных кристаллов (например, третий кристалл 736). В таких вариантах между соседними кристаллами может быть помещен разделитель (например, разделитель 740), чтобы можно было вывести проволочные перемычки (например, проволочки 732a-d) из-под кристалла. В различных вариантах третий кристалл 726 может иметь несколько соединений на уровне кристалла (например, соединений 742 на уровне кристалла), расположенных на поверхности кристалла. Соединения на уровне кристалла в составе второго кристалла 726 могут быть, как показано на чертеже, соединены соответствующими проволочными перемычками 738a-738d со второй подгруппой электрических маршрутных элементов через соответствующую вторую подгруппу из нескольких контактных площадок. Второй кристалл 726, третий кристалл 736 и проволочные перемычки 732a-d и 738a-d могут быть все погружены во второй герметизирующий слой 734. В некоторых вариантах со слоем RDL 722 может быть соединен четвертый кристалл в конфигурации, аналогичной кристаллу 602, показанному на фиг. 6.

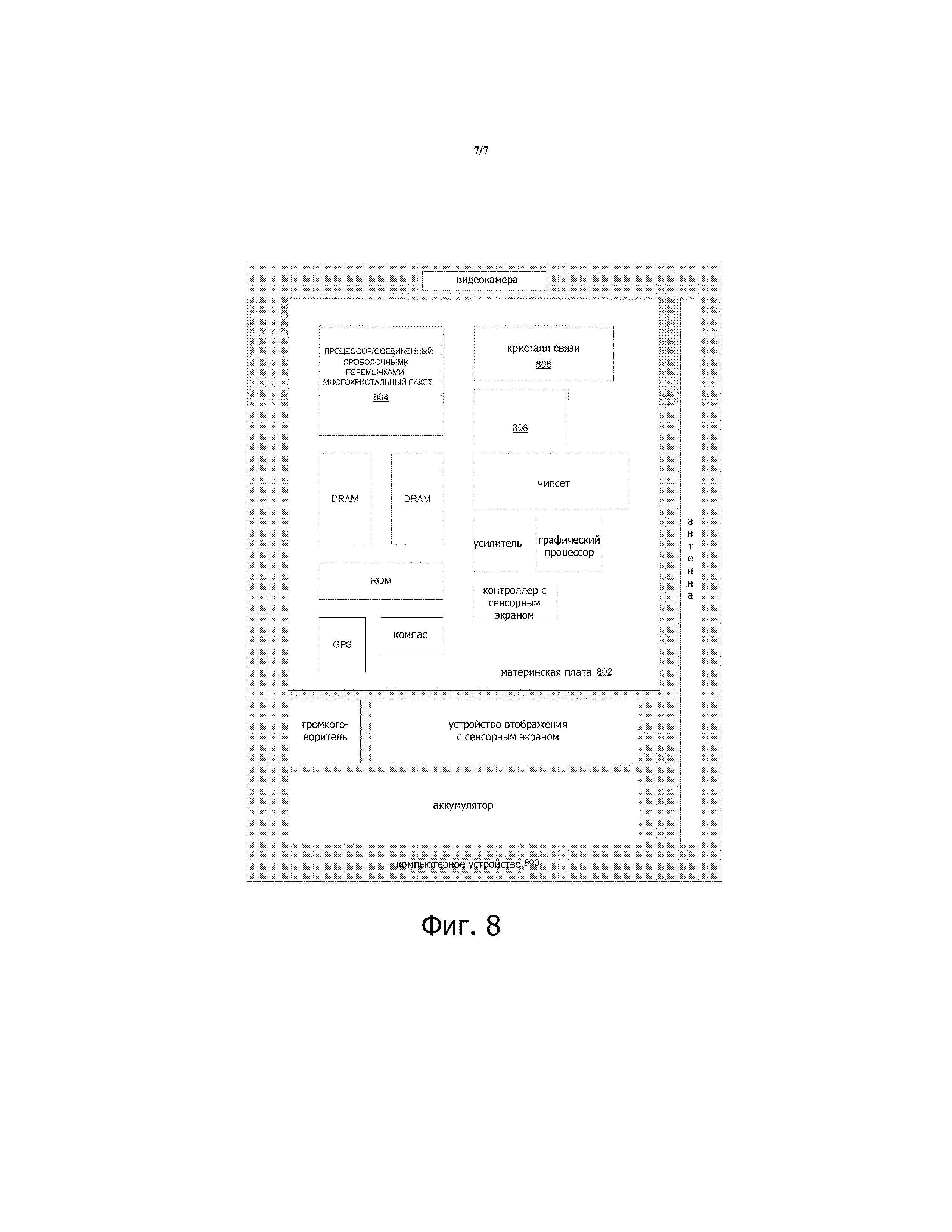

Варианты настоящего изобретения могут быть реализованы в системе с использованием какой-либо подходящей аппаратуры и/или программного обеспечения для конфигурирования по желанию. Фиг. 8 упрощенно иллюстрирует компьютерное устройство, содержащее корпусированную интегральную схему (IC), описанную здесь, например, такую как показано на фиг. 1-8. Компьютерное устройство 800 может содержать расположенную в корпусе устройства плату, такую как материнская плата 802. Эта материнская плата 802 может содержать несколько компонентов, включая, но не ограничиваясь этим, процессор 804 и по меньшей мере один кристалл (чип) 806 интегральной схемы связи. Процессор 804 может быть физически и электрически соединен с материнской платой 802. В некоторых вариантах указанный по меньшей мере один кристалл 806 связи также может быть физически и электрически соединен с материнской платой 802. В других вариантах кристалл 806 связи может быть частью процессора 804.

В зависимости от области применения компьютерное устройство 800 может также содержать другие компоненты, которые могут быть или могут не быть физически и электрически соединены с материнской платой 802. Такими другими компонентами могут быть, не ограничиваясь этим, энергозависимое запоминающее устройство (например, динамическое (DRAM)), энергонезависимое запоминающее устройство (например, (ROM)), устройство флэш-памяти, графический процессор, цифровой процессор сигнала, криптографический процессор, чипсет, антенна, дисплей, дисплей с сенсорным экраном, контроллер с сенсорным экраном, аккумулятор, аудио кодек, видео кодек, усилитель мощности, устройство глобальной системы местоопределения (GPS), компас, счетчик Гейгера, акселерометр, гироскоп, громкоговоритель, видеокамера и запоминающее устройство большой емкости (такое как накопитель на жестком диске, компакт-диск (CD), цифровой универсальный диск (DVD) и т.д.).

Кристалл 806 связи может обеспечивать радиосвязь для передачи данных к и от компьютерного устройства 800. Термин «радио» или «беспроводной» и его производные могут быть использованы для описания схем, устройств, систем, способов, методик, каналов связи и т.п., которые могут осуществлять связь и передачи данных с использованием модулированного электромагнитного излучения через несплошную среду. Термин не накладывает обязательного требования, чтобы соответствующие устройства не содержали никаких проводов, хотя в некоторых вариантах проводов может и не быть. Кристалл 806 связи может использовать какое-либо число стандартов или протоколов радиосвязи, включая, не ограничиваясь этим, стандарты, разработанные Институтов инженеров по электротехнике и электронике (Institute for Electrical and Electronic Engineers (IEEE)), включая WiFi (семейство IEEE 802.11), стандарты IEEE 802.16 (например, IEEE 802.16-2005, измененный), проект долговременной эволюции (Long-Term Evolution (LTE)) вместе с изменениями, обновлениями и/или пересмотрами (например, проект усовершенствованного LTE (advanced LTE), проект ультрамобильной широкополосной связи (UMB) (также именуемый "3GPP2"), и т.п.). Сети BWA, совместимые со стандартами IEEE 802.16, в общем случае называются сетями WiMAX, аббревиатура, обозначающая «всемирное взаимодействие для доступа в СВЧ-диапазоне» (Worldwide Interoperability for Microwave Access), что является сертификационным знаком для изделий, прошедших испытания соответствия и взаимодействия согласно требованиям стандартов IEEE 802.16. Кристалл 806 связи может работать в соответствии со стандартами, такими как глобальная система мобильной связи (GSM), система с общим сервисом пакетной радиопередачи (GPRS), универсальная мобильная телекоммуникационная система (UMTS), система с высокоскоростным пакетным доступом (HSPA), развитая система Evolved HSPA (E-HSPA) или сеть связи долговременной эволюции (Long-Term Evolution (LTE)). Кристалл 806 связи может также работать в соответствии со стандартом GSM с повышенными скоростями передачи данных (GSM Enhanced Data rates for GSM Evolution (EDGE)), стандартом сети радио доступа GSM с повышенными скоростями передачи данных (GERAN), стандартом универсальной наземной сети радио доступа (UTRAN) или развитой сети UTRAN (Evolved UTRAN (E-UTRAN)). Кристалл 806 связи может также работать в соответствии со стандартом многостанционного доступа с кодовым уплотнением (CDMA), стандартом многостанционного доступа с временным уплотнением (TDMA), стандартом цифровой усовершенствованной беспроводной связи (DECT), стандартом системы развития оптимизированной передачи данных (EV-DO), производными этих систем связи, равно как и какими-либо другими протоколами радиосвязи, обозначенными как протоколы третьего поколения (3G), четвертого поколения (4G), пятого поколения (5G) и последующих поколений. В других вариантах кристалл 806 связи может работать в соответствии с другими протоколами радиосвязи.

Компьютерное устройство 800 может содержать несколько кристаллов 806 связи. Например, первый кристалл 806 связи может быть выделен для радиосвязи малой дальности, такой как связь WiFi и связь Bluetooth, а второй кристалл 806 связи может быть выделен для радиосвязи большей дальности, такой как связь согласно стандартам GPS, EDGE, GPRS, CDMA, WiMAX, LTE, Ev-DO и другие.

Процессор 804 компьютерного устройства 800 может представлять собой корпусированную интегральную схему (IC) (например, корпусированную интегральную схему (IC) 102, показанную на фиг. 1), входящую в состав сборки с интегральной схемой (IC). Например, схемная плата 116, показанная на фиг. 1, может представлять собой материнскую плату 802 и процессор 804 может представлять собой кристалл корпусированной интегральной схемы (IC) 102, как описано ниже. Процессор 804 и материнская плата 802 могут быть соединены одно с другим с использованием соединений на уровне корпуса, как это описано здесь. Термин «процессор» может обозначать какое-либо устройство или часть устройства, обрабатывающую данные в электронной форме из регистров и/или запоминающих устройств для преобразования этих данных в электронной форме в другие данные в электронной форме, которые могут быть сохранены в регистрах и/или запоминающих устройствах.

Кристалл (чип) 806 связи может представлять собой корпусированную интегральную схему (IC) (например, корпусированную интегральную схему (IC) 102), входящую в состав сборки с интегральной схемой (IC), которая может содержать подложку корпуса. В следующих вариантах другой компонент (например, запоминающее устройство или другая интегральная схема), смонтированный в корпусе компьютерного устройства 800, может представлять собой корпусированную интегральную схему (IC) (например, корпусированную интегральную схему (IC) 102), входящую в состав сборки IC.

В различных вариантах компьютерное устройство 800 может представлять собой портативный компьютер, компьютер нетбук, компьютер ноутбук, компьютер «ультрабук», смартфон, планшетный компьютер, персональный цифровой помощник (personal digital assistant (PDA)), ультрамобильный персональный компьютер, мобильный телефон, настольный компьютер, сервер, принтер, сканер, монитор, приставка, пульт управления развлекательной системы, цифровую видеокамеру, портативный музыкальный плеер или цифровое видеозаписывающее устройство. В других вариантах компьютерное устройство 800 может представлять собой другое электронное устройство, обрабатывающее данные.

Примеры

Согласно различным вариантам здесь приведены описания ряда примеров.

Пример 1 может представлять корпусированную интегральную схему (IC), содержащую: первый кристалл интегральной схемы, по меньшей мере частично, погруженный в первый герметизирующий слой, первый кристалл имеет первую группу из нескольких структур соединений на уровне кристалла, расположенных на первой стороне первого герметизирующего слоя; несколько электрических маршрутных элементов, по меньшей мере частично погруженных в первый герметизирующий слой и конфигурированных для маршрутизации электрических сигналов между первой стороной первого герметизирующего слоя и второй стороной первого герметизирующего слоя, противоположной его первой стороне; и второй кристалл интегральной схемы, расположенный на второй стороне первого герметизирующего слоя и по меньшей мере частично погруженный во второй герметизирующий слой, второй кристалл имеет вторую группу из нескольких структур соединений на уровне кристалла, где вторая группа из нескольких структур соединений на уровне кристалла электрически соединена по меньшей мере с подгруппой множества электрических маршрутных элементов посредством проволочных перемычек.

Пример 2 может представлять предмет Примера 1, дополнительно содержащий: один или несколько перераспределительных слоев (RDL), расположенных на первой стороне первого герметизирующего слоя, где эти один или более слоев RDL электрически соединены с первым кристаллом, и где эти один или более слоев RDL электрически соединены со вторым кристаллом через множество электрических маршрутных элементов.

Пример 3 может представлять предмет Примера 2, дополнительно содержащий множество соединительных структур на уровне корпуса, расположенных на одном или более распределительных слоях RDL.

Пример 4 может представлять предмет Примера 2, дополнительно содержащий третий кристалл интегральной схемы, расположенный на одном или более слоях RDL и имеющий третью группу из множества структур соединений на уровне кристалла, электрически соединенных с одним или более слоями RDL.

Пример 5 может представлять предмет Примера 4, дополнительно содержащий множество соединительных структур на уровне корпуса, расположенных на одном или более слоях RDL, где суммарная толщина третьего кристалла и третьей группы из множества структур соединений на уровне кристалла меньше толщины индивидуальных соединительных структур на уровне корпуса из совокупности множества соединений на уровне корпуса, чтобы можно было установить третий кристалл в той же плоскости, где находятся указанные множество соединительных структур на уровне корпуса.

Пример 6 может представлять предмет Примера 1, где подгруппа группы из множества электрических маршрутных элементов является первой подгруппой, а корпусированная IC дополнительно содержит: третий кристалл интегральной схемы, по меньшей мере частично погруженный во второй герметизирующий слой и имеющий третью группу из множества структур соединений на уровне кристалла, электрически соединенных, посредством проволочных перемычек, со второй подгруппой из множества электрических маршрутных элементов, где третий кристалл и второй кристалл соединены один с другим через разделитель.

Пример 7 может представлять предмет какого-либо из Примеров 1 – 6, где указанное множество электрических маршрутных элементов содержат сквозные штырьки.

Пример 8 может представлять предмет какого-либо из Примеров 1 – 6, где корпусированная IC выполнена по технологии встроенных приборов с матрицей шариковых выводов на уровне пластины (eWLB).

Пример 9 может представлять способ изготовления корпусированной интегральной схемы (IC), содержащий этапы, на которых: обеспечивают первый герметизирующий слой, в который по меньшей мере частично погружены первый кристалл интегральной схемы и множество электрических маршрутных элементов, причем первый кристалл имеет первую группу из множества структур соединений на уровне кристалла, расположенных на первой стороне первого герметизирующего слоя, где эти электрические маршрутные элементы электрически соединяют первую сторону первого герметизирующего слоя со второй стороной этого первого герметизирующего слоя, где первая сторона первого герметизирующего слоя противоположна второй стороне этого первого слоя; соединение второго кристалла интегральной схемы сорт второй стороной первого герметизирующего слоя, где второй кристалл содержит вторую группу из множества структур соединений на уровне кристалла; электрическое соединение второй группы из множества структур соединений на уровне кристалла по меньшей мере с подгруппой совокупности из множества электрических маршрутных элементов посредством проволочных перемычек; и создание второго герметизирующего слоя поверх второго кристалла и конфигурации проволочных перемычек для герметизации по меньшей мере части второго кристалла и конфигурации проволочных перемычек во втором герметизирующем слое.

Пример 10 может представлять предмет Примера 9, где создание первого герметизирующего слоя содержит: соединение первого кристалла с носителем; соединение группы из множества электрических маршрутных элементов с носителем; и нанесение герметизирующего материала поверх первого кристалла и группы из нескольких электрических маршрутных элементов для создания первого герметизирующего слоя.

Пример 11 может представлять предмет Примера 9, где создание первого герметизирующего слоя содержит: соединение первого кристалла с носителем; нанесение герметизирующего материала поверх первого кристалла для образования первого герметизирующего слоя; и формирование множества электрических маршрутных элементов в герметизирующем материале.

Пример 12 может представлять предмет Примера 9, дополнительно содержащий:

формирование одного или более перераспределительных слоев (RDL) на первой стороне первого герметизирующего слоя, где один или более слоев RDL электрически соединены с первым кристаллом, и где один или более слоев RDL электрически соединены со вторым кристаллом посредством указанных нескольких электрических маршрутных элементов.

Пример 13 может представлять предмет Примера 12, дополнительно содержащий: группу из множества соединений на уровне корпуса на одном или более слоях RDL.

Пример 14 может представлять предмет Примера 12, дополнительно содержащий: электрическое соединение третьего кристалла интегральной схемы с одним или более слоями RDL через третью группу из множества структур соединений на уровне кристалла, расположенных на третьем кристалле.

Пример 15 может представлять предмет Примера 14, дополнительно содержащий формирование группы из множества соединительных структур на уровне корпуса на одном или более слоев RDL, где суммарная толщина третьего кристалла и третьей группы из множества структур соединений на уровне кристалла меньше толщины индивидуальных соединительных структур на уровне корпуса из совокупности множества соединений на уровне корпуса, чтобы можно было установить третий кристалл в той же плоскости, где находятся указанные множество соединительных структур на уровне корпуса.

Пример 16 может представлять предмет Примера 9, где подгруппа группы из множества электрических маршрутные элементов является первой подгруппой, а проволочные перемычки являются первыми проволочными перемычками, и корпусированная IC дополнительно содержит: физическое соединение третьего кристалла, имеющего третью группу из множества структур соединений на уровне кристалла, с поверхностью второго кристалла через разделитель; и электрическое соединение третьей группы из множества структур соединений на уровне кристалла со второй подгруппой из множества электрических маршрутных элементов посредством вторых проволочных перемычек, где второй герметизирующий слой создан для герметизации третьего кристалла, и

Пример 17 может представлять предмет какого-либо из Примеров 9 – 16, где указанные несколько электрических маршрутных элементов содержат сквозные штырьки.

Пример 18 может представлять предмет какого-либо из Примеров 9 – 16, где корпусированная IC выполнена по технологии встроенных приборов с матрицей шариковых выводов на уровне пластины (eWLB).

Пример 19 может представлять сборку с интегральной схемой (IC), содержащую: корпусированную IC, имеющую: первый кристалл интегральной схемы, по меньшей мере частично, погруженный в первый герметизирующий слой, первый кристалл имеет первую группу из множества структур соединений на уровне кристалла, расположенных на первой стороне первого герметизирующего слоя; множество электрических маршрутных элементов, по меньшей мере частично погруженных в первый герметизирующий слой и конфигурированных для маршрутизации электрических сигналов между первой стороной первого герметизирующего слоя и второй стороной первого герметизирующего слоя, противоположной его первой стороне; и второй кристалл интегральной схемы, расположенный на второй стороне первого герметизирующего слоя и по меньшей мере частично погруженный во второй герметизирующий слой, второй кристалл имеет вторую группу из множества структур соединений на уровне кристалла, где вторая группа из множества структур соединений на уровне кристалла электрически соединена по меньшей мере с подгруппой множества электрических маршрутных элементов посредством проволочных перемычек; и множество соединений на уровне корпуса, расположенных на первой стороне первого герметизирующего слоя и электрически соединенных со второй группой из множества структур соединений на уровне кристалла через множество электрических маршрутных элементов и первую группу из множества структур соединений на уровне кристалла; и схемную плату, имеющую множество электрических маршрутных элементов, расположенных в плате, и множество контактных площадок, расположенных на плате, где несколько контактных площадок электрически соединены с множеством соединительными структурами на уровне корпуса.

Пример 20 может представлять предмет Примера 19, где корпусированная интегральная схема (IC) содержит процессор.

Пример 21 может представлять предмет Примера 20, дополнительно содержащий одну или более антенн, устройство отображения, дисплей с сенсорным экраном, контроллер с сенсорным экраном, аккумулятор, аудио кодек, видео кодек, усилитель мощности, устройство системы глобального местоопределения (GPS), компас, счетчик Гейгера, акселерометр, гироскоп, громкоговоритель или видеокамеру, соединенные со схемной платой.

Пример 22 может представлять предмет какого-либо из Примеров 19 – 21, где сборка с интегральной схемой (IC) является частью портативного компьютера, компьютера нетбук, компьютера ноутбук, компьютера «ультрабук», смартфона, планшетного компьютера, персонального цифрового помощника (PDA), ультрамобильного персонального компьютера, мобильного телефона, настольного компьютера, сервера, принтера, сканера, монитора, приставки, пульта управления развлекательной системы, цифровой видеокамеры, портативного музыкального плеера или цифрового видеозаписывающего устройства.

Различные варианты могут содержать какие-либо подходящие сочетания описанных выше вариантов, включая альтернативные («или») варианты относительно вариантов, описанных в конъюнктивной форме («и») выше (например, «и» может также означать «и/или»). Более того, некоторые варианты могут содержать одно или несколько изделий (например, энергонезависимых компьютерных носителей информации), имеющих записанные команды, которые, при исполнении, ведут к действиям согласно какому-либо из описанных выше вариантов. Более того, некоторые варианты могут содержать аппаратуру или системы, имеющие какие-либо подходящие средства для выполнения различных операций согласно описываемым выше вариантам.

Приведенное выше описание иллюстрируемых вариантов, включая то, что описано в Реферате, не следует считать исчерпывающим или ограничивающим настоящее изобретение точно теми формами, какие рассмотрены здесь. Хотя здесь для иллюстрации рассмотрены конкретные варианты осуществления и примеры, специалистами в рассматриваемой области могут быть созданы многочисленные эквивалентные модификации, не отклоняясь от объема настоящего изобретения.

Эти модификации могут быть внесены в варианты настоящего изобретения в свете приведенного выше подробного описания. Термины, используемые в последующей Формуле изобретения, не следует толковать как ограничения различных вариантов настоящего изобретения конкретными вариантами, приведенными в настоящем описании и в Формуле изобретения. Напротив, объем изобретения следует определить целиком на основе прилагаемой Формулы изобретения, которую следует толковать согласно установленной доктрине интерпретации формулы изобретения.