Результат интеллектуальной деятельности: ЗАЩИТА ОТ ПЕРЕГРУЗКИ ОДНОЙ ЦЕПОЧКИ И СХЕМА ДРАЙВЕРА ИСТОЧНИКА ОСВЕЩЕНИЯ ДЛЯ УСТРОЙСТВА ОТОБРАЖЕНИЯ

Вид РИД

Изобретение

Область техники

Настоящее изобретение относится к области технологии отображения, в частности к устройству защиты от перегрузки одной цепочки и к схеме драйвера источника освещения для устройства отображения.

Технические предпосылки для создания изобретения

Планка освещения является одним из основных компонентов модуля подсветки жидкокристаллического дисплея (ЖК-дисплея). Планка освещения, включающая несколько цепочек, в настоящее время наиболее часто используется в модуле подсветки ЖК-дисплея. Некоторое множество светоизлучающих диодов (СИД) равномерно распределены по основанию планки, создавая планку освещения. Известные планки освещения обычно установлены симметрично на верхней или нижней сторонах или и на верхней, и на нижней сторонах ЖК-дисплея, или даже на всех четырех сторонах ЖК-дисплея.

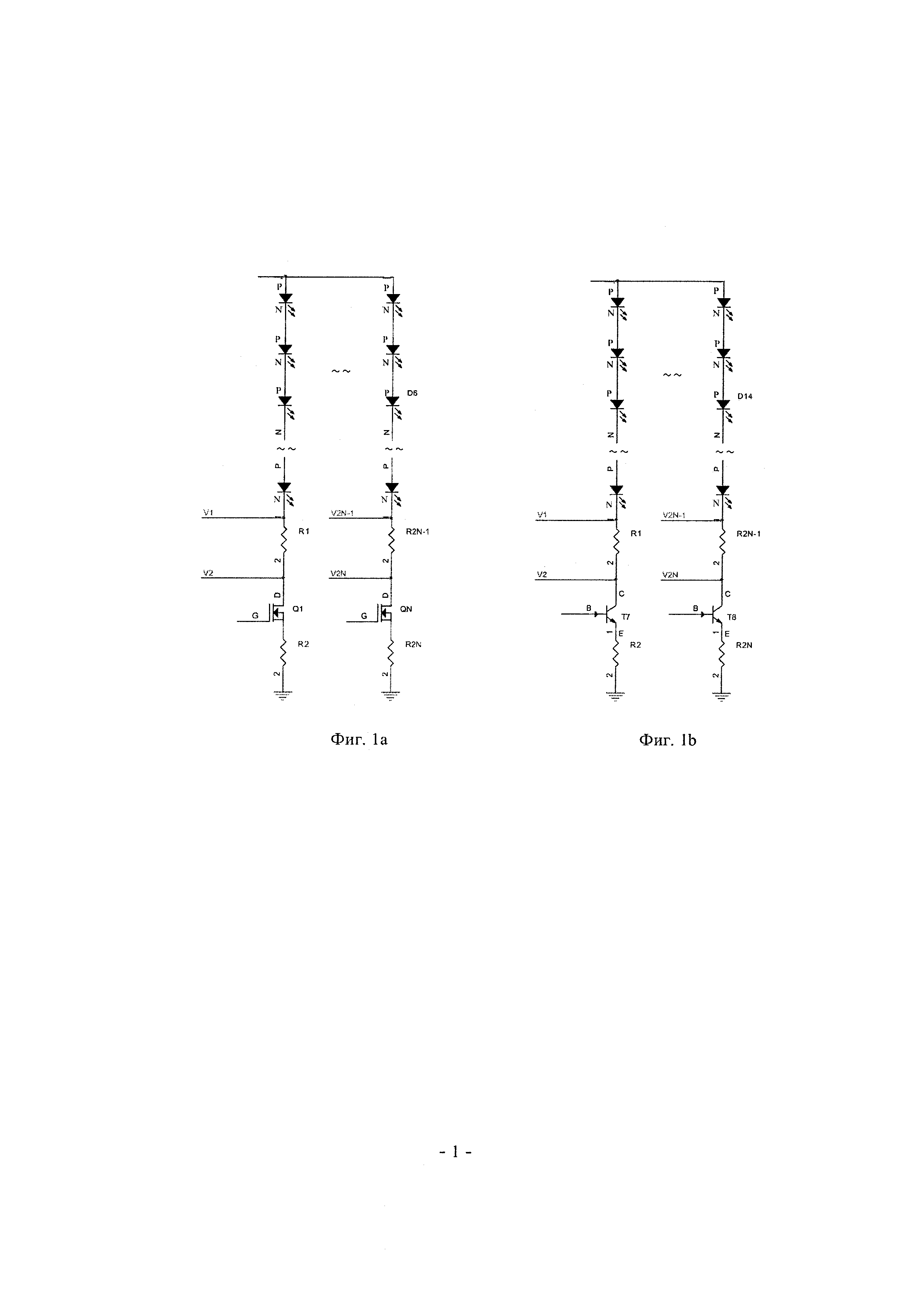

Однако повышающий преобразователь драйвера подсветки не включает схему защиты от перегрузки для каждой цепочки планки освещения. Используется просто схема защиты от чрезмерного тока или чрезмерного напряжения для всего входа. В этом случае могут возникать некоторые риски. Как показано на Фиг. 1а и 1b, если происходит пробой МОП-транзистора (MOSFET) (Фиг. 1а) или биполярного плоскостного транзистора (BJT) (Фиг. 1b), то ток в планке освещения становится неконтролируемым, приводя к чрезмерно большому току на поврежденной цепочке. При этом, поскольку токи в данных настройках немного превышают нормальный рабочий ток, то выход из строя только одной цепочки приведет к невозможности детектирования вышеуказанной проблемы.

Помимо этого, перегрузка в цепочке планки освещения может приводить к ряду проблем, таких как чрезмерная яркость в данной области, чрезмерная температуры планки освещения и выгорание диафрагмы ЖК-дисплея, и т.д.

Поэтому существует необходимость разработки подходящей защиты от перегрузки для схемы каждой цепочки светоизлучающих диодов.

Раскрытие изобретения

Одна из технических задач, решаемых настоящим изобретением, заключается в том, чтобы предложить устройство, которое может защищать другие компоненты от повреждения при чрезмерном токе или чрезмерном напряжении в одноцепочечной планке освещения.

Для решения вышеуказанной технической задачи настоящее изобретение предлагает устройство защиты от перегрузки для одноцепочечной светодиодной планки освещения. Устройство включает:

блок детектирования напряжения, входной контакт которого соединен с резистором в схеме одноцепочечной планки освещения на обоих выводах, чтобы получать напряжение на резисторе;

блок интеграции, входной контакт которого соединен с выходным контактом блока детектирования напряжения, чтобы выполнять интегральное преобразование полученного напряжения;

блок сравнения, который соединен с выходным контактом блока интеграции, чтобы сравнивать напряжение после интегрального преобразования с опорным напряжением, определяемым параметрами системы, для вывода сигнала эффективного превышения напряжения, если напряжение после интегрального преобразования выше, чем опорное напряжение; и

запирающий блок, соединенный с блоком сравнения, чтобы запирать сигнал ожидания вывода по сигналу эффективного превышения напряжения, при этом во время рабочего цикла, если появляется сигнал эффективного превышения напряжения, запирающий блок будет сохранять сигнал ожидания до перезапуска.

Согласно одному варианту осуществления настоящего изобретения, блок интеграции является блоком интеграции с дифференциальным входом, при этом его другой входной контакт соединен с внутренним блоком генерации опорного напряжения, чтобы выполнять интегральное преобразование конечного напряжения на основании внутреннего опорного напряжения. Вышеупомянутый внутренний блок генерации опорного напряжения включает блок пропорционального усилителя для пропорционального усиления конечного напряжения.

Согласно одному варианту осуществления настоящего изобретения, первый переключающий элемент и второй переключающий элемент также соединены с выходным контактом вышеупомянутого блока пропорционального усилителя. В один и тот же период времени первый переключающий элемент поддерживается в другом состоянии "включен-отключен", чем второй переключающий элемент.

Согласно одному варианту осуществления настоящего изобретения, первым переключающим элементом и вторым переключающим элементом являются МОП-транзисторы. Последовательности импульсов одной частоты, но с противоположными высоким-низким уровнями соответственно поступают на управляющие контакты этих двух переключающих элементов.

Согласно одному варианту осуществления настоящего изобретения, частота последовательностей импульсов соотносится с частотой диммирования.

Согласно одному варианту осуществления настоящего изобретения, вышеупомянутый запирающий блок включает первый и второй транзисторы, при этом первым транзистором является транзистор NPN-типа, и вторым транзистором является транзистор PNP-типа, база первого транзистора соединена с выходным контактом блока сравнения и коллектором второго транзистора. Коллектор первого транзистора соединен с базой второго транзистора. Эмиттер второго транзистора соединен с клеммой электропитания Vcc через нагрузочный резистор.

Согласно одному варианту осуществления настоящего изобретения, запирающий блок, кроме того, включает третий и четвертый переключающие элементы, при этом управляющий контакт третьего переключающего элемента соединен с эмиттером второго транзистора, чтобы управлять включением-отключением третьего переключающего элемента по сигналу на эмиттере второго транзистора. Два выходных контакта третьего переключающего элемента соединены, соответственно, с заземлением и с контактом электропитания Vcc, и управляющий контакт четвертого переключающего элемента соединен с входным контактом третьего переключающего элемента, который соединен с контактом электропитания Vcc, и выходные контакты четвертого переключающего элемента соединены, соответственно, с разрешающим контактом повышающего преобразователя и заземлением. Повышающий преобразователь устанавливается в состояние ожидания, когда сигнал, подводимый на разрешающий контакт, имеет низкий уровень, и устанавливается в нормальное рабочее состояние, когда сигнал, подводимый на разрешающий контакт, имеет высокий уровень.

Согласно одному варианту осуществления настоящего изобретения, вышеупомянутый блок пропорционального усилителя приспособлен для удвоения напряжения на входном контакте.

Согласно одному варианту осуществления настоящего изобретения, частота последовательности импульсов равна частоте диммирования, так что блок интеграции может возвращать результат интегрального преобразования на нуль на основании интегрального опорного напряжения.

Согласно еще одному аспекту настоящего изобретения, предложена схема драйвера источника освещения, включающая:

несколько планок освещения;

упомянутое устройство защиты от перегрузки одной цепочки, которое соединено с блоком получения напряжения каждой планки освещения, чтобы детектировать его напряжение и выводить сигнал запертого режима ожидания на основании значения напряжения;

повышающий преобразователь и ИС драйвера, соединенную с входным контактом планки освещения, чтобы подавать напряжение возбуждения на планку освещения и определять, нужно ли переходить в состояние ожидания по сигналу запирания режима ожидания, направленному устройством защиты от перегрузки.

Другие признаки и преимущества настоящего изобретения будут проиллюстрированы и станут частично понятными из нижеследующего описания или же будут поняты посредством реализации настоящего изобретения. Цели и другие преимущества настоящего изобретения могут быть достигнуты и получены на основании конструкций, указанных в описании, формуле изобретения и на прилагаемых чертежах.

Краткое описание чертежей

Прилагаемые чертежи, которые являются частью описания, представлены для более глубокого понимания настоящего изобретения и объяснения настоящего изобретения в связи с вариантами его осуществления. Они не должны истолковываться как ограничивающие настоящее изобретение. На прилагаемых чертежах:

Фиг. 1а и 1b - схематический вид светодиодной планки освещения, известной из уровня техники;

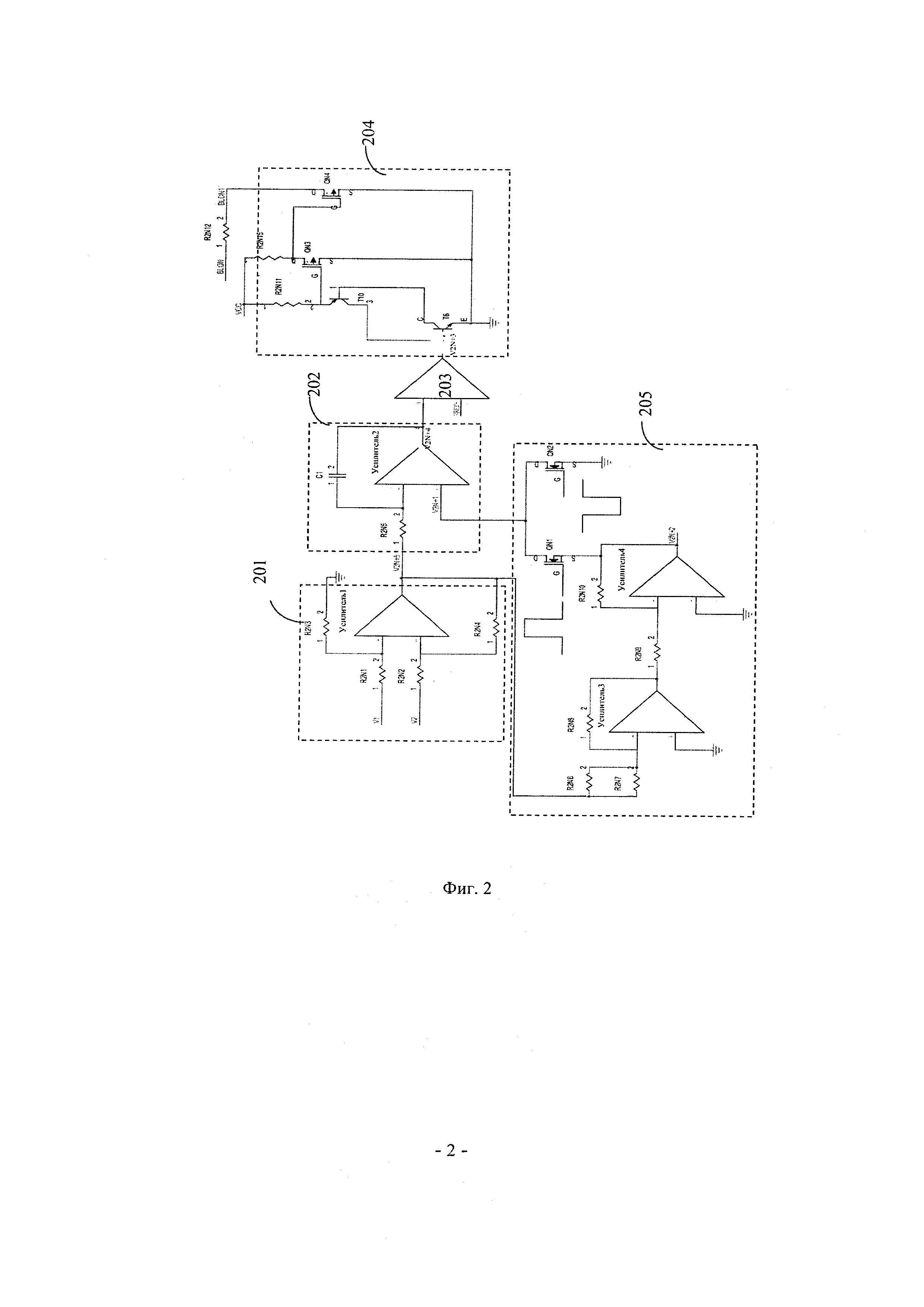

Фиг. 2 - схема защиты от перегрузки одноцепочечной планки освещения согласно одному варианту осуществления настоящего изобретения;

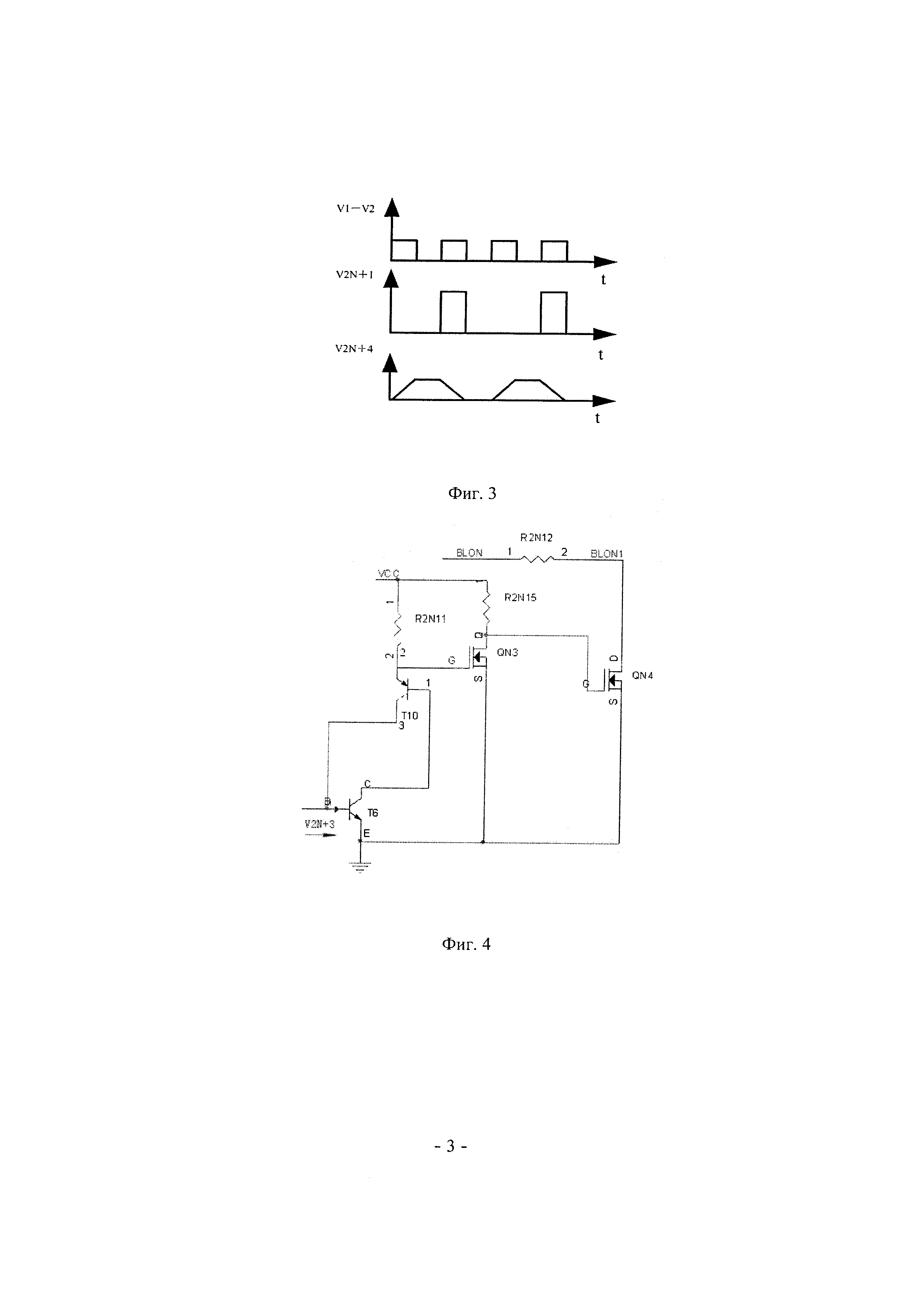

Фиг. 3 - график последовательности конечного напряжения, интегрального опорного напряжения и интегрального напряжения согласно одному варианту осуществления настоящего изобретения.

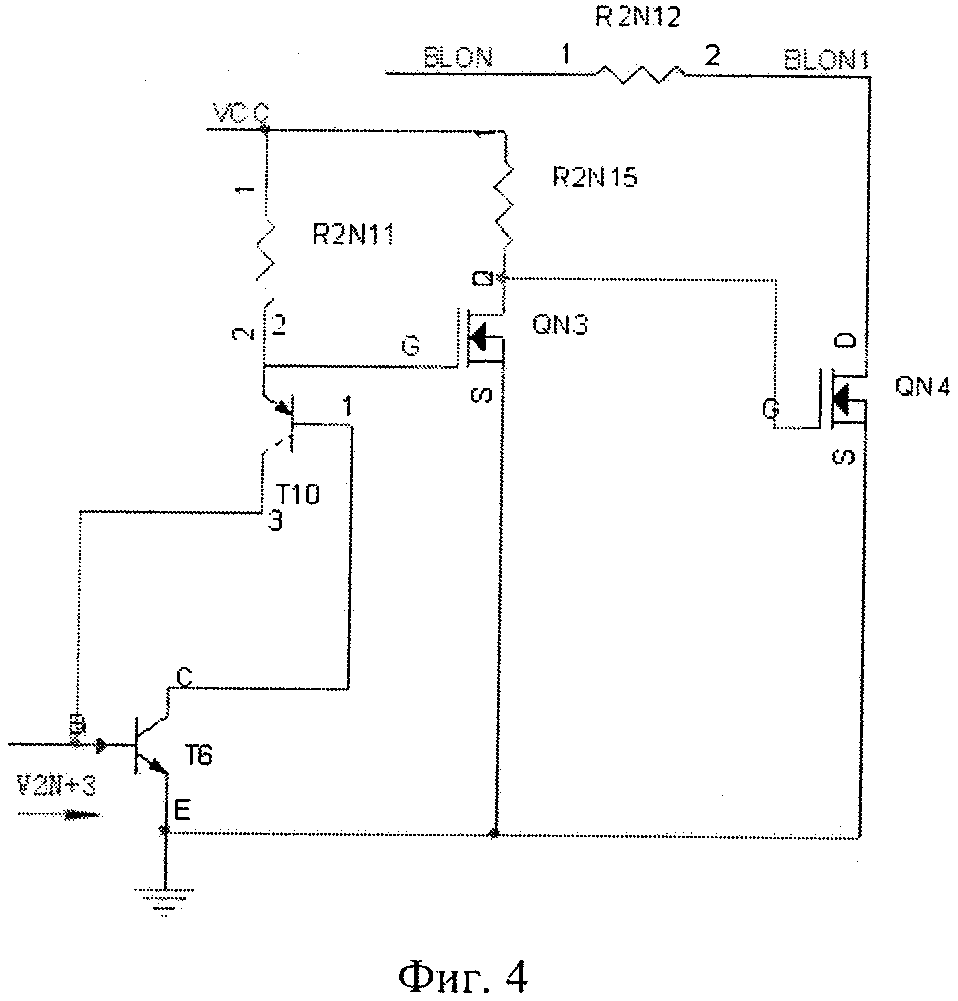

Фиг. 4 - схематический вид запирающего блока схемы защиты от перегрузки согласно

одному варианту осуществления настоящего изобретения.

Подробное описание вариантов осуществления

Настоящее изобретение будет подробно описано ниже в связи с вариантами осуществления и прилагаемыми чертежами, чтобы достичь цели понимания технических средств настоящего изобретения для решения его технических задач и процесса достижения его технических результатов. Следует сказать, что если нет противоречий, все технические признаки настоящего изобретения могут быть объединены друг с другом любым образом, и сформированные таким образом технические решения подпадают под объем настоящего изобретения.

На Фиг. 2 показана схема устройства защиты от перегрузки одноцепочечной планки освещения согласно одному варианту осуществления настоящего изобретения. Устройство защиты от перегрузки включает блок детектирования напряжения 201, блок интеграции 202, блок сравнения 203 и запирающий блок 204.

Входной контакт блока детектирования напряжения 201 соединен с резистором (показан как R1…R2N+1 на Фиг. 1а или Фиг.1b) на обоих выводах, который последовательно соединен со схемой одноцепочечной планки освещения, чтобы получить напряжение V1-V2 на этом резисторе. При условии, что дано сопротивление R1…R2N+1, можно измерить ток, протекающий через схему одноцепочечной планки освещения.

Согласно одному варианту осуществления настоящего изобретения, блок детектирования напряжения 201 включает схему вычитания, состоящую из усилителя и соответствующих резисторов. Резисторы, имеющие одинаковое сопротивление расположены, соответственно, на двух контактах дифференциального входа и на контуре обратной связи усилителя, т.е., R2N1=R2N2=R2N3=R2N4. Согласно уравнению рабочего усиления, на выходе V2N+5 усилителя 1 получаем V1-V2. Для схемы одноцепочечной планки освещения график последовательности напряжения V1-V2 на контакте показан на Фиг. 3.

Входной контакт блока интеграции 202 соединен с выходным контактом блока детектирования напряжения 201, чтобы выполнять интегральное преобразование конечного напряжения V1-V2 для получения выходного напряжения V2N+4 после интегрирования. Как показано на Фиг. 3, из-за наличия конденсатора в схеме контура обратной связи выход блока интеграции медленно возрастает до определенного значения. Таким образом, как преимущество, блок интеграции предназначен для подавления всплесков напряжения V1-V2 и, за счет этого, устранения неправильных срабатываний, вызываемых прямой защитой от превышения по току. Например, даже если произойдет кратковременное резкое изменение значения V1-V2 или тока в схеме одноцепочечной планки освещения (например, при трехмерном сканировании, максимальной яркости, ШИМ-диммировании), на выходе блока интеграции 202 не будет резкого изменения. Поэтому устройство защиты от перегрузки способно избегать сбоев в работе при, например, трехмерном сканировании.

Согласно одному варианту осуществления настоящего изобретения, как показано на Фиг. 2, блок интеграции 202 является блоком с дифференциальным входом. Другой входной контакт блока интеграции 202 соединен с внутренним блоком генерации опорного напряжения 205, чтобы выполнять периодическое интегральное преобразование конечного напряжения V1-V2 на основании интегрального опорного напряжения V2N+1. Внутренний блок генерации опорного напряжения 205 включает блок пропорционального усилителя 205а, который используется для пропорционального усиления полученного конечного напряжения.

Первый переключатель QN1 и второй переключатель QN2 соединены с выходными контактами блока пропорционального усилителя 205а, при этом один контакт QN1 соединен с выходным контактом блока пропорционального усилителя 205а, чтобы получать сигнал усиленного напряжения V2N+2, и один контакт QN2 соединен с заземлением, при этом другие контакты QN1 и QN2 соединены с блоком интеграции 202. QN1 поддерживается в противоположном QN2 состоянии "включен-отключен" в один период времени. Другими словами, в тот же период времени только один из QN1 и QN2 включен. На Фиг. 3 показана форма волны выходного интегрального опорного напряжения V2N+1.

QN1 и QN2 являются МОП-транзисторами. Последовательности импульсов одной частоты, но с противоположными высоким-низким уровнями, подводятся на управляющие контакты первого переключающего элемента QN1 и второго переключающего элемента QN2. Здесь частота последовательностей импульсов соотносится с частотой диммирования.

Как показано на Фиг. 2, блок пропорционального усилителя 205а приспособлен для удвоения напряжения на входном контакте, т.е., V2N+2=2(V1-V2). Для того, чтобы вернуть интеграл конечного напряжения V2N+4 на нуль за два цикла, частота последовательностей импульсов, подводимых на управляющие контакты QN1 и QN2, сделана равной частоте диммирования. Однако настоящее изобретение этим не ограничено, коэффициент усиления блока пропорционального усилителя 205а может быть разным, исходя из практического применения. Соответственно, частота последовательностей импульсов, подводимых на управляющие контакты QN1 и QN2 может быть равна или соотнесена с частотой диммирования.

За счет этого результат интегрирования не будет превышать опорное напряжение Vref, устанавливаемое системой.

Снова со ссылкой на Фиг. 2, блок сравнения 203 соединен с выходным контактом блока интеграции 202, чтобы сравнивать напряжение после интегрального преобразования с опорным напряжением Vref, установленным параметрами системы, и затем выводить сигнал эффективного превышения напряжения, если напряжение после интегрального преобразования выше, чем опорное напряжение Vref. Сигнал эффективного превышения напряжения, обозначенный как V2N+3 на Фиг. 2, например, когда он имеет высокий уровень, показывает, что ток, протекающий по одноцепочечной планке освещения, превышает номинальное значение.

В этом случае запирающий блок 204, который соединен с блоком сравнения 203, будет запирать выходной сигнал режима ожидания по сигналу эффективного превышения напряжения V2N+3. Во время рабочего цикла, если появляется сигнал эффективного превышения напряжения, такой как сигнал V2N+3 высокого уровня, запирающий блок 204 будет сохранять сигнал режима ожидания BLON1 до перезапуска.

Согласно одному варианту осуществления настоящего изобретения, как показано на Фиг. 2, запирающий блок 204 включает первый транзистор Т6 и второй транзистор Т10. Первый транзистор является транзистором NPN-типа, и второй является транзистором PNP-типа. База первого транзистора Т6 соединена с выходным контактом блока сравнения 203 и коллектором второго транзистора Т10. Коллектор первого транзистора Т6 соединен с базой второго транзистора Т10. Эмиттер второго транзистора Т10 соединен с контактом электропитания Vcc через нагрузочный резистор R2N11.

Запирающий блок 204 также включает третий переключающий элемент QN3 и четвертый переключающий элемент QN4. Управляющий контакт третьего переключающего элемента QN3 соединен с эмиттером второго транзистора Т10, так что состояние "включен-отключен" третьего переключающего элемента QN3 управляется сигналом с эмиттера второго транзистора Т10. Два выходных контакта третьего переключающего элемента QN3 соединены, соответственно, с заземлением и с контактом электропитания Vcc. Управляющий контакт четвертого переключающего элемента QN4 соединен с выходным контактом третьего переключающего элемента QN3, который соединен с контактом электропитания Vcc. Выходные контакты четвертого переключающего элемента QN4 соединены, соответственно, с разрешающим контактом повышающего преобразователя и заземлением. Повышающий преобразователь устанавливается в состояние ожидания, когда сигнал BLON1 с разрешающего контакта имеет низкий уровень, и устанавливается в нормальное рабочее состояние, когда сигнал BLON1 с разрешающего контакта имеет высокий уровень.

Более конкретно, как показано на Фиг. 4, третьим переключающим элементом QN3 и четвертым переключающим элементом QN4 являются МОП-транзисторы. Когда V2N+3 имеет высокий уровень (т.е., когда значение интегрального преобразования V2N+4 напряжения V1-V2 превышает Vref), транзисторы Т6 и Т10 включены, напряжение на затворе QN3 заблокировано на низком уровне запирающей схемой, поэтому, согласно характеристикам индуцирующего устройства, когда переключатель QN3 удерживается в отключенном состоянии, и QN4 удерживается во включенном состоянии, сигнал BLON1 имеет низкий уровень. Сигнал BLON1 посылается на разрешающий контакт повышающего преобразователя, чтобы поддерживать его в состоянии ожидания.

Однако, если значение V1-V2 превышает опорное напряжение, запирающая схема, включающая Т6 и Т10, будет запирать выход блока сравнения 203 при эффективном превышении напряжения даже после того, как интегральное значение V2N+4 напряжения V1-V2 возвратится к значению ниже, чем опорное напряжение, и запирающая схема будет продолжать удерживать BLON1 на низком уровне. Повышающий преобразователь может начать нормально работать только после перезапуска. Таким образом, устройство защиты от перегрузки может обеспечивать стабильную защиту для светодиодной планки освещения.

Согласно еще одному аспекту настоящего изобретения, предложена схема драйвера источника освещения, включающая:

некоторое число планок освещения;

вышеупомянутое устройство защиты от перегрузки одной цепочки, которое соединено с блоком получения напряжения каждой планки освещения, чтобы детектировать напряжение на блоке получения напряжения и выводить сигнал запирания режима ожидания;

повышающий преобразователь и ИС драйвера, соединенную с входным контактом планки освещения, чтобы подавать напряжение возбуждения на планку освещения и определять, переходить ли в состояние ожидания по сигналу запирания режима ожидания, направленному устройством защиты от перегрузки.

Вышеописанные варианты осуществления представлены только для облегчения понимания настоящего изобретения, и они не должны истолковываться как ограничивающие объем настоящего изобретения. Любые изменения или модификации в рамках объема настоящего изобретения могут быть внесены в форму реализации или конкретные детали настоящего изобретения любым специалистом в данной области техники. Однако объем настоящего изобретения должен определяться только формулой изобретения.