Результат интеллектуальной деятельности: ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ И ПОДЛОЖКА МАТРИЦЫ ТАКОГО УСТРОЙСТВА

Вид РИД

Изобретение

Область техники

[0001] Изобретение относится к области технологии жидкокристаллических дисплеев и, в частности, к жидкокристаллическому устройству отображения и подложке матрицы такого устройства.

Описание предшествующего уровня техники

[0002] В традиционной конструкции пиксельной структуры шина передачи данных электрически соединена с соседними пиксельными электродами черед тонкопленочные транзисторы и обеспечивает напряжение шкалы оттенков серого пиксельным электродам. Поскольку пространство компоновки компонентов, занятое тонкопленочным транзистором в направлении продолжения шины передачи данных, большое, чтобы обеспечить относительную апертуру пикселя, области апертуры двух пикселей между двумя соседними шинами передачи данных не могут быть расположены параллельно вдоль направления продолжения линии сканирования. Однако такая компоновка уменьшит унифицированность маски RGB, увеличит стоимость изготовления пиксельного электрода, приведет к простой генерации областью апертуры пикселя оптической интерференции с оптической пленкой жидкокристаллического устройства отображения и тем самым ухудшит качество отображения жидкокристаллического устройства отображения. Если обеспечить параллельное расположение областей апертуры двух пикселей вдоль направления продолжения линии сканирования, области областей апертуры должны быть уменьшены, что приведет к уменьшению относительной апертуры пикселей.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

[0003] Соответственно, варианты осуществления изобретения предусматривают жидкокристаллическое устройство отображения и подложку матрицы такого устройства, которые могут обеспечить качество отображения жидкокристаллического устройства отображения и увеличить относительную апертуру пикселей.

[0004] Техническим решением, предлагаемым изобретением, является создание подложки матрицы. Подложка матрицы содержит: первую шину передачи данных и вторую шину передачи данных, причем первая шина передачи данных и вторая шина передачи проходят вдоль первого направления и расположены на расстоянии друг от друга вдоль второго направления, перпендикулярного первому направлению; первый пиксельный электрод и второй пиксельный электрод, причем первый пиксельный электрод и второй пиксельный электрод расположены между первой шиной передачи данных и второй шиной передачи данных и расположены на расстоянии друг от друга вдоль второго направления, первый пиксельный электрод расположен рядом с первой шиной передачи данных, второй пиксельный электрод расположен рядом со второй шиной передачи данных, первая шина передачи данных выполнена с возможностью подачи напряжения шкалы оттенков серого на второй пиксельный электрод, а вторая шина передачи данных выполнена с возможностью подачи напряжения шкалы оттенков серого на первый пиксельный электрод; первый тонкопленочный транзистор и второй тонкопленочный транзистор, расположенные между первой шиной передачи данных и второй шиной передачи данных, причем первая шина передачи данных электрически соединена с истоком первого тонкопленочного транзистора, второй пиксельный электрод электрически соединен со стоком первого тонкопленочного транзистора, вторая шина передачи данных электрически соединена с истоком второго тонкопленочного транзистора, а первый пиксельный электрод электрически соединен со стоком второго тонкопленочного транзистора; первое сквозное отверстие и второе сквозное отверстие, причем первое сквозное отверстие и второе сквозное отверстие расположены соответственно на одних прямых линиях с первым тонкопленочным транзистором и вторым тонкопленочным транзистором вдоль направления, перпендикулярного первой шине передачи данных, а также второй шине передачи данных, второй пиксельный электрод электрически соединен со стоком первого тонкопленочного транзистора через первое сквозное отверстие, а первый пиксельный электрод электрически соединен со стоком второго тонкопленочного транзистора через второе сквозное отверстие.

[0005] В одном варианте осуществления первый пиксельный электрод и второй пиксельный электрод имеют соответственно первую область апертуры и вторую область апертуры, первая область апертуры и вторая область апертуры выровнены вдоль второго направления.

[0006] Другое техническое решение, предлагаемое изобретением, состоит в том, чтобы обеспечить подложку матрицы. Подложка матрицы содержит: первую шину передачи данных и вторую шину передачи данных, причем первая шина передачи данных и вторая шина передачи данных проходят вдоль первого направления и расположены на расстоянии друг от друга вдоль второго направления, перпендикулярного первому направлению; первый пиксельный электрод и второй пиксельный электрод, причем первый пиксельный электрод и второй пиксельный электрод расположены между первой шиной передачи данных и второй шиной передачи данных и расположены на расстоянии друг от друга вдоль второго направления, первый пиксельный электрод и первая шина передачи данных расположены рядом друг с другом, второй пиксельный электрод и вторая шина передачи данных расположены рядом друг с другом, первая шина передачи данных выполнена с возможностью подачи напряжения шкалы оттенков серого на второй пиксельный электрод, а вторая шина передачи данных выполнена с возможностью подачи напряжения оттенков серого на первый пиксельный электрод.

[0007] В варианте осуществления подложка матрицы дополнительно содержит первый тонкопленочный транзистор и второй тонкопленочный транзистор, расположенные между первой шиной передачи данных и второй шиной передачи данных, первая шина передачи данных электрически соединена с одним из элементов: истоком или стоком первого тонкопленочного транзистора, второй пиксельный электрод электрически соединен с другим из элементов: истоком или стоком первого тонкопленочного транзистора, вторая шина передачи данных электрически соединена с одним из элементов: истоком или стоком второго тонкопленочного транзистора, и первый пиксельный электрод электрически соединен с другим из элементов: истоком или стоком второго тонкопленочного транзистора.

[0008] В варианте осуществления первый тонкопленочный транзистор и второй тонкопленочный транзистор расположены на расстоянии друг от друга вдоль первого направления и соответственно на противоположных сторонах первого пиксельного электрода, а также второго пиксельного электрода.

[0009] В варианте осуществления первый пиксельный электрод и второй пиксельный электрод выровнены вдоль второго направления.

[0010] В варианте осуществления первый пиксельный электрод и второй пиксельный электрод соответственно имеют первую область апертуры и вторую область апертуры, первая область апертуры и вторая область апертуры выровнены вдоль второго направления.

[0011] В варианте осуществления подложка матрицы дополнительно содержит первую шину сканирования и вторую шину сканирования, первая шина сканирования и вторая шина сканирования проходят вдоль второго направления и расположены на расстоянии друг от друга вдоль первого направления; первый пиксельный электрод, второй пиксельный электрод, первый тонкопленочный транзистор и второй тонкопленочный транзистор дополнительно расположены между первой шиной сканирования и второй шиной сканирования, первая шина сканирования расположена рядом с первым тонкопленочным транзистором и электрически соединена с затвором первого тонкопленочного транзистора, вторая шина сканирования расположена рядом со вторым тонкопленочным транзистором и электрически соединена с затвором второго тонкопленочного транзистора.

[0012] В варианте осуществления подложка матрицы дополнительно сформирована с первым сквозным отверстием и вторым сквозным отверстием, второй пиксельный электрод электрически соединен с одним из элементов: истоком или стоком первого тонкопленочного транзистора через первое сквозное отверстие, первый пиксельный электрод электрически соединен с другим из элементов: истоком или стоком второго тонкопленочного транзистора через второе сквозное отверстие.

[0013] В варианте осуществления первое сквозное отверстие и первый тонкопленочный транзистор расположены на расстоянии друг от друга вдоль второго направления, второе сквозное отверстие и второй тонкопленочный транзистор расположены на расстоянии друг от друга вдоль второго направления.

[0014] В варианте осуществления первое сквозное отверстие и первый тонкопленочный транзистор расположены на одной прямой линии вдоль второго направления, второе сквозное отверстие и второй тонкопленочный транзистор расположены на одной прямой линии вдоль второго направления.

[0015] Для решения указанной выше технической проблемы техническое решение, предлагаемое изобретением, состоит в обеспечении жидкокристаллического устройства отображения, содержащего подложку матрицы. Подложка матрицы содержит: первую шину передачи данных и вторую шину передачи данных, причем первая шина передачи данных и вторая шина передачи данных проходят вдоль первого направления и расположены на расстоянии друг от друга вдоль второго направления, перпендикулярного первому направлению; первый пиксельный электрод и второй пиксельный электрод, причем первый пиксельный электрод и второй пиксельный электрод расположены между первой шиной передачи данных и второй шиной передачи данных и расположены на расстоянии друг от друга вдоль второго направления, первый пиксельный электрод и первая шина передачи данных расположены рядом друг с другом, второй пиксельный электрод и вторая шина передачи данных расположены рядом друг с другом, первая шина передачи данных выполнена с возможностью подачи напряжения шкалы оттенков серого на второй пиксельный электрод, а вторая шина передачи данных выполнена с возможностью подачи напряжения оттенков серого на первый пиксельный электрод.

[0016] В варианте осуществления подложка матрицы дополнительно содержит первый тонкопленочный транзистор и второй тонкопленочный транзистор, расположенные между первой шиной передачи данных и второй шиной передачи данных, первая шина передачи данных электрически соединена с одним из элементов: истоком или стоком первого тонкопленочного транзистора, второй пиксельный электрод электрически соединен с другим из элементов: истоком или стоком первого тонкопленочного транзистора, вторая шина передачи данных электрически соединена с одним из элементов: истоком или стоком второго тонкопленочного транзистора, и первый пиксельный электрод электрически соединен с другим из элементов: истоком или стоком второго тонкопленочного транзистора.

[0017] В варианте осуществления первый тонкопленочный транзистор и второй тонкопленочный транзистор расположены на расстоянии друг от друга вдоль первого направления и соответственно на противоположных сторонах первого пиксельного электрода, а также второго пиксельного электрода.

[0018] В варианте осуществления первый пиксельный электрод и второй пиксельный электрод выровнены вдоль второго направления.

[0019] В варианте осуществления первый пиксельный электрод и второй пиксельный электрод соответственно имеют первую область апертуры и вторую область апертуры, первая область апертуры и вторая область апертуры выровнены вдоль второго направления.

[0020] В варианте осуществления подложка матрицы дополнительно содержит первую шину сканирования и вторую шину сканирования, первая шина сканирования и вторая шина сканирования проходят вдоль второго направления и расположены на расстоянии друг от друга вдоль первого направления; первый пиксельный электрод, второй пиксельный электрод, первый тонкопленочный транзистор и второй тонкопленочный транзистор дополнительно расположены между первой шиной сканирования и второй шиной сканирования, первая шина сканирования расположена рядом с первым тонкопленочным транзистором и электрически соединена с затвором первого тонкопленочного транзистора, вторая шина сканирования расположена рядом со вторым тонкопленочным транзистором и электрически соединена с затвором второго тонкопленочного транзистора.

[0021] В варианте осуществления подложка матрицы дополнительно сформирована с первым сквозным отверстием и вторым сквозным отверстием, второй пиксельный электрод электрически соединен с одним из элементов: истоком или стоком первого тонкопленочного транзистора через первое сквозное отверстие, первый пиксельный электрод электрически соединен с другим из элементов: истоком или стоком второго тонкопленочного транзистора через второе сквозное отверстие.

[0022] В варианте осуществления первое сквозное отверстие и первый тонкопленочный транзистор расположены на расстоянии друг от друга вдоль второго направления, второе сквозное отверстие и второй тонкопленочный транзистор расположены на расстоянии друг от друга вдоль второго направления.

[0023] В варианте осуществления первое сквозное отверстие и первый тонкопленочный транзистор расположены на одной прямой линии вдоль второго направления, второе сквозное отверстие и второй тонкопленочный транзистор расположены на одной прямой линии вдоль второго направления.

[0024] С помощью вышеуказанных технических решений эффективность, которая может быть достигнута изобретением, заключается в следующем: подложка матрицы различных вариантов осуществления изобретения создана быть следующей: первая шина передачи данных и вторая шина передачи данных проходят вдоль первого направления и расположены на расстоянии друг от друга вдоль второго направления, перпендикулярного первому направлению, первый пиксельный электрод и второй пиксельный электрод расположены между первой шиной передачи данных и второй шиной передачи данных и расположены на расстоянии друг от друга вдоль второго направления, первый пиксельный электрод расположен рядом с первой шиной передачи данных, второй пиксельный электрод расположен рядом со второй шиной передачи данных, первая шина передачи данных предназначена для обеспечения напряжения шкалы оттенков серого для второго пиксельного электрода, а вторая шина передачи данных предназначена для обеспечения напряжения шкалы оттенков серого для первого пиксельного электрода, и увеличивает пространство компоновки компонентов вдоль направления продолжения шины передачи данных, так что компоненты, соединенные с пиксельными электродами, могут быть расположены горизонтально вдоль направления продолжения шины сканирования и области апертуры двух пикселей между двумя соседними шинами передачи данных могут быть расположены параллельно вдоль направления продолжения шины сканирования. В результате может быть обеспечено качество отображения жидкокристаллического устройства отображения, и может быть увеличена относительная апертура пикселя.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0025] Чтобы более четко проиллюстрировать технические решения различных вариантов осуществления настоящего изобретения, в описании вариантов осуществления будут использованы чертежи, краткое описание которых будет дано ниже. Очевидно, чертежи в следующем описании являются только некоторыми вариантами осуществления изобретения, обычный специалист в данной области техники может получить другие чертежи в соответствии с этими представленными чертежами без творческих усилий. На чертежах:

[0026] Фиг. 1 - схематический структурный вид жидкокристаллической панели отображения в соответствии с предпочтительным вариантом осуществления изобретения;

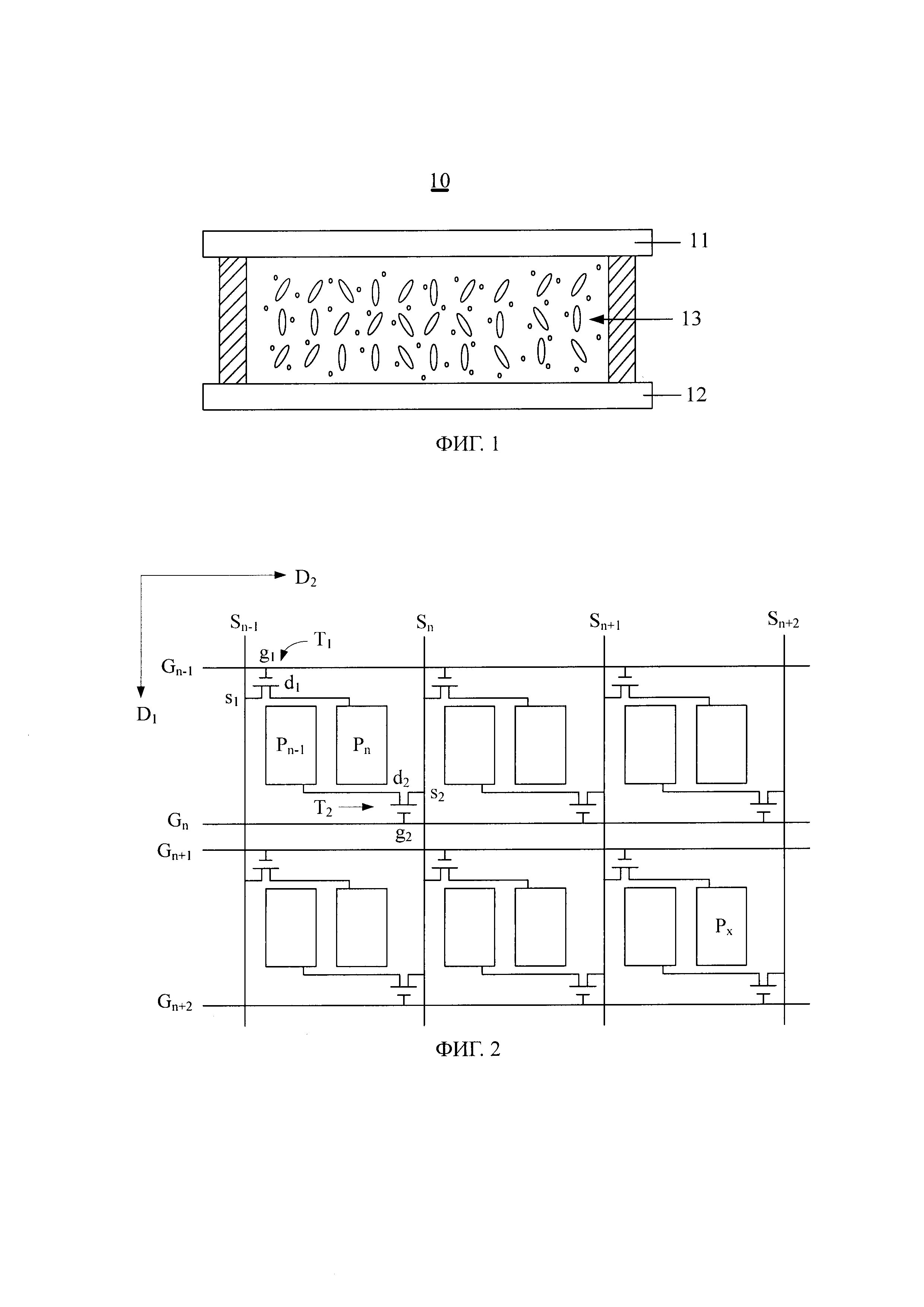

[0027] Фиг. 2 - схематический частичный вид пиксельной структуры жидкокристаллической панели отображения, показанной на фиг. 1; и

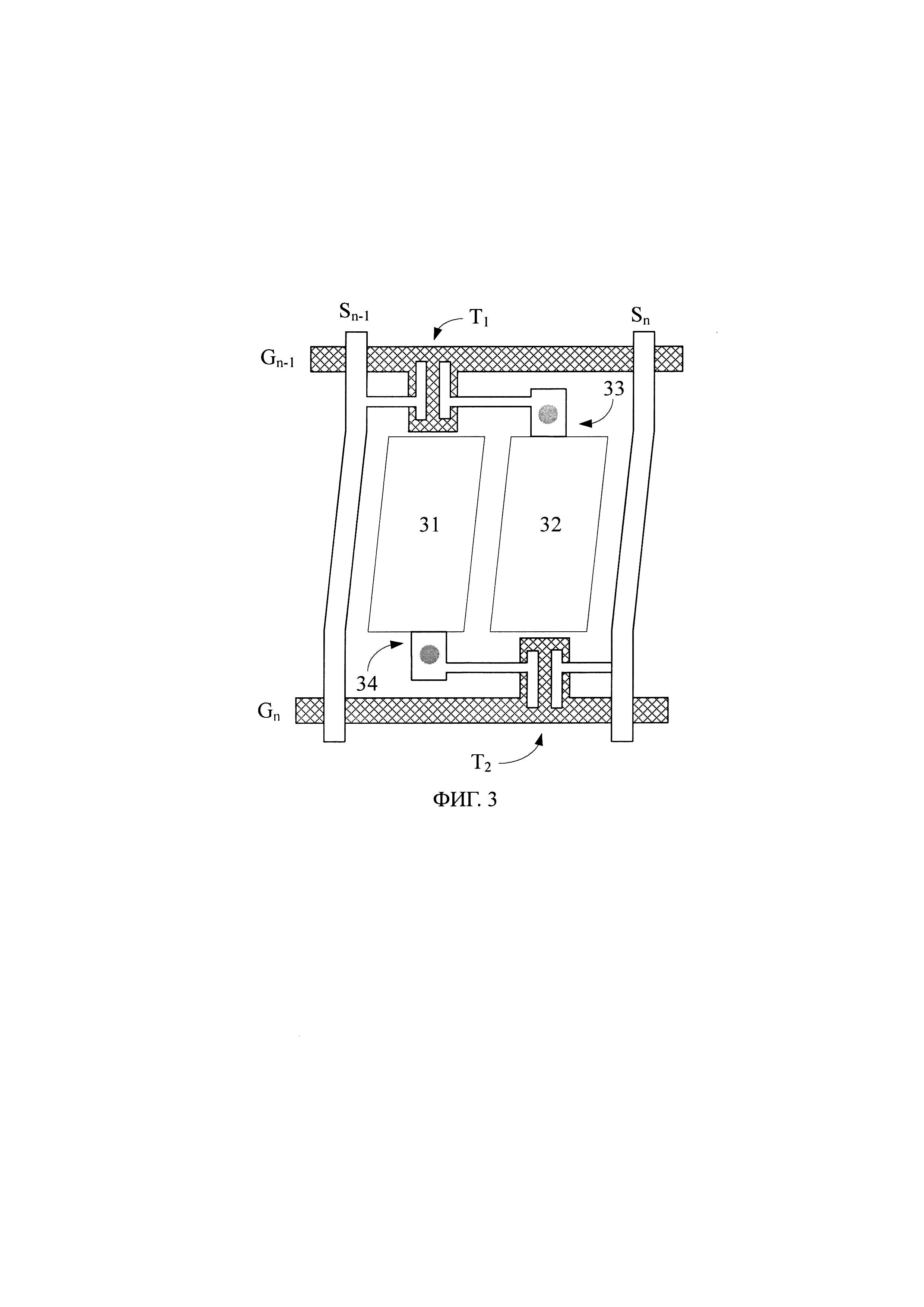

[0028] Фиг. 3 - схематический частичный вид подложки матрицы, имеющей пиксельную структуру, показанную на фиг. 2, в соответствии с изобретением.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

[0029] Ниже со ссылкой на прилагаемые чертежи вариантов осуществления изобретения технические решения в вариантах осуществления изобретения будут четко и полностью описаны. Очевидно, что варианты осуществления изобретения, описанные ниже, являются только частью вариантов осуществления изобретения, а не всеми вариантами осуществления. На основе описанных вариантов осуществления изобретения все другие варианты осуществления, полученные обычным специалистом в данной области техники без творческих усилий, относятся к объему правовой охраны изобретения.

[0030] Фиг. 1 - схематический структурный вид жидкокристаллической панели отображения в соответствии с предпочтительным вариантом осуществления изобретения, и фиг. 2 - схематический частичный вид пиксельной структуры жидкокристаллической панели отображения, показанной на фиг. 1. Со ссылкой на фиг. 1 и фиг. 2, жидкокристаллическая панель отображения 10 содержит первую подложку 11, вторую подложку 12 и жидкокристаллический слой 13. Первая подложка 11 и вторая подложка 12 расположены напротив друг друга, вторая подложка 12 может быть CF (подложкой цветного фильтра), и соответственно первая подложка 11 может быть подложкой матрицы TFT (тонкопленочного транзистора).

[0031] Первая подложка 11 содержит прозрачную основу и различные межсоединения, и пиксельные электроды, и т.д., расположенные на прозрачной основе. Например, первая подложка 11 содержит несколько (т.е. более одной) шин передачи данных Sn-1, Sn, Sn+1, Sn+2, несколько шин сканирования Gn-1, Gn, Gn+1, Gn+2, расположенные перпендикулярно шинам передачи данных Sn-1, Sn, Sn+1, Sn+2, и несколько пиксельных электродов Pn-1, Рn, …, Рх, определяемых шинами сканирования и шинами передачи данных. Шины сканирования Gn-1, Gn, Gn+1, Gn+2 соединены с драйвером затвора, шины передачи данных Sn-1, Sn, Sn+1, Sn+2 соединены с драйвером истока, драйвер затвора выполнен с возможностью (т.е. структурирован и расположен) подачи напряжений сканирования в пиксельные блоки Pn-1, Рn, …, Рх по соответствующим шинам сканирования, а драйвер истока выполнен с возможностью подачи напряжений шкалы оттенков серого в пиксельные блоки Рn-1, Рn, …, Рх по соответствующим шинам передачи данных.

[0032] Со ссылкой на фиг. 2, каждые две соседние шины передачи данных и соответствующие две соседние шины сканирования вместе определяют области апертуры двух пикселей с одинаковой структурой, каждая область апертуры пикселя содержит один пиксельный электрод, и далее в данном документе это осуществление берет области апертуры двух пикселей, определяемых первой шиной передачи данных Sn-1, второй шиной передачи данных Sn, первой шиной сканирования Gn-1 и второй шиной сканирования Gn, в качестве примера в целях иллюстрации.

[0033] Первая шина передачи данных Sn-1 и вторая шина передачи данных Sn проходят вдоль первого направления D1 и расположены на расстоянии друг от друга вдоль второго направления D2, первая шина сканирования Gn-1 и вторая шина сканирования Gn проходят вдоль второго направления D2 и расположены на расстоянии друг от друга вдоль первого направления D1, и первое направление D1, и второе направление D2 взаимно перпендикулярны.

[0034] Первый пиксельный электрод Pn-1 и второй пиксельный электрод Рn расположены между первой шиной передачи данных Sn-1 и второй шиной передачи данных Sn и расположены на расстоянии друг от друга вдоль второго направления D2. Первый пиксельный электрод Pn-1 расположен рядом с первой шиной передачи данных Sn-1, второй пиксельный электрод Рn расположен рядом со второй шиной передачи данных Sn, первая шина передачи данных Sn-1 предназначена для подачи напряжения шкалы оттенков серого на второй пиксельный электрод Pn, а вторая шина передачи данных Sn предназначена для подачи напряжения шкалы оттенков серого на первый пиксельный электрод Рn-1.

[0035] Первая шина передачи данных Sn-1 и вторая шина передачи данных Sn имеют первый тонкопленочный транзистор Т1 и второй тонкопленочный транзистор Т2, расположенные между ними, первый тонкопленочный транзистор T1 и второй тонкопленочный транзистор Т2 расположены на расстоянии друг от друга вдоль первого направления D1 и соответственно на противоположных сторонах первого пиксельного электрода Pn-1, а также второго пиксельного электрода Рn. Первый пиксельный электрод Pn-1 и второй пиксельный электрод Рn выровнены относительно друг друга вдоль второго направления D2.

[0036] Более того, первый пиксельный электрод Pn-1, второй пиксельный электрод Рn, первый тонкопленочный транзистор T1 и второй тонкопленочный транзистор Т2 дополнительно расположены между первой шиной сканирования Gn-1 и второй шиной сканирования Gn. Первая шина сканирования Gn-1 расположена рядом с первым тонкопленочным транзистором T1 и электрически соединена с затвором g1 первого тонкопленочного транзистора T1, вторая шина сканирования Gn расположена рядом со вторым тонкопленочным транзистором Т2 и электрически соединена с затвором g2 второго тонкопленочного транзистора Т2.

[0037] Кроме того, первая шина передачи данных Sn-1 электрически соединена с истоком s1 первого тонкопленочного транзистора T1, второй пиксельный электрод Рn электрически соединен со стоком d1 первого тонкопленочного транзистора T1. Вторая шина передачи данных Sn электрически соединена с истоком s2 второго тонкопленочного транзистора Т2, и первый пиксельный электрод Pn-1 электрически соединен со стоком d2 второго тонкопленочного транзистора Т2.

[0038] Фиг. 3 - схематический частичный вид подложки матрицы, имеющей пиксельную структуру, показанную на фиг. 2, в соответствии с изобретением. Вместе с фиг. 3, первый пиксельный электрод Pn-1 и второй пиксельный электрод Рn соответственно имеют первую область апертуры 31 и вторую область апертуры 32, первая область апертуры 31 и вторая область апертуры 32 выровнены относительно друг друга вдоль второго направления D2. Подложка матрицы 11 дополнительно сформирована с первым сквозным отверстием 33 и вторым сквозным отверстием 34. Первое сквозное отверстие 33 и первый тонкопленочный транзистор T1 расположены на расстоянии друг от друга вдоль второго направления D2, второе сквозное отверстие 34 и второй тонкопленочный транзистор Т2 расположены на расстоянии друг от друга вдоль второго направления D2, второй пиксельный электрод Рn электрически соединен со стоком d1 первого тонкопленочного транзистора T1 через первое сквозное отверстие 33, а первый пиксельный электрод Pn-1 электрически соединен со стоком d2 второго тонкопленочного транзистора Т2 через второе сквозное отверстие 34.

[0039] В другом варианте осуществления первая шина передачи данных Sn-1 может быть электрически соединена со стоком d1 первого тонкопленочного транзистора T1, второй пиксельный электрод Рn электрически соединен с истоком s1 первого тонкопленочного транзистора T1, вторая шина передачи данных Sn электрически соединена со стоком d2 второго тонкопленочного транзистора Т2, и первый пиксельный электрод Pn-1 электрически соединен с истоком s2 второго тонкопленочного транзистора Т2. В этой ситуации второй пиксельный электрод Рn электрически соединен с истоком s1 первого тонкопленочного транзистора Т1 через первое сквозное отверстие 33, а первый пиксельный электрод Pn-1 электрически соединен с истоком s2 второго тонкопленочного транзистора Т2 через второе сквозное отверстие 34.

[0040] Варианты осуществления изобретения могут увеличить пространство компоновки компонентов в направлении продолжения шины передачи данных, например пространство компоновки компонентов между первой шиной передачи данных Sn-1 и вторым пиксельным электродом Рn вдоль второго направления D2, такое, что первое сквозное отверстие 33 и первый тонкопленочный транзистор T1 расположены на одной прямой линии вдоль второго направления D2, второе сквозное отверстие 34 и второй тонкопленочный транзистор Т2 расположены на одной прямой линии вдоль второго направления D2, и первая область апертуры 31 и вторая область апертуры 32 расположены на одной прямой линии. В результате может быть увеличена относительная апертура пикселя при одновременном обеспечении качества отображения жидкокристаллической панели отображения 10.

[0041] Вариант осуществления изобретения также предусматривает жидкокристаллическое устройство отображения. Жидкокристаллическое устройство отображения содержит жидкокристаллическую панель отображения 10, как показано на фиг. 1, и, конечно, содержит подложку матрицы 11, имеющую пиксельную структуру в соответствии с вариантом осуществления, связанным с фиг. 2 и фиг. 3, и поэтому имеет такой же технический эффект.

[0042] Хотя изобретение было описано с точки зрения того, что в настоящее время считается наиболее практичными и предпочтительными вариантами осуществления, следует понимать, что изобретение не должно ограничиваться раскрытыми вариантами осуществления. Напротив, оно предназначено для охвата различных модификаций и аналогичных устройств, включенных в объем и содержание прилагаемой формулы изобретения, которая должна предоставляться с самой широкой интерпретацией, чтобы охватить все такие модификации и аналогичные структуры.