Результат интеллектуальной деятельности: МАГНИТОРЕЗИСТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Вид РИД

Изобретение

Перекрестные ссылки на родственные заявки

Данная заявка основана и притязает на приоритет предварительной заявки на патент США номер 61/949054, поданной 6 марта 2014 года, содержимое которой полностью содержится в данном документе по ссылке.

Область техники, к которой относится изобретение

Варианты осуществления относятся к магниторезистивному запоминающему устройству.

Уровень техники

В последние годы, предлагаются различные новые запоминающие устройства в качестве альтернативных запоминающих устройств для флэш-памяти или динамического оперативного запоминающего устройства (DRAM). Такие запоминающие устройства включают в себя магниторезистивное RAM (MRAM). MRAM, из числа новых запоминающих устройств, может работать на высокой скорости и может относительно легко сокращаться в размерах.

Краткое описание чертежей

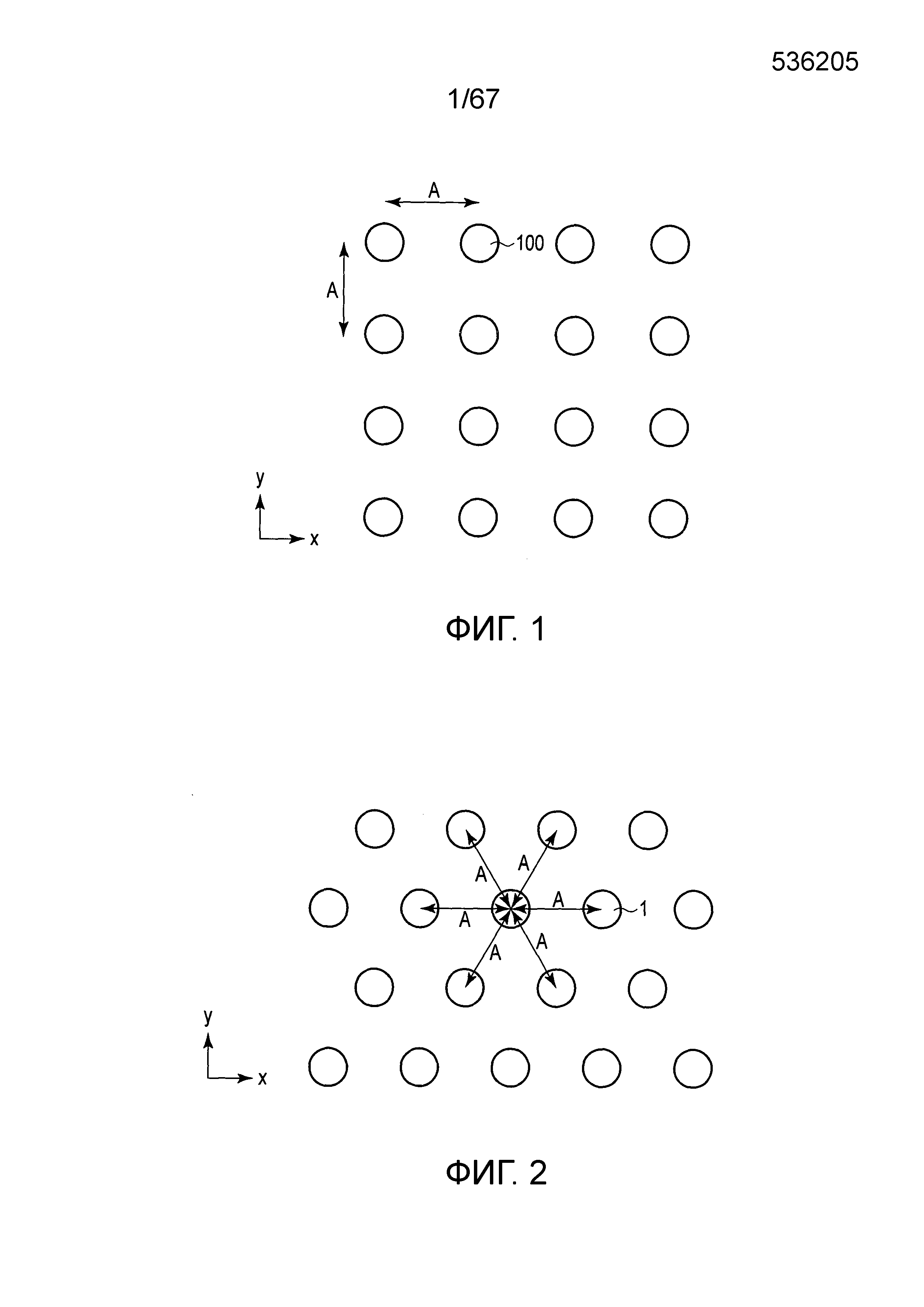

Фиг. 1 иллюстрирует пример компоновки запоминающих элементов запоминающих ячеек запоминающего устройства;

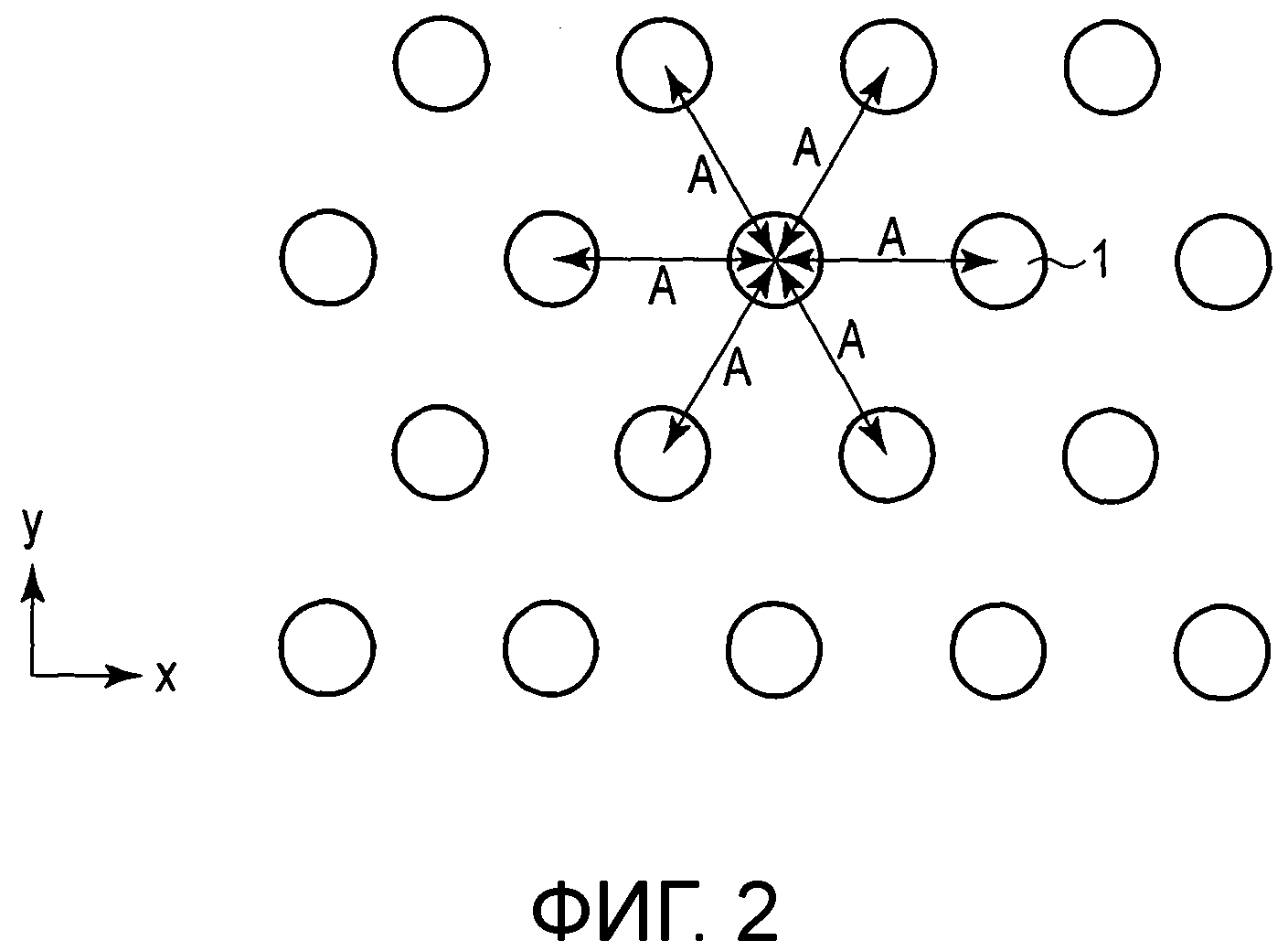

Фиг. 2 иллюстрирует первый пример компоновки запоминающих элементов запоминающих ячеек запоминающего устройства по первому варианту осуществления;

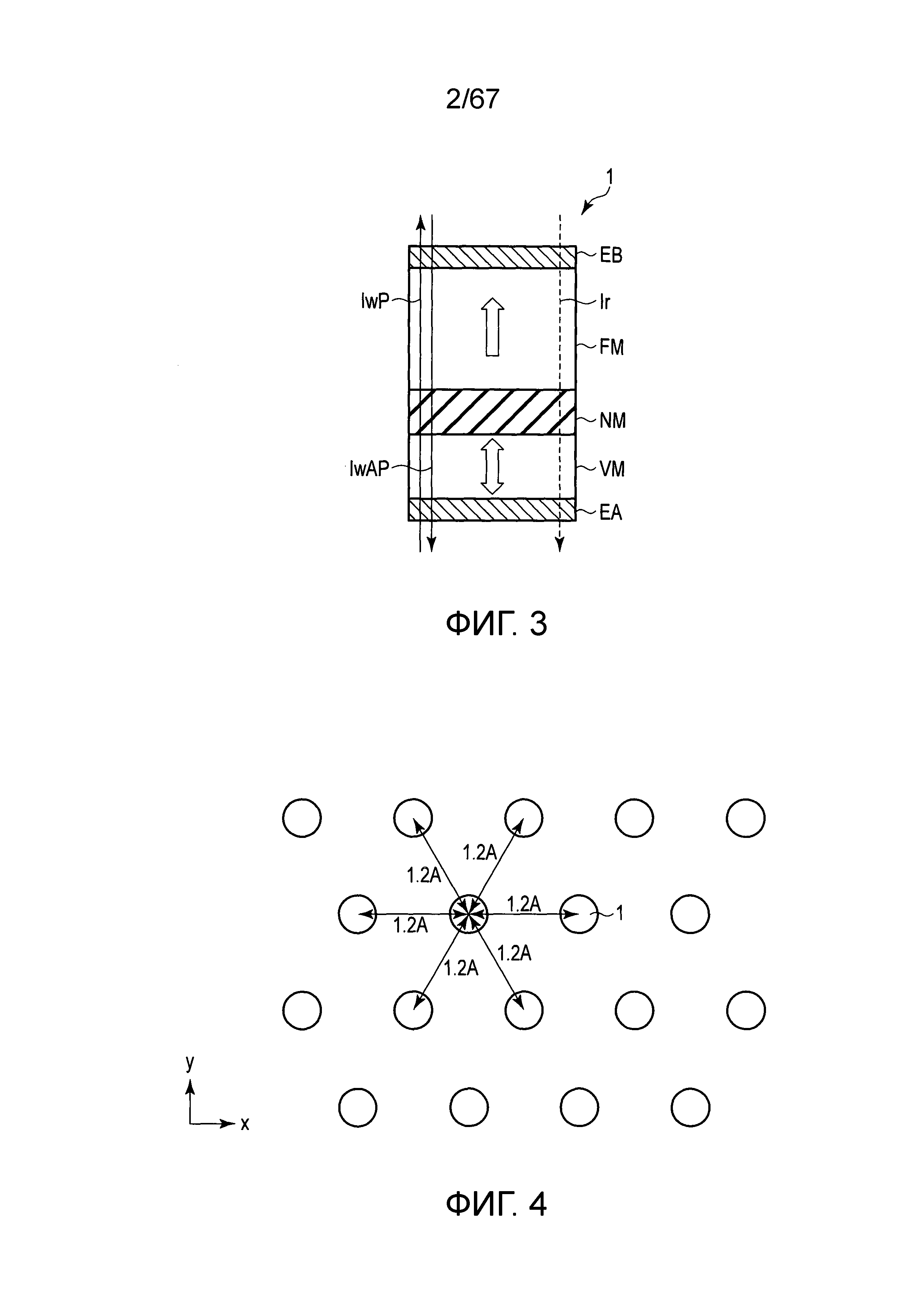

Фиг. 3 иллюстрирует структуру MTJ-элемента по первому варианту осуществления;

Фиг. 4 иллюстрирует второй пример компоновки запоминающих элементов запоминающих ячеек запоминающего устройства по первому варианту осуществления;

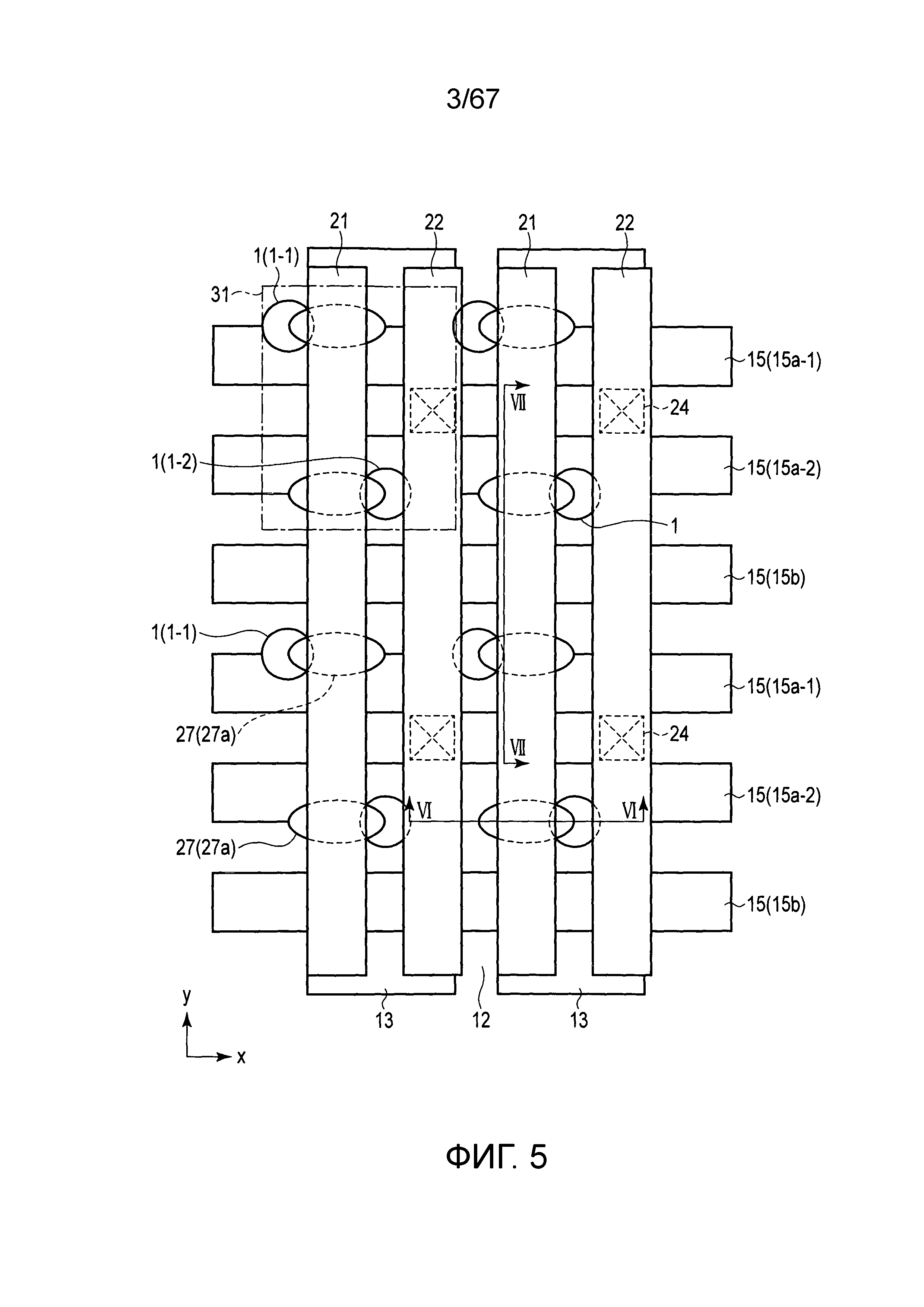

Фиг. 5 иллюстрирует вид запоминающего устройства по первому примеру первого варианта осуществления при виде сверху;

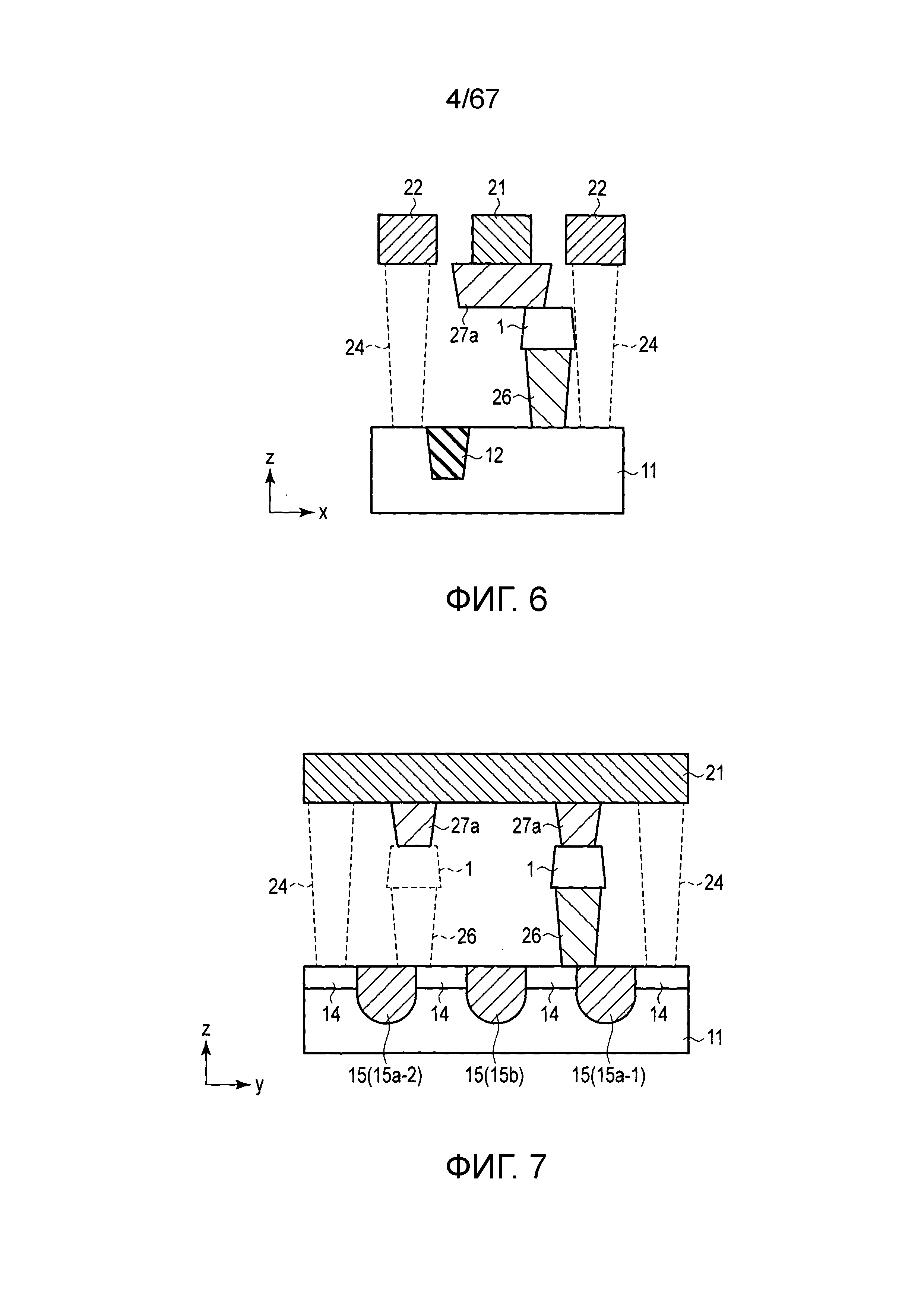

Фиг. 6 иллюстрирует вид вдоль линии VI-VI по фиг. 5;

Фиг. 7 иллюстрирует вид вдоль линии VII-VII по фиг. 5;

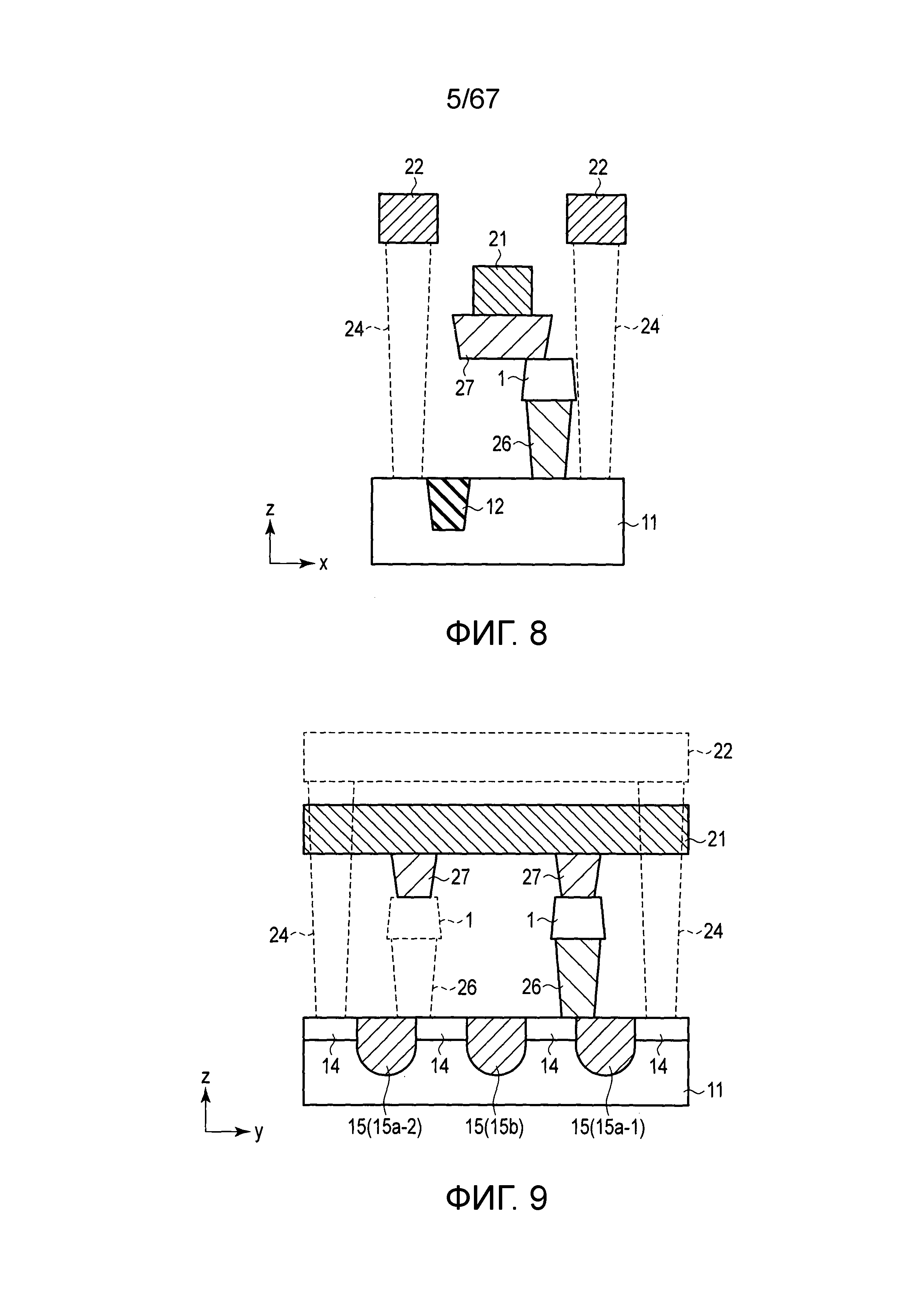

Фиг. 8 иллюстрирует вид вдоль линии VI-VI по фиг. 5;

Фиг. 9 иллюстрирует вид вдоль линии VII-VII по фиг. 5;

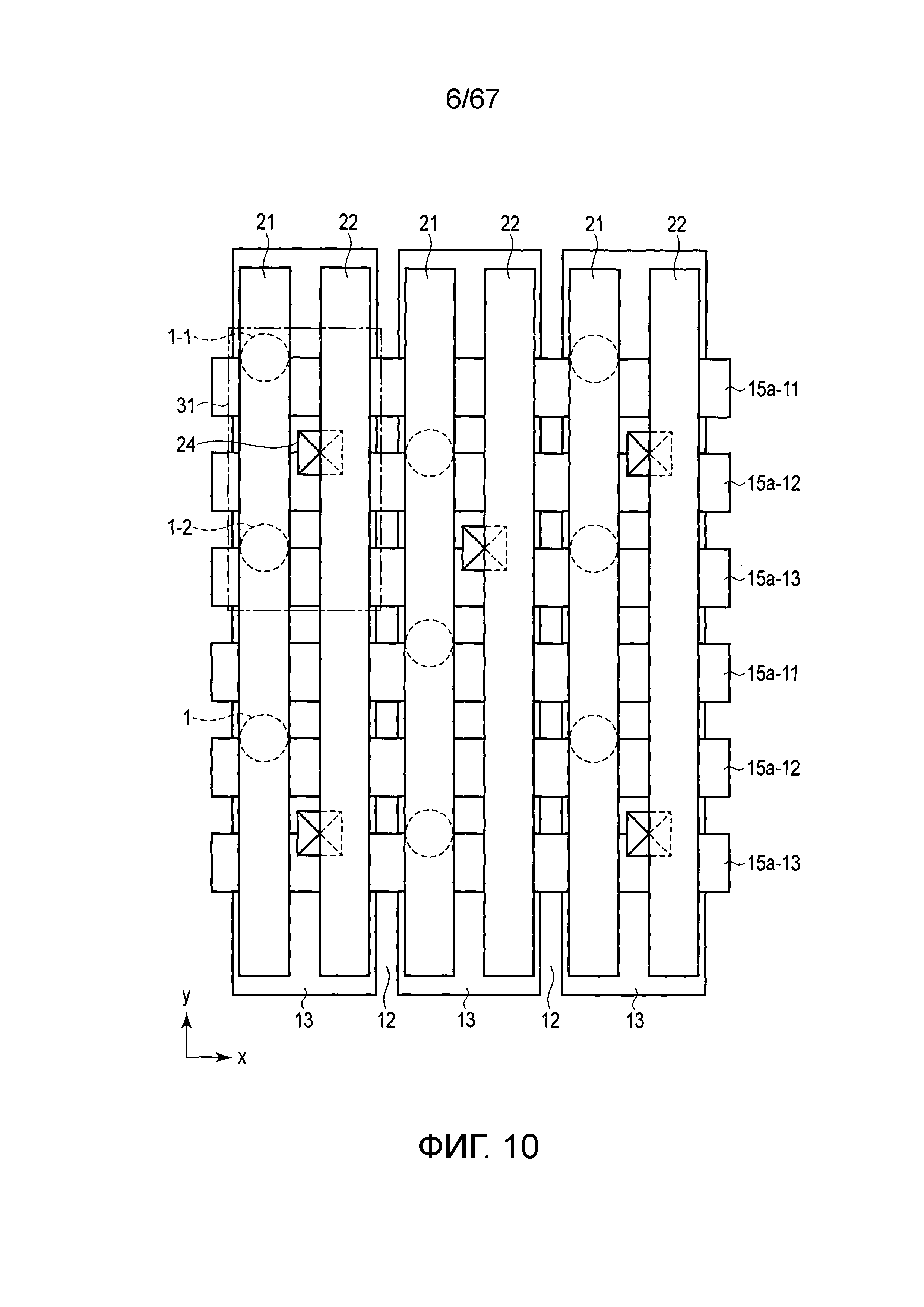

Фиг. 10 иллюстрирует вид запоминающего устройства по третьему примеру первого варианта осуществления при виде сверху;

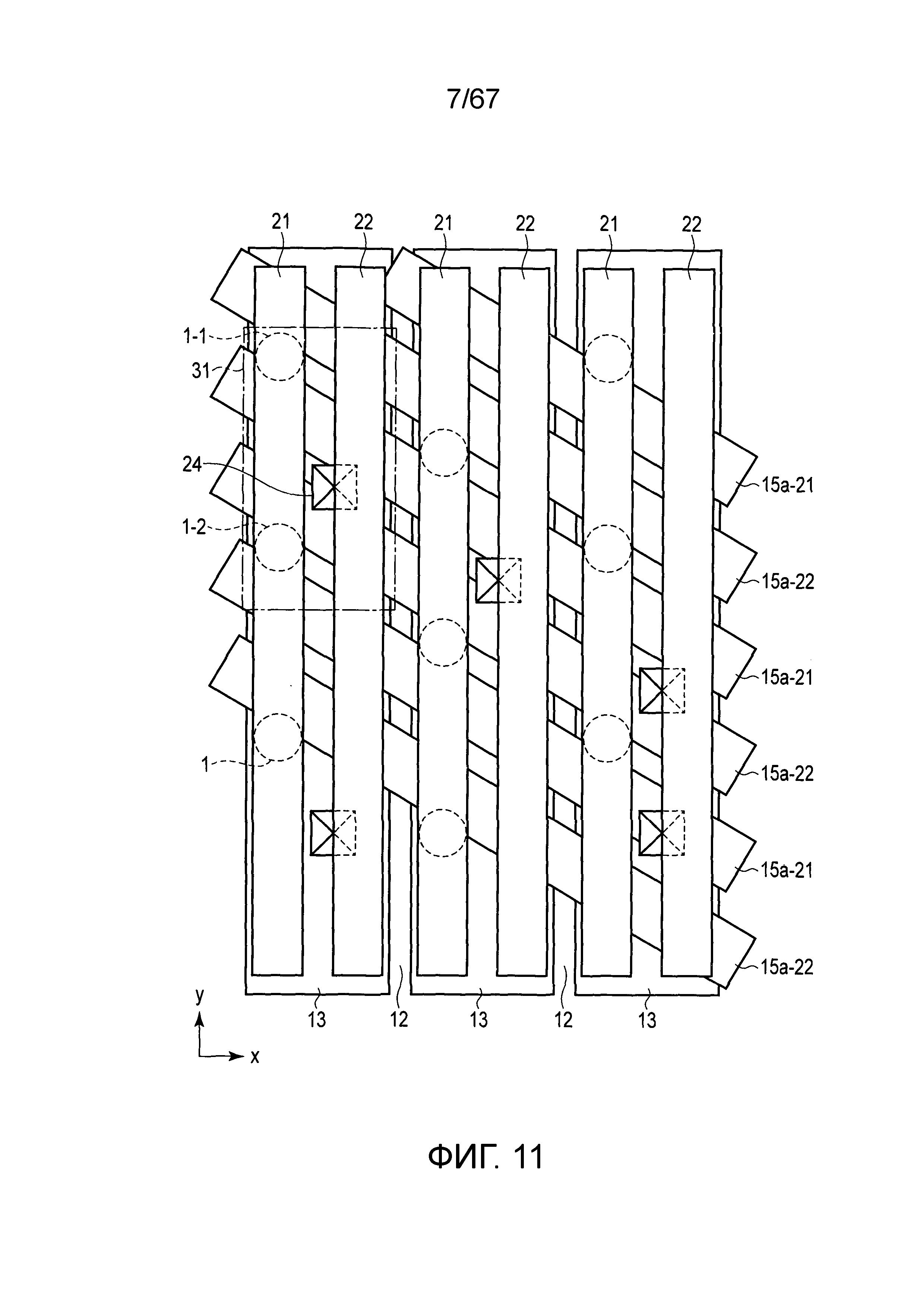

Фиг. 11 иллюстрирует вид запоминающего устройства по четвертому примеру первого варианта осуществления при виде сверху;

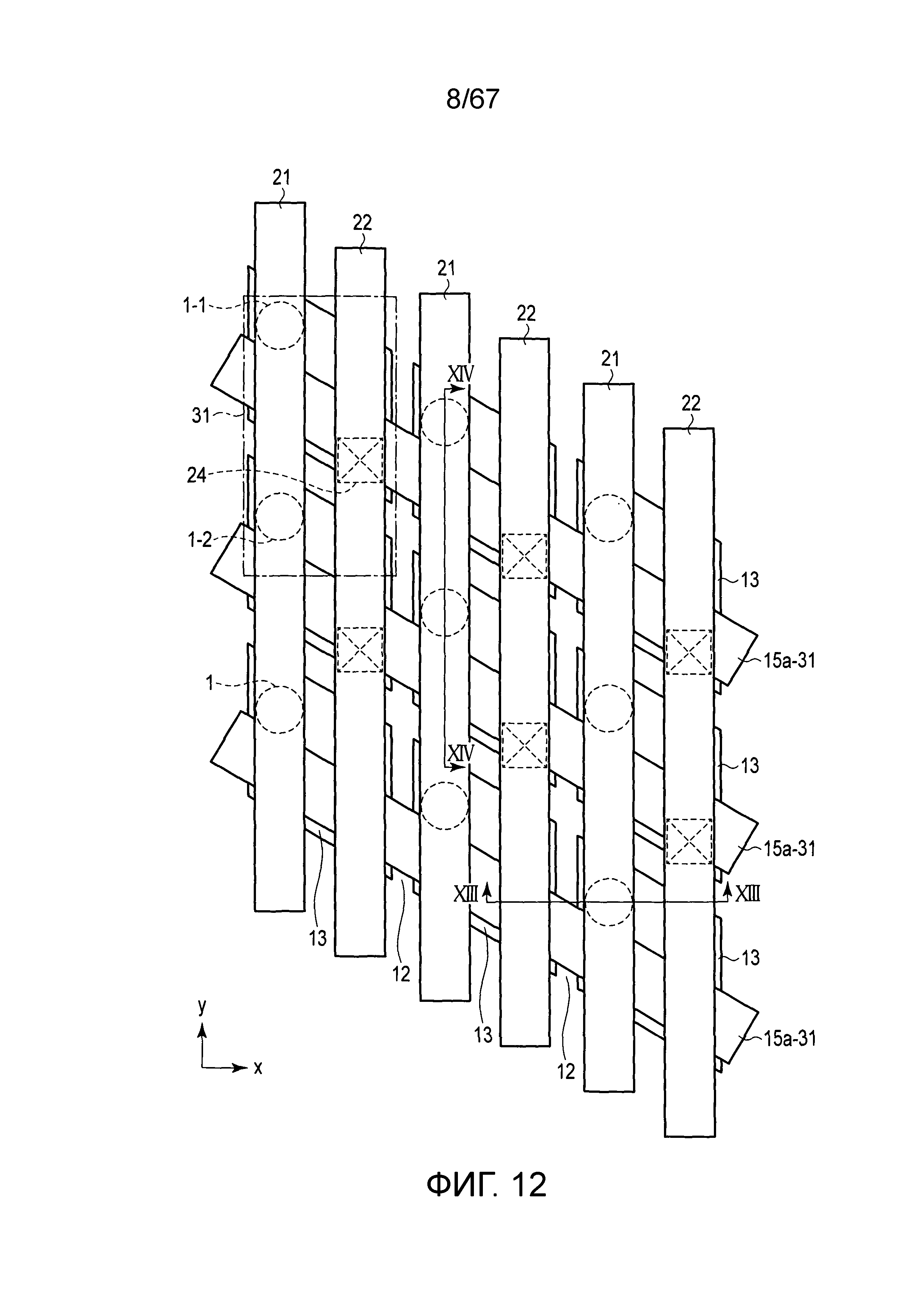

Фиг. 12 иллюстрирует вид запоминающего устройства по пятому примеру первого варианта осуществления при виде сверху;

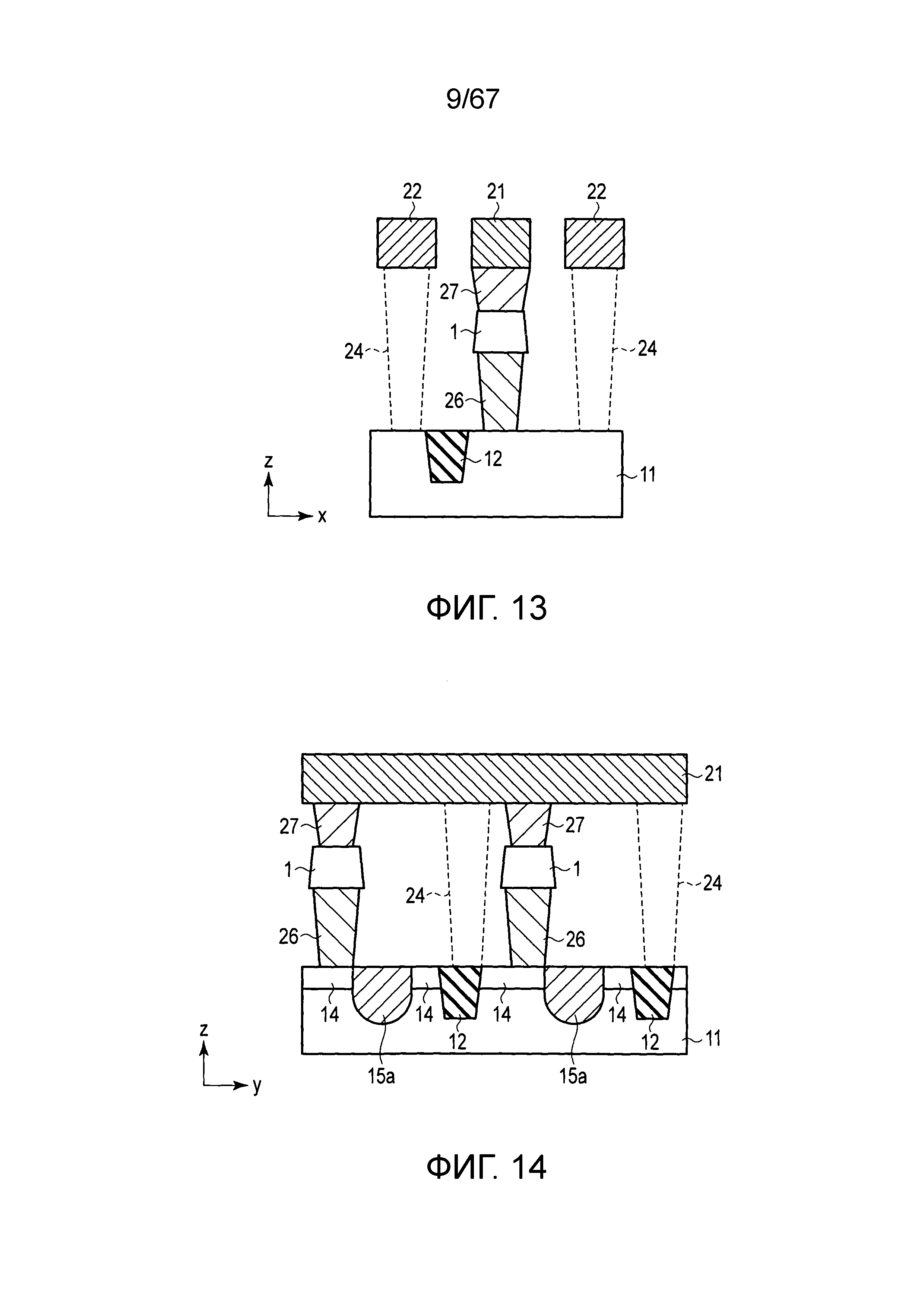

Фиг. 13 иллюстрирует вид вдоль линии XIII-XIII по фиг. 12;

Фиг. 14 иллюстрирует вид вдоль линии XIV-XIV по фиг. 12;

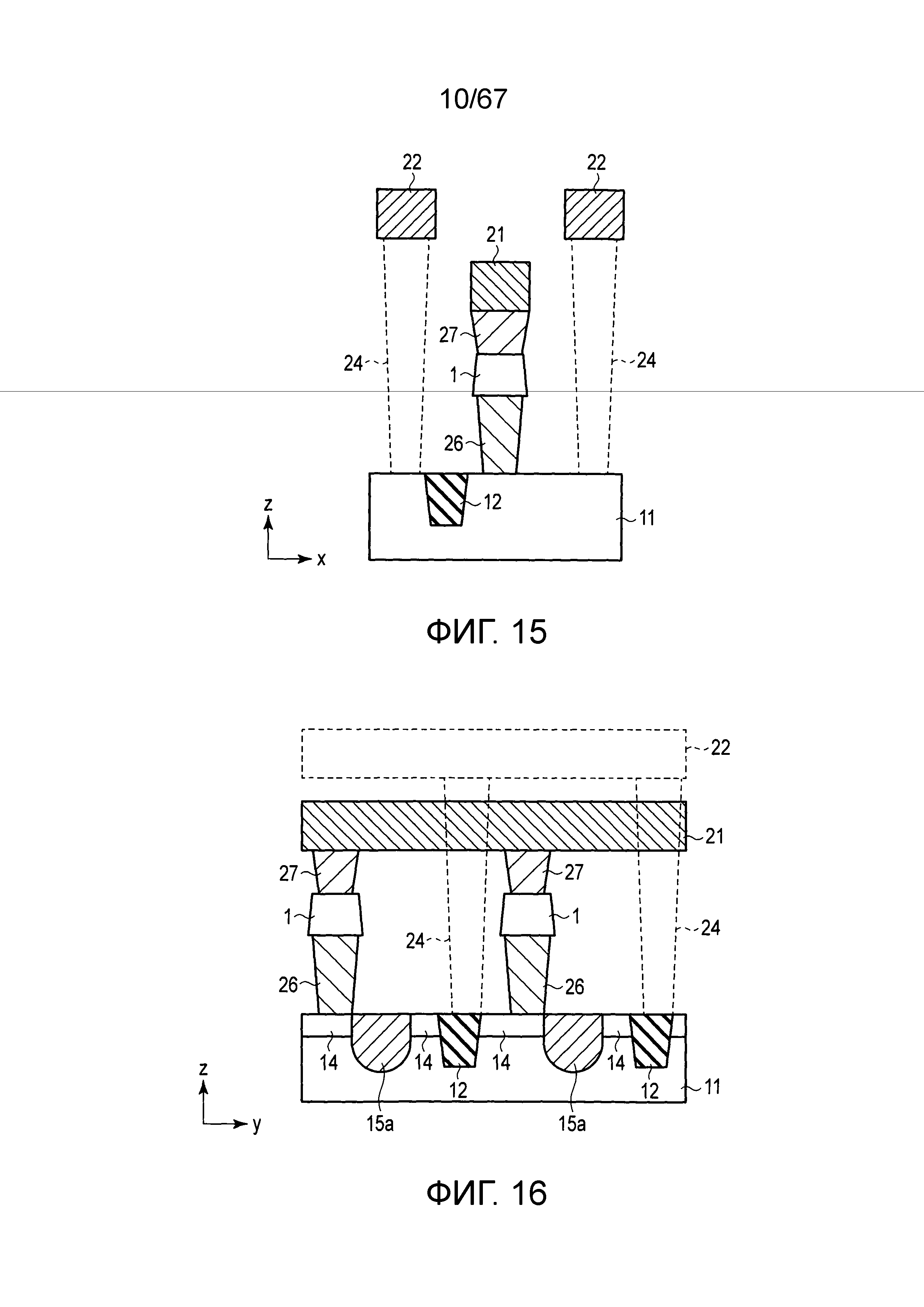

Фиг. 15 иллюстрирует вид вдоль линии XIII-XIII по фиг. 12;

Фиг. 16 иллюстрирует вид вдоль линии XIV-XIV по фиг. 12;

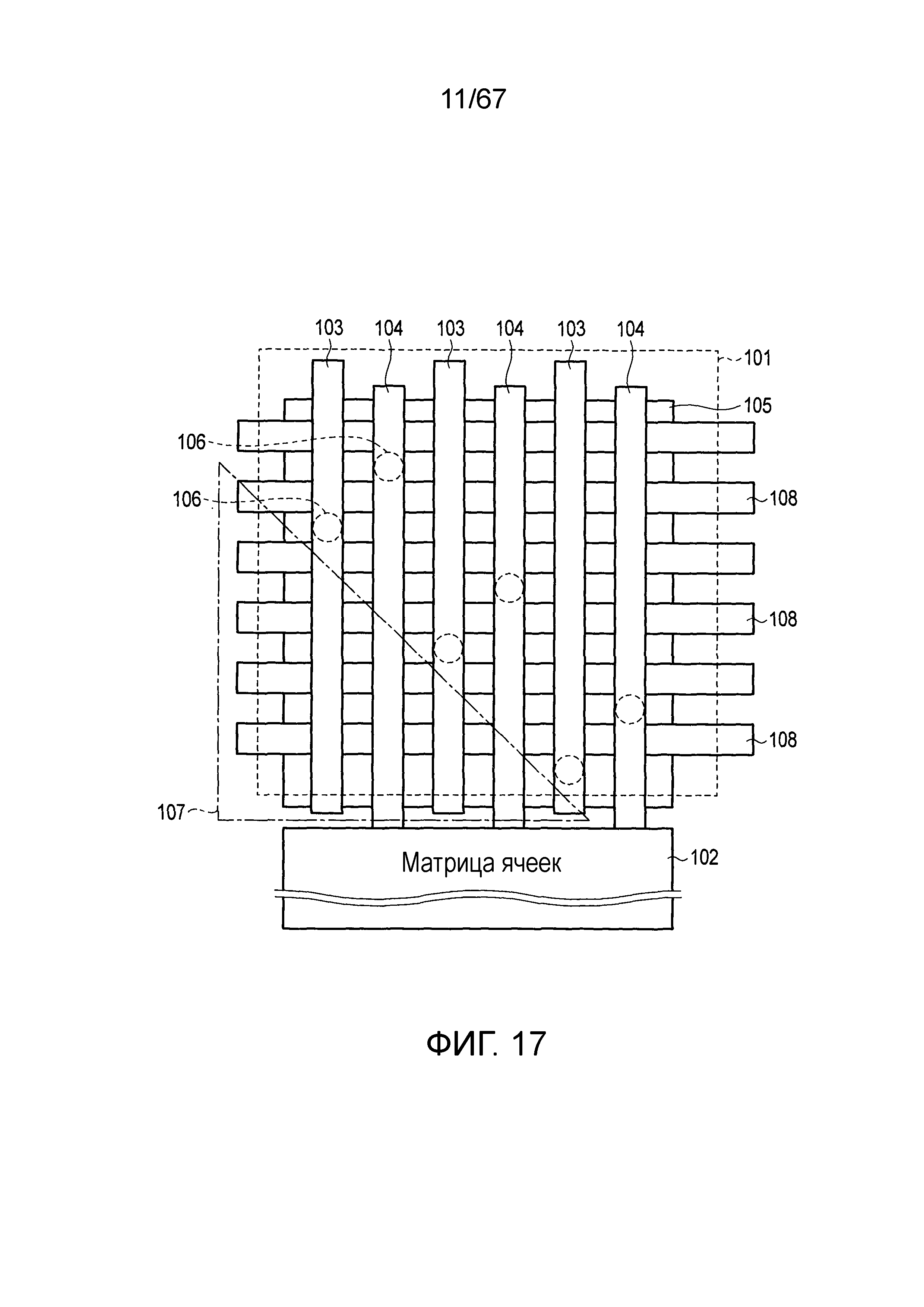

Фиг. 17 иллюстрирует вид окрестности границы матрицы ячеек для справки при виде сверху;

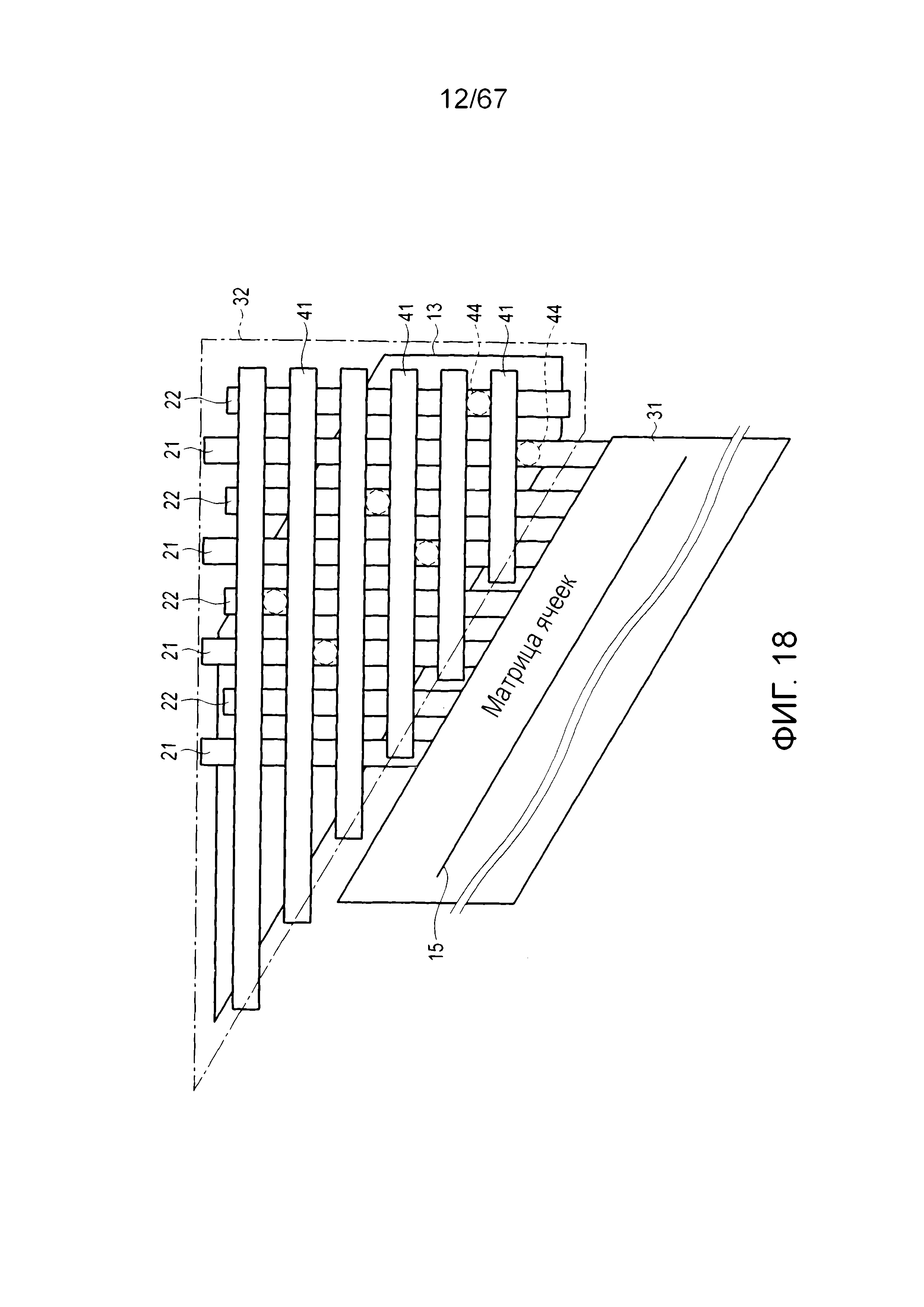

Фиг. 18 иллюстрирует вид окрестности границы матрицы ячеек по второму варианту осуществления при виде сверху;

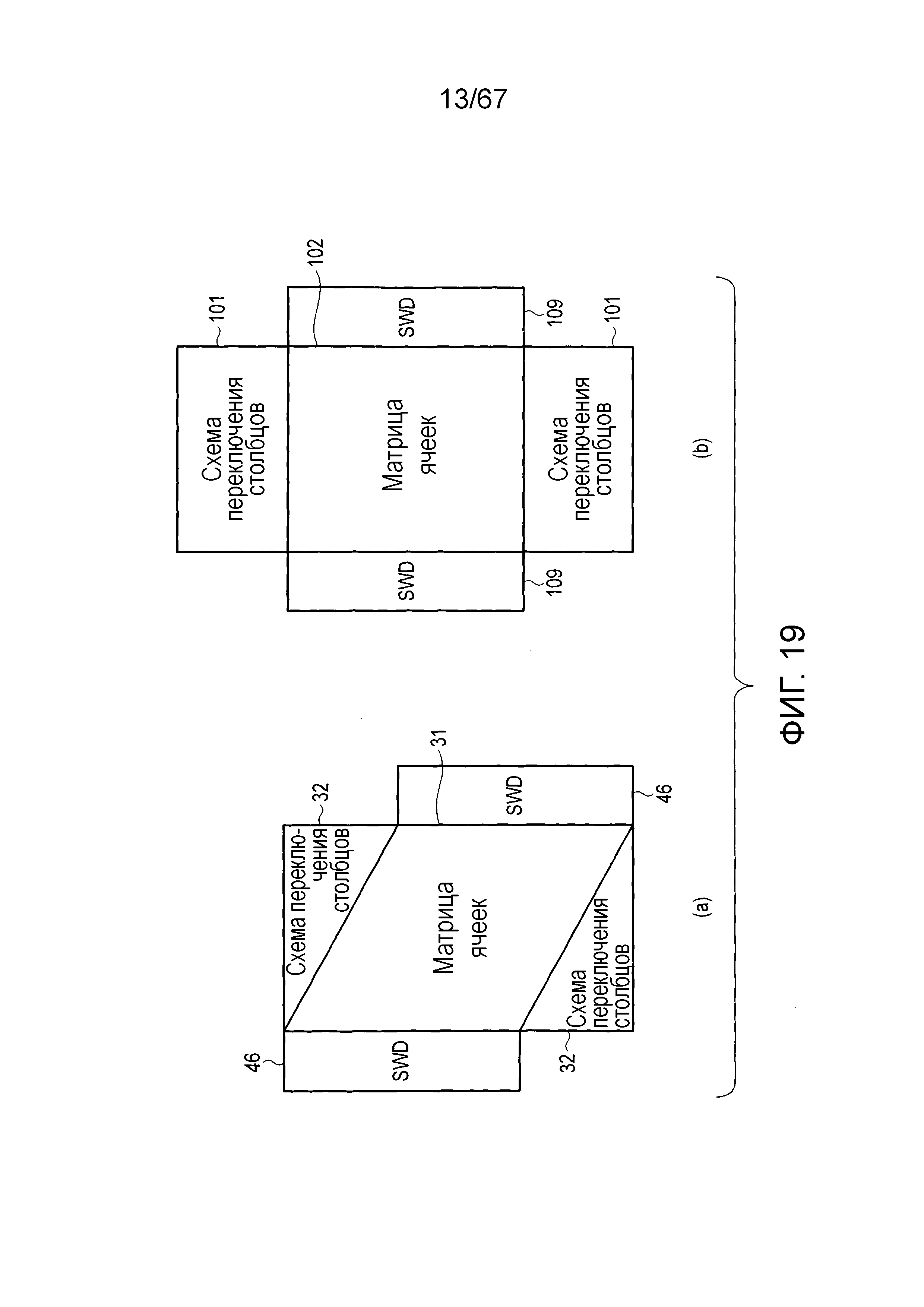

Фиг. 19 иллюстрирует схемы размещения части запоминающих устройств по второму варианту осуществления и для справки;

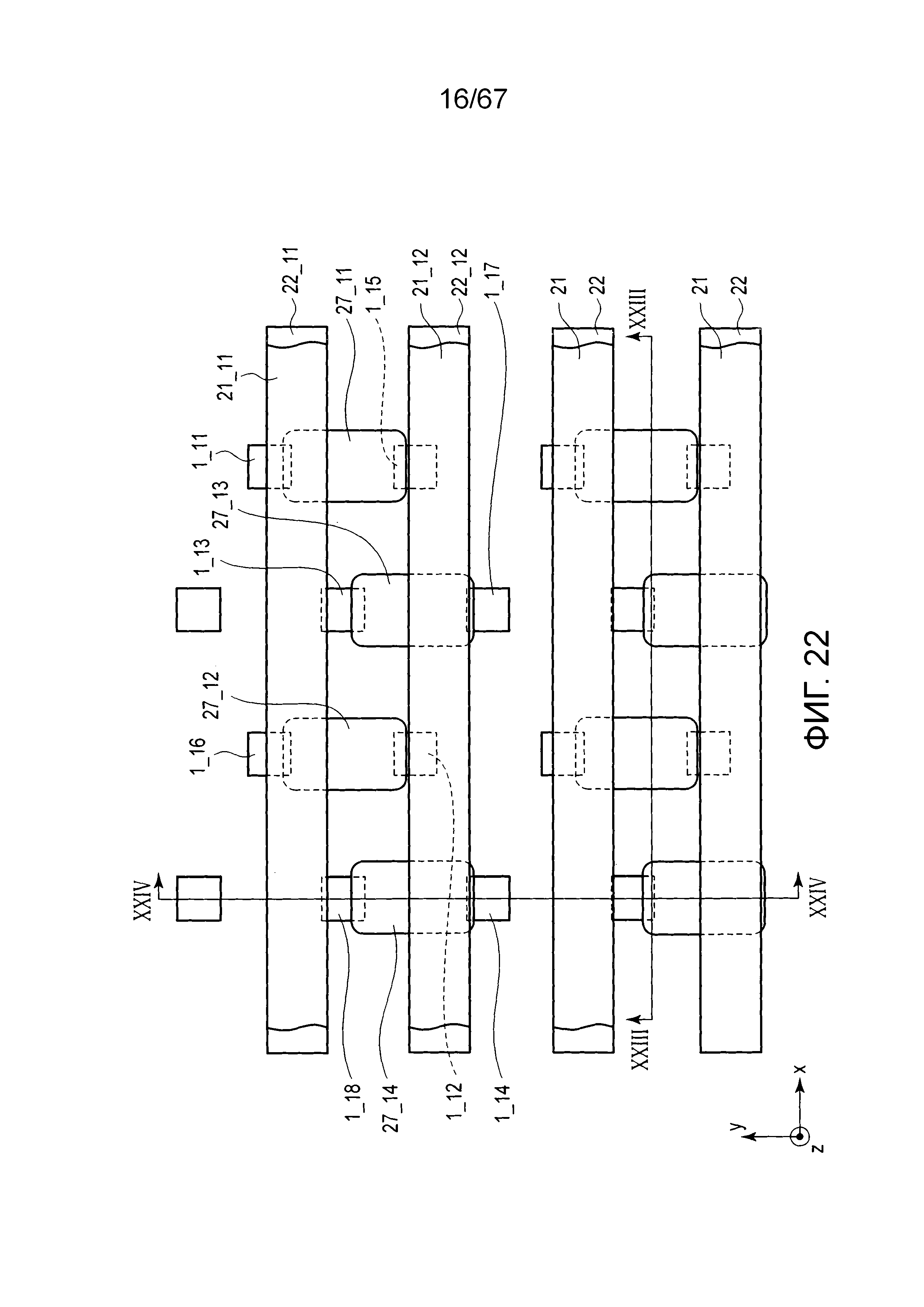

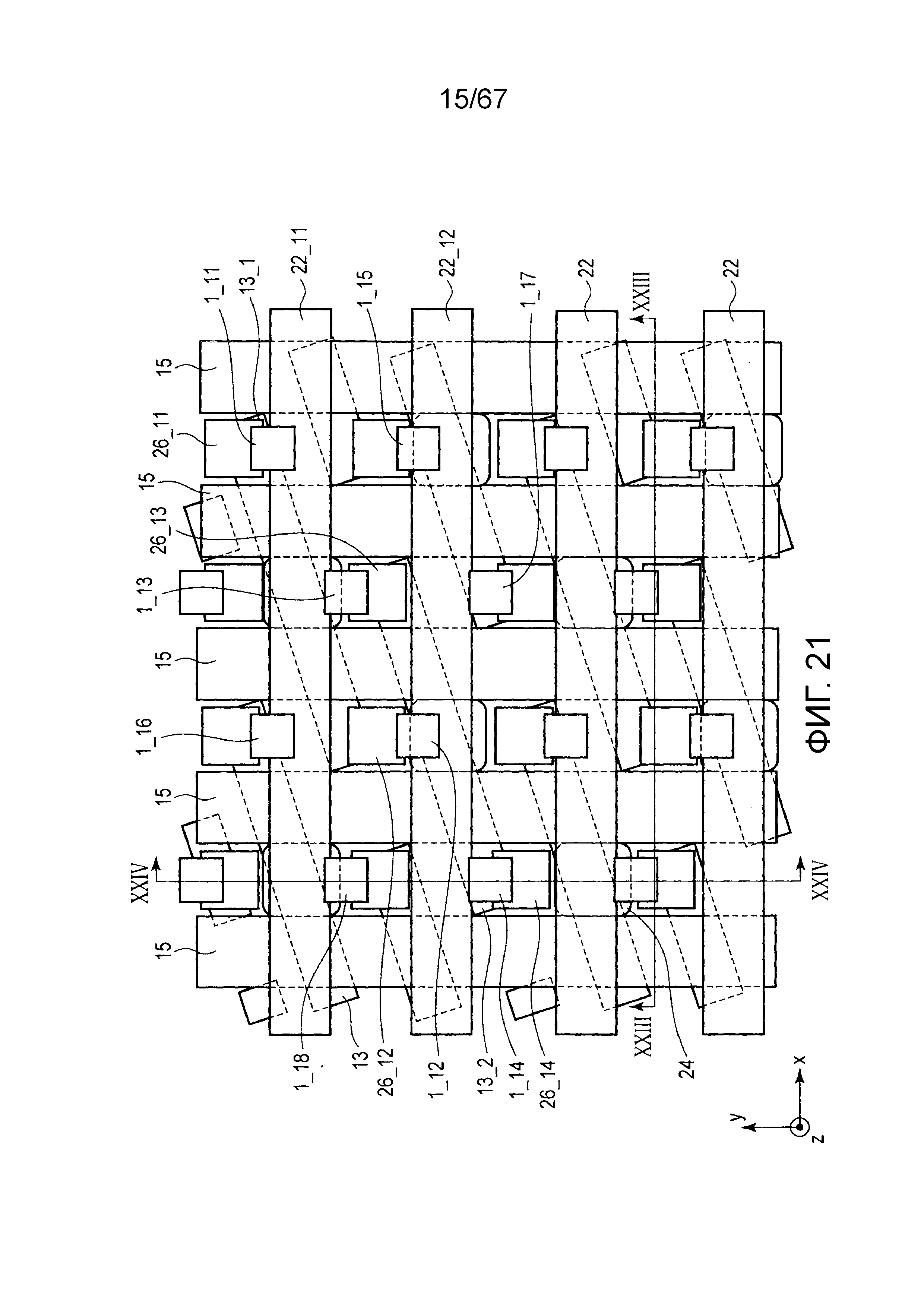

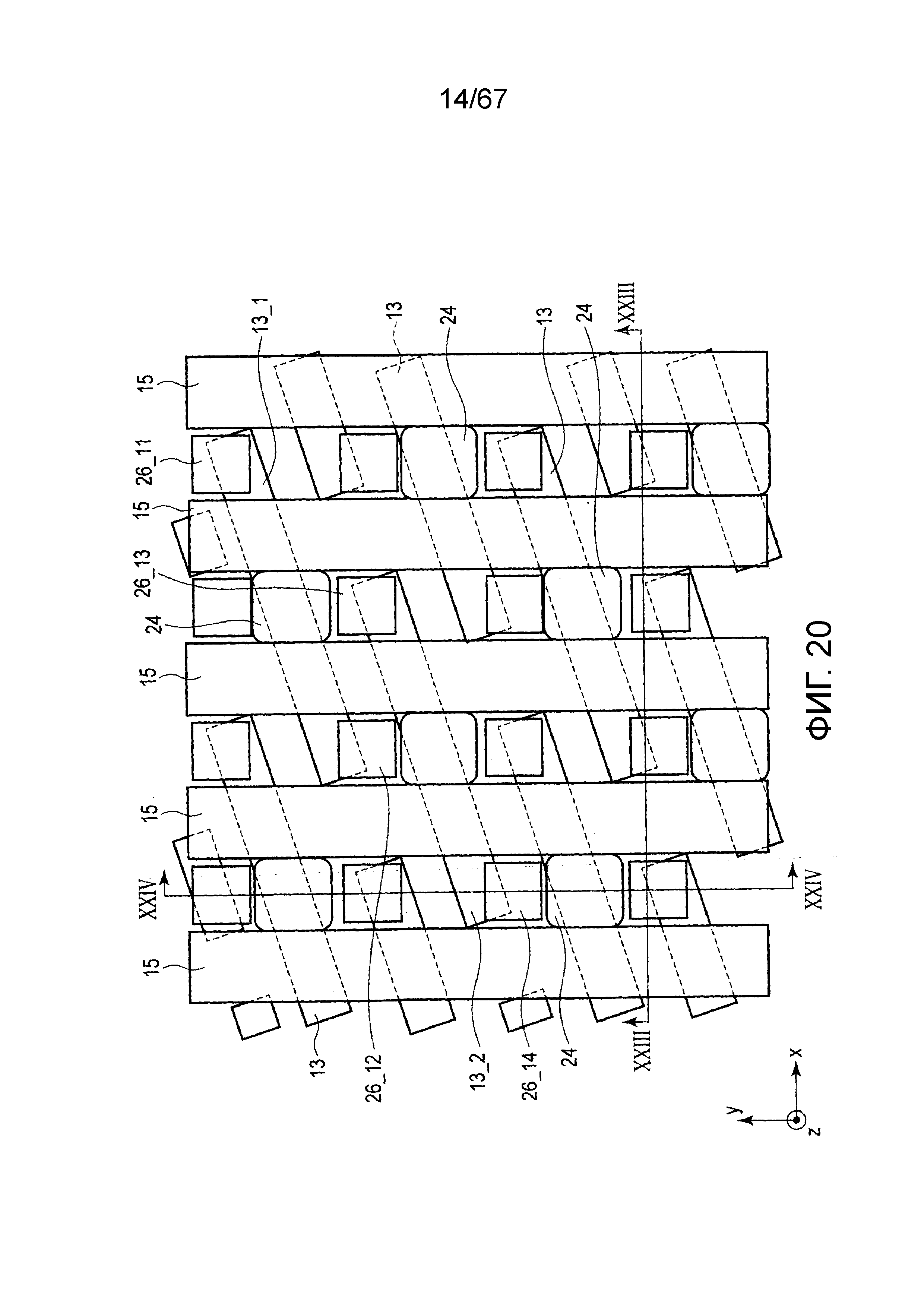

Фиг. 20-22 иллюстрируют виды части запоминающего устройства по первому примеру третьего варианта осуществления при виде сверху;

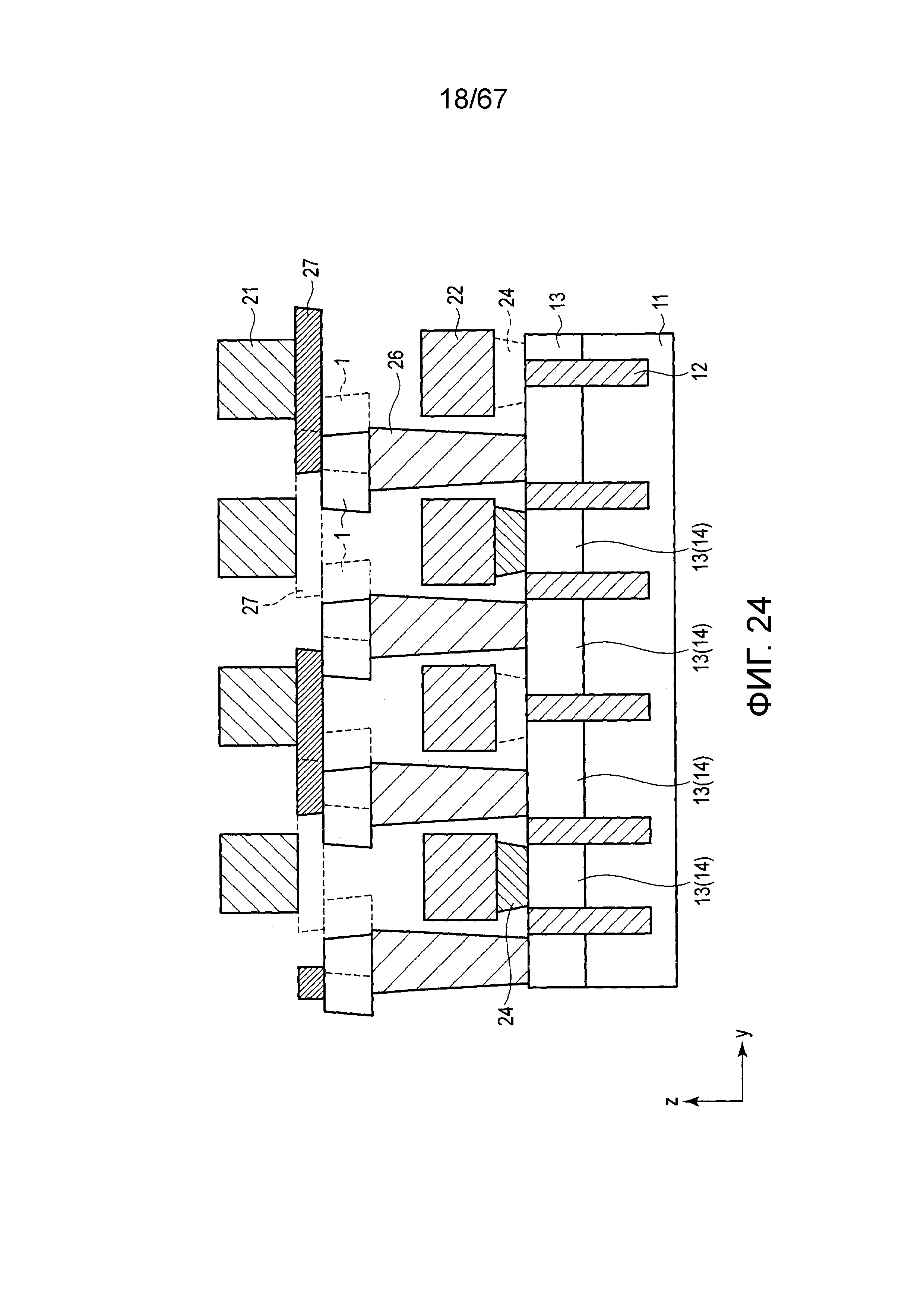

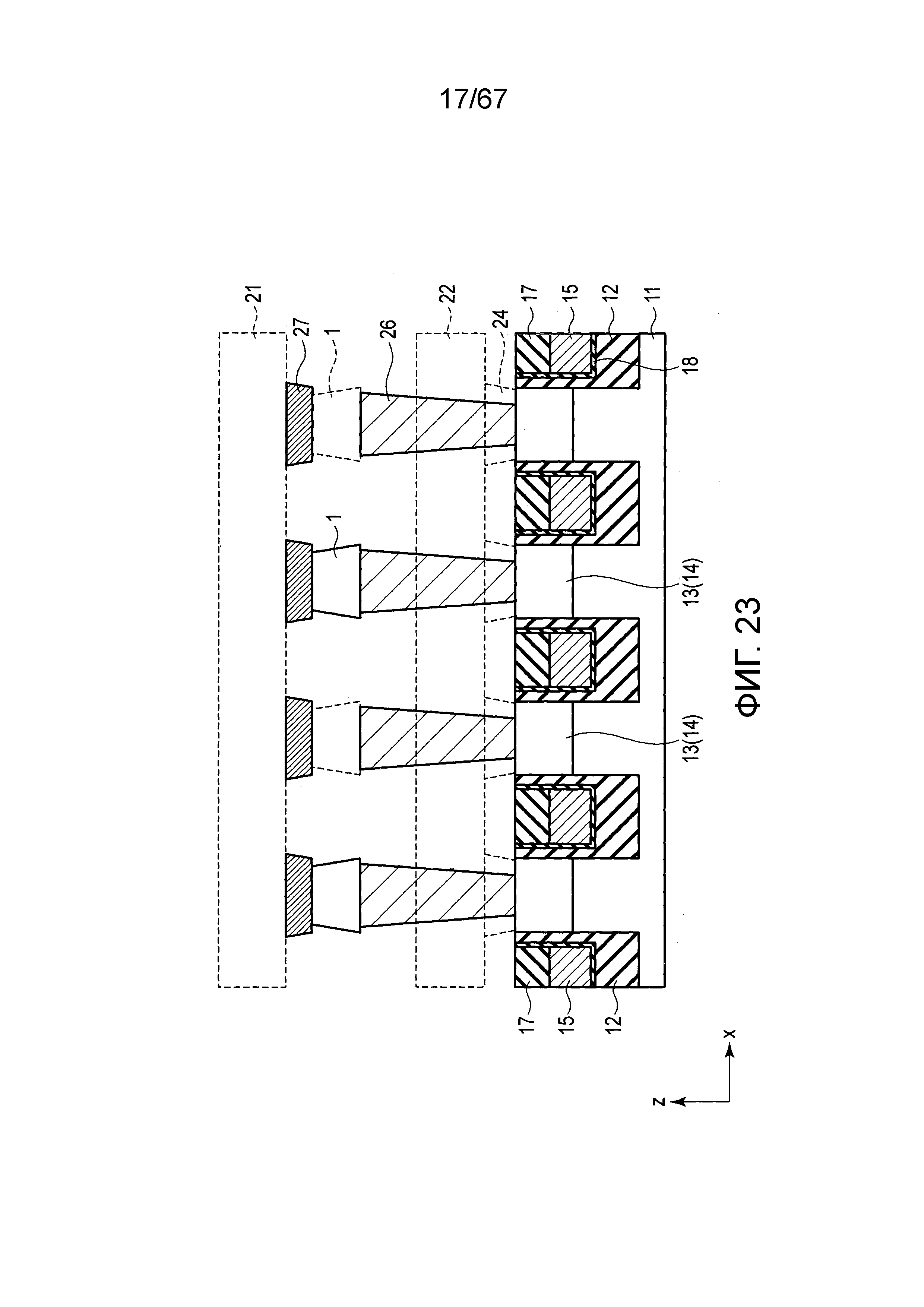

Фиг. 23 и 24 иллюстрируют виды вдоль линии XXIII-XXIII и линии XXIV-XXIV по фиг. 20, соответственно;

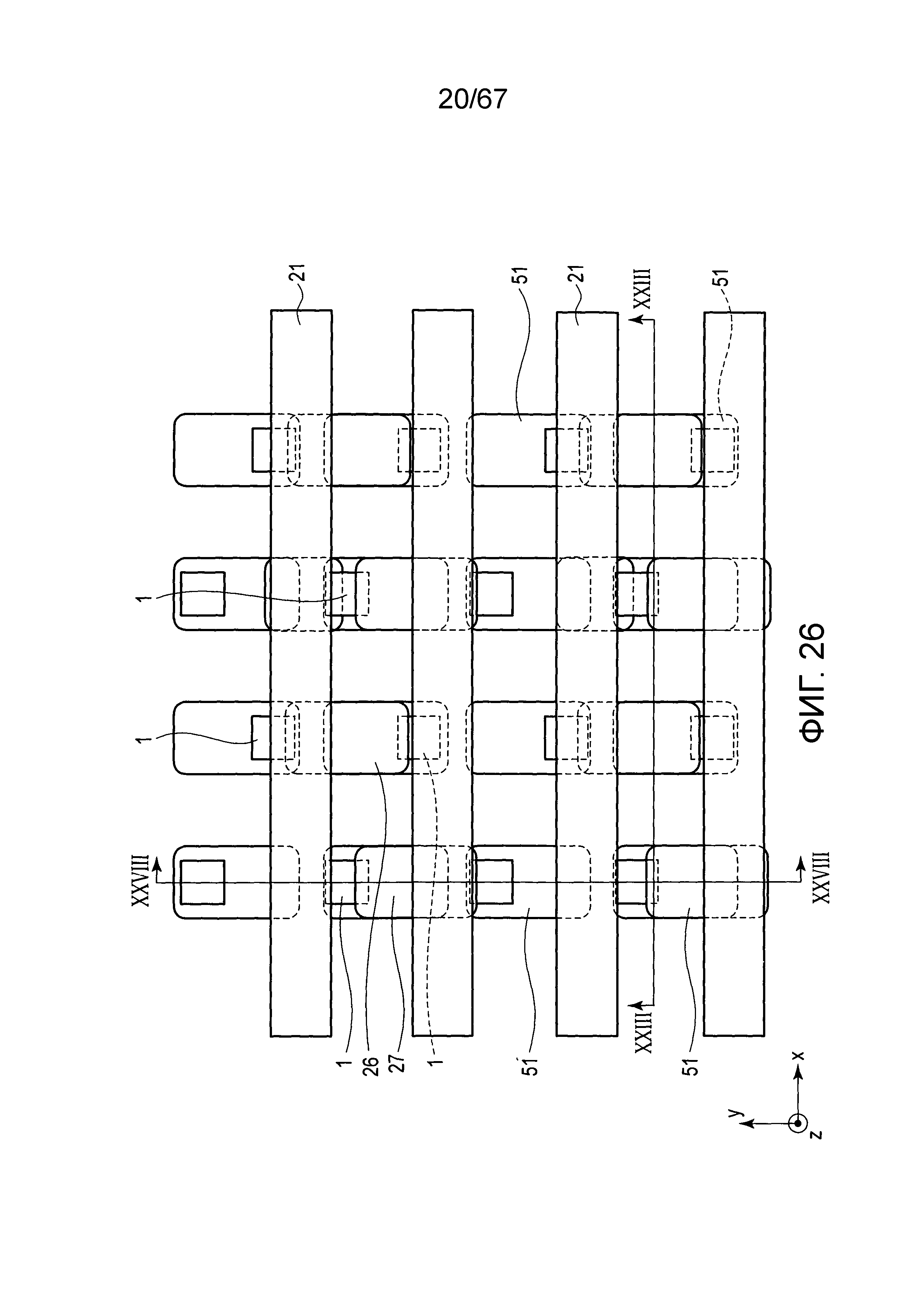

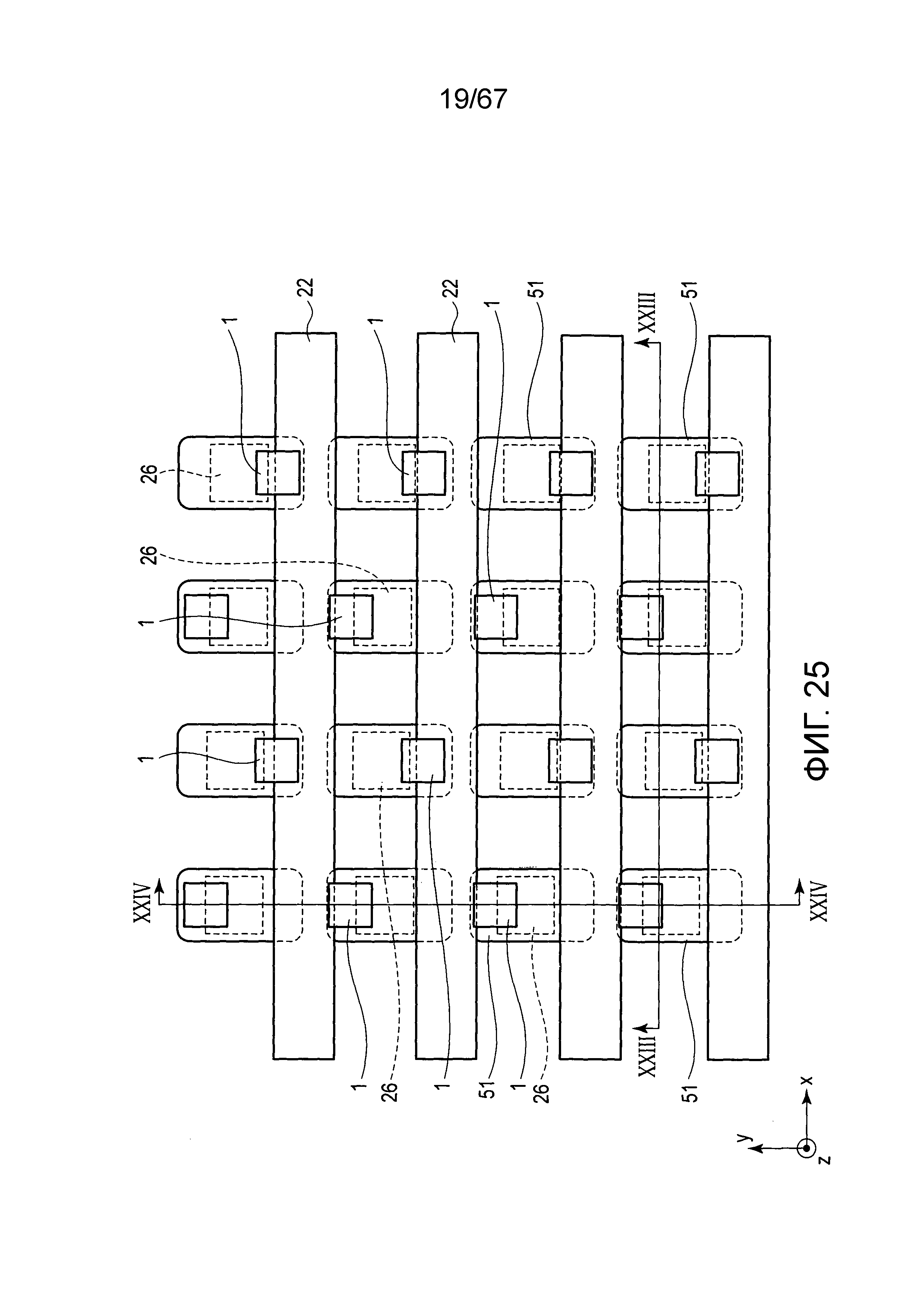

Фиг. 25 и 26 иллюстрируют виды части запоминающего устройства по второму примеру третьего варианта осуществления при виде сверху;

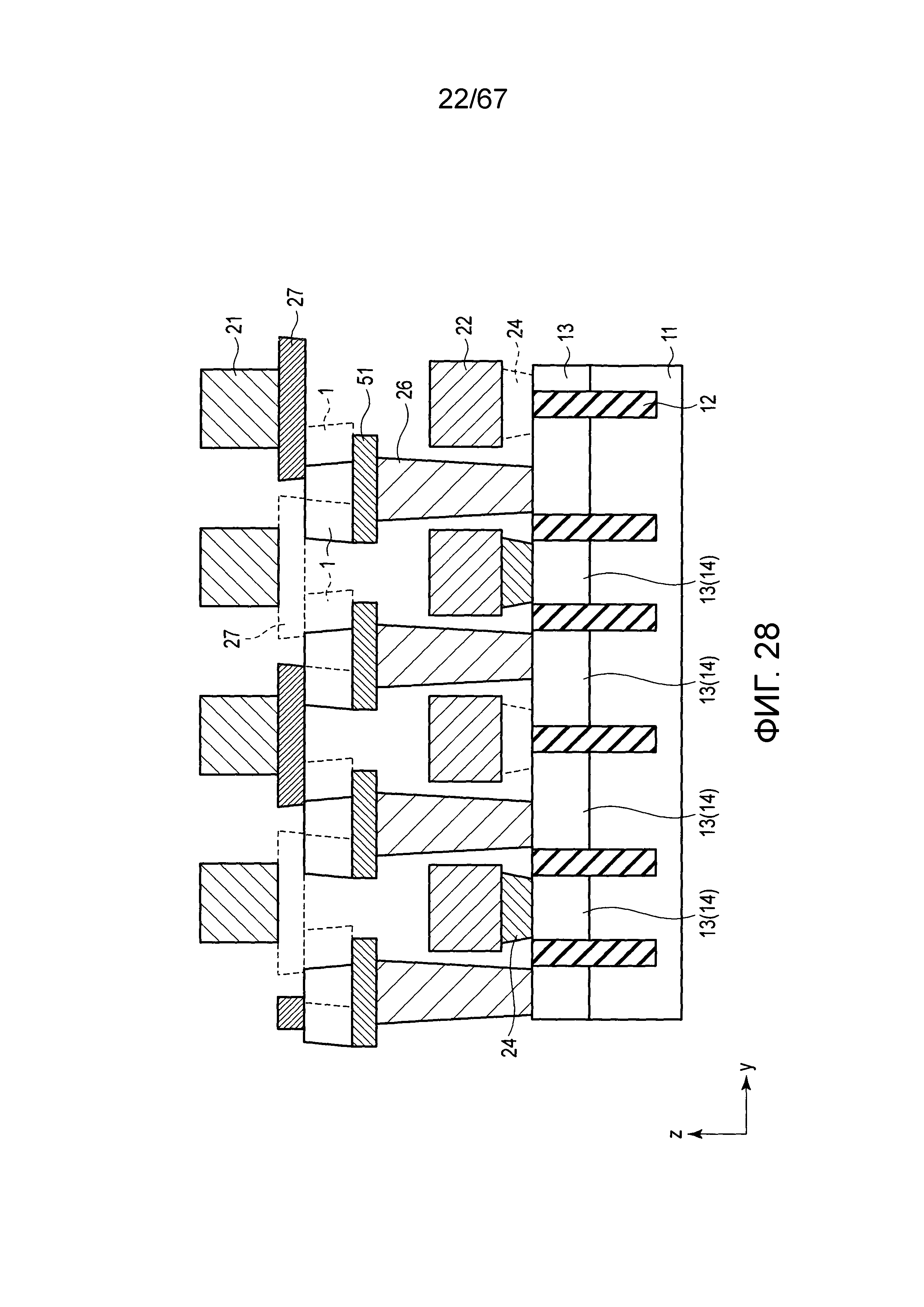

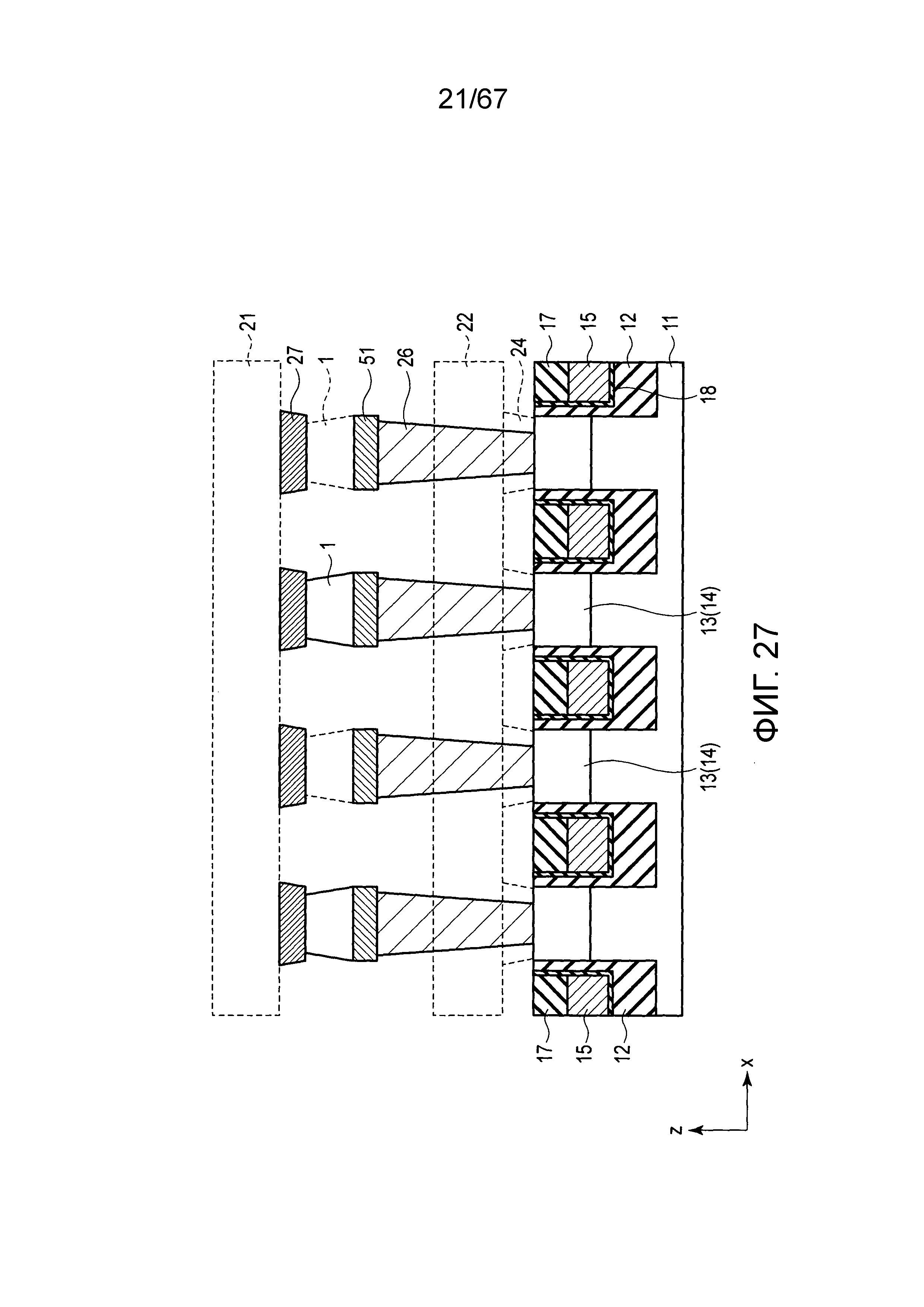

Фиг. 27 и 28 иллюстрируют виды вдоль линии XXVII-XXVII и линии XXVIII-XXVIII по фиг. 25, соответственно;

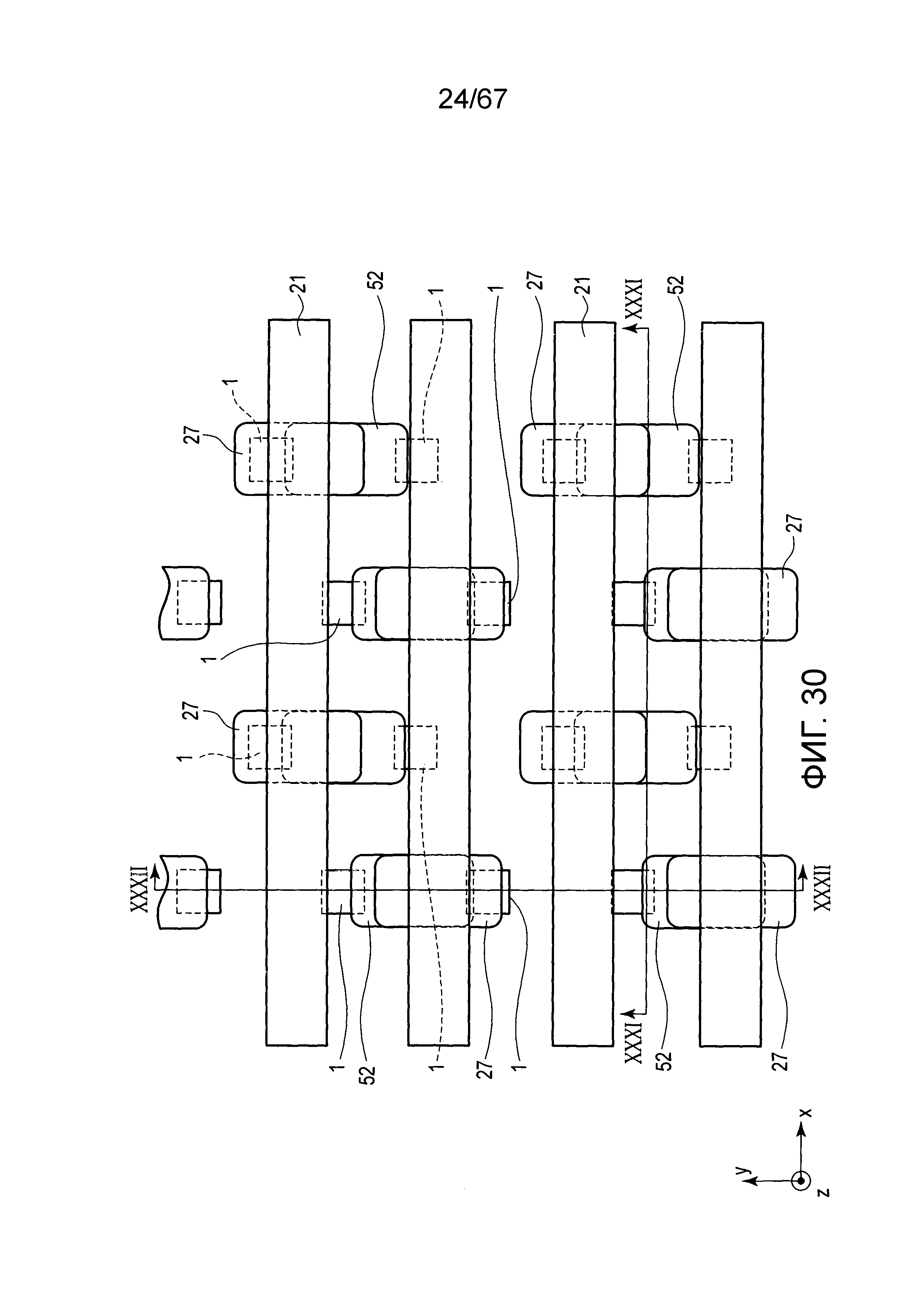

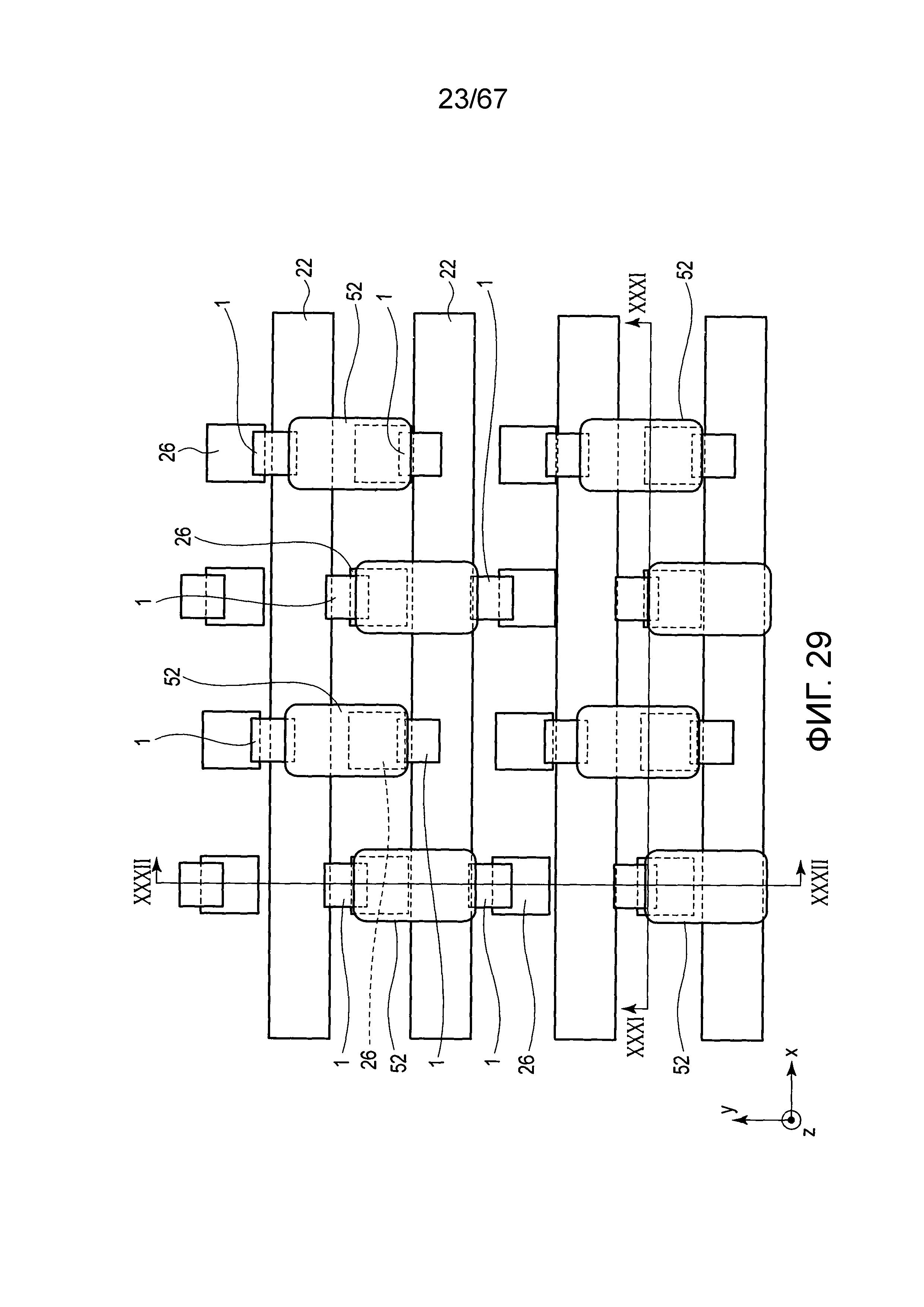

Фиг. 29 и 30 иллюстрируют виды части запоминающего устройства по третьему примеру третьего варианта осуществления при виде сверху;

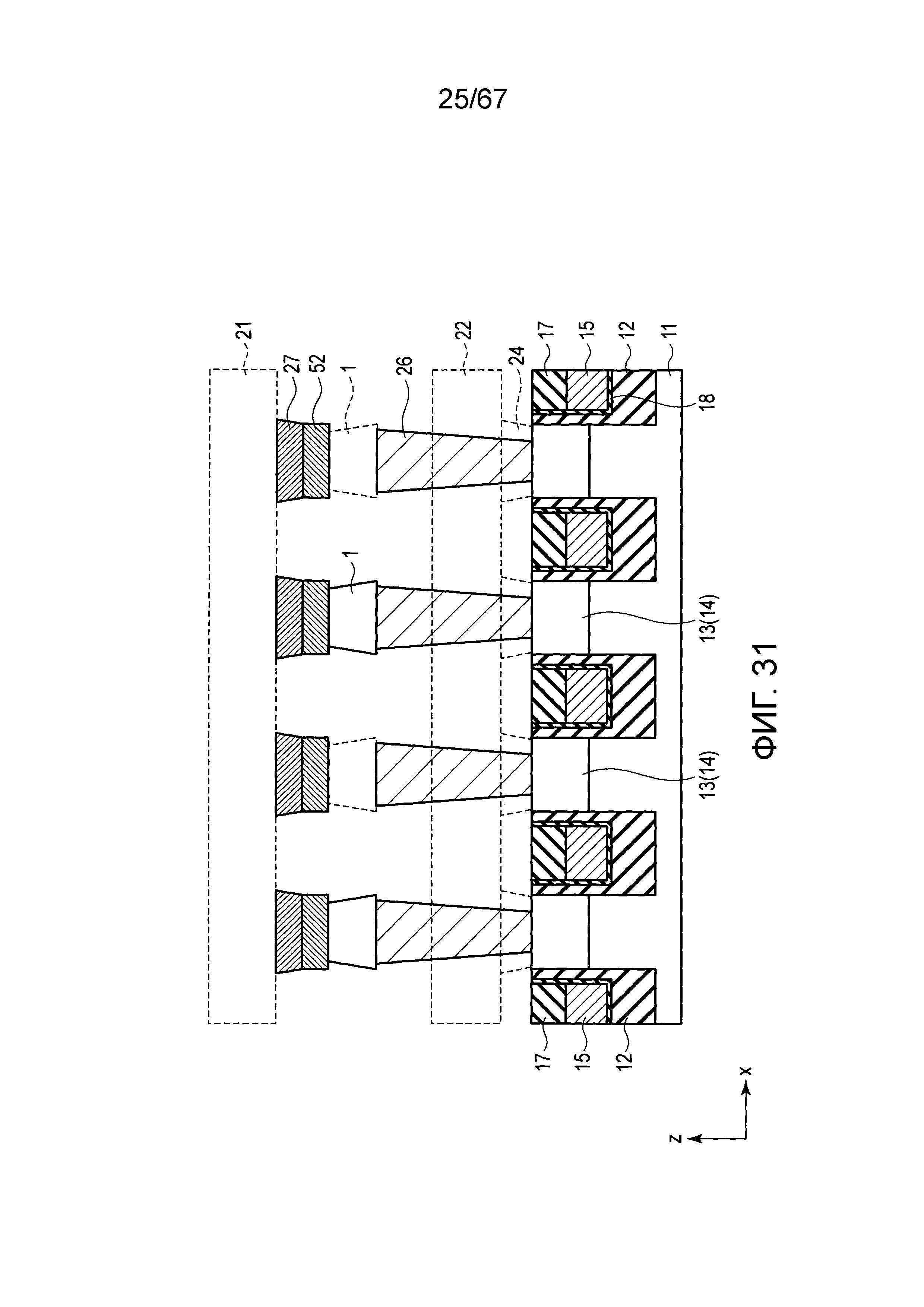

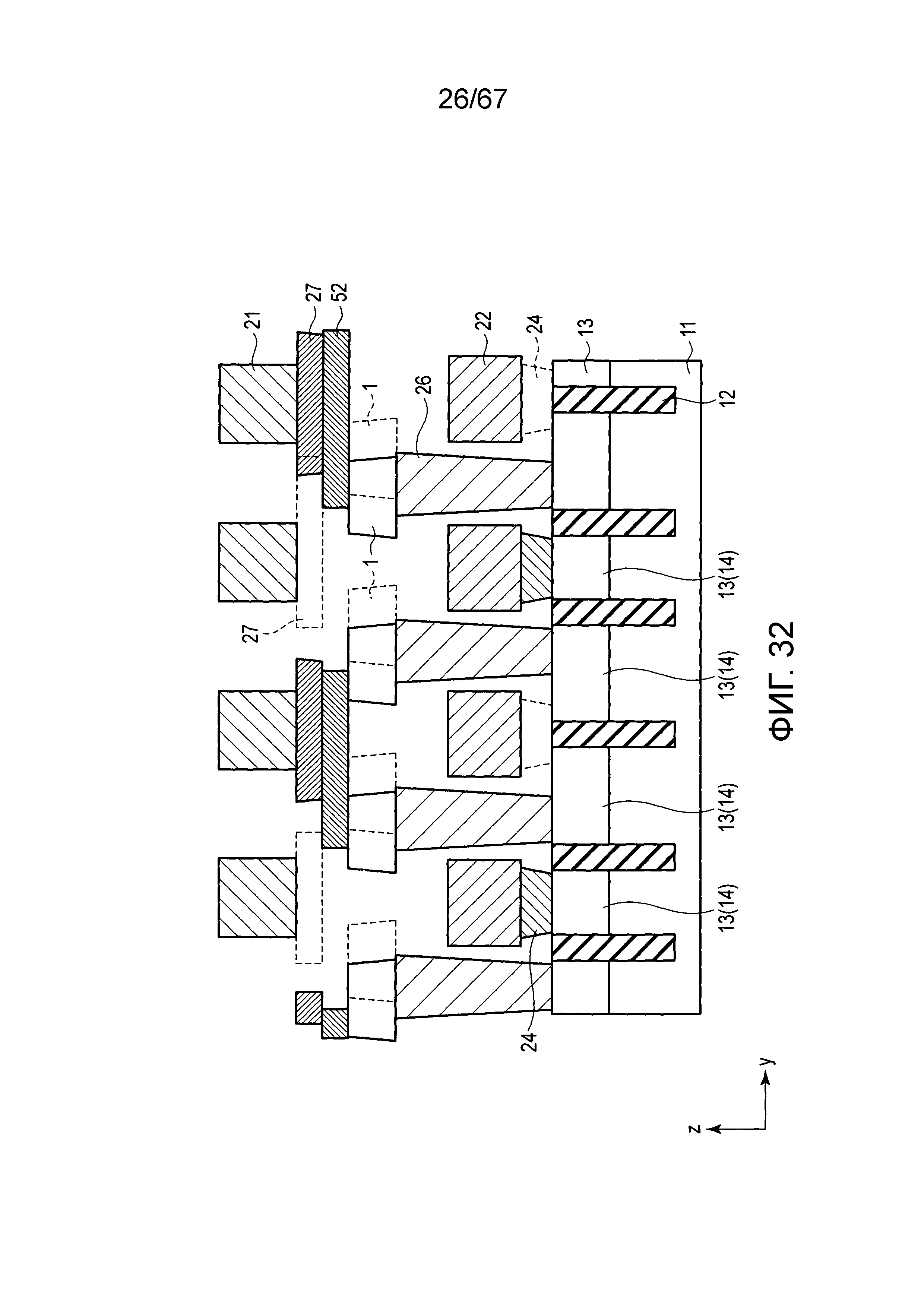

Фиг. 31 и 32 иллюстрируют виды вдоль линии XXXI-XXXI и линии XXXII-XXXII по фиг. 29, соответственно;

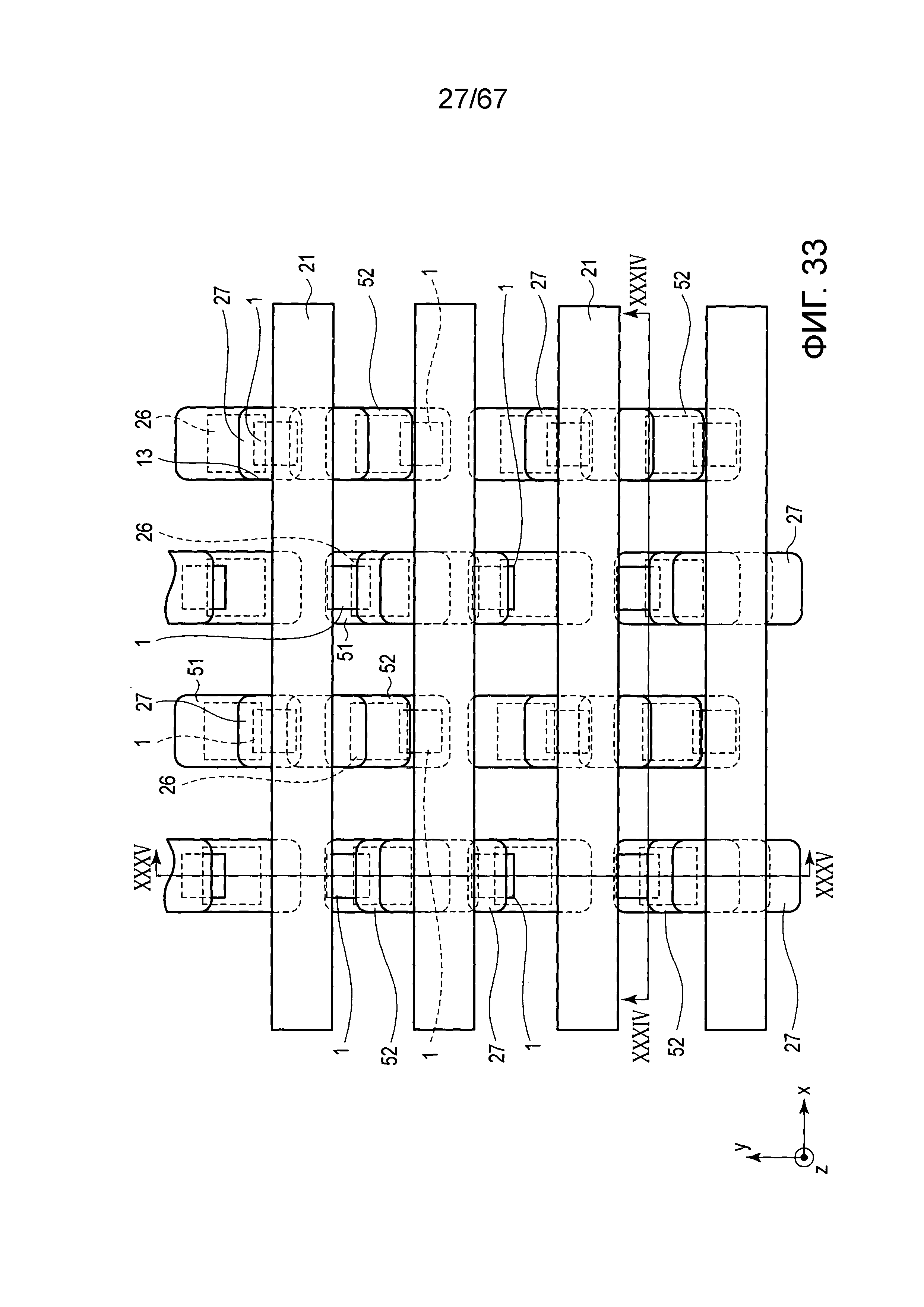

Фиг. 33 иллюстрирует вид части запоминающего устройства по четвертому примеру третьего варианта осуществления при виде сверху;

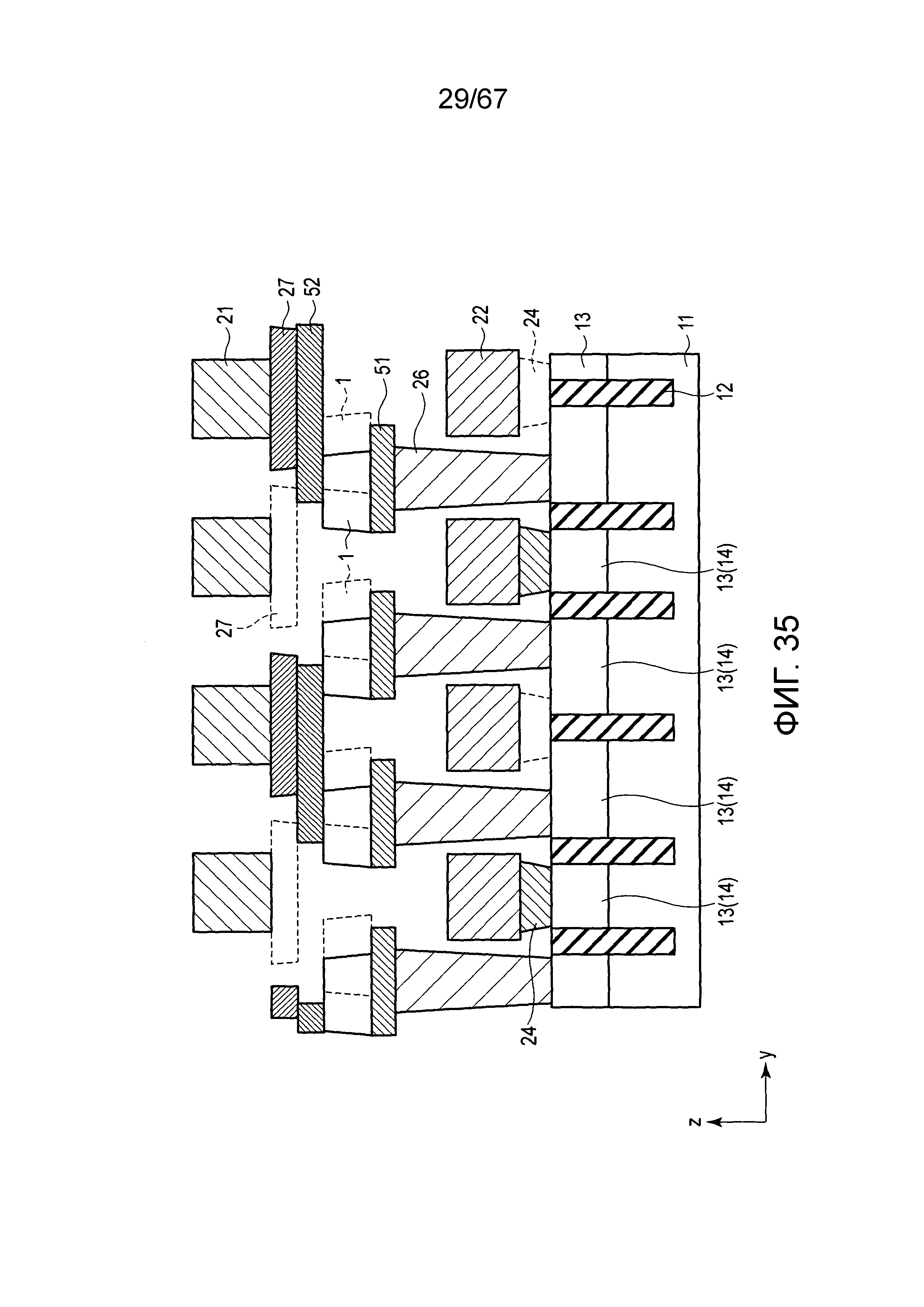

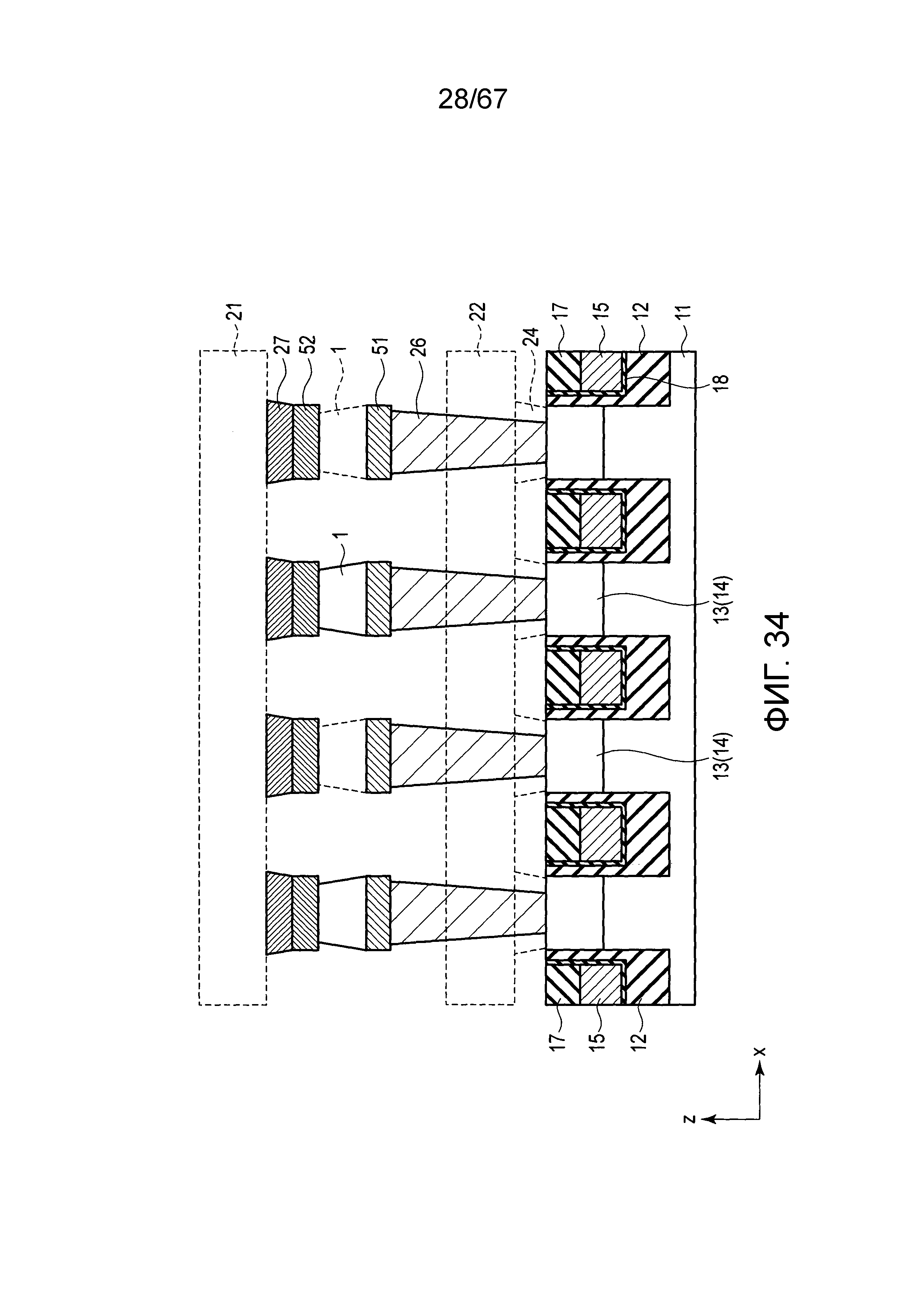

Фиг. 34 и 35 иллюстрируют виды вдоль линии XXXIV-XXXIV и линии XXXV-XXXV по фиг. 33;

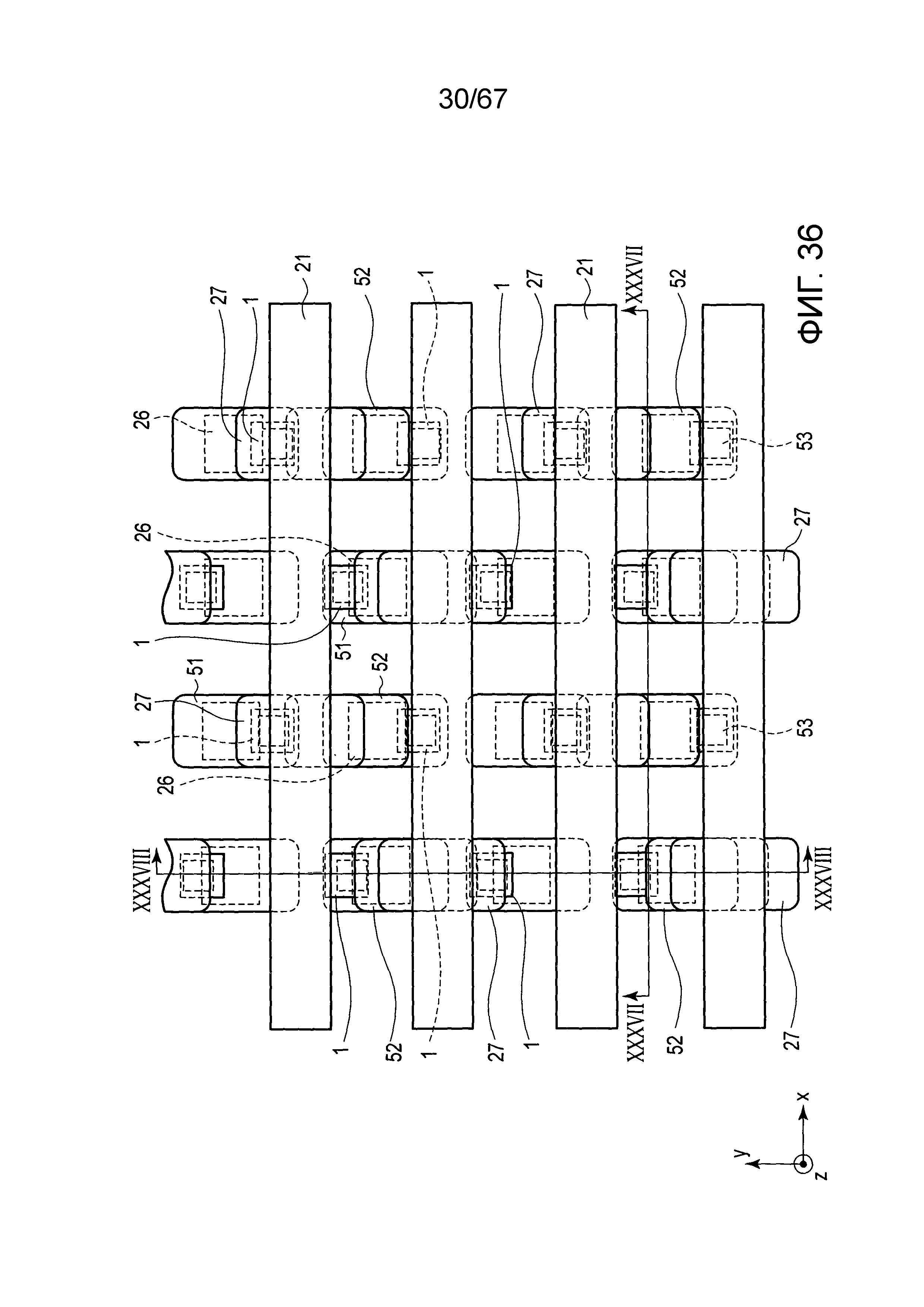

Фиг. 36 иллюстрирует вид части запоминающего устройства по пятому примеру третьего варианта осуществления при виде сверху;

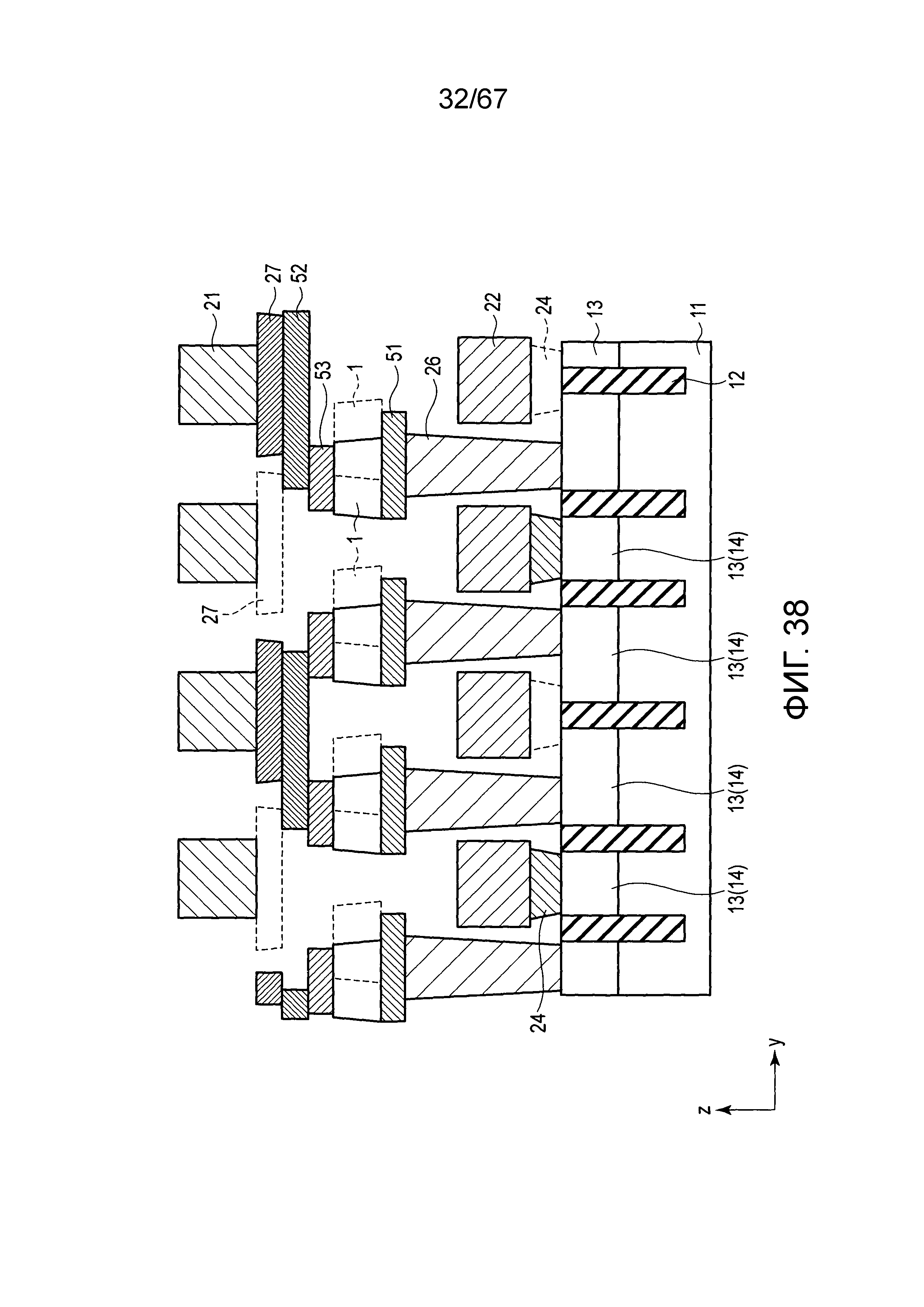

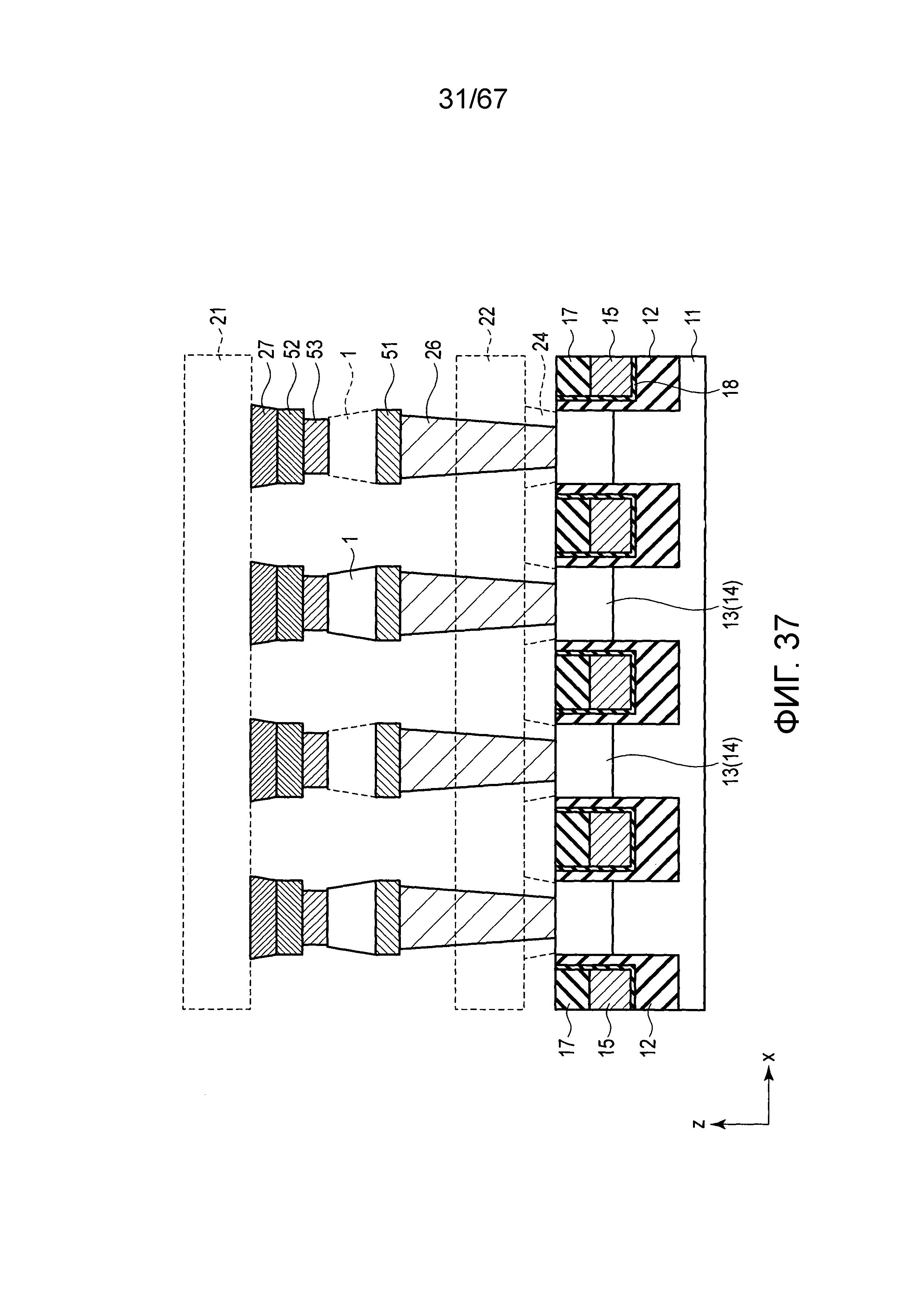

Фиг. 37 и 38 иллюстрируют виды вдоль линии XXXVII-XXXVII и линии XXXVIII-XXXVIII по фиг. 36, соответственно;

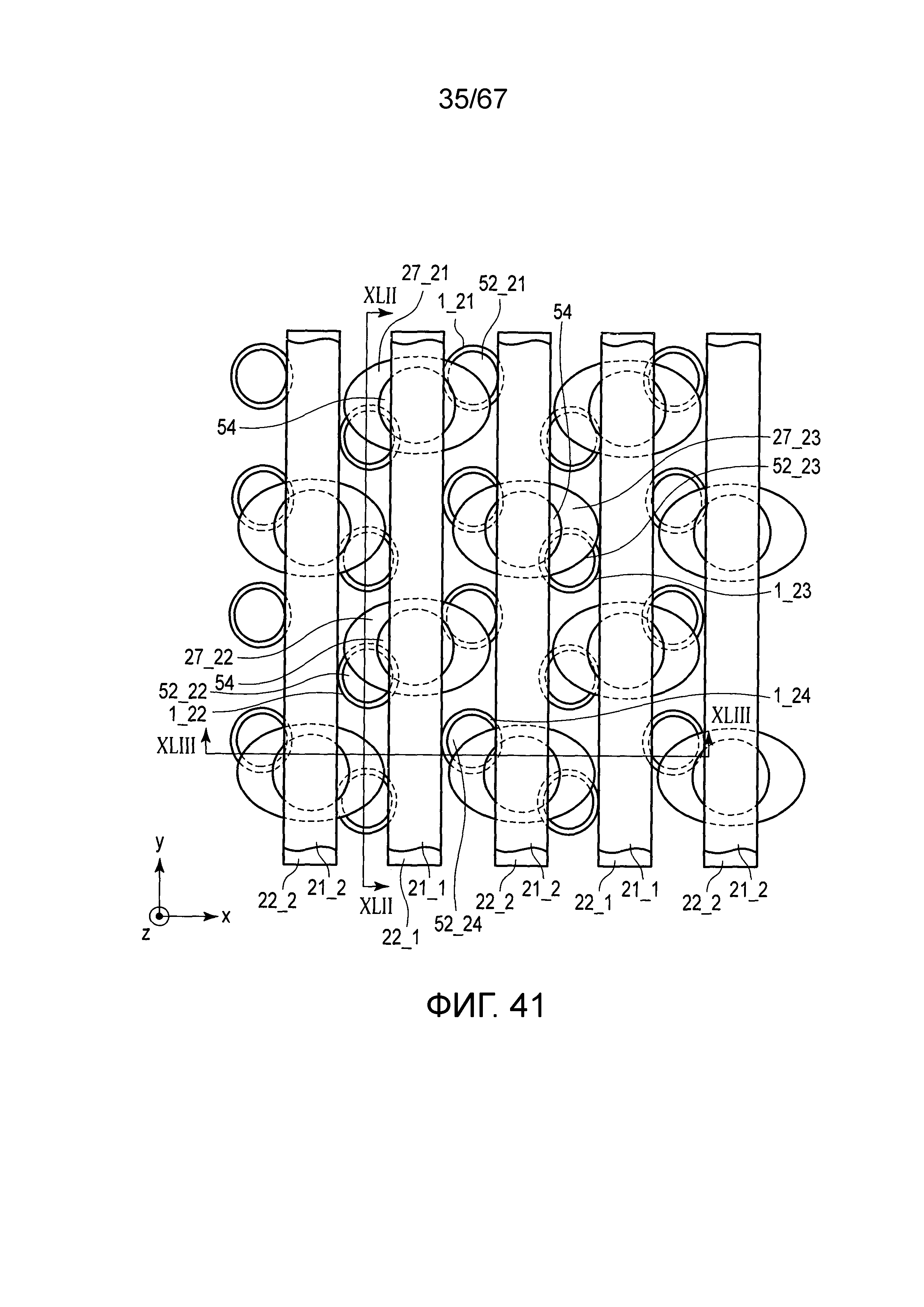

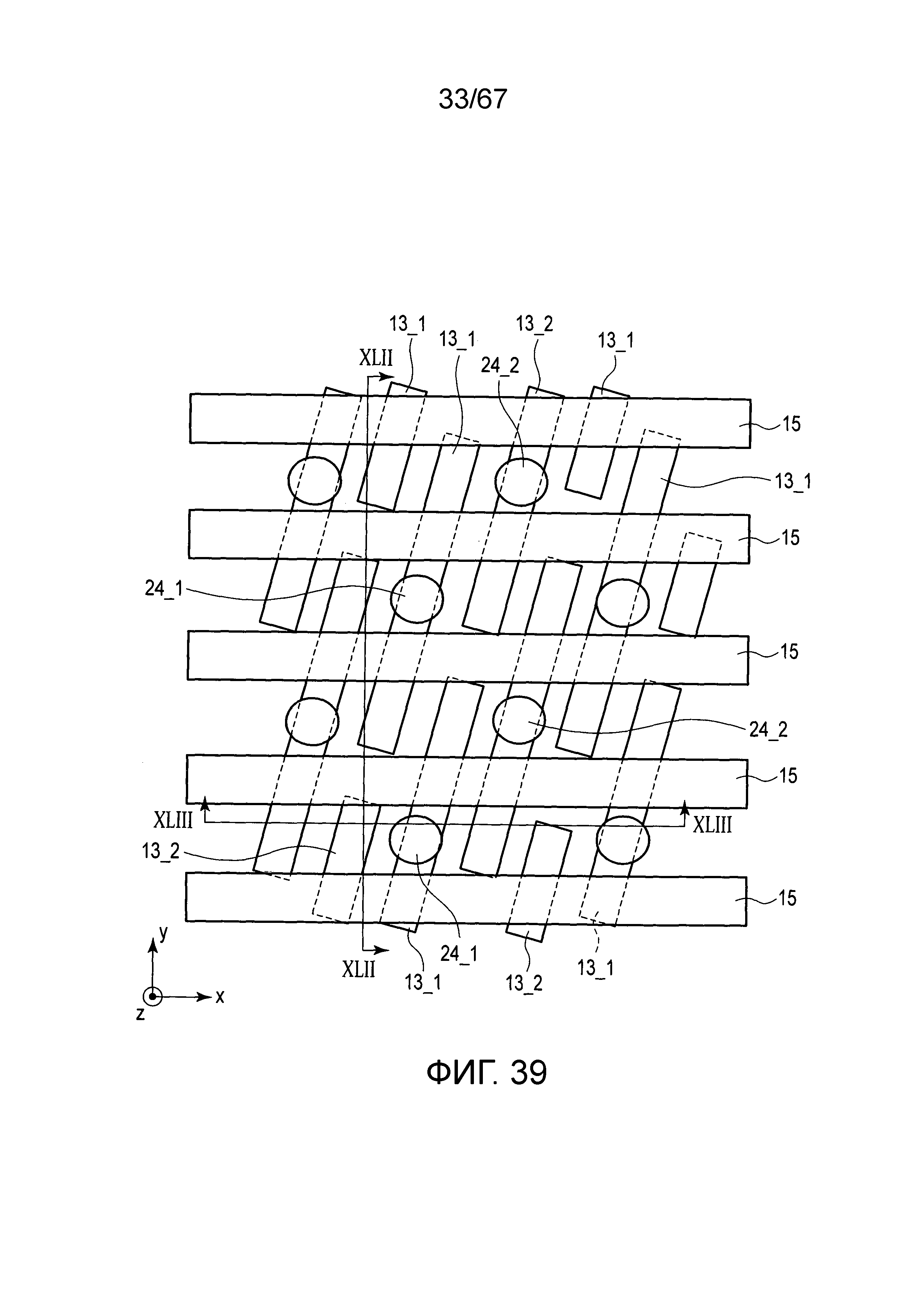

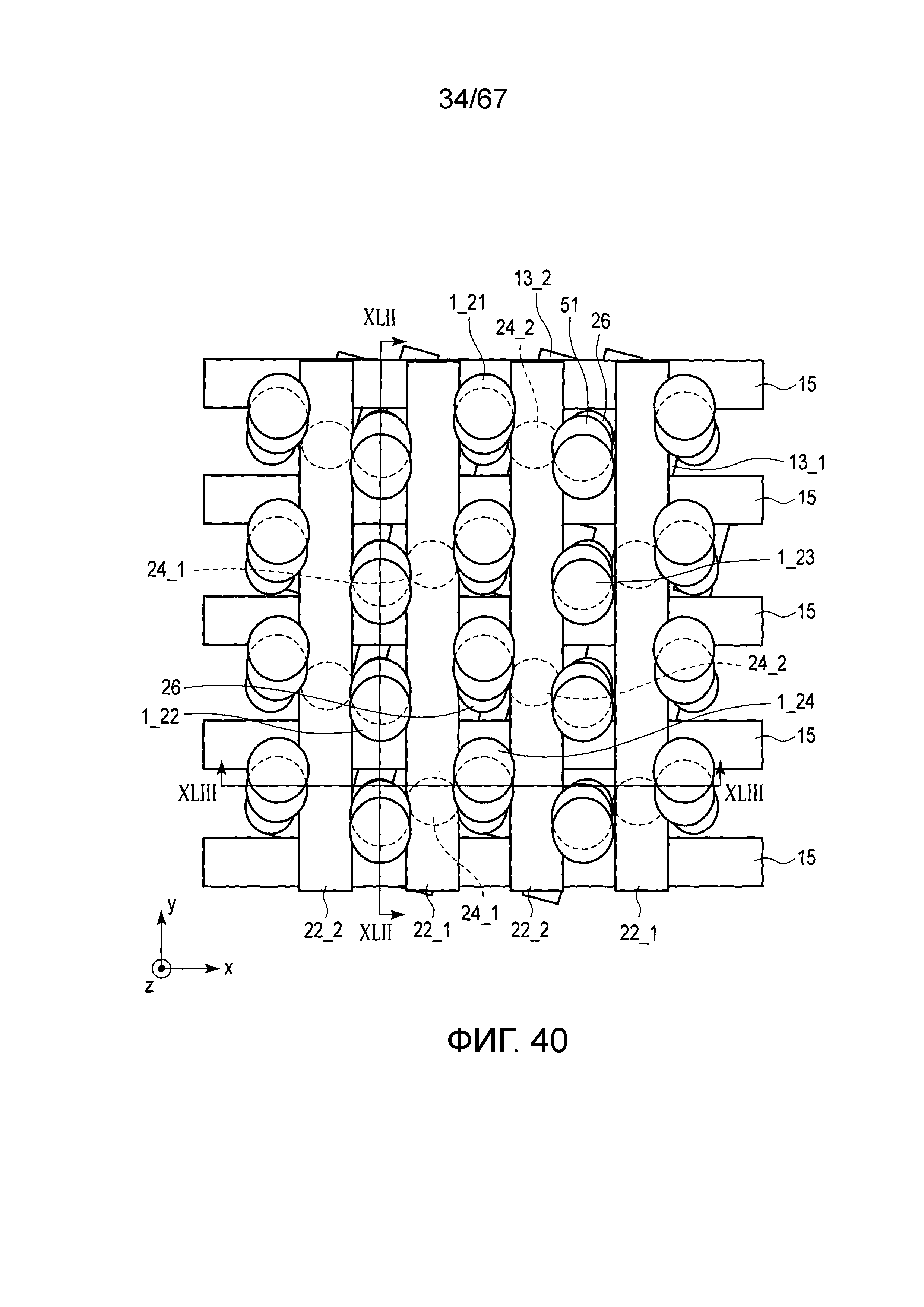

Фиг. 39-41 иллюстрируют виды части запоминающего устройства по первому примеру четвертого варианта осуществления при виде сверху;

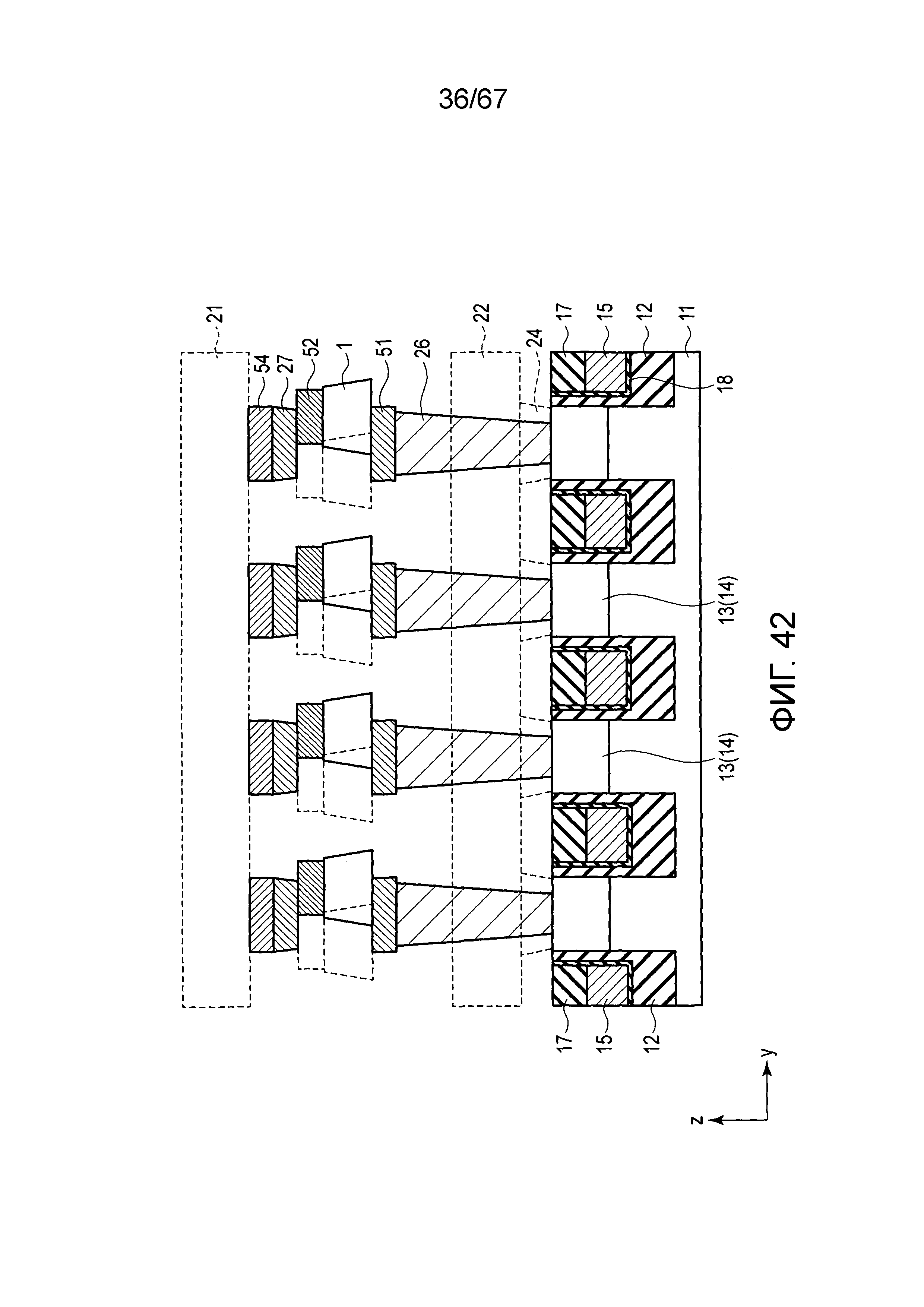

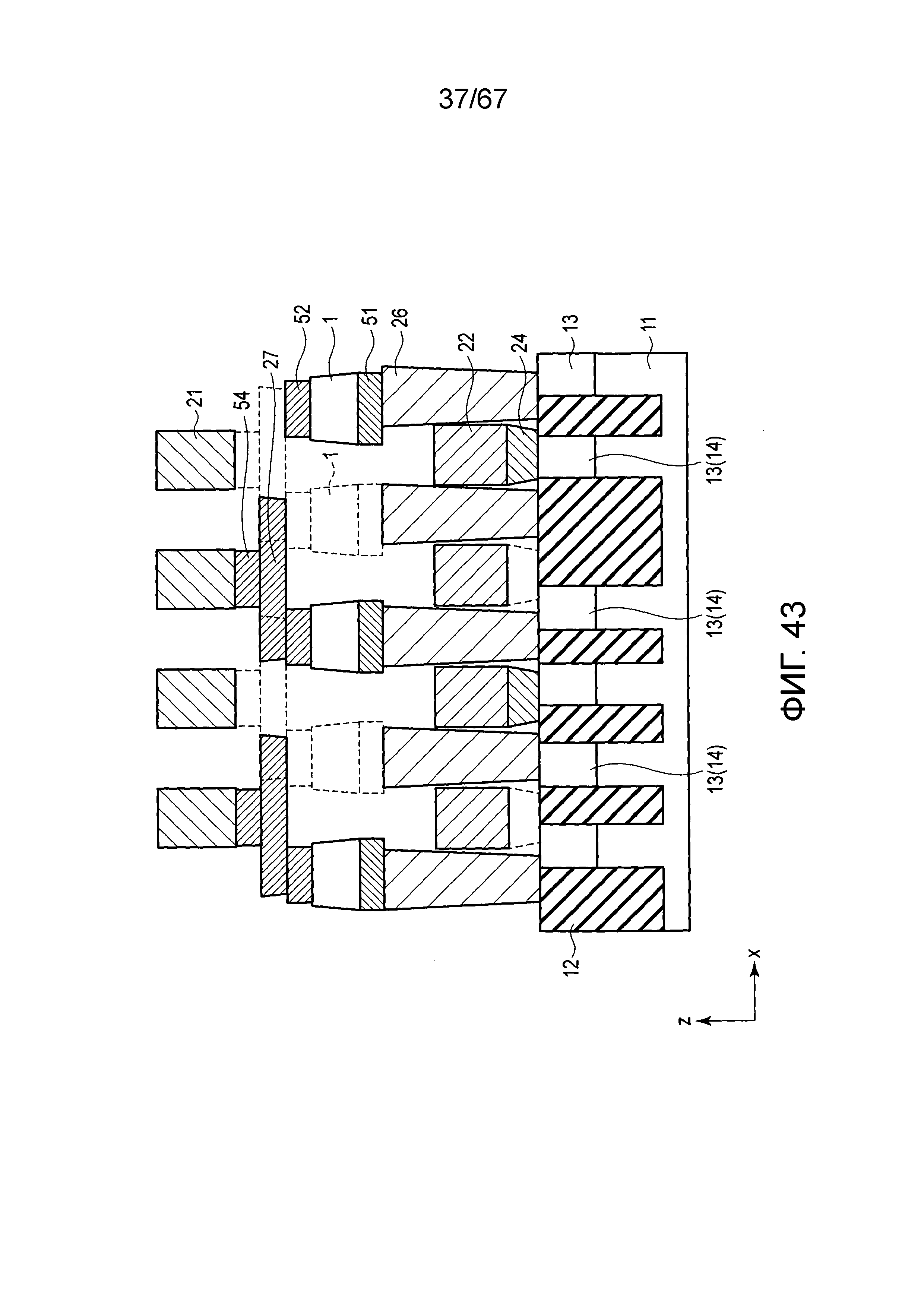

Фиг. 42 и 43 иллюстрируют виды вдоль линии XLII-XLII и линии XLIII-XLIII по фиг. 39-41, соответственно;

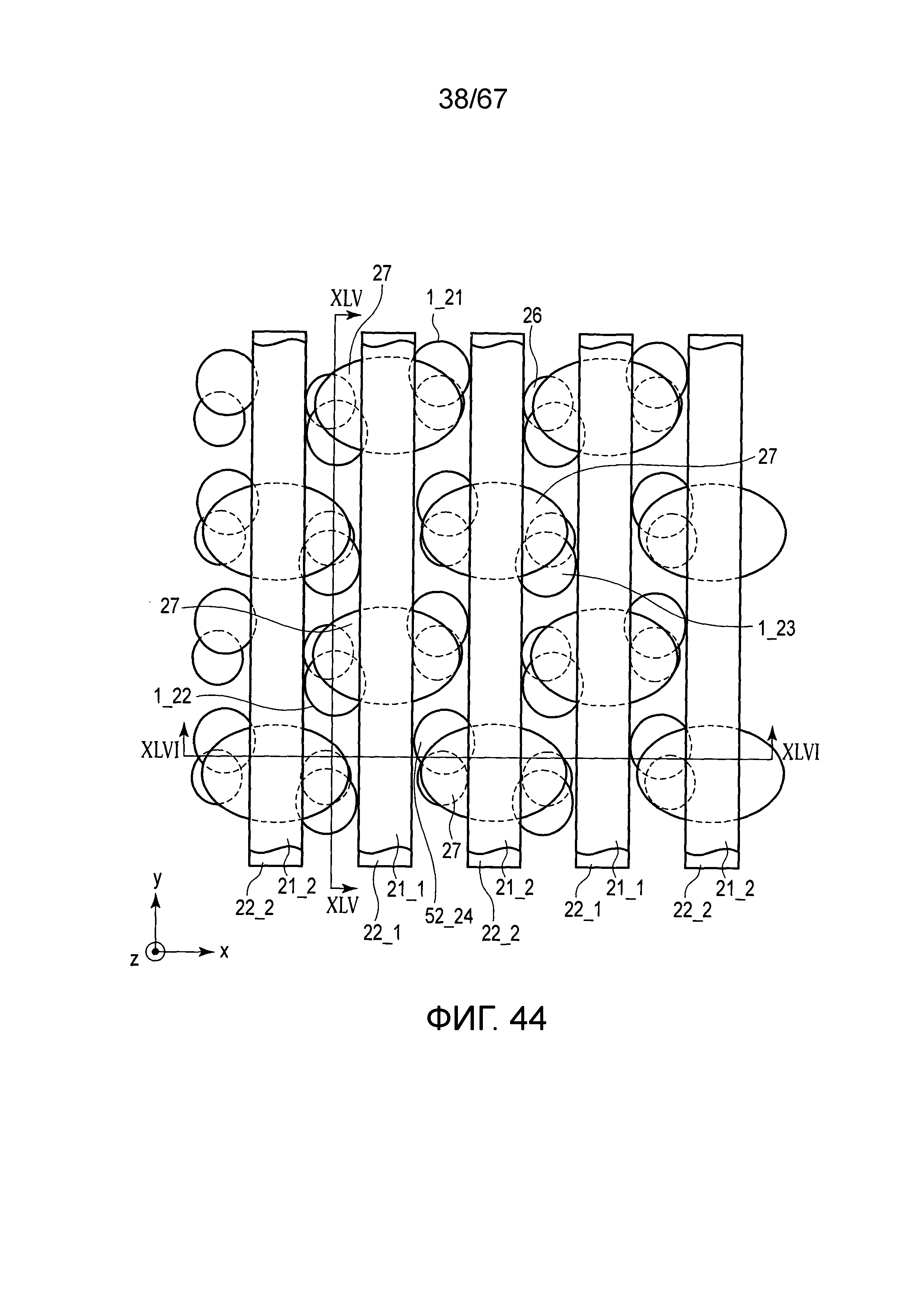

Фиг. 44 иллюстрирует вид части запоминающего устройства по второму примеру четвертого варианта осуществления при виде сверху;

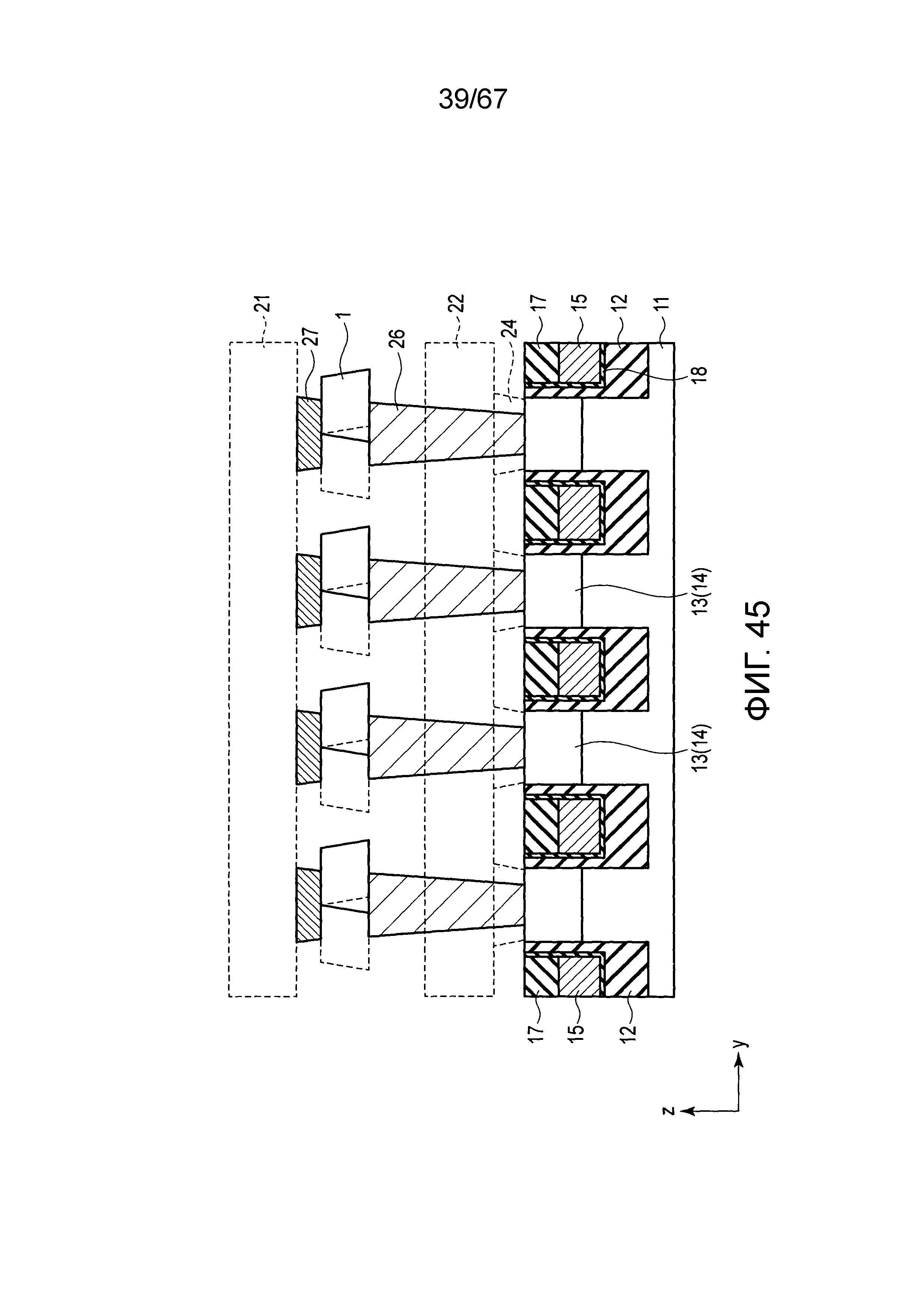

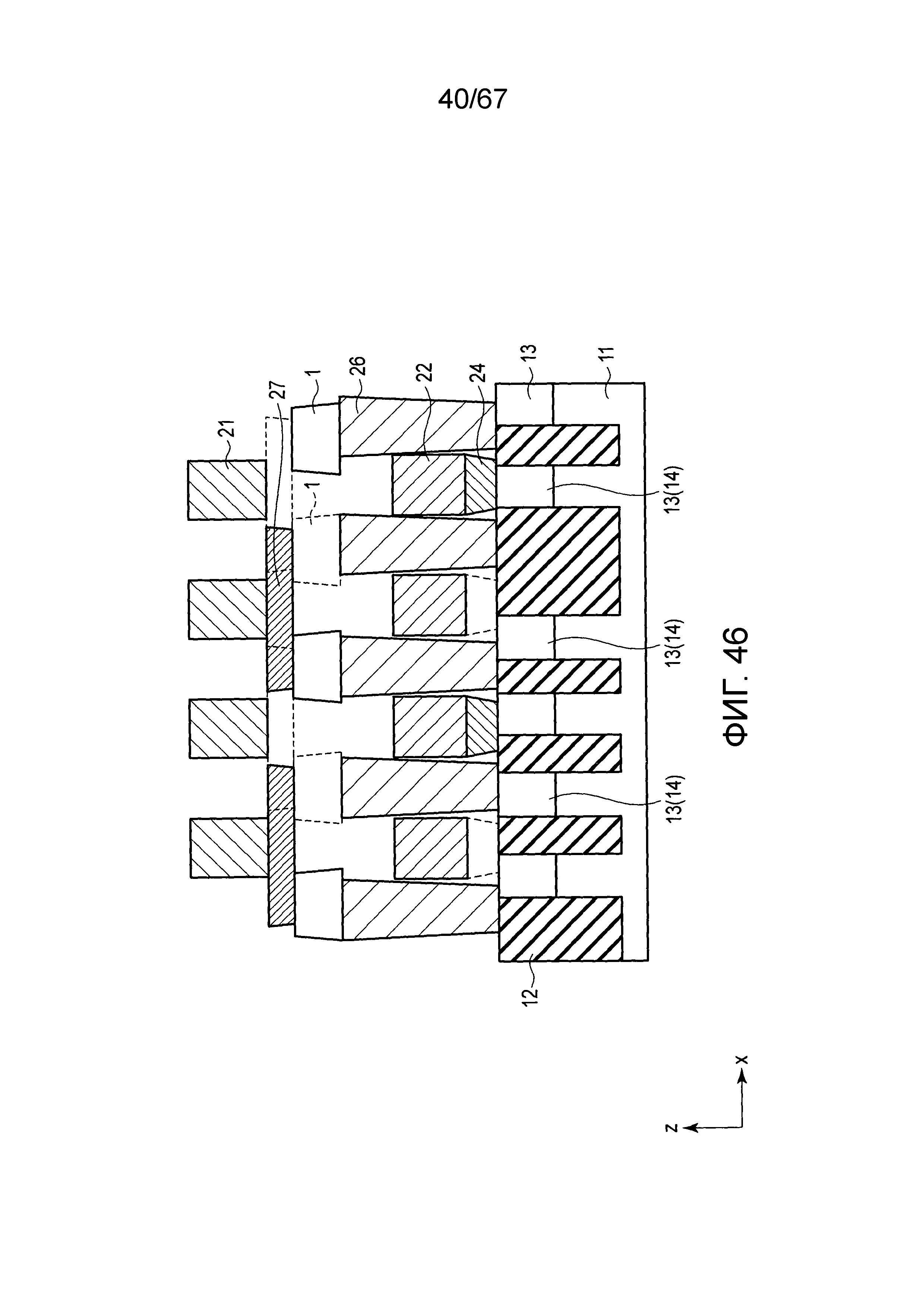

Фиг. 45 и 46 иллюстрируют виды вдоль линии XLV-XLV и линии XLVI-XLVI по фиг. 44, соответственно;

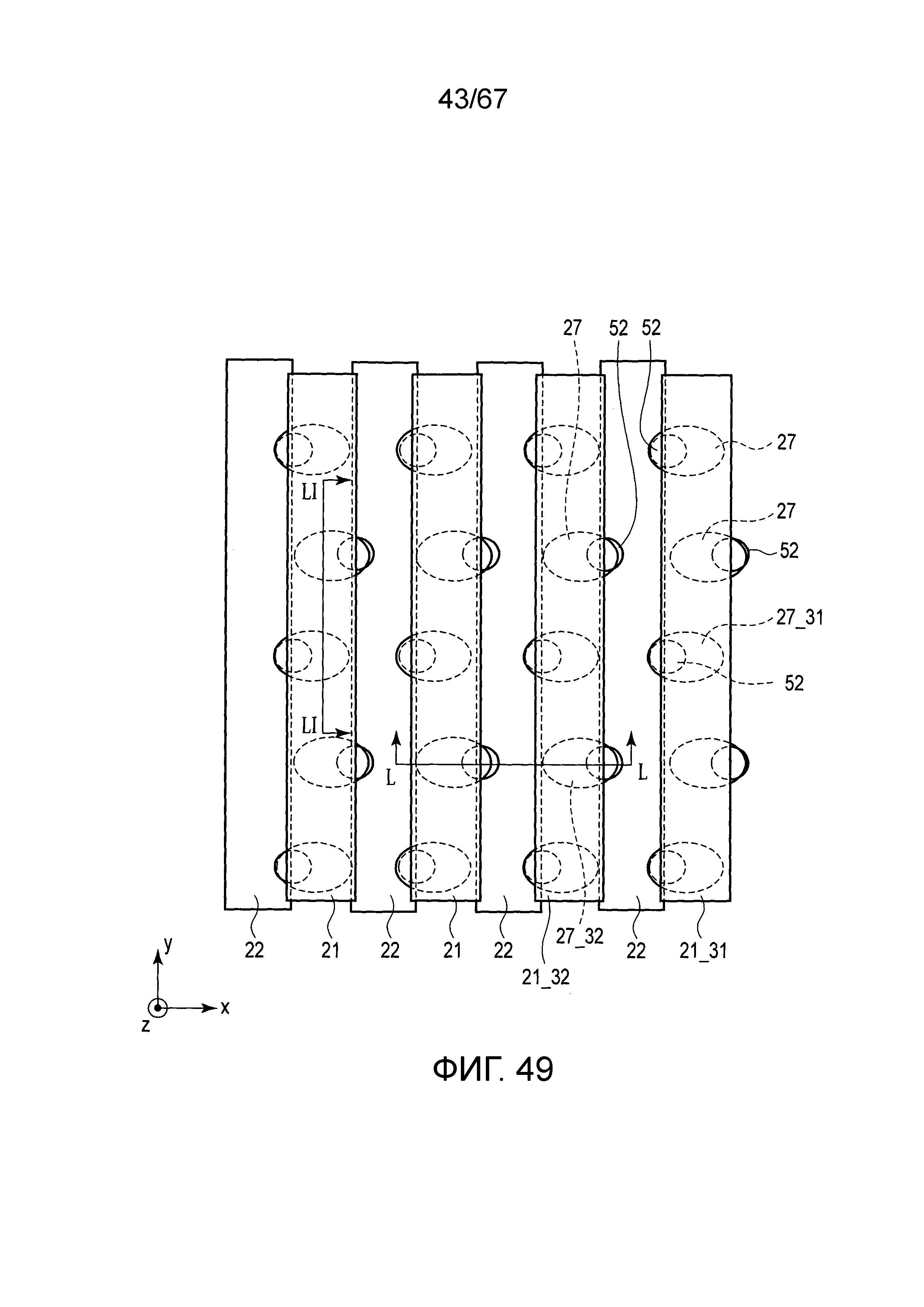

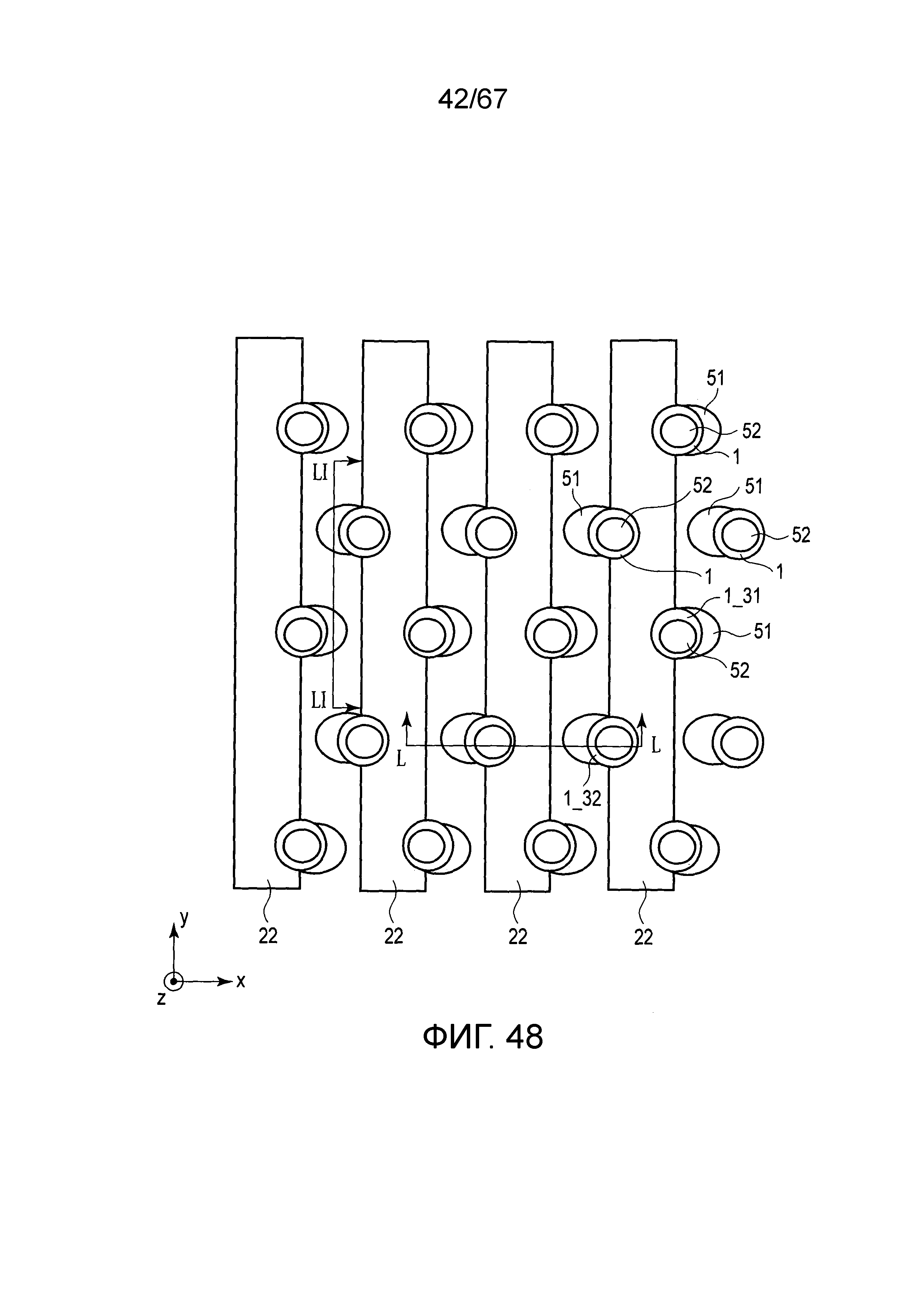

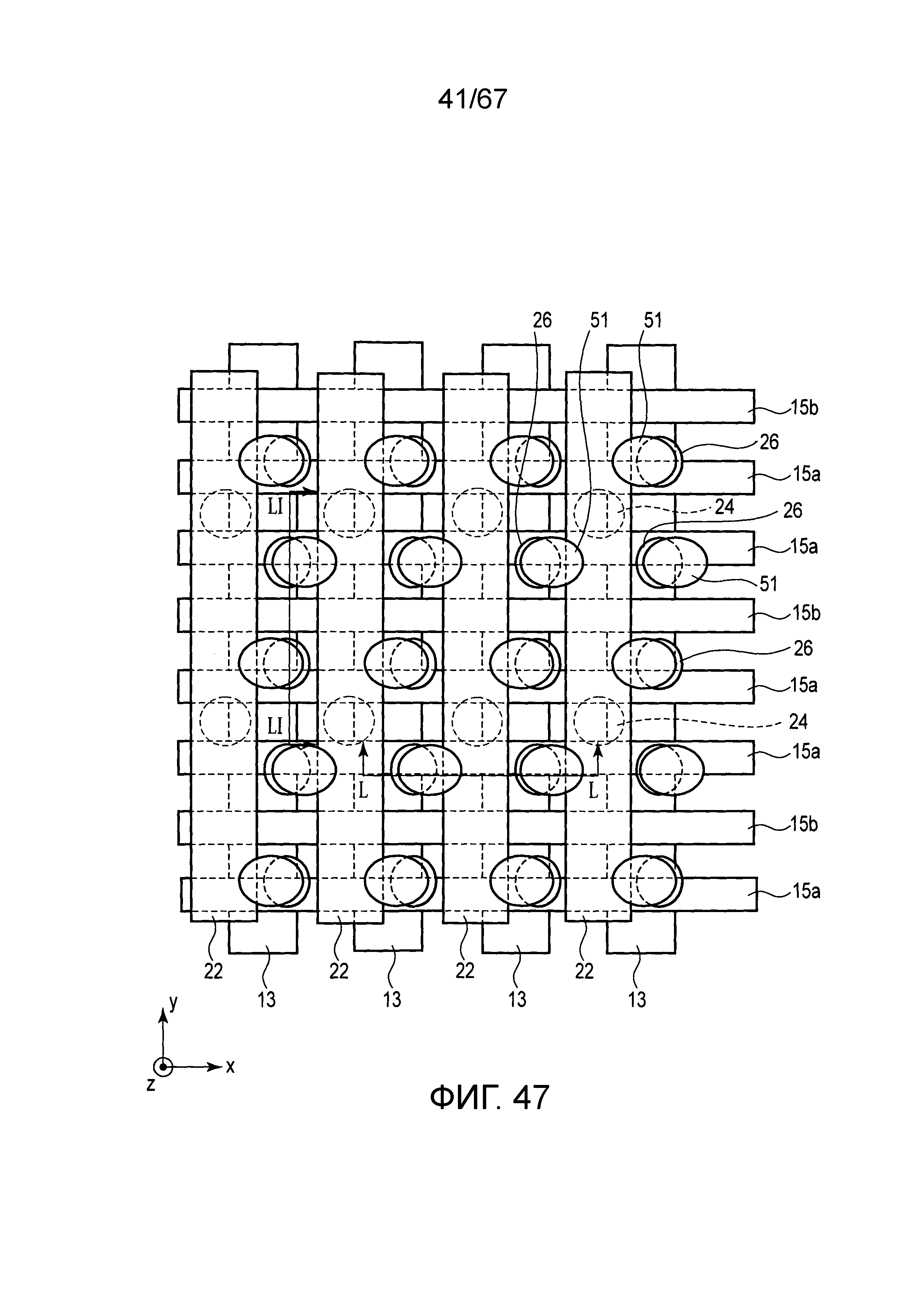

Фиг. 47-49 иллюстрируют виды части запоминающего устройства по первому примеру пятого варианта осуществления при виде сверху;

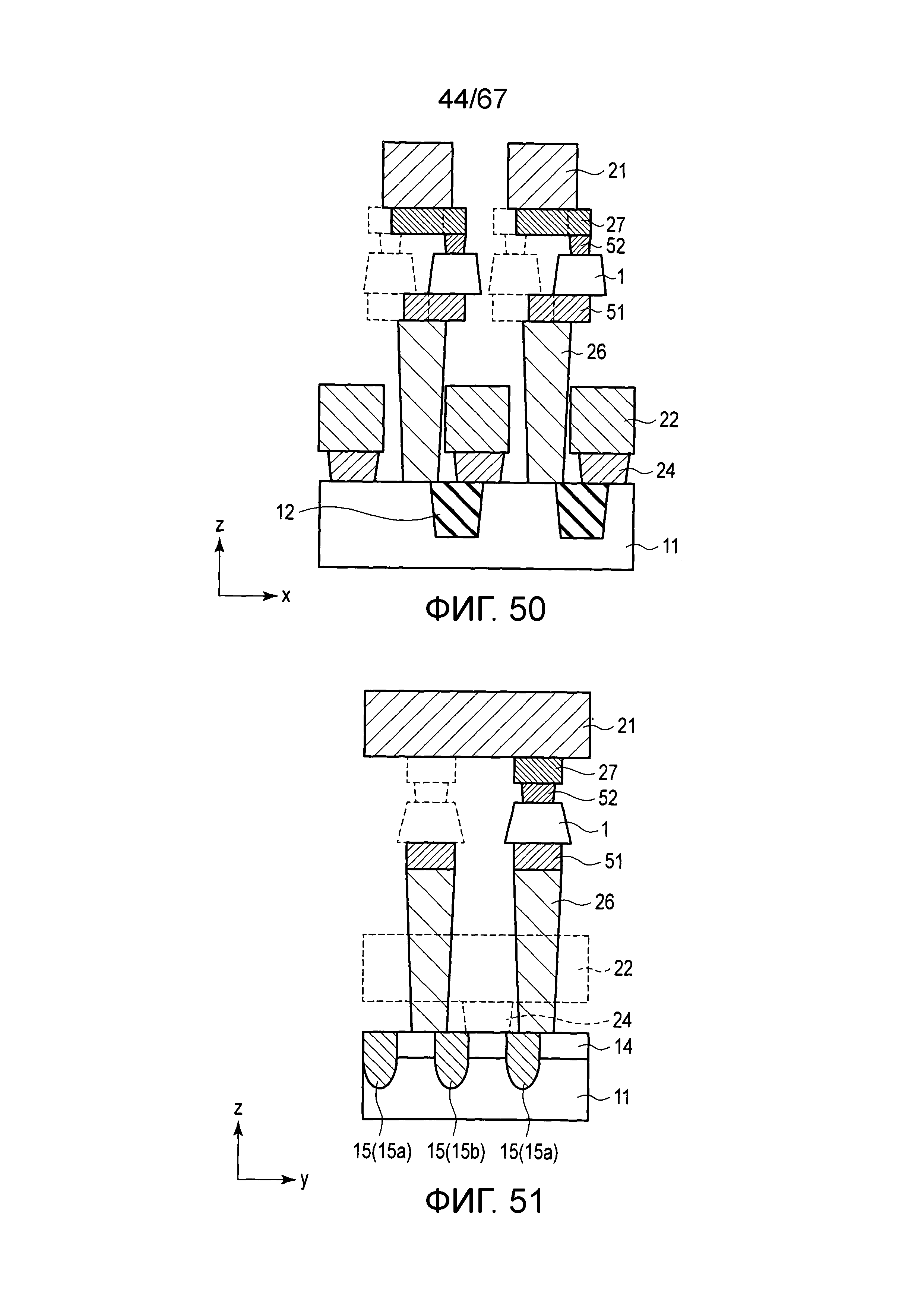

Фиг. 50 и 51 иллюстрируют виды вдоль линии L-L и линии LI-LI по фиг. 47-49, соответственно;

Фиг. 52 иллюстрирует вид части запоминающего устройства по второму примеру пятого варианта осуществления при виде сверху;

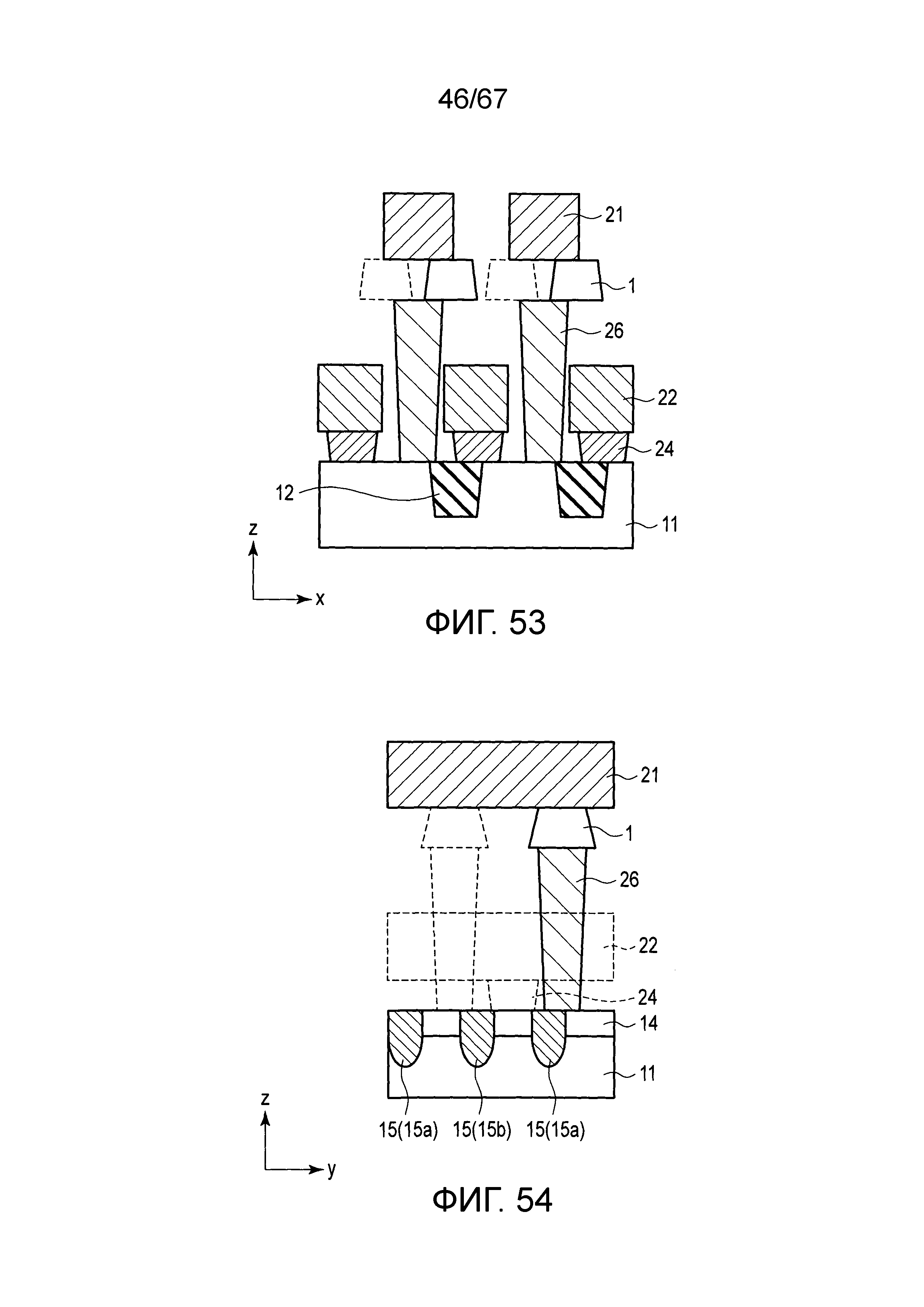

Фиг. 53 и 54 иллюстрируют виды вдоль линии LIII-LIII и линии LIV-LIV по фиг. 52, соответственно;

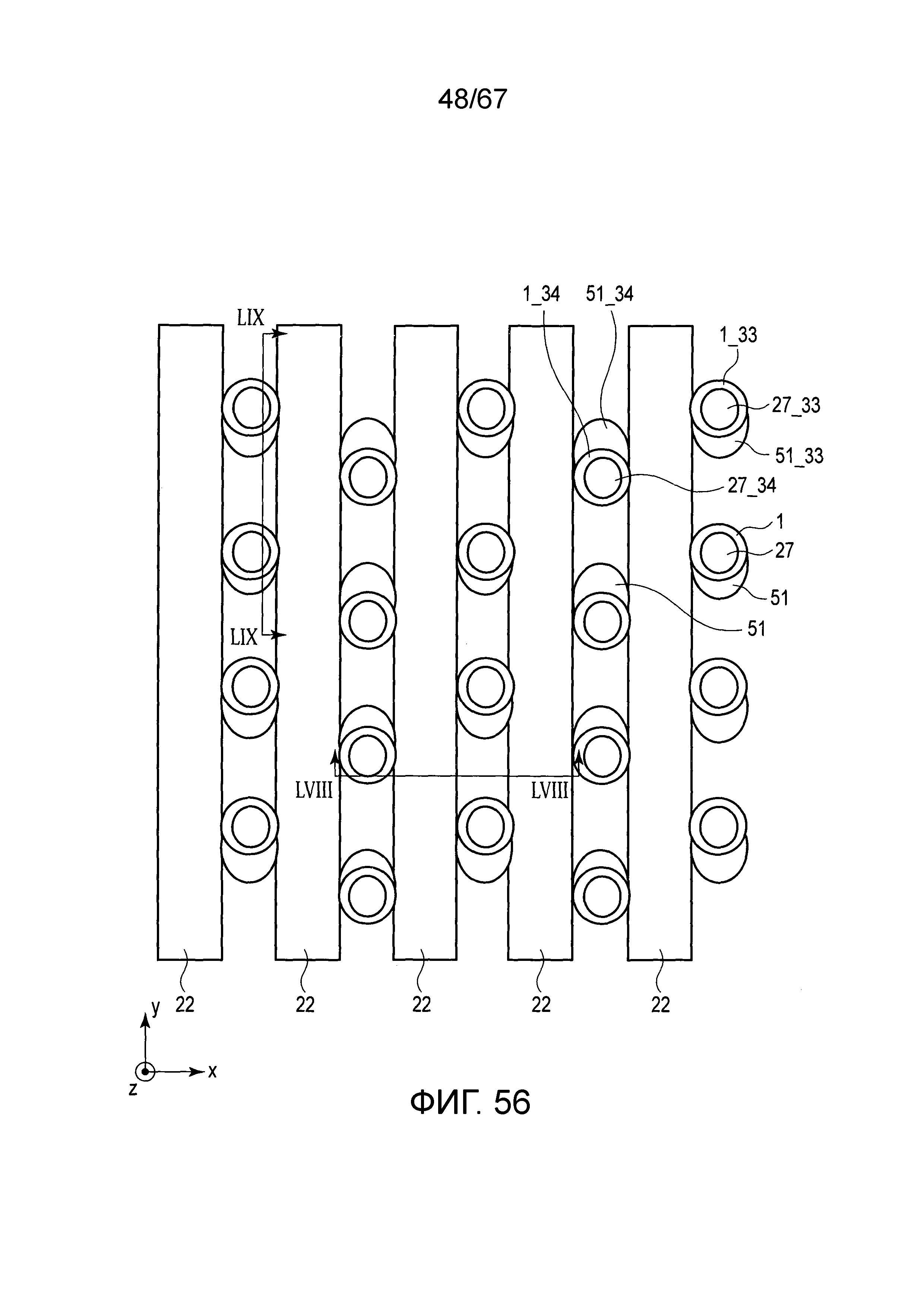

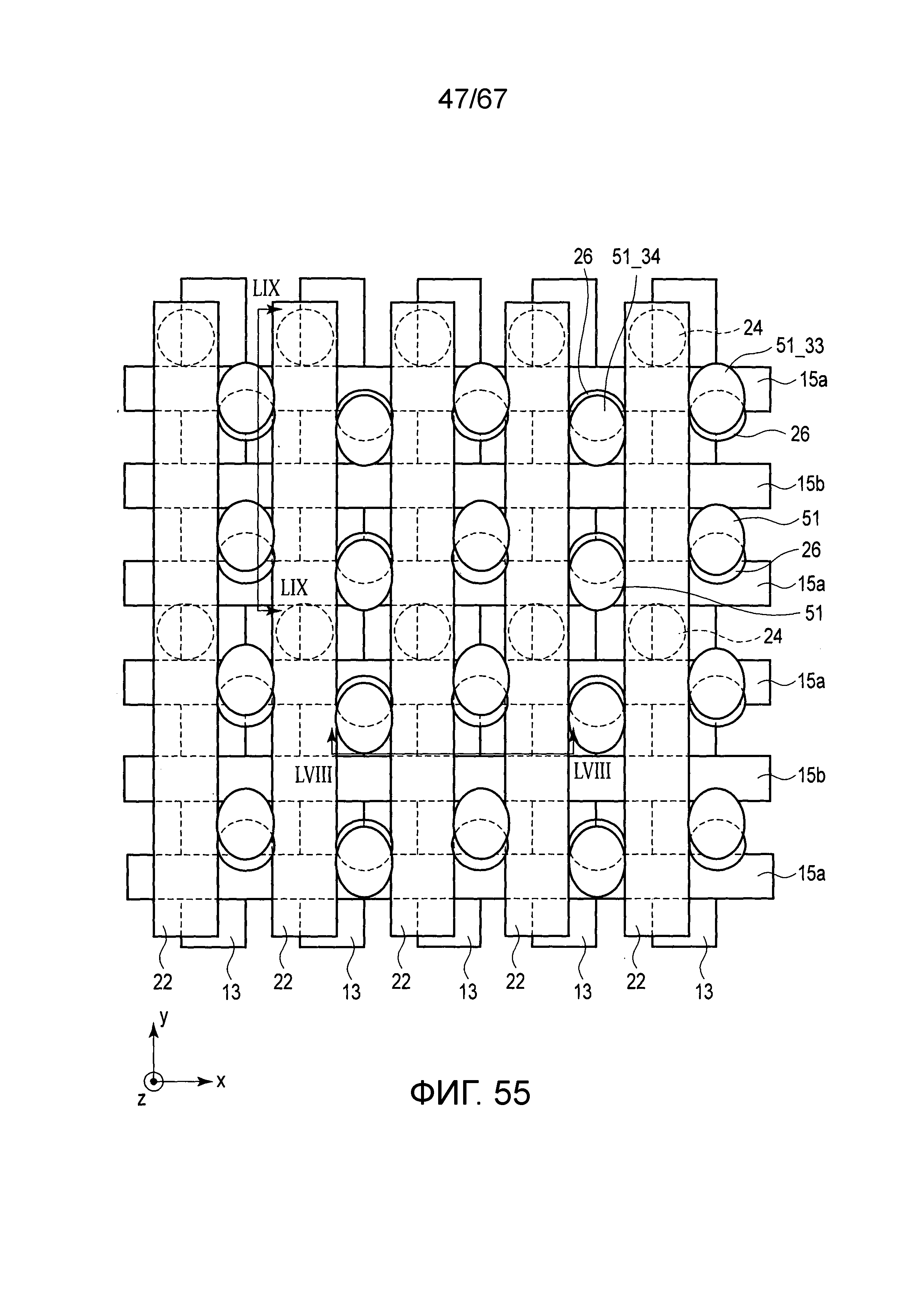

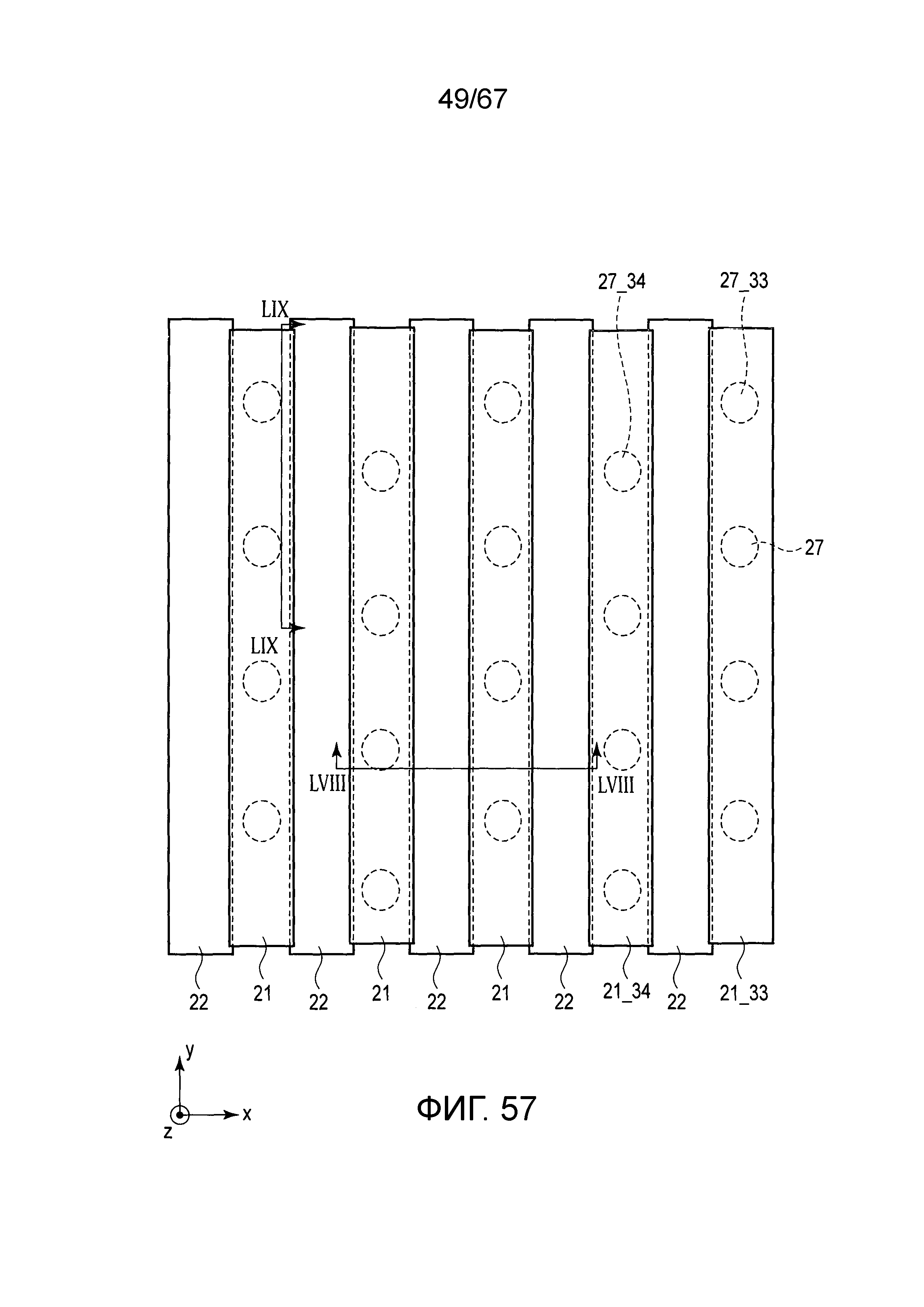

Фиг. 55-57 иллюстрируют виды части запоминающего устройства по третьему примеру пятого варианта осуществления при виде сверху;

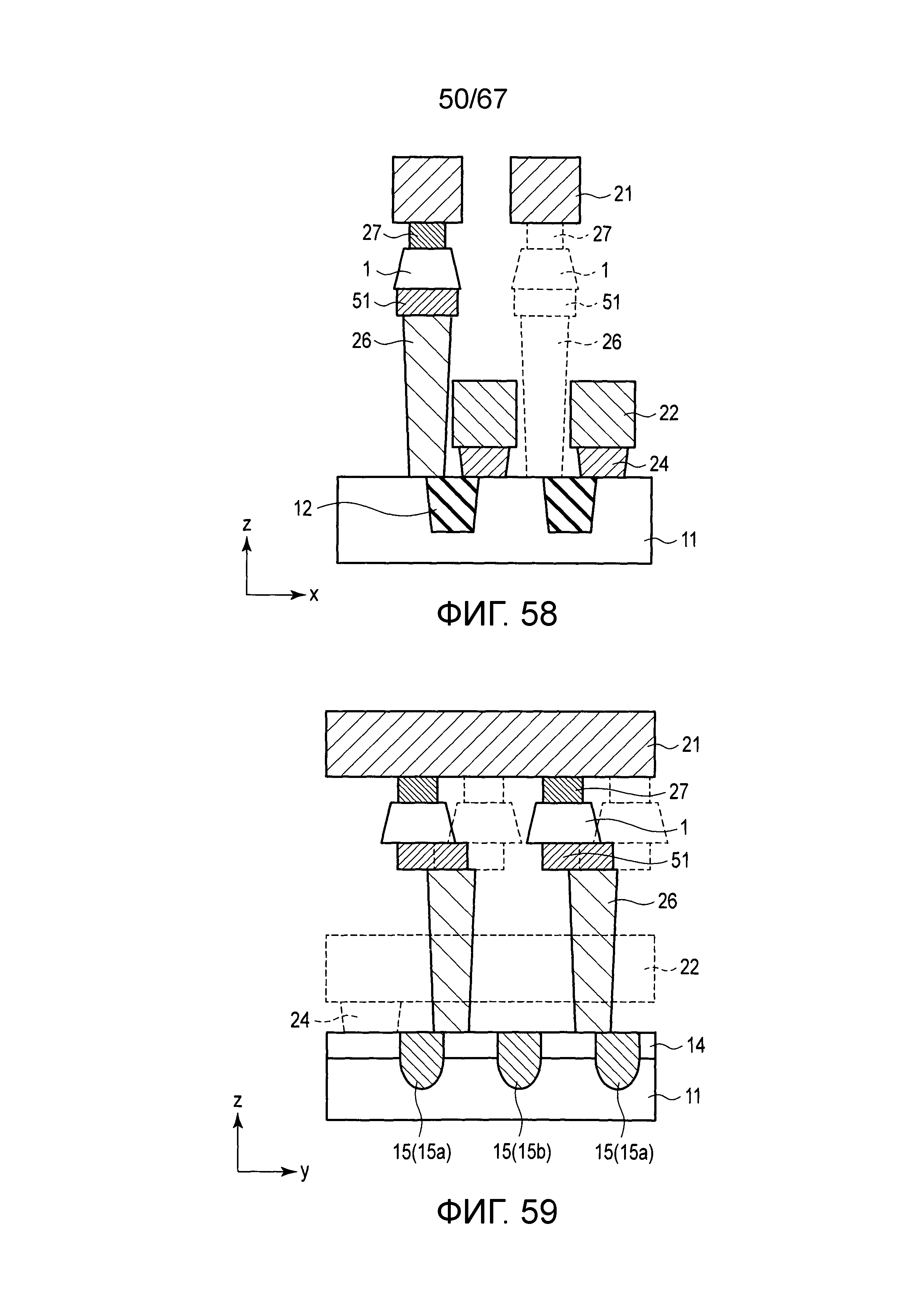

Фиг. 58 и 59 иллюстрируют виды вдоль линии LVIII-LVIII и линии LIX-LIX по фиг. 55-57, соответственно;

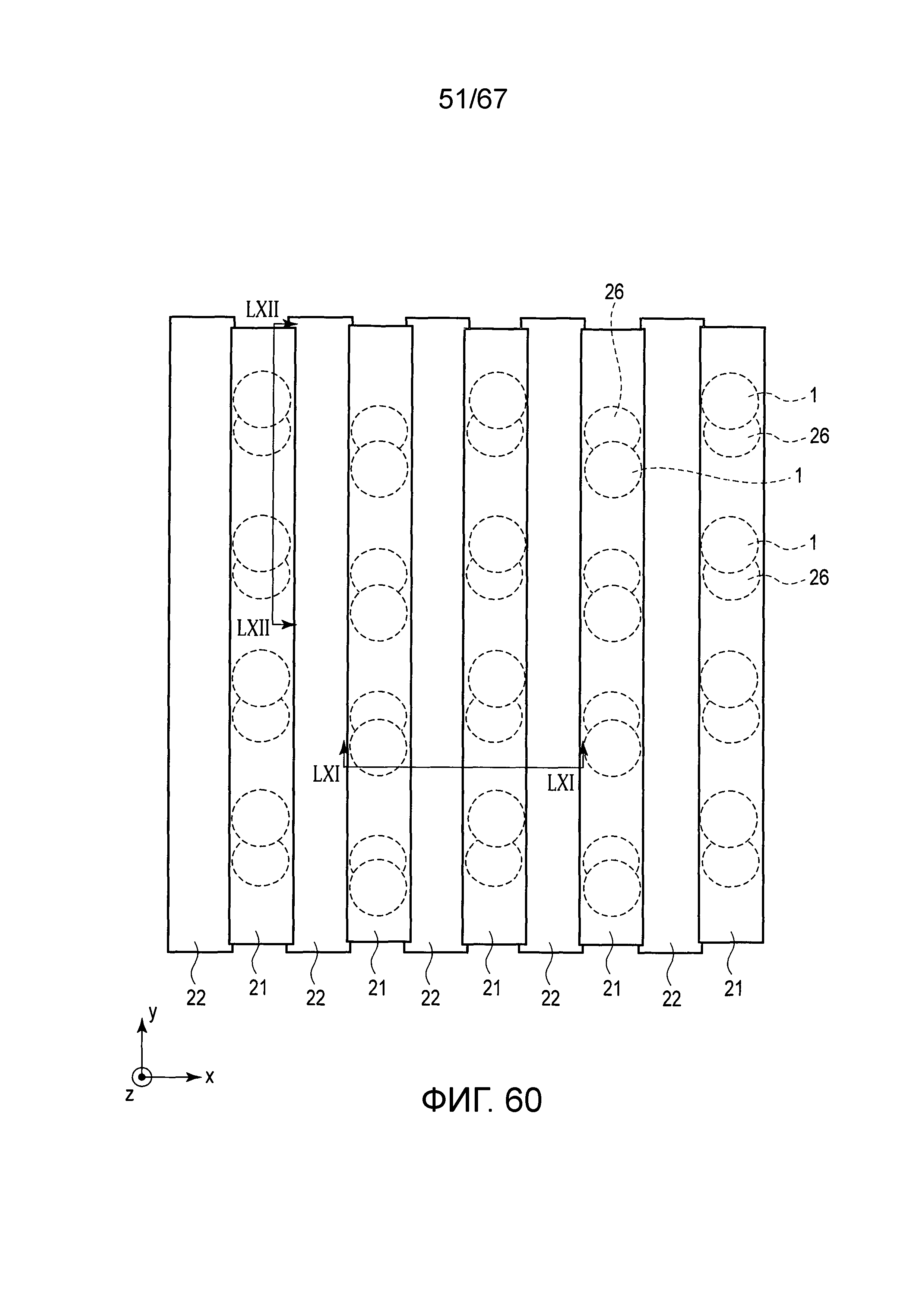

Фиг. 60 иллюстрирует вид части запоминающего устройства по четвертому примеру пятого варианта осуществления при виде сверху;

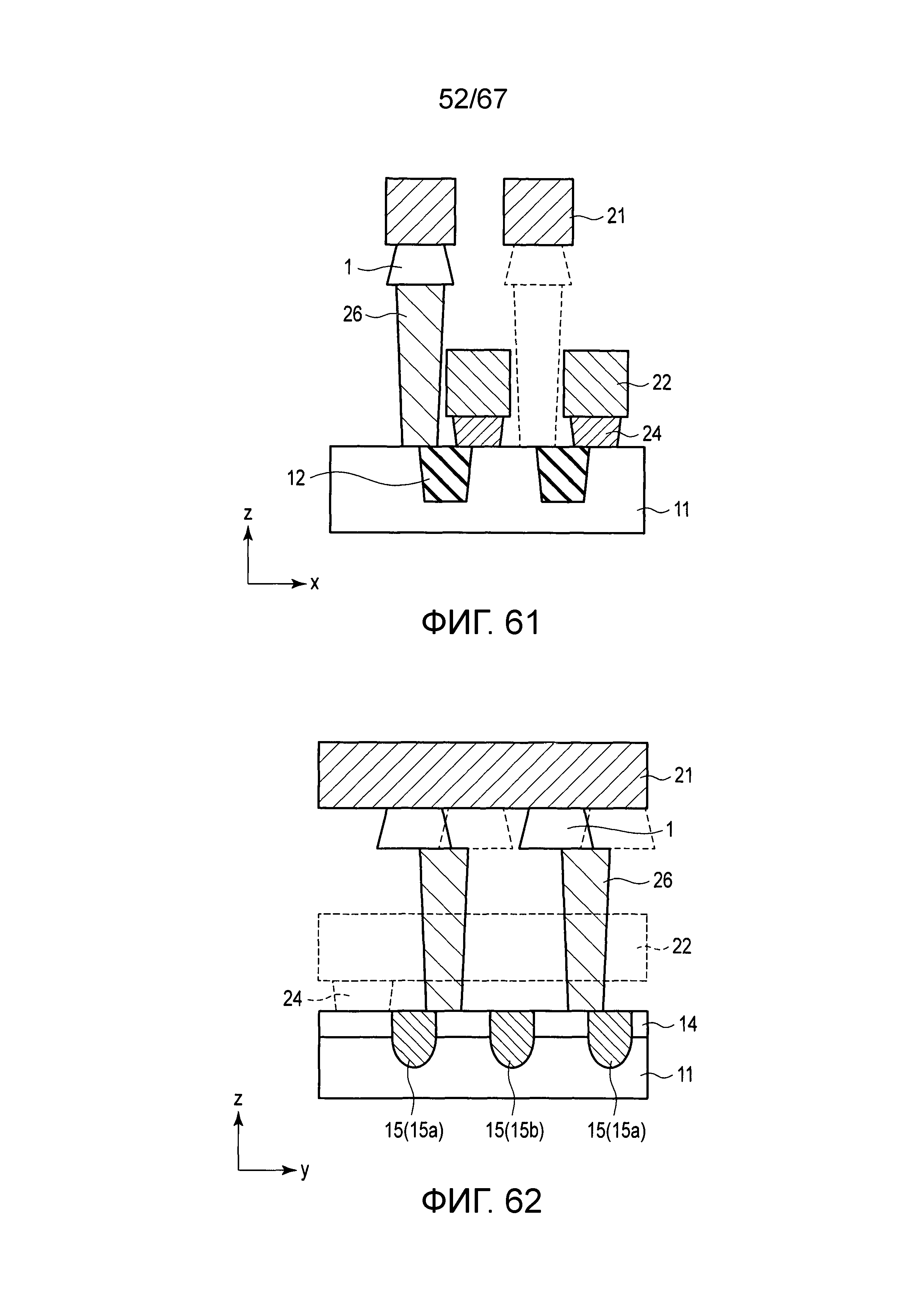

Фиг. 61 и 62 иллюстрируют виды вдоль линии LXI-LXI и линии LXII-LXII по фиг. 60, соответственно;

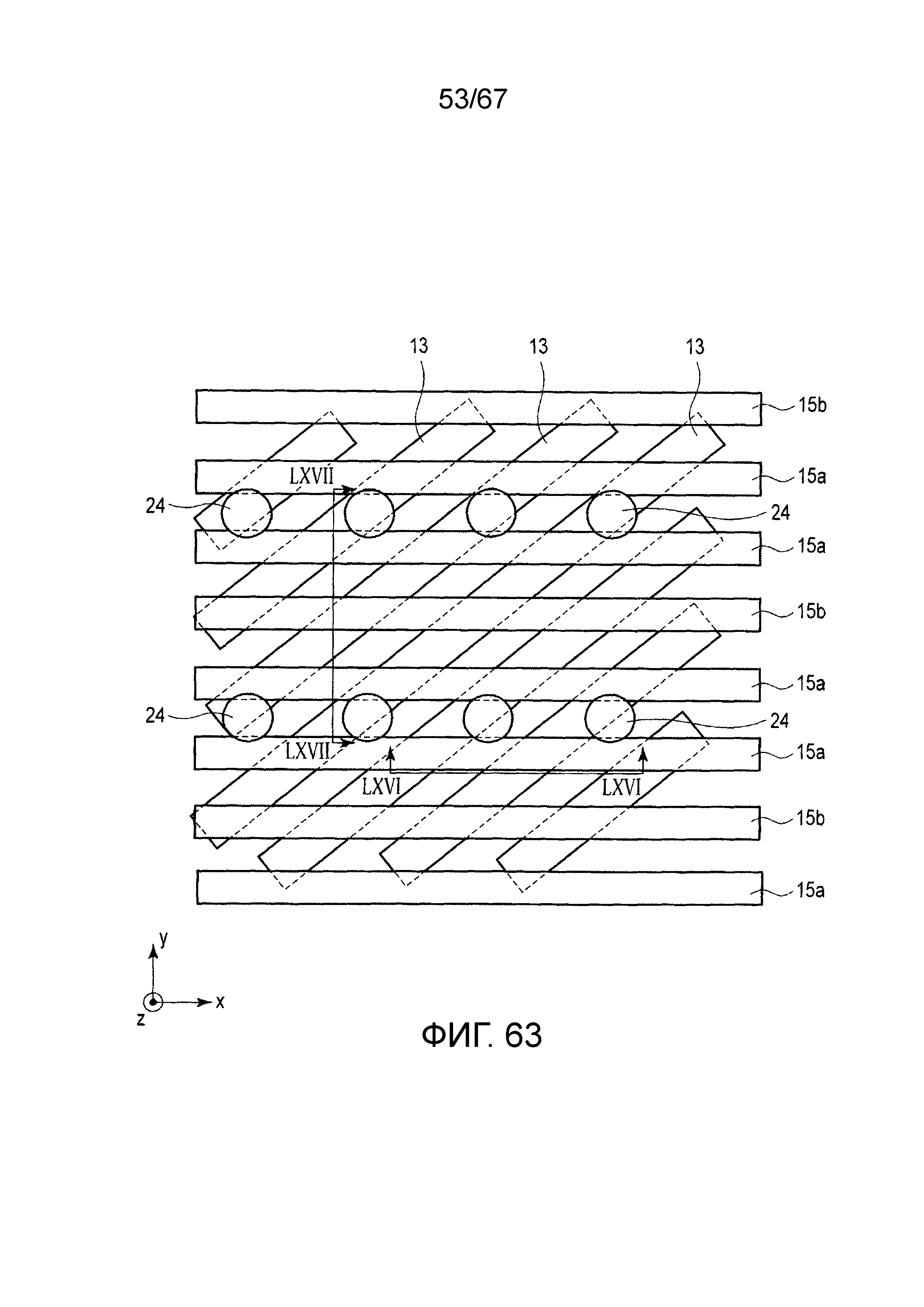

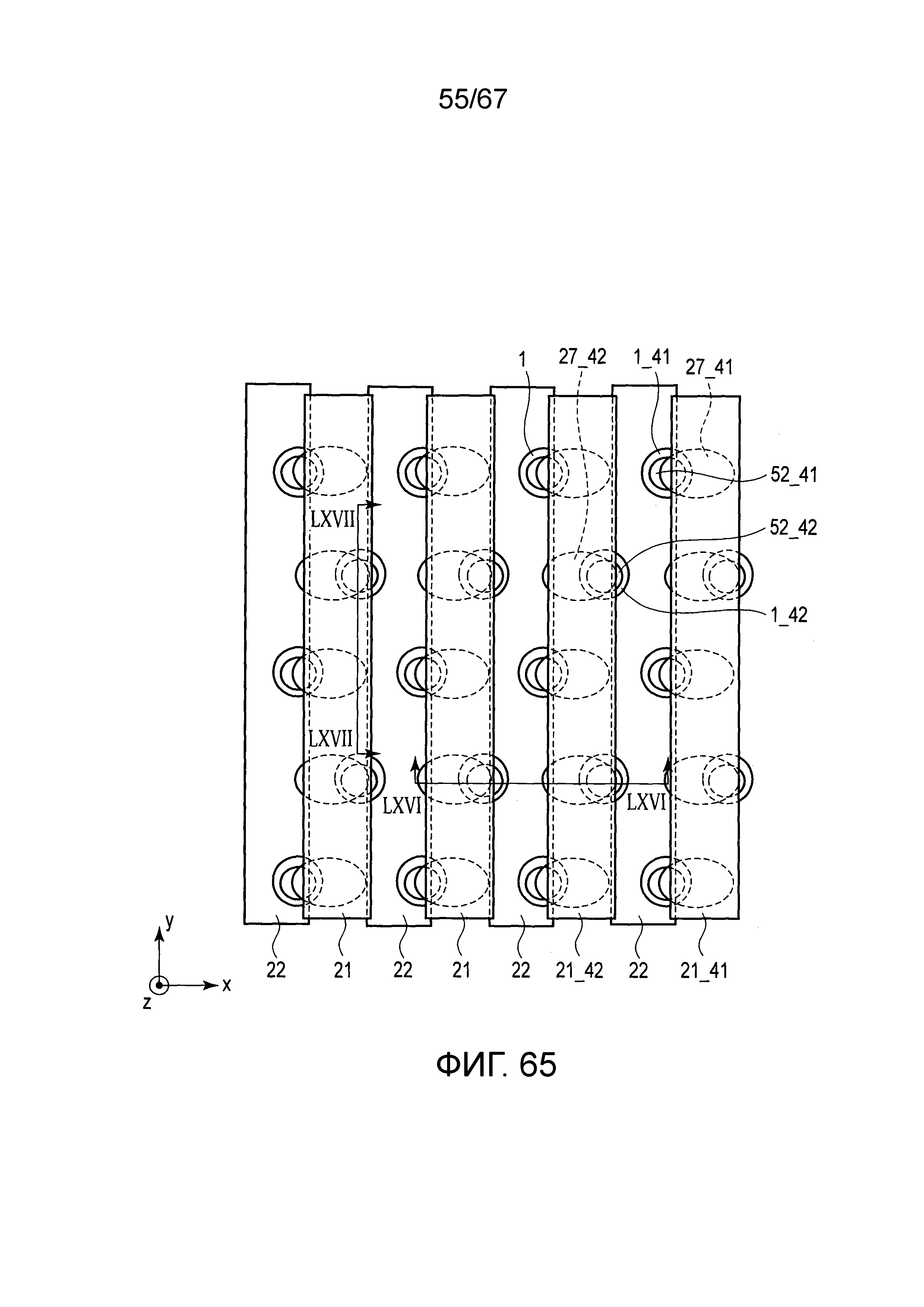

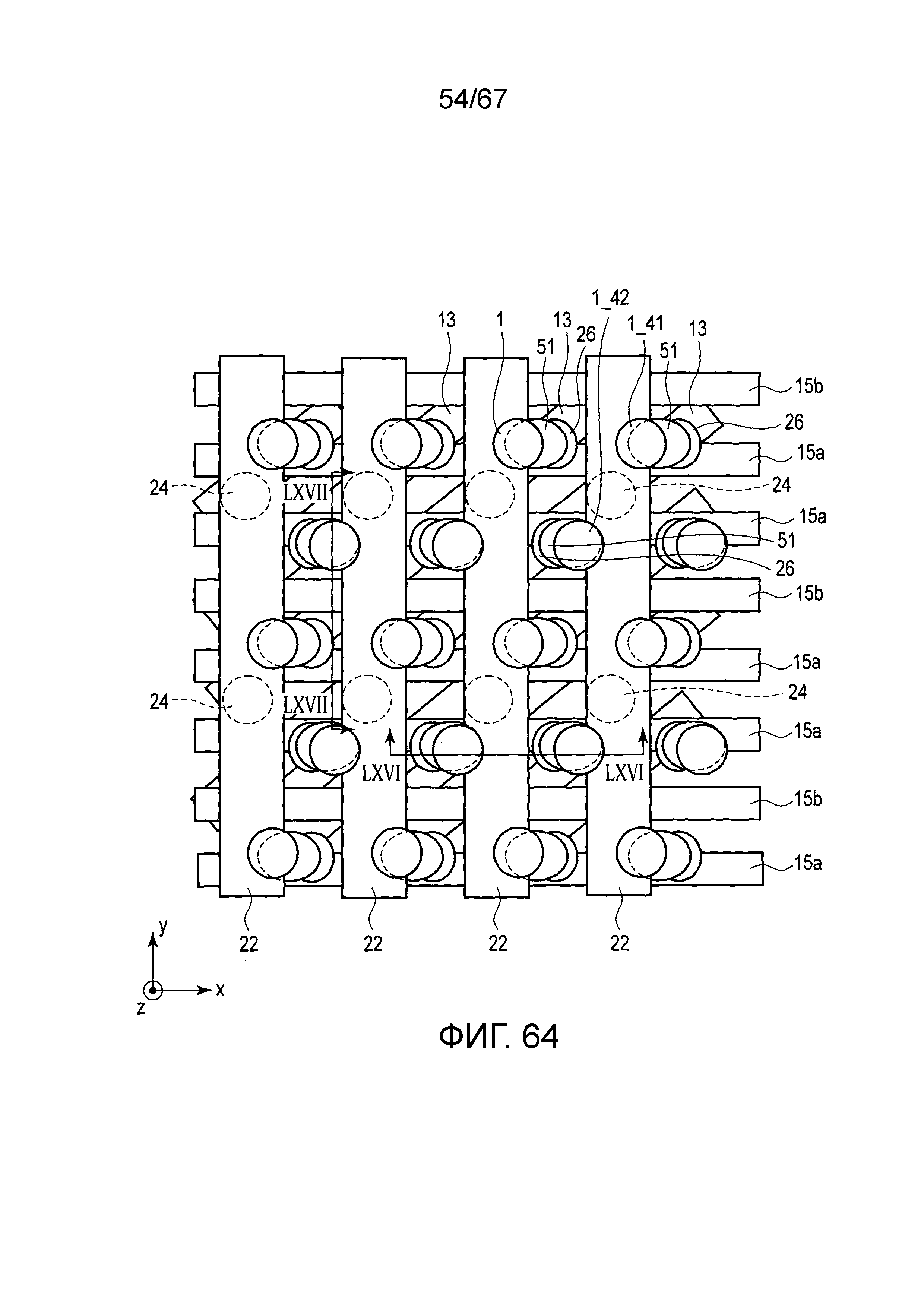

Фиг. 63-65 иллюстрируют виды части запоминающего устройства по первому примеру шестого варианта осуществления при виде сверху;

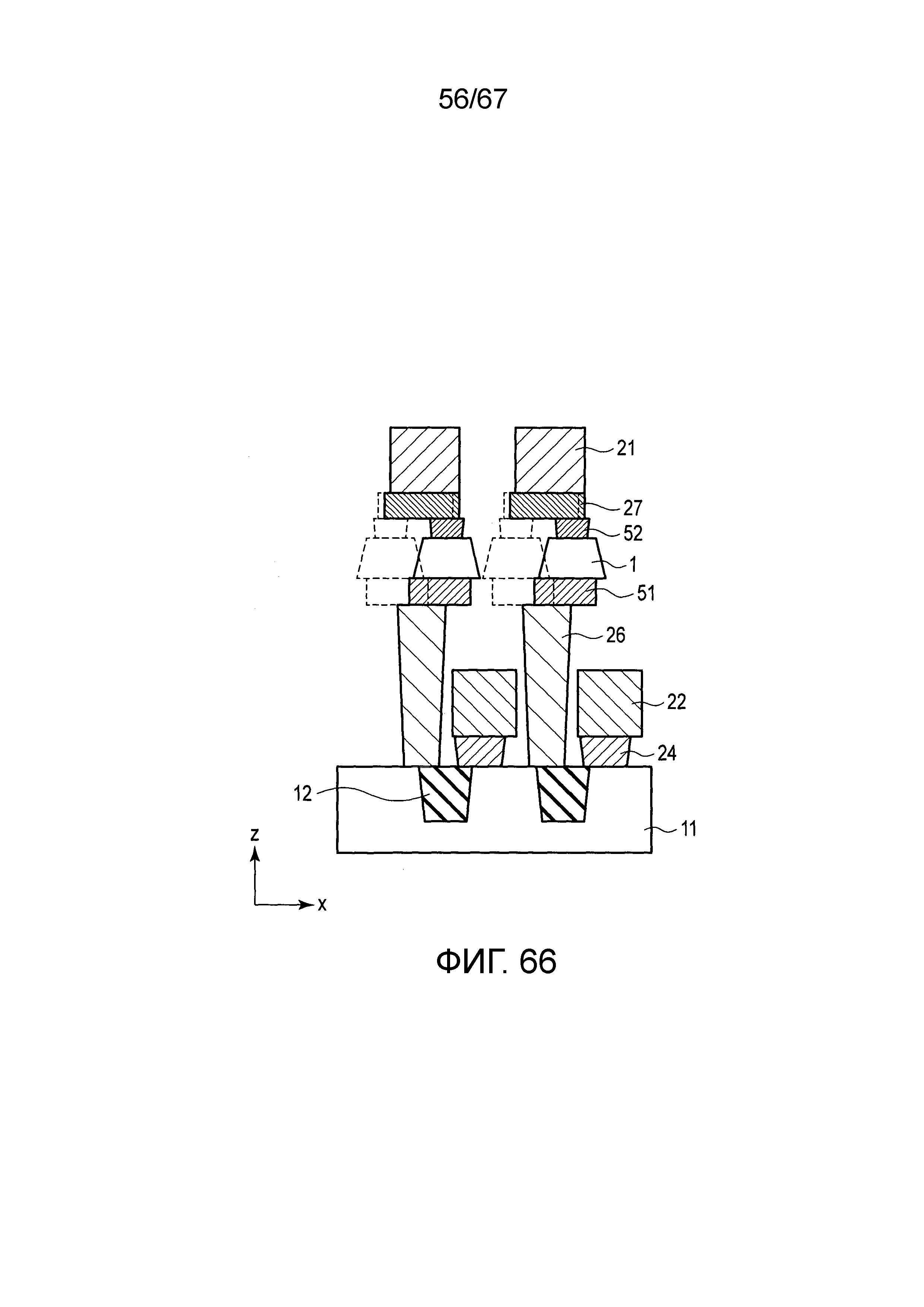

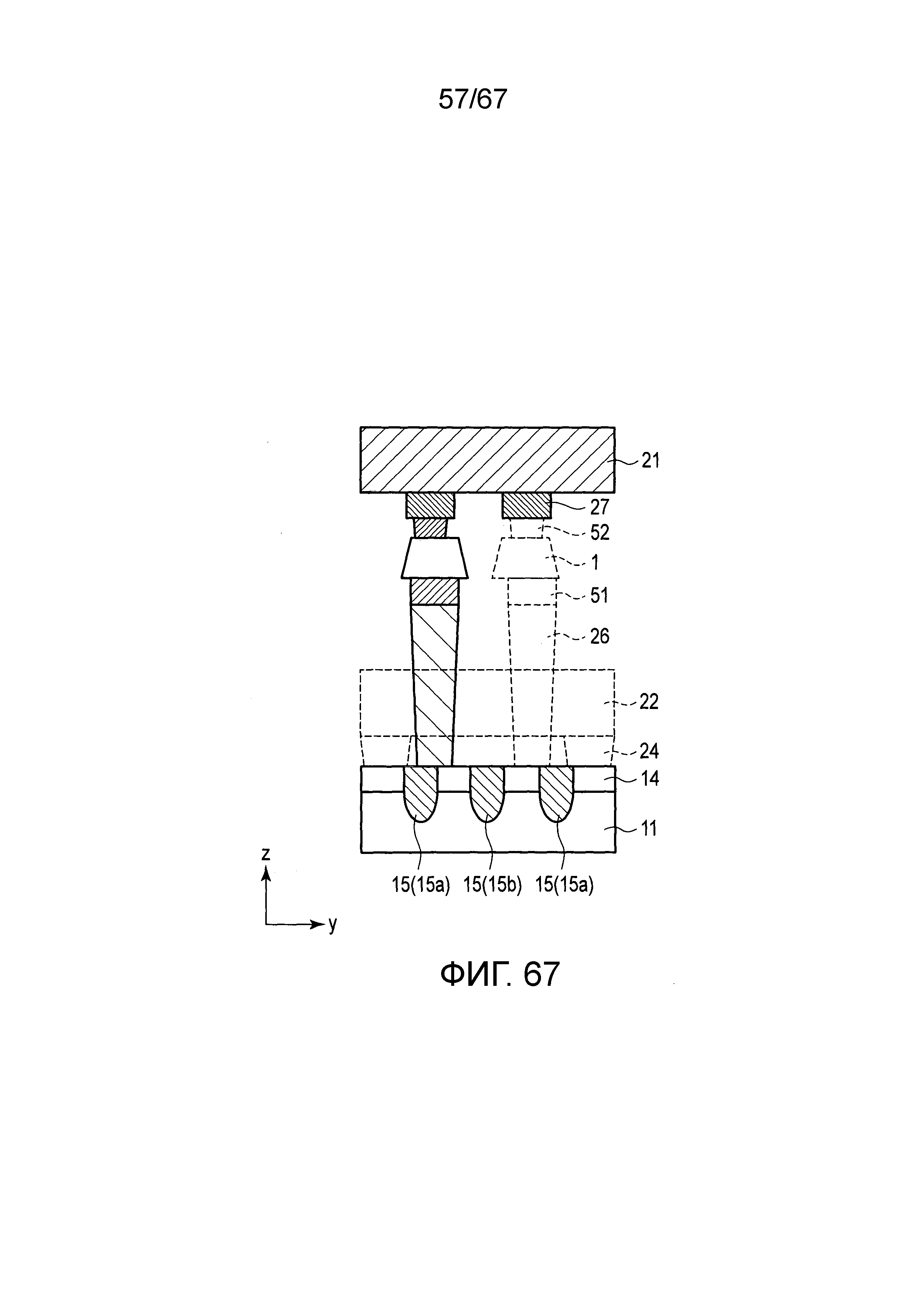

Фиг. 66 и 67 иллюстрируют виды вдоль линии LXVI-LXVI и линии LXVII-LXVII по фиг. 63-65, соответственно;

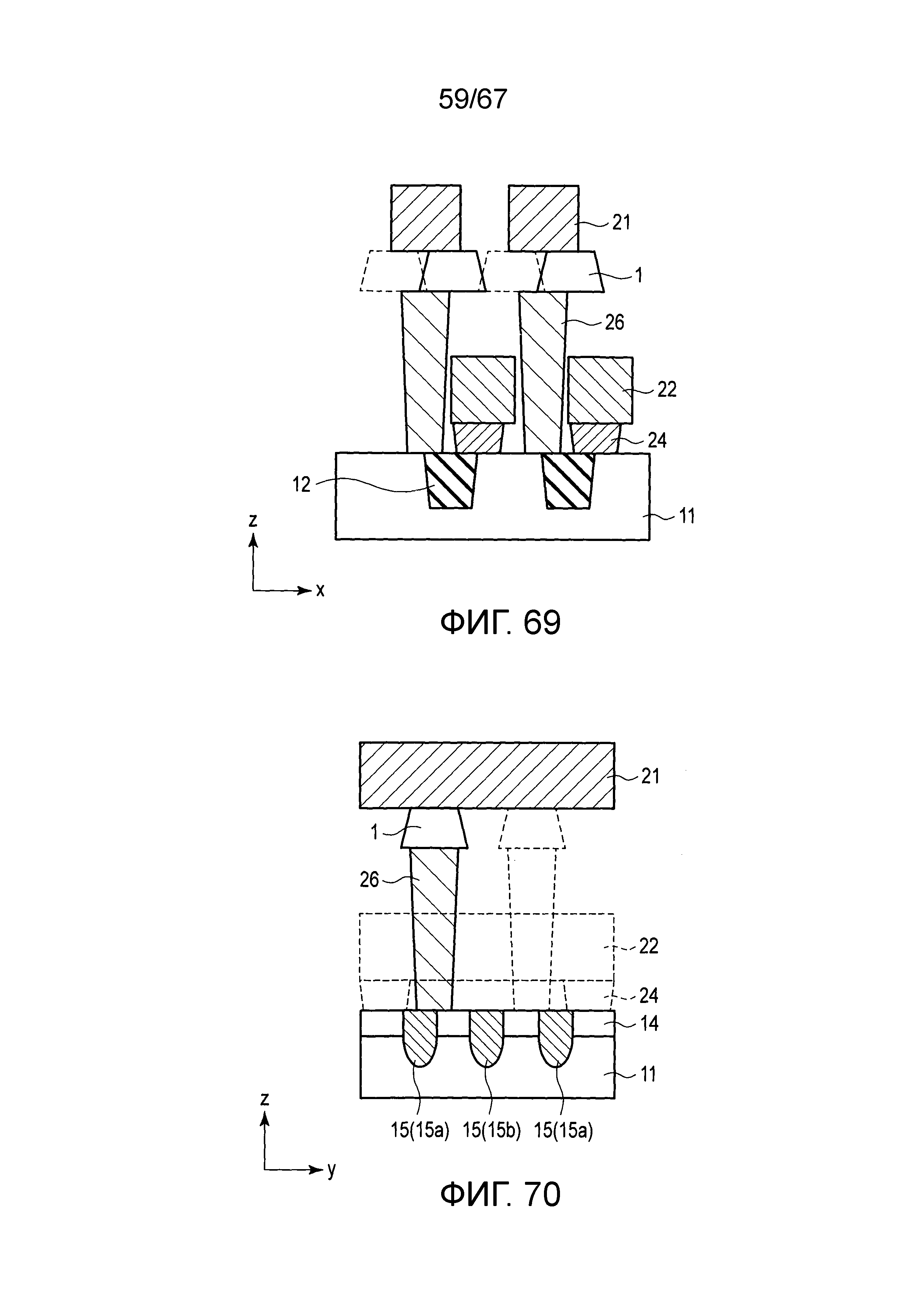

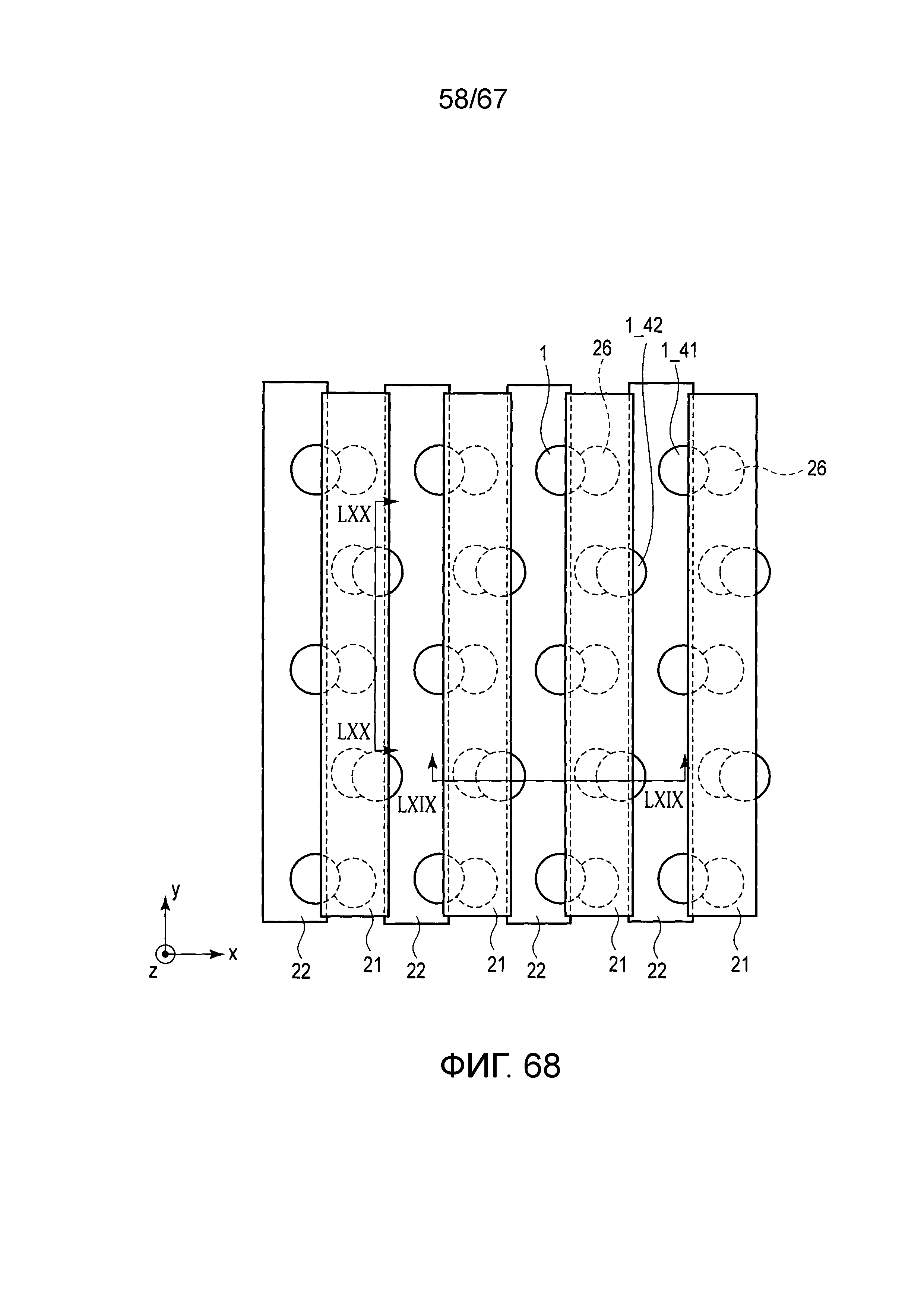

Фиг. 68 иллюстрирует вид части запоминающего устройства по второму примеру шестого варианта осуществления при виде сверху;

Фиг. 69 и 70 иллюстрируют виды вдоль линии LXIX-LXIX и линии LXX-LXX по фиг. 68, соответственно;

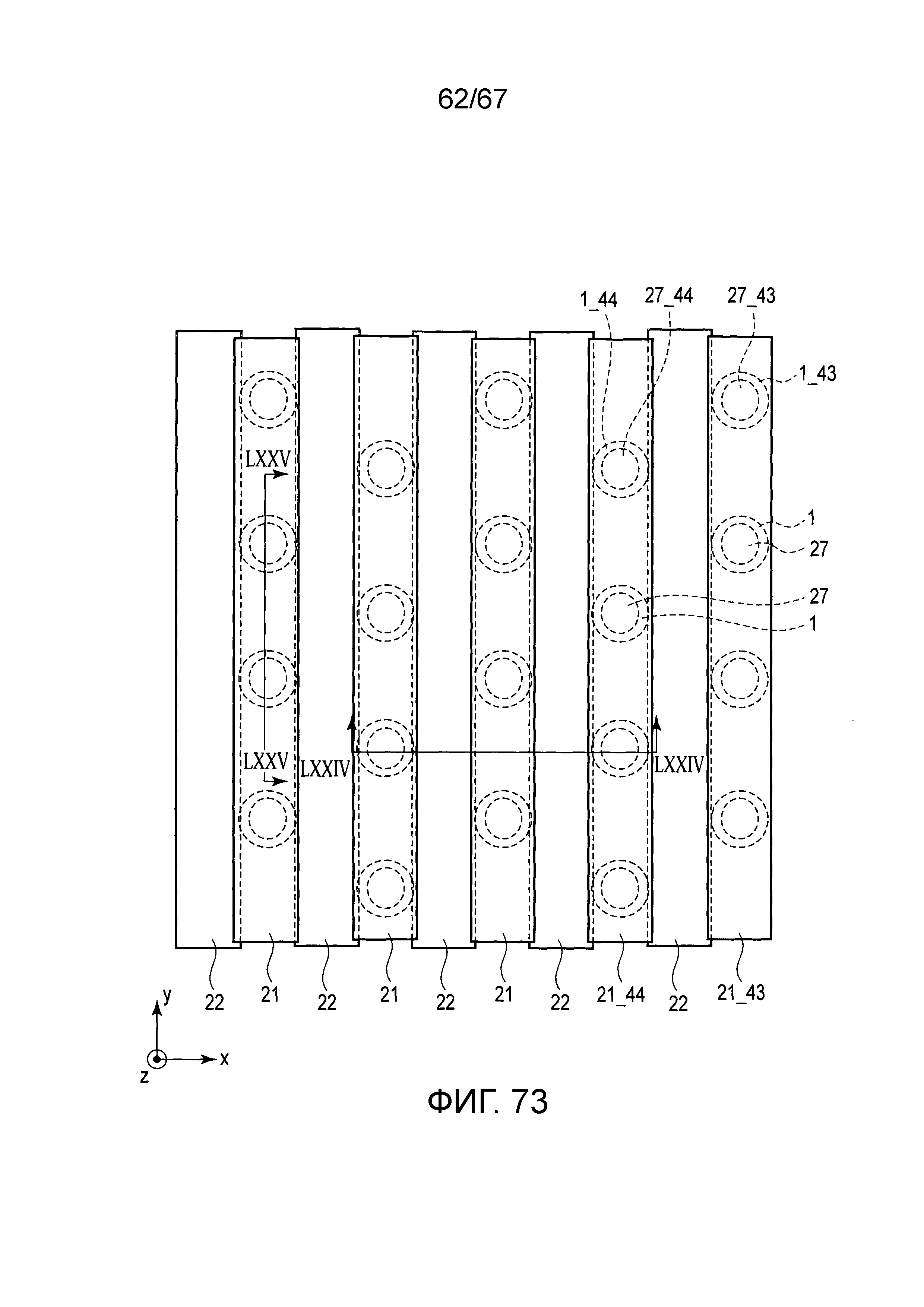

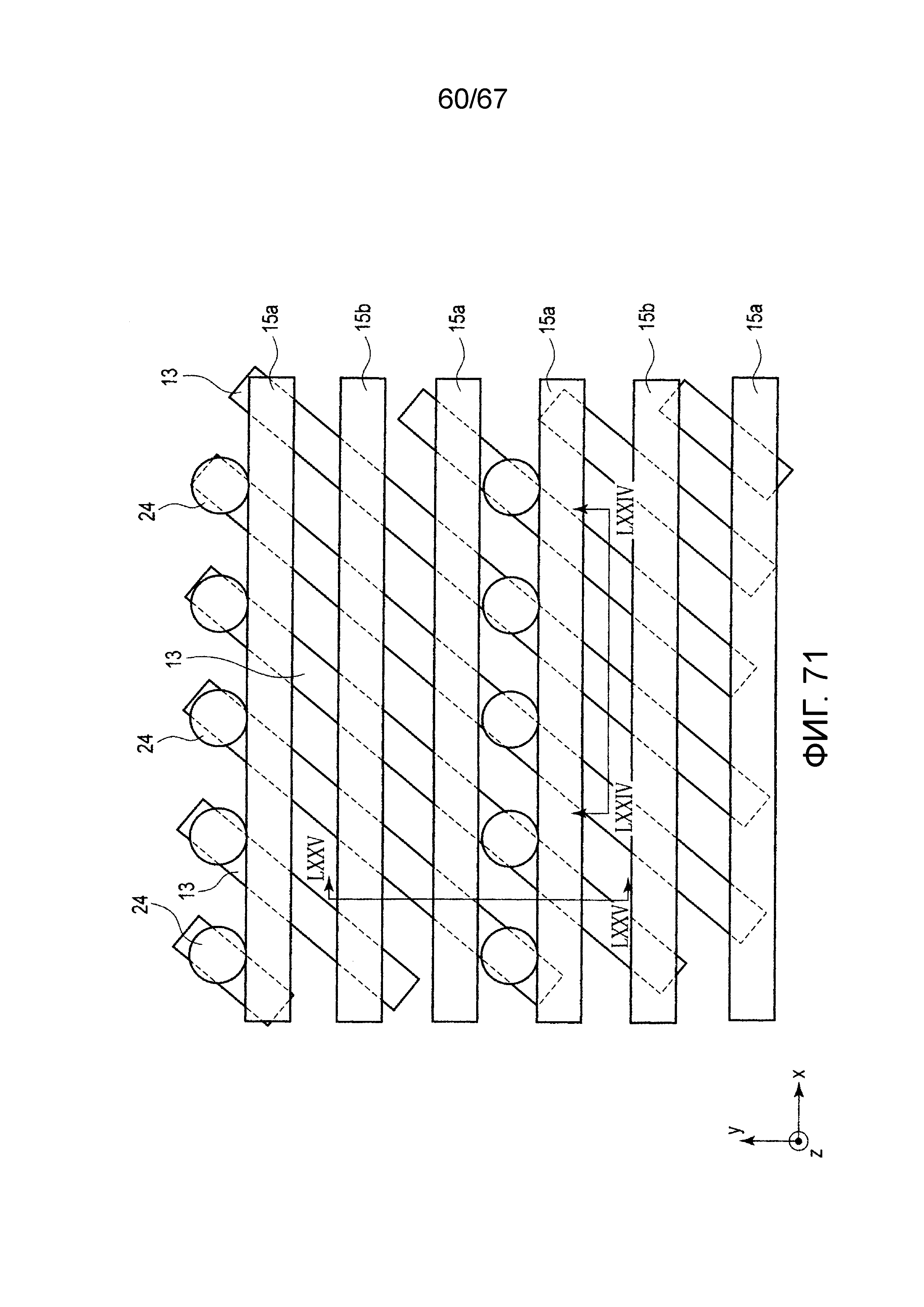

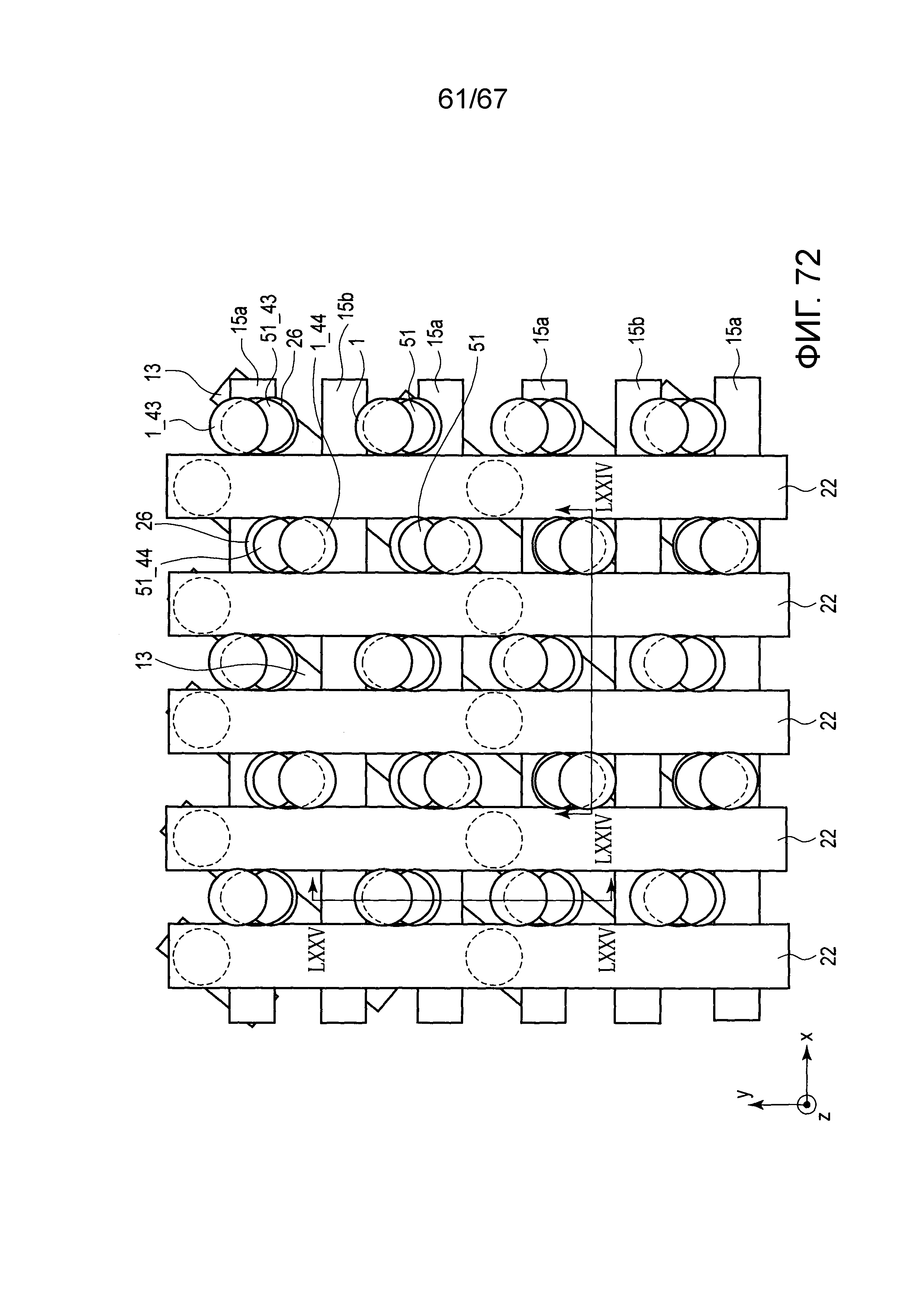

Фиг. 71-73 иллюстрируют виды части запоминающего устройства по третьему примеру шестого варианта осуществления при виде сверху;

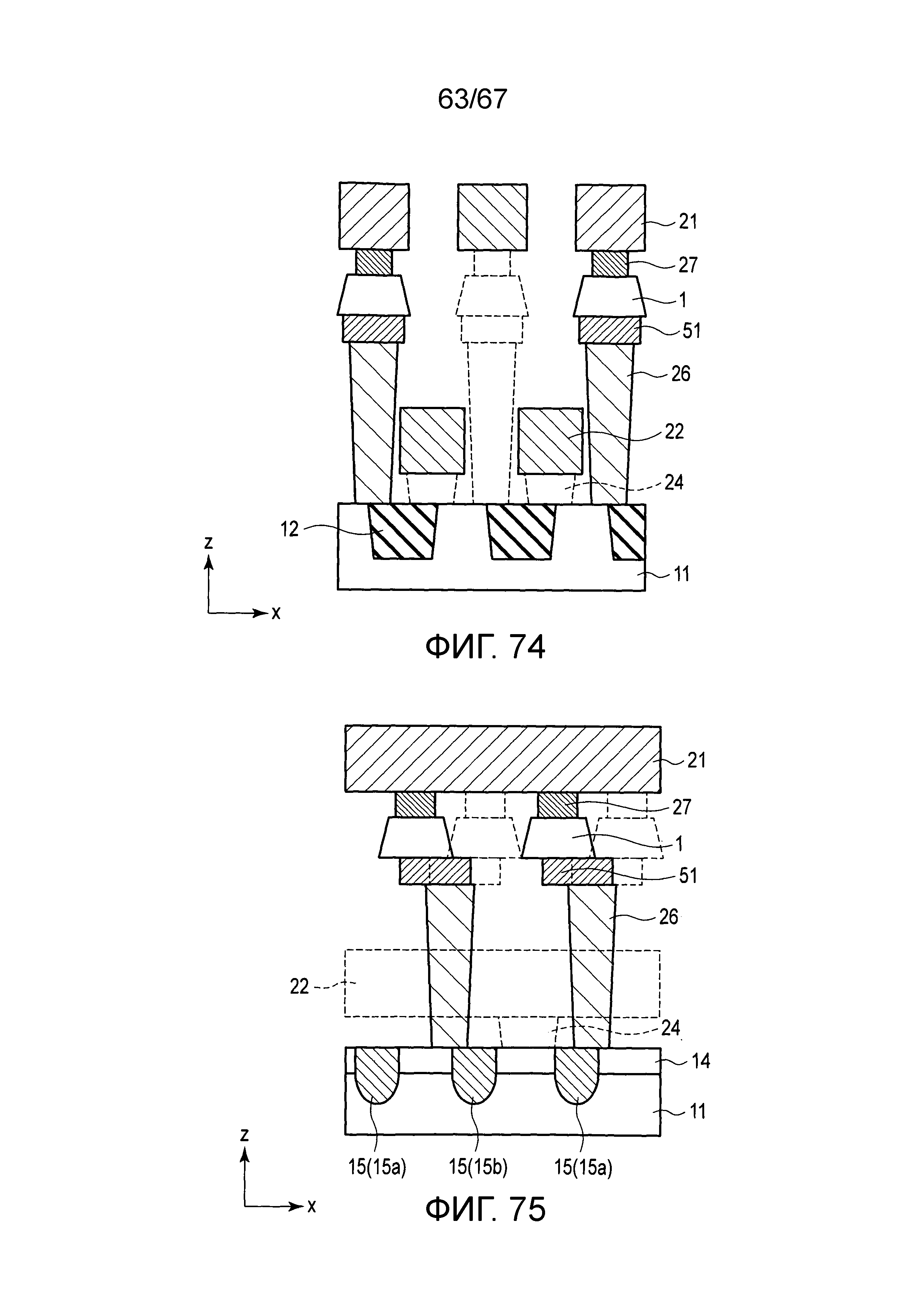

Фиг. 74 и 75 иллюстрируют виды вдоль линии LXXIV-LXXIV и линии LXXV-LXXV по фиг. 71-73, соответственно;

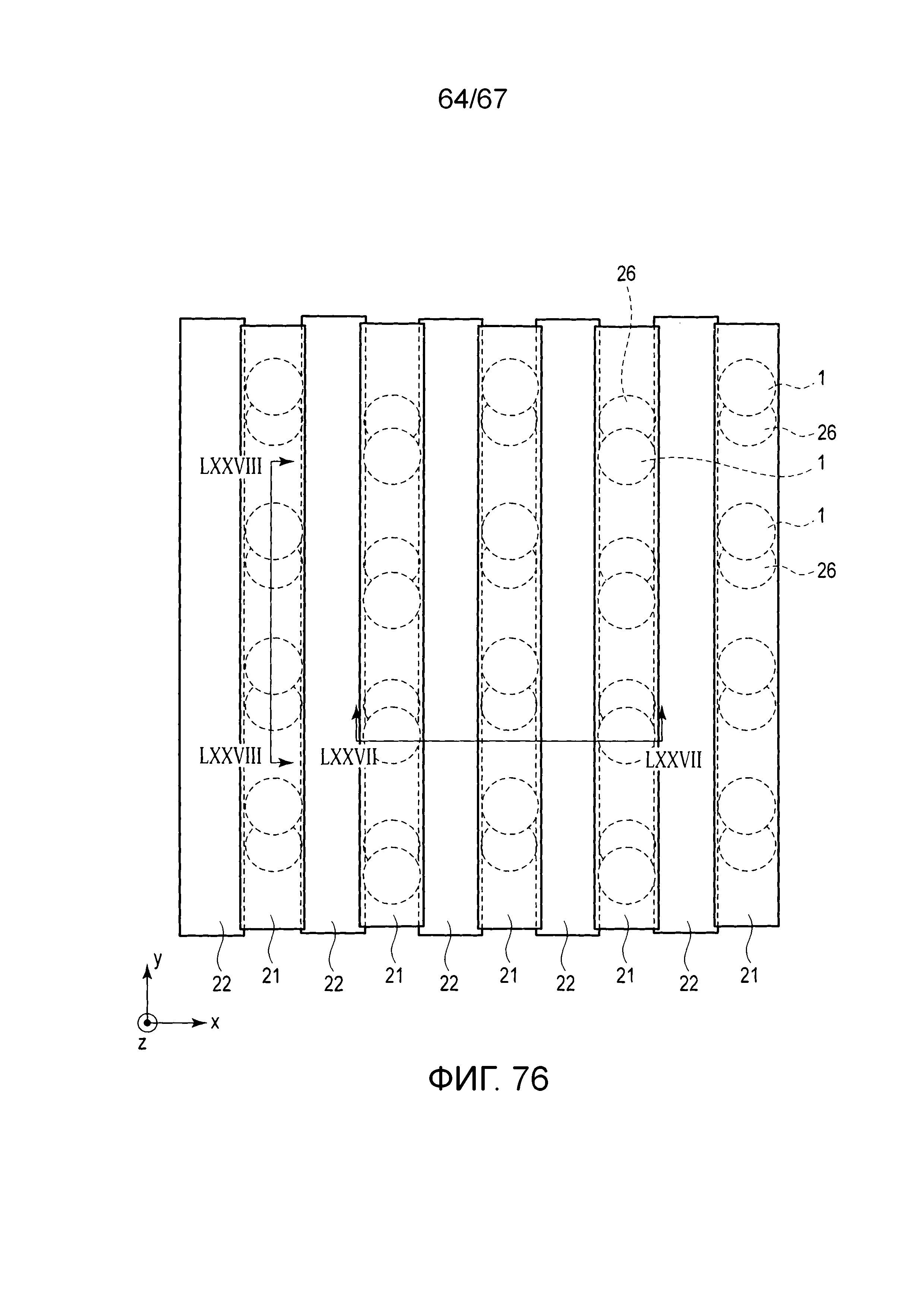

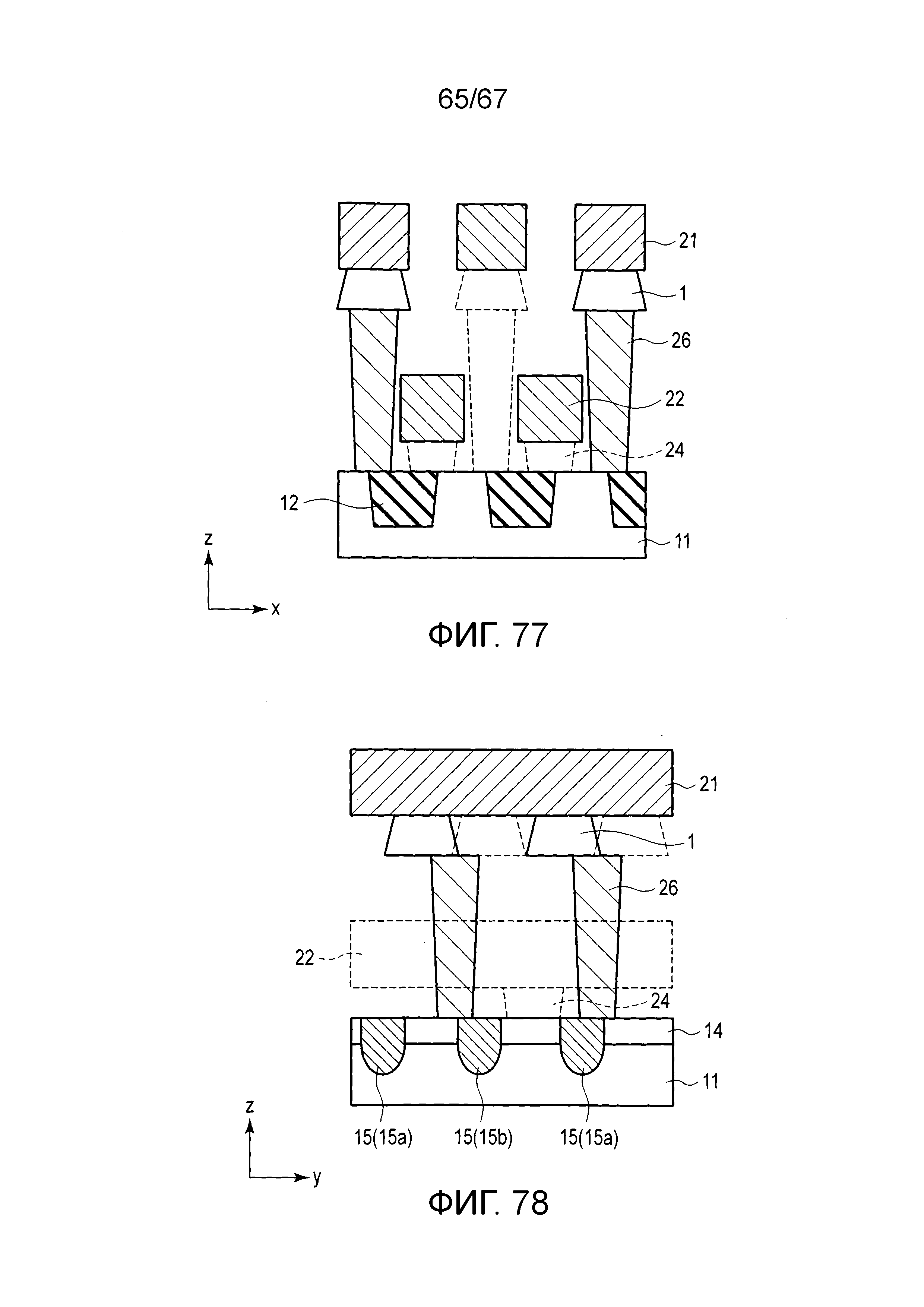

Фиг. 76 иллюстрирует вид части запоминающего устройства по четвертому примеру шестого варианта осуществления при виде сверху;

Фиг. 77 и 78 иллюстрируют виды вдоль линии LXXVII-LXXVII и линии LXXVIII-LXXVIII по фиг. 76;

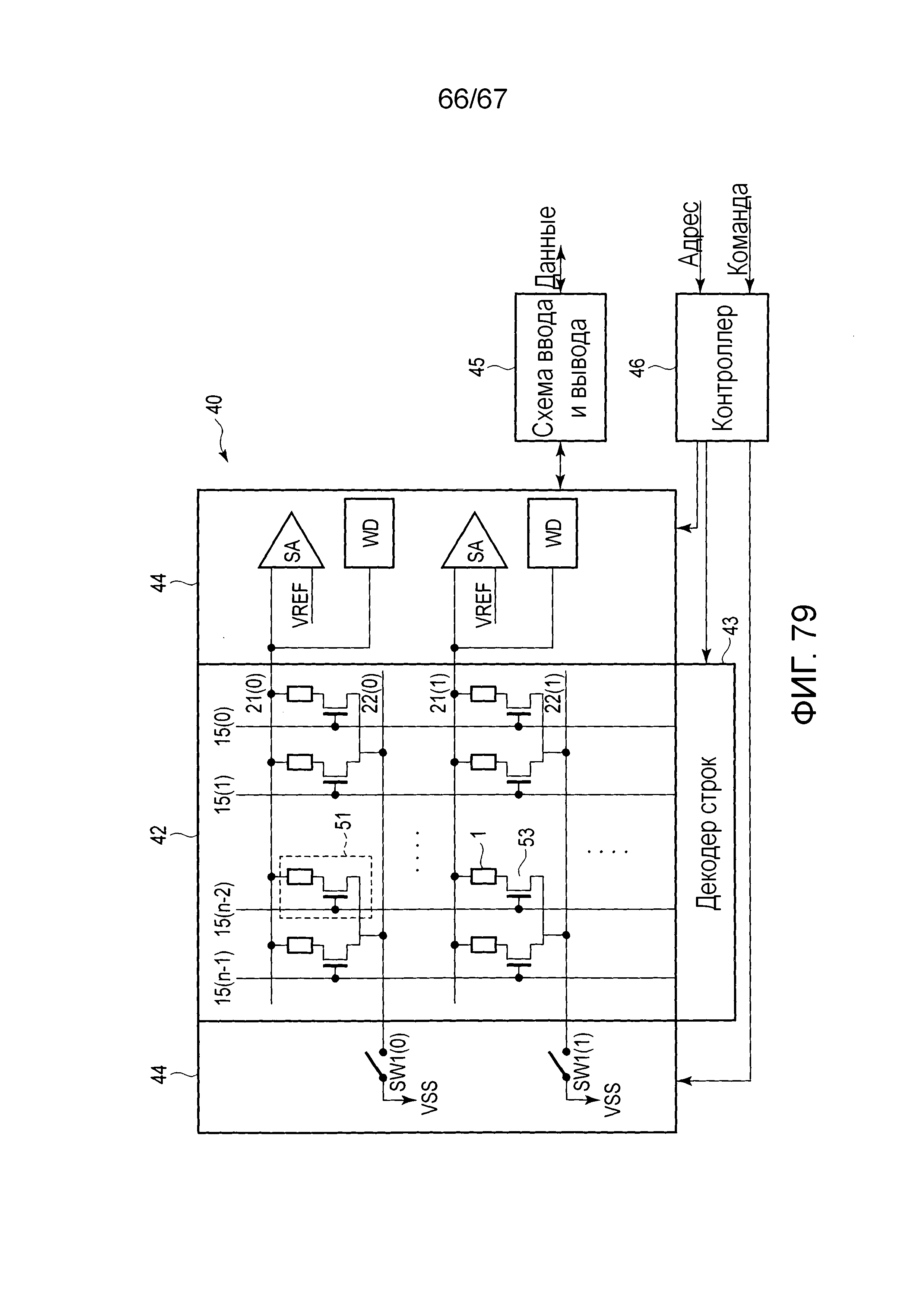

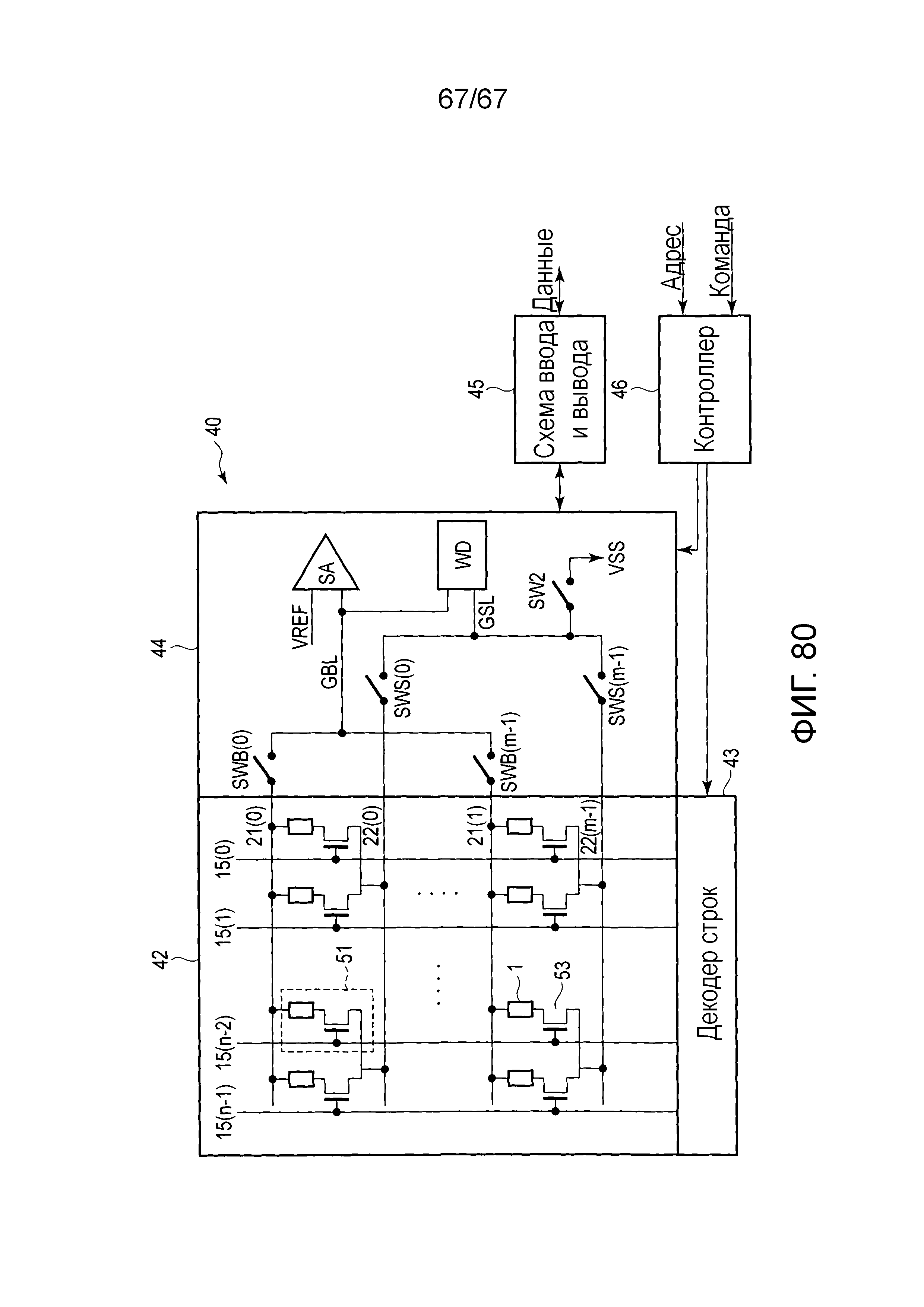

Фиг. 79 является принципиальной схемой части запоминающего устройства по седьмому варианту осуществления; и

Фиг. 80 является принципиальной схемой части второго примера запоминающего устройства по второму примеру седьмого варианта осуществления.

Подробное описание изобретения

Согласно одному варианту осуществления, магниторезистивное запоминающее устройство включает в себя подложку, имеющую первую поверхность, которая включает в себя первое направление; и запоминающие элементы, имеющие переключаемое сопротивление. Первый столбец запоминающих элементов, выстроенных в линию вдоль первого направления, отличается от смежного второго столбца запоминающих элементов, выстроенных в линию вдоль первого направления, в позициях запоминающих элементов в первом направлении.

Запоминающий элемент запоминающей ячейки MRAM включает в себя два контактных вывода и магнитный материал между ними. Запись данных в запоминающую ячейку выполняется посредством прохождения тока между двумя контактными выводами целевого записываемого запоминающего элемента. Один учитываемый аспект при разработке и проектировании MRAM заключается в предотвращении ошибочных записей в запоминающие элементы, отличные от целевого записываемого запоминающего элемента. Другими словами, ток, протекающий через запоминающие элементы, вызывает магнитное поле, которое может приводить к ошибочным записям в нецелевые записываемые запоминающие элементы с конкретной вероятностью. Вероятность ошибочных записей зависит от коэрцитивной силы (устойчивость в отношении внешнего магнитного поля) запоминающих элементов и абсолютной величины магнитного поля. Абсолютная величина магнитного поля является пропорциональной обратной величине расстояния между целевым записываемым запоминающим элементом и затрагиваемым нецелевым записываемым запоминающим элементом.

С другой стороны, для высокой интеграции MRAM, запоминающие элементы должны размещаться плотно. Один простой способ для этого состоит в том, чтобы уменьшать расстояния между запоминающими элементами. Тем не менее, чем короче расстояния между запоминающими элементами, тем проще возникают ошибочные записи, как описано выше. С другой стороны, чтобы формировать MRAM большой емкости, запоминающие элементы должны размещаться плотно. Таким образом, необходимо плотно размещать запоминающие элементы при обеспечении расстояний между смежными запоминающими элементами максимально можно большими.

Далее описываются варианты осуществления со ссылкой на чертежи. Компоненты с практически идентичными функциональностями и конфигурациями упоминаются с использованием идентичной ссылки с номером, и дублированные описания приводятся только при необходимости. Чертежи являются схематическими. Каждый вариант осуществления иллюстрирует устройство и способ для осуществления технической идеи этого варианта осуществления, и техническая идея варианта осуществления не указывает конкретное качество материала, форму, структуру, компоновку компонентов и т.д.

Первый вариант осуществления

Фиг. 1 иллюстрирует пример компоновки запоминающих элементов 100 и иллюстрирует вид запоминающих элементов при виде сверху. Запоминающие элементы 100 размещаются на плоскости из оси X и оси Y, которые пересекаются перпендикулярно, и выстраиваются в линию вдоль оси X и оси Y с регулярным интервалом A. Другими словами, кратчайший интервал запоминающих элементов составляет A. Одна из причин такой компоновки запоминающих элементов 100 в матричной форме заключается в простоте обработки ассоциированных межсоединений. Такая компоновка запоминающих элементов 100 приводит к области минимального рисунка, которая многократно размещается как A2.

Фиг. 2 иллюстрирует первый пример компоновки запоминающих элементов запоминающих ячеек запоминающего устройства согласно первому варианту осуществления и иллюстрирует вид запоминающих элементов 1 при виде сверху. Запоминающий элемент 1 представляет собой элемент, который включает в себя магнитный туннельный переход, как описано. Компоновка запоминающих элементов 1 включает в себя несколько столбцов (т.е. наборов запоминающих элементов вдоль оси Y на идентичной координате по оси X), как проиллюстрировано на фиг. 2. В каждом столбце запоминающих элементов (столбце запоминающих элементов), запоминающие элементы 1 выстраиваются в линию с регулярным интервалом A. Напротив, запоминающие элементы 1 из смежных столбцов запоминающих элементов не выстраиваются в линию вдоль оси X. Вместо этого, запоминающие элементы 1 расположены в вершинах и в центре правильного шестиугольника поверх трех столбцов. Затем такие правильные шестиугольники заполнены в плоскости, состоящей из оси X и оси Y. Другими словами, запоминающие элементы 1 расположены в вершинах и в центрах сотовой структуры, которая продолжается вдоль плоскости, состоящей из оси X и оси Y.

Запоминающие элементы 1 расположены в вершинах и в центре шестиугольника, и, следовательно, все запоминающие элементы 1, смежные в шестиугольнике, имеют равный интервал. Аналогично, такие шестиугольники заполнены вдоль плоскости, состоящей из оси X и оси Y, и следовательно, каждый запоминающий элемент 1 имеет равный интервал со всеми смежными запоминающими элементами 1. Тем не менее, когда компоненты формируются с помощью процесса изготовления полупроводников, т.е. когда формирование маски с отверстиями в ней на пленке и травление с отверстиями, чтобы обрабатывать пленку, повторяется, может возникать непреднамеренное неточное совмещение маски, как известно специалистам в данной области техники. Это может приводить к компонентам, сдвинутым относительно намеченных позиций. Следовательно, позиция конкретного компонента, указываемого в этом подробном описании и в формуле изобретения, также включает в себя позиции, сдвинутые относительно намеченной позиции вследствие варьирования процесса изготовления. Например, описание запоминающих элементов 1 "расположены в вершинах и в центре правильного шестиугольника" не является строгим требованием и также включает в себя запоминающие элементы 1, сдвинутые непредотвратимо.

Запоминающие элементы 1 в столбцах с четным номером размещаются в матричной форме вдоль оси Y и оси X, а запоминающие элементы 1 в столбцах с нечетным номером, размещаются в матричной форме, отличающейся от матрицы запоминающих элементов 1 столбцов с четным номером, и развертываются вдоль оси X и оси Y. Каждый запоминающий элемент 1 каждого столбца запоминающих элементов не находится на линии, соединяющей запоминающие элементы идентичной строки (т.е. выстроенные в линию по оси X) в обоих смежных столбцах запоминающих элементов. Вместо этого, запоминающие элементы 1 размещаются таким образом, что каждый запоминающий элемент 1 в конкретном столбце запоминающих элементов расположен на протяжении вдоль оси X от позиции между двумя смежными запоминающими элементами 1 в смежном столбце запоминающих элементов. Помимо этого, каждый запоминающий элемент 1 находится на расстоянии A от ближайших четырех запоминающих элементов в обоих смежных столбцах запоминающих элементов. Следовательно, каждый запоминающий элемент 1 и два ближайших запоминающих элемента 1 в обоих смежных столбцах запоминающих элементов формируют равносторонний треугольник, и, следовательно, различные запоминающие элементы 1 из различных столбцов запоминающих элементов выстраиваются в линию вдоль прямой линии, наклоненной относительно оси X на 60 градусов.

Вследствие вышеописанной компоновки запоминающих элементов 1, ось X является параллельной прямой линии, соединяющей пару запоминающих элементов в вершинах правильного шестиугольника, противостоящих через центр (т.е. которые находятся на диагонали). Кроме того, ось Y является параллельной прямой линии, соединяющей два запоминающих элемента, которые ни находятся в вершинах правильного шестиугольника, противостоящих через центр (т.е. которые находятся на диагонали), ни примыкают вдоль края правильного шестиугольника.

Запоминающие элементы 1 сохраняют данные энергонезависимым способом согласно состоянию намагничивания и имеют такую структуру, как проиллюстрировано, например, на фиг. 3. Запоминающий элемент 1 включает в себя два магнитных слоя FM и VM и немагнитные слои NM между ними. Магнитный слой FM имеет фиксированную ориентацию намагничивания, а магнитный слой VM имеет переменную ориентацию намагничивания. Магнитные слои FM и VM имеют ось легкого намагничивания (проиллюстрирована посредством стрелок) вдоль направления, которое пересекает поверхности раздела слоев FM, NM и VM. Магнитные слои FM и VM могут иметь ось легкого намагничивания вдоль поверхностей раздела слоев FM, NM и VM. Слои FM, NM и VM предоставляются между электродами EA и EB. Элемент MTJ демонстрирует минимальные и максимальные сопротивления, когда ориентации намагничивания магнитных слоев FM и VM являются параллельными и антипараллельными, соответственно. Состояния, которые демонстрируют два различных сопротивления, назначаются данным двух значений, соответственно. Например, параллель и антипараллель для ориентаций намагничивания магнитных слоев FM и VM ассоциированы с состоянием, в котором биты "0" и "1" сохраняются, соответственно. Когда ток IwP протекает из магнитного слоя VM к магнитному слою FM, ориентации намагничивания магнитных слоев FM и VM становятся параллельными. Напротив, когда ток IwAP протекает из магнитного слоя FM к магнитному слою VM, ориентации намагничивания магнитных слоев FM и VM становятся антипараллельными. Для считываемых данных, ток Ir передается, например, из электрода EB к электроду EA, и состояние сопротивления запоминающего элемента 1 определяется.

Фиг. 2 связан с примером, в котором смежные запоминающие элементы 1 имеют расстояние A, идентичное расстоянию A между сетками по фиг. 1. Согласно этому примеру, область для размещения конкретного числа запоминающих элементов 1 снижается до 0,87 от области для размещения идентичного числа запоминающих элементов 1 в примере по фиг. 1. Следовательно, при использовании компоновки фиг. 2, в области, идентичной области для компоновки по фиг. 1, идентичное число запоминающих элементов 1 может размещаться с большим интервалом. Фиг. 4 иллюстрирует такой пример, иллюстрирует второй пример компоновки запоминающих элементов запоминающих ячеек запоминающего устройства согласно первому варианту осуществления и иллюстрирует вид запоминающих элементов 1 при виде сверху. В примере по фиг. 4, интервал запоминающих элементов 1 составляет 1,2 А. Согласно примеру по фиг. 4, влияние магнитного поля в запоминающих элементах 1 меньше влияния магнитного поля в примере по фиг. 2.

Далее описываются примеры структуры с компоновкой запоминающих ячеек по фиг. 2 и 4 со ссылкой на фиг. 5-16. Фиг. 5-16 иллюстрируют часть матрицы ячеек запоминающего устройства по первому варианту осуществления.

Фиг. 5 иллюстрирует вид запоминающего устройства по первому примеру первого варианта осуществления при виде сверху. Фиг. 6 и 7 иллюстрируют секции вдоль линии VI-VI и линий VII-VII по фиг. 5, соответственно. Как проиллюстрировано на фиг. 5-7, изолятор 12 развязки элементов узкощелевой изоляции (STI) формируется, например, на поверхности полупроводниковой подложки 11. Изолятор развязки элементов окружает активные области 13, чтобы разделять активные области 13. Активные области 13 имеют прямоугольную форму вдоль оси Y. Активные области 13 включают в себя отдельные области 14 истока/стока на поверхности.

Подложка 11 также имеет электроды 15 затвора на поверхности. Электроды 15 затвора представляют собой так называемые заглубленные электроды затвора и, в частности, заглубляются в канавках на поверхности подложки 11 с размещенными изоляторами затвора (не показаны) на поверхности канавки. Когда конкретная область (например, канавка) описывается как "заглубленная" в этом подробном описании, это не обязательно означает, что область полностью заглублена. Вместо этого, специалисты в данной области техники должны понимать, что "заглубляться" включает в себя область, предназначенную для заглубления, но частично незаглубленную или с другим материалом, размещенным в промежутке.

Электроды 15 затвора продолжаются вдоль оси X с равными интервалами вдоль оси Y. Электроды 15 затвора также упоминаются как числовые линии. Каждый электрод 15 затвора, в секции между парой областей 14 истока/стока на обеих сторонах, составляет полевой транзистор на основе перехода металл-оксид-полупроводник (MOSFET) с этими областями 14 истока/стока. Два смежных электрода 15 затвора составляют пару, и электрод 15b затвора между двумя смежными парами электродов затвора задается фиксированно равным конкретному потенциалу, электрически изолирует электроды 15 затвора на обеих сторонах и не составляет транзистор ячейки. Электроды затвора, отличные от электродов 15b затвора, в дальнейшем называются электродами 15a затвора при различении от электродов 15b затвора.

В этом подробном описании, когда первый элемент ссылки с номером представляет собой число или букву, а ее второй элемент представляет собой букву или число с/без дефиса или подчеркивания, второй элемент отличает первые элементы идентичного вида друг от друга. Когда несколько первых элементов не должны отличаться друг от друга, описание без второго элемента используется и ссылается на все ссылки с номерами, имеющие первый элемент.

Запоминающие элементы 1 формируются в компоновке, проиллюстрированной на фиг. 2 и 4 выше подложки 11 вдоль оси Z. Каждый запоминающий элемент 1 соединяется с верхней частью контактного столбика 26 в нижней части. Каждый контактный столбик 26 находится в контакте с областью 14 истока/стока в нижней части. Транзистор ячейки, включающий в себя пару областей истока/стока на обеих сторонах конкретного электрода 15 затвора и запоминающего элемента, электрически соединенного с одной из этой пары областей истока/стока, составляет запоминающую ячейку. Потенциал электрода 15 затвора, который является частью транзистора ячейки в запоминающей ячейке, задается высоким, чтобы включать этот транзистор ячейки с тем, чтобы выбирать запоминающую ячейку, включающую в себя этот транзистор ячейки.

Выше запоминающего элемента 1, продолжаются разрядные линии 21 и линии 22 истока из проводящих материалов. Смежная разрядная линия 21 и линия 22 истока составляют пару. Набор такой пары разрядной линии 21 и линии 22 истока продолжается вдоль оси Y выше активной области 13 вдоль оси -Z, выстраивается в линию вдоль оси X с интервалом и расположен на идентичном уровне (слое межсоединений). Разрядные линии 21 и линии 22 истока электрические тракты между запоминающими ячейками и схемой считывания и схемой записи. В ходе записи, одна из выбранной пары разрядной линии 21 и линии 22 истока электрически соединяется с источником тока, а другая разрядная линия 22 электрически соединяется с приемником тока. Ток, протекающий из источника тока в приемник тока, протекает через запоминающий элемент 1, и запоминающий элемент 1 принимает состояние сопротивления в соответствии с направлением тока. В ходе считывания, выбранная разрядная линия 21 соединяется со схемой считывания, включающей в себя сенсорный считывающий усилитель.

Для линий 22 истока, предоставляются контактные столбики 24 из проводящего материала. Несколько контактных столбиков 24 предоставляются для одной линии 22 истока и выстраиваются в линию вдоль соответствующей линии 22 истока вдоль оси Y. Каждый контактный столбик 24 находится в контакте с нижней частью соответствующей линии 22 истока в верхней части и с областью 14 истока/стока в нижней части. Каждый контактный столбик 24 расположен между парой электродов 15a затвора между двумя электродами 15b затвора. Каждый контактный столбик 24 соединяет транзистор ячейки, включающий в себя соединенную область 14 истока/стока, с соответствующей линией 22 истока. Когда транзистор ячейки включается, запоминающая ячейка, включающая в себя этот транзистор ячейки, электрически соединяется с линией 22 истока.

Для предоставления запоминающих элементов 1 в компоновке фиг. 2 и 4, запоминающие элементы 1 сдвигаются от пересечений разрядных линий 21 и электродов 15a затвора, в частности, следующим образом. Разрядная линия 21 расположена между двумя смежными столбцами запоминающих элементов, каждый из которых представляет собой набор запоминающих элементов 1, которые находятся по идентичным координатам по оси X и выстроены в линию вдоль оси Y. Другими словами, один из двух смежных столбцов запоминающих элементов продолжается вдоль разрядной линии 21 на первой стороне, а другой продолжается вдоль разрядной линии 21a на второй стороне, противостоящей первой стороне.

Кроме того, вдоль электродов 15a-1 и 15a-2 затвора между двумя электродами 15b затвора, расположены два смежных набора запоминающих элементов, выстроенных в линию вдоль оси X, которые называются строками запоминающих элементов. Другими словами, один из двух смежных запоминающих элементов продолжается вдоль электрода 15a-1 затвора на первой стороне, а другой продолжается вдоль оси X вдоль электрода 15a-2 затвора на второй стороне, противостоящей первой стороне. Кроме того, при просмотре сверху (т.е. на фиг. 5), каждый запоминающий элемент 1 частично перекрывает один электрод 15a затвора и одну разрядную линию 21.

При такой компоновке запоминающих элементов 1, разрядных линий 21 и электродов 1 затвора, взаимосвязи запоминающих элементов 1, разрядных линий 21 и электродов 15 затвора могут описываться следующим образом. Иными словами, при обращении к фиг. 5, каждый из запоминающих элементов 1-1, которые перекрывают электроды 15a-1 затвора, находится около пересечения соответствующей разрядной линии 21 и электрода 15a-1 затвора и сдвигается от пересечения влево вверх. Каждый из запоминающих элементов 1-2, которые перекрывают электроды 15a-2 затвора, находится около пересечения соответствующей разрядной линии 21 и электрода 15a-2 затвора и сдвигается от пересечения вправо вниз. Запоминающие элементы 1-1 и 1-2 могут сдвигаться от соответствующих пересечений вправо вверх и влево вниз, соответственно. Кроме того, разрядная линия 21 расположена между двумя запоминающими элементами 1-1, которые ни находятся в паре вершин, противостоящих через центр правильного шестиугольника, ни примыкают вдоль края правильного шестиугольника и запоминающего элемента 1-2 в центре правильного шестиугольника.

Каждый запоминающий элемент 1 также соединяется с нижней частью сквозного контактного столбика 27 в верхней части. Каждый сквозной контактный столбик 27 соединяется с нижней частью одной разрядной линии 21 в верхней части. Как описано выше, запоминающие элементы 1 значительно сдвигаются от центра разрядных линий 21 и перекрывают разрядные линии 21только в небольшой области. Следовательно, каждый сквозной контактный столбик 27 имеет плоскую форму, продолжающуюся вдоль ширины (т.е. длины вдоль оси X) разрядных линий 21, чтобы соединять соответствующий запоминающий элемент 1 с разрядными линиями 21. В частности, сквозной контактный столбик 27 имеет эллиптическую форму, которая имеет длину в направлении по оси X, превышающую ширину разрядной линии 21.

При такой компоновке одна единичная область 31 может задаваться следующим образом. Единичная область 31 представляет собой компонент, который повторяется, чтобы формировать матрицу запоминающих ячеек. Единичная область 31 включает в себя электроды 15a-1 и 15a-2 затвора, разрядную линию 21, линию 22 истока, два запоминающих элемента 1-1 и 1-2, контактные столбики 26 и 24 и сквозные контактные столбики 27.

Фиг. 8 и 9 иллюстрируют запоминающее устройство по второму примеру первого варианта осуществления и иллюстрируют секции вдоль линий VI-VI и VII-VII по фиг. 5, соответственно. Во втором примере, разрядные линии 21 и линии 22 истока расположены на разных уровнях (слоях межсоединений) по сравнению с первым примером, т.е. линии 22 истока находятся на уровне выше разрядных линий 21.

Фиг. 10 иллюстрирует вид запоминающего устройства по третьему примеру первого варианта осуществления при виде сверху. Компоновка запоминающих элементов 1 по фиг. 10 повернута относительно компоновки по фиг. 2 и 5 на 90 градусов. В примере по фиг. 10, каждая разрядная линия 21 перекрывает один столбец запоминающих элементов. Это отличается от первого примера по фиг. 5, в котором одна разрядная линия 21 перекрывает два столбца запоминающих элементов. В примере по фиг. 10, единичная область 31 включает в себя разрядную линию 21, линию 22 истока, три электрода 15a-11, 15a-12 и 15a-13 затвора, два запоминающих элемента 1-11 и 1-12 и ассоциированные контактные столбики. Каждый запоминающий элемент 1 находится около пересечения разрядной линии 21 и электрода 15a затвора и сдвигается от пересечения вверх вдоль оси Y с тем, чтобы частично перекрывать разрядную линию 21 и электрод 15a затвора. Два смежных запоминающих элемента 1-1 и 1-2 в идентичном столбце запоминающих элементов перекрываются, соответственно, с двумя электродами 15a-11 и 15a-13 затвора, которые выстраиваются в линию с одним электродом 15a-11 затвора между ними. Контактный столбик 24 находится около пересечения электрода 15a-12 затвора и линии 22 истока и сдвигается от пересечения влево вверх, чтобы частично перекрывать электрод 15a-12 затвора и линию 22 истока. Запоминающие элементы 1 перекрывают разрядные линии 21, и следовательно, сквозные контактные столбики 27 между запоминающими элементами 1 и разрядными линиями 21 не должны иметь эллиптические формы, в отличие от сквозных контактных столбиков 27a.

Запоминающие элементы 1 выстраиваются в линию на прямой линии, наклоненной относительно оси X на 60 градусов, как описано выше. Следовательно, есть возможность наклонять электроды 15a затвора на 60 градусов с тем, чтобы совмещать наборы запоминающих элементов 1 (наборы запоминающих элементов), выстроенные в линию вдоль прямой линии, которая наклоняется от оси X на 60 градусов. Фиг. 11 иллюстрирует такой пример и иллюстрирует вид запоминающего устройства по четвертому примеру первого варианта осуществления при виде сверху. Также в примере по фиг. 11, компоновка запоминающих элементов 1 повернута относительно компоновки по фиг. 2 и 5 на 90 градусов, как указано в примере по фиг. 10. Следовательно, электроды 15a затвора являются наклонными относительно оси X на 30 градусов. Два смежных электрода 15a-21 и 15a-22 затвора составляют пару. Набор запоминающих элементов продолжается вдоль электрода 15a-21 затвора на первой стороне, и другой набор запоминающих элементов продолжается вдоль электрода 15a-22 затвора на второй стороне, противостоящей первой стороне. Наборы запоминающих элементов частично перекрывают соответствующие электроды 15a затвора.

Разрядные линии 21 и линии 22 истока могут находиться на идентичном уровне или разных уровнях.

Фиг. 12 иллюстрирует вид запоминающего устройства по пятому примеру первого варианта осуществления при виде сверху. Фиг. 13 и 14 иллюстрируют секции вдоль линий XIII-XIII и XIV-XIV по фиг. 12, соответственно. Пятый пример является аналогичным четвертому примеру, и в пятом примере активные области 13, к примеру, активные области по фиг. 12, разделяются вдоль оси Y, что приводит к предоставлению нескольких активных областей 13, выстроенных в линию вдоль электродов 15a-31 затвора. В отличие от четвертого примера, набор контактных столбиков 24 линии истока (набор контактных столбиков), выстроенных в линию вдоль прямой линии, наклоненной относительно оси X на 60 градусов, предоставляется в каждой области между наборами запоминающих элементов (наборами запоминающих элементов 1, выстроенных в линию вдоль прямой линии, наклоненной относительно оси X на 60 градусов). Каждая активная область 13 имеет форму параллелограмма. Одна пара параллельных краев параллелограмма продолжается вдоль оси Y, а другая пара краев продолжается вдоль электродов 15a-31 затвора. Каждый электрод 15a-31 затвора проходит около центров активных областей 13, выстроенных в линию вдоль этого электрода 15a-31 затвора. Каждый электрод 15a-31 затвора расположен между набором контактных столбиков и набором запоминающих элементов, частично перекрывает запоминающие элементы 1 на первой стороне этого электрода 15a-31 затвора и частично перекрывает контактные столбики 24 на второй стороне.

Фиг. 15 и 16 иллюстрируют запоминающее устройство по шестому примеру первого варианта осуществления и иллюстрируют секции вдоль линий XIII-XIII и XIV-XIV по фиг. 12, соответственно. В шестом примере, разрядные линии 21 и линии 22 истока расположены на разных уровнях (слоях межсоединений) по сравнению с пятым примером, т.е. линии 22 истока находятся на уровне выше разрядных линий 21.

Как описано выше, согласно первому варианту осуществления, запоминающие элементы 1 выполнены с возможностью располагаться в вершинах и в центрах правильных шестиугольников, и как результат, все смежные запоминающие элементы 1 имеют равные интервалы. При такой компоновке, область для размещения конкретного числа запоминающих элементов 1 снижается таким образом, что она составляет 0,87 от области для размещения идентичного числа запоминающих элементов 1 в примере по фиг. 1. Это предоставляет возможность реализации меньшей матрицы запоминающих ячеек. Кроме того, компоновка запоминающих элементов 1 по первому варианту осуществления может размещать, в идентичной области для компоновки по фиг. 1, идентичное число запоминающих элементов 1 с большим интервалом. Другими словами, столько же запоминающих элементов, сколько запоминающих элементов на фиг. 1, может размещаться в идентичной области с уменьшенным влиянием в запоминающих элементах.

Второй вариант осуществления

Второй вариант осуществления основан на первом варианте осуществления и, в частности, на четвертом, пятом или шестом примере первого варианта осуществления.

Согласно четвертому-шестому примерам первого варианта осуществления, электроды 15 затвора являются наклонными относительно оси X на 30 градусов. Следовательно, форма матрицы ячеек, т.е. линия, которая соединяет границу матрицы ячеек, представляет собой параллелограмм. Это можно понять посредством продления фиг. 11 и 12, которые иллюстрируют часть матрицы ячеек, до всей матрицы ячеек. Второй вариант осуществления основан на использовании такой формы матрицы ячеек.

Как описано выше, запоминающие ячейки избирательно соединены со схемой считывания и схемой записи. С этой целью, конкретная разрядная линия 21 и линия 22 истока электрически соединяются со схемой считывания или схемой записи, чтобы формировать электрический путь между выбранной ячейкой запоминающего устройства и схемой считывания или записи. Для такого избирательного соединения разрядных линий 21 и линий 22 истока, контроллер разрядных линий и линий истока предоставляется в запоминающем устройстве 1. Контроллер разрядных линий и линий истока включает в себя схему переключения и использует схему переключения, чтобы соединять одну разрядную линию 21 и одну линию 22 истока, которые указываются посредством сигнала адреса снаружи, с глобальной разрядной линией и глобальной линией истока, соответственно. Глобальная разрядная линия означает часть пути между разрядными линиями 21 и схемами считывания и записи, и глобальная линия истока означает часть пути между линиями 22 истока и схемой считывания и схемами записи.

Как проиллюстрировано на фиг. 17, схема 101 переключения (схема переключения столбцов) в контроллере разрядных линий и линий истока может предоставляться в периферии матрицы 102 ячеек. Разрядные линии 103 и линии 104 истока в матрице 102 ячеек извлекаются из матрицы 102 ячеек в схему 101 переключения столбцов. Разрядные линии 103 и линии 104 истока соединяются с активными областями 105, в частности, областями истока/стока, через контактные столбики 106 в области схемы 101 переключения столбцов. Специальные требования не налагаются на позиции контактных столбиков 106 при условии, что разрядные линии 103 и линии 104 истока соединяются с активными областями 105, чтобы обеспечивать нормальный режим работы запоминающего устройства. Следовательно, область 107 разрядной линии 103 и линии 104 истока, которые включает в себя секции из границы матрицы 102 ячеек в позиции контактных столбиков 106, не участвует нигде, кроме нормального режима работы. Следовательно, если эта секция может удаляться, площадь схемы 101 переключения столбцов может уменьшаться.

На основе этого, во втором варианте осуществления, предпринята попытка для того, чтобы уменьшать площадь схемы переключения столбцов, состоящей посредством использования конкретной компоновки контактных столбиков в схеме переключения столбцов и комбинирования первого варианта осуществления.

Фиг. 18 иллюстрирует вид запоминающего устройства согласно второму варианту осуществления при виде сверху и, в частности, иллюстрирует окрестность границы между матрицей 31 ячеек и схемой 32 переключения столбцов контроллера разрядных линий и линий истока. Матрица 31 ячеек имеет форму параллелограмма с парой противостоящих краев вдоль оси Y, как описано выше. Матрица 31 ячеек такой формы может быть реализована, например, с использованием четвертого, пятого или шестого примера первого варианта осуществления. В этом случае, оставшаяся пара наклонных краев продолжается вдоль электрода 15 затвора, т.е. является наклонной относительно оси X на 30 градусов и не является параллельной оси X или оси Y.

Контроллер разрядных линий и линий истока управляет разрядными линиями 21 и линиями 22 истока и включает в себя схему 32 переключения столбцов. Схема 32 переключения столбцов включает в себя схемы переключения и использует схемы переключения, чтобы соединять одну разрядную линию 21 и одну линию 22 истока, которые указываются посредством сигнала адреса снаружи, с глобальной разрядной линией и глобальным истоком, соответственно. Глобальная разрядная линия и глобальная линия истока соединяются со схемой считывания и схемой записи. Каждая схема переключения схемы 32 переключения столбцов включает в себя, например, MOSFET-транзистор. Схема 32 переключения столбцов также включает в себя электроды 41 затвора, продолжающиеся вдоль оси X. Электроды 41 затвора предоставляются, например, выше подложки 11. Электроды 41 затвора могут заглубляться в подложке 11.

Схема 32 переключения столбцов дополнительно включает в себя активную область 13. Активная область 13 включает в себя области истока/стока (не показаны) на поверхности. Один электрод 41 затвора и пара областей истока/стока на обеих сторонах составляют транзистор в качестве схемы переключения.

Разрядные линии 21 и линии 22 истока исходят из матрицы 31 ячеек вдоль оси Y с тем, чтобы достигать схемы 32 переключения столбцов. Разрядные линии 21 и линии 22 истока соединяются с верхними частями контактных столбиков 46 в нижних частях. Нижние части контактных столбиков 44 находятся в контакте с активной областью 13, в частности, с областями истока/стока в активной области 13.

Как описано выше, секции разрядных линий 21 и линий 22 истока от границы матрицы 31 ячеек до позиций контактных столбиков 44, которые называются секциями отвода, не предоставляют большое преимущество, за исключением электрических соединений между разрядными линиями 21, линиями 22 истока и контактными столбиками 44. Следовательно, предпринимается попытка регулировать эти секции отвода разрядных линий 21 и линий 22 истока. В частности, контактные столбики 44 размещаются вдоль наклонного края матрицы 31 ячеек, более конкретно на прямой линии, наклоненной относительно оси X на 30 градусов. Как результат, набор секций отвода составляет удобную форму вдоль наклонного края матрицы 31 ячеек. С использованием этого, каждая секция отвода частично удаляется, за исключением части непосредственно ниже контактного столбика 44 вдоль оси Y. В частности, как результат, секции отвода имеют необходимые минимальные длины. Уменьшение секций отвода уменьшает сопротивления разрядных линий 21 и линий 22 истока.

В соответствии с уменьшением секций отвода, активная область 13 также частично удаляется слева внизу таким образом, чтобы иметь форму с обрезанным левым нижним углом. В частности, активная область 13 частично удаляется слева внизу в соответствии со структурой матрицы 31 ячеек за исключением области, достаточной для соединения с контактными столбиками 44. Это приводит к активной области 13 с наклонным краем, наклоненным от оси X на 30 градусов. Фиг. 18 иллюстрирует то, что край, соединяющий верхние и правые края активной области 13, также наклонен на 30 градусов от оси X; тем не менее, это необязательно.

При такой форме секций отвода и активных областей 13, схема 32 переключения столбцов имеет форму с обрезанным нижним левым углом и имеет угол, идентичный углу наклонной матрицы границы соты 31. С использованием этого, матрица 31 ячеек размещается вдоль этого наклонного края. Это точно соответствует удалению необязательной области 107 примера по фиг. 17.

При вышеописанной компоновке, все секции отвода имеют идентичную длину вдоль оси Y. Кроме того, матрица 31 ячеек расположена на протяжении электродов 15 затвора. Это отличается от примера по фиг. 17. В примере по фиг. 17, схема 101 переключения столбцов является прямоугольной, и на основе этого, матрица ячеек не находится на протяжении электродов 108 затвора.

Схема 32 переключения столбцов на противоположной стороне матрицы 31 ячеек относительно стороны, проиллюстрированной в фиг. 18, также может иметь структуру, идентичную структуре по фиг. 18. В частности, форма схемы 32 переключения столбцов ниже матрицы 31 ячеек модифицируется таким образом, чтобы совмещать нижний край матрицы 31 ячеек, и схема 32 переключения столбцов имеет форму с обрезанным верхним правым углом. Это может легко визуально и интуитивно пониматься из вида на фиг. 19. Фиг. 19(a) иллюстрирует схему размещения части запоминающего устройства по второму варианту осуществления.

Как проиллюстрировано на фиг. 19(a), матрица 31 ячеек имеет пару краев вдоль оси Y и пару наклонных краев. Кроме того, схема 32 переключения столбцов выше матрицы 31 ячеек имеет форму с обрезанным нижним левым углом для того, чтобы совмещать верхний наклонный край матрицы 31 ячеек. Схема 32 переключения столбцов ниже матрицы 31 ячеек имеет обрезанный верхний правый угол для того, чтобы совмещать нижний наклонный край матрицы 31 ячеек. При такой схеме размещения, полная площадь запоминающего устройства по второму варианту осуществления (т.е. сумма площадей всех компонентов, проиллюстрированных на фиг. 19(a)) намного меньше площади схемы размещения фиг. 19(b), которая имеет прямоугольные схемы 101 переключения столбцов и матрицу 102 ячеек. Можно понимать, что схема размещения по фиг. 19(a) соответствует схеме размещения по фиг. 19(b), причем матрица 31 ячеек вписывается в ту позицию, в которой ранее была расположена схема 101 переключения столбцов. Следует отметить, что компоненты 46 и 109 по фиг. 19 представляют собой контроллеры числовых линий, которые управляют электродами 15 затвора.

Как описано выше, согласно второму варианту осуществления, матрица 31 ячеек имеет наклонный край, который не является параллельным оси X или оси Y, и одна или более схем 32 переключения столбцов имеют форму с обрезанным углом для того, чтобы совмещать наклонный край. Как результат, секции схем 32 переключения столбцов, которые не участвуют нигде, кроме нормального режима работы, могут удаляться, чтобы уменьшать площадь схемы 32 переключения столбцов при поддержании нормального режима работы.

Третий вариант осуществления

Третий вариант осуществления основан на компоновке запоминающих элементов 1, расположенных в вершинах и в центрах правильных шестиугольников, аналогично первому варианту осуществления.

Фиг. 20-22 иллюстрируют виды части запоминающего устройства по первому примеру третьего варианта осуществления при виде сверху. Компоновка запоминающих элементов 1 на фиг. 20-22 повернута относительно компоновки по фиг. 2 и 5 на 90 градусов так, как показано на фиг. 10 и т.д. Фиг. 20 иллюстрирует компоненты в слоях, включающих в себя самый нижний слой (уровень) вдоль оси Z, и иллюстрирует поверхность подложки 11, контактных столбиков 24 и компонентов между ними. Фиг. 21 в основном иллюстрирует компоненты в слоях выше фиг. 20 и иллюстрирует контактные столбики 24, запоминающие элементы 1 и компоненты между ними. Фиг. 22 в основном иллюстрирует компоненты в слоях выше фиг. 21 и иллюстрирует запоминающие элементы 1, разрядные линии 21 и компоненты между ними. Фиг. 23 и 24 иллюстрируют виды вдоль линии XXIII-XXIII и линии XXIV-XXIV по фиг. 20-22, соответственно.

Запоминающие элементы 1 размещаются в направлении, повернутом относительно компоновки запоминающих элементов 1 по фиг. 2 и 4 на 90 градусов выше подложки 11 вдоль оси Z. Следовательно, запоминающие элементы 1 выстраиваются в линию вдоль оси Y и размещаются в столбцах.

Электроды 15 затвора продолжаются вдоль оси Y, выстраиваются в линию вдоль оси X с интервалом и продолжаются между столбцами запоминающих элементов. Электроды 15 затвора предоставляются в изоляторах 12 развязки элементов на поверхности подложки 11 и закрываются в верхних частях с помощью колпачковых изоляторов 17. В частности, электроды 15 затвора и колпачковые изоляторы 17 предоставляются в изоляторах 12 развязки элементов с изоляторами 17 затвора между ними. Электроды 15 затвора окружены посредством соответствующих изоляторов 18 затвора и соответствующих колпачковых изоляторов 17. Колпачковые изоляторы 17 закрываются по бокам с помощью соответствующих изоляторов 18 затвора и продолжаются между верхними частями соответствующих электродов 15 затвора и поверхностью подложки 11. Фиг. 20-23 не иллюстрируют колпачковые изоляторы 17 в целях прояснения этих чертежей.

Разрядные линии 21 и линии 22 истока продолжаются вдоль оси X. Разрядные линии 21 расположены выше линий 22 истока вдоль оси Z, разрядные линий 21 и линии 22 истока перекрываются в плоскости, состоящей из оси X и оси Y, т.е. в плоскости XY, и перекрывающиеся одна разрядная линия 21 и одна линия 22 истока составляют пару. В плоскости XY, пары разрядных линий и линий истока выстраиваются в линию вдоль оси Y с интервалом. Следовательно, пары разрядных линий и линий истока размещаются в строках. Разрядные линии 21 и линии 22 истока, в плоскости XY, находятся в окрестности или частично перекрываются с запоминающими элементами 1, выстраивающимися в линию вдоль оси X.

Активные области 13 (13_1 и 13_2) являются независимыми друг от друга, разделяются и окружаются посредством изоляторов 12 развязки элементов и имеют прямоугольные формы в плоскости XY. Активные области 13 продолжаются, в плоскости XY, в направлении, которое соединяет области около соответствующих двух конкретных запоминающих элементов 1. Подробности приводятся далее. Из числа запоминающих элементов 1 в вершинах правильного шестиугольника, два запоминающих элемента 1 на одной из двух диагональных линий, которые проходят через центр шестиугольника и не являются параллельными с осью Y (например, запоминающие элементы 1_11 и 1_12), составляют пару. С тем чтобы идти поверх областей под и около этой пары запоминающих элементов 1, одна активная область 13 продолжается вдоль плоскости XY. Следовательно, активные области 13 не являются параллельными с осью X или осью Y. Активная область 13, продолжающаяся поверх пары запоминающих элементов 1, в плоскости XY, находится под и около или частично перекрывается с запоминающим элементом 1 между этой парой запоминающих элементов 1 (т.е. запоминающим элементом 1 в центре правильного шестиугольника, который имеет пару запоминающих элементов в своих вершинах).

Более одной активных областей 13 выстраиваются в линию вдоль оси X с формированием строк. В каждой строке активных областей (строке активных областей) активные области 13 имеют регулярный интервал и, например, обращены друг к другу на концах в направлении вдоль оси Y. В частности, две активных области 13, в плоскости XY, находятся под и около или частично перекрываются с соответствующими двумя запоминающими элементами 1, выстраивающимися в линию вдоль оси Y. Набор активных областей 13 вдоль оси X расположен ниже линии 22 истока вдоль оси Z, имеет соответствие как этой линией 22 истока, так и с разрядной линией 21 выше вдоль оси Z и электрически соединяется с этой соответствующей парой линии истока и разрядной линии.

Активные области 13 в конкретной строке активных областей отличаются от активных областей 13 в смежной строке активных областей по позиции или координате (центров) на оси X. Как результат, позиции в оси X соответствующих активных областей 13 в строках с четным номером и позиции в оси X соответствующих активных областей 13 в строках с нечетным номером отличаются. Например, одна из двух активных областей 13, которые принадлежат двум соответствующим смежным строкам и обращены друг к другу, продолжается, из первого-четвертого столбцов, которые выстраиваются в линию, поверх первого-третьего столбцы (или наборов запоминающего элемента 1, выстраивающихся в линию вдоль оси Y), а другая продолжается поверх второго-четвертого столбцов.

Каждая активная область 13 продолжается поверх, по меньшей мере, двух электродов 15 затвора, которые примыкают друг к другу, и через нее проходят два электрода затвора таким образом, что она разделяется на три секции. В трех секциях каждой активной области 13, разделенной посредством двух электродов 15 затвора, формируются области 14 истока/стока. Каждый электрод 15 затвора, в секции между парой областей 14 истока/стока на обеих сторонах, составляет транзистор ячейки с этими областями 14 истока/стока. Середина секций каждой активной области 13 соединяется с нижней частью контактного столбика 24. Контактные столбики 24 соединяются в верхних частях с линиями 22 истока. Каждый контактный столбик 24 расположен между двумя смежными электродами 15 затвора в плоскости XY.

Каждая активная область 13 должна электрически соединяться на одном конце (в области 14 истока/стока) с соответствующей разрядной линией 21 через запоминающий элемент 1 и на другом конце (в области 14 истока/стока) с этой разрядной линией 21 через другой запоминающий элемент 1. Тем не менее, некоторые активные области 13 не перекрываются как с соответствующей разрядной линией 21, так и с соответствующим запоминающим элементом 1 на каждом из своих концов в плоскости XY, как видно из чертежей. Чтобы разрешать это, контактные столбики 26 и сквозные контактные столбики 27 имеют формы и компоновку, которые предоставляют возможность электрических соединений активных областей 13, разрядных линий 21 и запоминающих элементов 1. Подробности приводятся далее.

В наборе каждых вторых строк, например, в строках с четным номером, каждая активная область 13_1 перекрывается на одном из двух концов (например, в правой стороне) с контактным столбиком 26_11 в плоскости XY. Например, контактный столбик 26_11 перекрывается в плоскости XY с верхней частью первого конца активной области 13_1. Контактный столбик 26_11 дополнительно перекрывается в плоскости XY с верхней частью запоминающего элемента 1_11. Между запоминающим элементом 1_11 и соответствующей разрядной линией 21_11, предоставляется сквозной контактный столбик 27_11. Сквозной контактный столбик 27_11 соединяется с запоминающим элементом 1_11 и разрядной линией 21_11, перекрывается в плоскости XY с запоминающим элементом 1_11 и разрядной линией 21_11 и расположен между двумя электродами 15 затвора. При таких формах и компоновке запоминающего элемента 1_11, контактного столбика 26_11 и сквозного контактного столбика 27_11, первый конец активной области 13_1 электрически соединяется с разрядной линией 21_11 через запоминающий элемент 1_11.

Второй конец (например, в левой стороне) активной области 13_1 перекрывается в плоскости XY с контактным столбиком 26_12. Например, контактный столбик 26_12 перекрывается в плоскости XY с нижней частью второго конца активной области 13_1. Контактный столбик 26_12 дополнительно перекрывается в плоскости XY с верхней частью запоминающего элемента 1_12. Запоминающий элемент 1_12 частично перекрывается в плоскости XY с несоответствующей разрядной линией 21_12. Между запоминающим элементом 1_12 и соответствующей разрядной линией 21_11, предоставляется сквозной контактный столбик 27_12. Сквозной контактный столбик 27_12 соединяется с запоминающим элементом 1_12 и разрядной линией 21_11, перекрывается в плоскости XY с запоминающим элементом 1_12 и разрядной линией 21_11 и расположен между двумя электродами 15 затвора. При таких формах и компоновке запоминающего элемента 1_12, контактного столбика 26_12 и сквозного контактного столбика 27_12, второй конец активной области 13_1 электрически соединяется с разрядной линией 21_11 через запоминающий элемент 1_12.

Наборы из такой активной области 13_1, соответствующих запоминающих элементов 1_11 и 1_12 и контактных столбиков 24, 26_11 и 26_12 и сквозных контактных столбиков 27_11 и 27_12 многократно предоставляются вдоль разрядной линии 21_11.

В наборе каждых вторых строк, включающих в себя строку, отличающуюся от строки, которой принадлежит активная область 13_1, например, в строках с нечетным номером, каждая активная область 13_2 перекрывается на одном из двух концов (например, в правой стороне) с контактным столбиком 26_13 в плоскости XY. Например, контактный столбик 26_13 перекрывается в плоскости XY с верхней частью первого конца активной области 13_2. Контактный столбик 26_13 дополнительно перекрывается в плоскости XY с запоминающим элементом 1_13. Между запоминающим элементом 1_13 и разрядной линией 21_12, предоставляется сквозной контактный столбик 27_13. Сквозной контактный столбик 27_13 соединяется с запоминающим элементом 1_13 и разрядной линией 21_12, перекрывается в плоскости XY с запоминающим элементом 1_13 и разрядной линией 21_12 и расположен между двумя электродами 15 затвора. При таких формах и компоновке запоминающего элемента 1_13, контактного столбика 26_13 и сквозного контактного столбика 27_13, первый конец активной области 13_2 электрически соединяется с разрядной линией 21_12 через запоминающий элемент 1_13.

Второй конец (например, в левой стороне) активной области 13_2 перекрывается в плоскости XY с контактным столбиком 26_14. Например, контактный столбик 26_14 перекрывается в плоскости XY с нижней частью второго конца активной области 13_2. Контактный столбик 26_14 дополнительно перекрывается в плоскости XY с нижней частью запоминающих элементов 1_14. Между запоминающим элементом 1_14 и соответствующей разрядной линией 21_12, предоставляется сквозной контактный столбик 27_14. Сквозной контактный столбик 27_14 соединяется с запоминающим элементом 1_14 и разрядной линией 21_12, перекрывается в плоскости XY с запоминающим элементом 1_14 и разрядной линией 21_12 и расположен между двумя электродами 15 затвора. При таких формах и компоновке запоминающего элемента 1_14, контактного столбика 26_14 и сквозного контактного столбика 27_14, второй конец активной области 13_2 электрически соединяется с разрядной линией 21_12 через запоминающий элемент 1_12.

Наборы таких активных областей 13_2, соответствующих запоминающих элементы 1_13 и 1_14, контактных столбиков 24, 26_13 и 26_14 и сквозных контактных столбиков 27_13 и 27_14 многократно предоставляются вдоль разрядной линии 21_12.

Сквозные контактные столбики 27 также способствуют соединениям между запоминающим элементом 1, отличающимся от вышеописанного запоминающего элемента, и разрядной линией 21. В частности, сквозной контактный столбик 27_11 соединяет запоминающий элемент 1_15, смежный с запоминающим элементом 1_11 вдоль оси Y, и разрядную линию 21_11 и перекрывается в плоскости XY с запоминающим элементом 1_15 и разрядной линией 21_11. Запоминающий элемент 1_15 соответствует запоминающему элементу 1 слева, т.е. запоминающему элементу 1_12, другой активной области 13 строки, идентичной строке активной области 13_1, с которой электрически соединяется запоминающий элемент 1_11.

Сквозной контактный столбик 27_12 соединяет запоминающий элемент 1_16, смежный с запоминающим элементом 1_12 вдоль оси Y, и разрядную линию 21_11 и перекрывается в плоскости XY с запоминающим элементом 1_16 и разрядной линией 21_11. Запоминающий элемент 1_16 соответствует запоминающему элементу 1 справа, т.е. запоминающему элементу 1_11, другой активной области 13 строки, идентичной строке активной области 13_1, с которой электрически соединяется запоминающий элемент 1_12.

Сквозной контактный столбик 27_13 соединяет запоминающий элемент 1_17, смежный с запоминающим элементом 1_13 вдоль оси Y, и разрядную линию 21_12 и перекрывается в плоскости XY с запоминающим элементом 1_17 и разрядной линией 21_12. Запоминающий элемент 1_17 соответствует запоминающему элементу 1 слева, т.е. запоминающему элементу 1_14, другой активной области 13 строки, идентичной строке активной области 13_2, с которой электрически соединяется запоминающий элемент 1_13.

Сквозной контактный столбик 27_14 соединяет запоминающий элемент 1_18, смежный с запоминающим элементом 1_14 вдоль оси Y, и разрядную линию 21_12 и перекрывается в плоскости XY с запоминающим элементом 1_18 и разрядной линией 21_12. Запоминающий элемент 1_18 соответствует запоминающему элементу 1 справа, т.е. запоминающему элементу 1_13, другой активной области 13 строки, идентичной строке активной области 13_2, с которой электрически соединяется запоминающий элемент 1_14.

Угол в плоскости XY активных областей 13 должен иметь только такое значение, чтобы обеспечивать возможность обоим концам активных областей 13 электрически соединяться с запоминающими элементами 1 через контактные столбики 24 и 26 и сквозные контактные столбики 27, и не ограничен примерами фиг. 20-24. Угол θ между активными областями 13 и осью X зависит от размеров и шагов разрядных линий 21 и электродов 15 затвора.

Согласно вышеописанной схеме размещения, размер одной ячейки является следующим, по сравнению с фиг. 1. В примере по фиг. 1, отношение длины вдоль оси Y к длине вдоль оси X размера одной ячейки составляет 1:1. Напротив, в третьем варианте осуществления, отношение длины вдоль оси Y к длине вдоль оси X размера одной ячейки составляет 1:0,866.

Как описано выше, согласно третьему варианту осуществления, запоминающие элементы 1 выполнены с возможностью располагаться в вершинах и в центрах правильных шестиугольников, и как результат, все смежные запоминающие элементы 1 имеют идентичный интервал, аналогично первому варианту осуществления. По этой причине, может получаться преимущество, идентичное преимуществу первого варианта осуществления. Помимо этого, активные области 13, разрядные линии 21, линии 22 истока, контактные столбики 24, 26 и сквозные контактные столбики 27 третьего варианта осуществления также предоставляют возможность соединений активных областей 13, запоминающих элементов 1, разрядных линий 21 и линий 22 истока.

Дополнительные слои могут быть включены между активными областями 13 и разрядными линиями 21. Далее описываются такие примеры. Фиг. 25 и 26 иллюстрируют виды части запоминающего устройства по второму примеру третьего варианта осуществления при виде сверху. Фиг. 25 иллюстрирует контактные столбики 26, линии 22 истока и компоненты между ними. Фиг. 26 иллюстрирует компоненты в слоях выше фиг. 25 и иллюстрирует запоминающие элементы 1, разрядные линии 21 и компоненты между ними. Фиг. 27 и 28 иллюстрируют виды вдоль линии XXVII-XXVII и линии XXVIII-XXVIII по фиг. 25 и 26, соответственно.

Во втором примере, проводящие слои 51 предоставляются между контактными столбиками 26 и запоминающими элементами 1 в дополнение к компонентам, компоновке и соединениям в первом примере. Каждый проводящий слой 51 находится в контакте на обеих сторонах с контактным столбиком 26 и запоминающим элементом 1. Кроме того, каждый проводящий слой 51 расположен в плоскости XY между двумя электродами 15 затвора и, например, перекрывается с двумя электродами 15 затвора. Кроме того, каждый проводящий слой 51 продолжается вдоль оси Y поверх обоих концов набора двух запоминающих элементов 1 в соответствующих двух столбцах, которые выстраиваются в линию вдоль оси X. Например, каждый проводящий слой 51 имеет такой размер, чтобы охватывать один контактный столбик 26 и один запоминающий элемент 1, электрически соединенный с этим контактным столбиком в плоскости XY. Такие проводящие слои 51 могут стабильно электрически соединять контактные столбики 26 и запоминающие элементы 1. В частности, можно не допускать того, что позиции контактных столбиков 26 и запоминающих элементов 1 сдвигаются от намеченных позиций, что приводит к большому варьированию контактных областей из числа пар контактного столбика 26 и запоминающего элемента 1, которые должны соединяться друг с другом. Такое варьирование свойств вследствие варьирования контактной области или дефекты вследствие отсутствия контакта могут подавляться посредством проводящих слоев 51.

Фиг. 29 и 30 иллюстрируют виды части запоминающего устройства по третьему примеру третьего варианта осуществления при виде сверху. Фиг. 29 иллюстрирует контактные столбики 26, проводящие слои 52 и компоненты между ними. Фиг. 30 в основном иллюстрирует компоненты в слоях выше фиг. 29 и иллюстрирует запоминающие элементы 1, разрядные линии 21 и компоненты между ними. Фиг. 31 и 32 иллюстрируют виды вдоль линии XXXI-XXXI и линии XXXII-XXXII по фиг. 29 и 30, соответственно.

В третьем примере, проводящие слои 52 предоставляются между запоминающими элементами 1 и сквозными контактными столбиками 27 в дополнение к компонентам, компоновке и соединениям во втором примере. Каждый проводящий слой 52 находится в контакте на обеих сторонах с запоминающим элементом 1 и сквозным контактным столбиком 27. Каждый проводящий слой 52 расположен в плоскости XY между двумя электродами 15 затвора и, например, перекрывается с двумя электродами 15 затвора. Кроме того, каждый проводящий слой 52 продолжается вдоль оси Y поверх обоих запоминающих элементов 1, которые выстраиваются в линию вдоль оси Y и соединяются с идентичной разрядной линией 21. Например, каждый проводящий слой 52 частично перекрывается с одним из соответствующих двух запоминающих элементов 1 и частично перекрывается с другим. Предоставление проводящих слоев 52 исключает необходимость прохождения сквозных контактных столбиков 27 в плоскости XY поверх соответствующих пар запоминающих элементов 1, выстраивающихся в линию вдоль оси Y. Например, каждый сквозной контактный столбик 27 продолжается из центра вдоль оси Y соответствующей разрядной линии 21 к обеим сторонам вдоль оси Y практически на идентичное расстояние и имеет длину по оси Y, меньшую длины по оси Y сквозного контактного столбика 27 в примере фиг. 20-24. Предоставление проводящих слоев 52 позволяет уменьшать длину по оси Y сквозных контактных столбиков 27, что, в свою очередь, позволяет снижать вероятность того, что сквозной контактный столбик 27 непреднамеренно контактирует с разрядной линией 21, которая не должна соединяться с этим сквозным контактным столбиком 27.

Фиг. 33 иллюстрирует вид части запоминающего устройства по четвертому примеру третьего варианта осуществления при виде сверху и иллюстрирует контактные столбики 26, разрядные линии 21 и компоненты между ними. Фиг. 34 и 35 иллюстрируют виды вдоль линии XXXIV-XXXIV и линии XXXV-XXXV по фиг. 33, соответственно. Запоминающее устройство по четвертому примеру соответствует комбинации второго и третьего примеров и, в частности, включает в себя оба проводящих слоя 51 и 52. Согласно четвертому примеру, могут получаться преимущества как второго, так и третьего примеров.

Фиг. 36 иллюстрирует вид части запоминающего устройства по пятому примеру третьего варианта осуществления при виде сверху и иллюстрирует контактные столбики 26, разрядные линии 21 и компоненты между ними. Фиг. 37 и 38 иллюстрируют виды вдоль линии XXXVII-XXXVII и линии XXXVIII-XXXVIII по фиг. 36, соответственно. Запоминающее устройство по пятому примеру включает в себя дополнительный слой в дополнение к компонентам, компоновке и соединениям в четвертом варианте осуществления. В частности, запоминающее устройство по пятому примеру включает в себя проводящие слои 53 между запоминающими элементами 1 и проводящими слоями 52. Проводящие слои 53 имеют размеры в плоскости XY, практически идентичные размерам, например, верхних частей запоминающих элементов 1. Согласно пятому примеру, могут получаться преимущества как второго, так и третьего примеров. Кроме того, согласно пятому примеру, верхние части запоминающих элементов 1 могут быть защищены от доступности в конкретном процессе при изготовлении запоминающего устройства. В частности, например, отверстия для проводящих слоев 52 травятся в изоляторе, чтобы формировать проводящие слои 52. Не допускается непреднамеренное достижение запоминающих элементов 1 посредством этого травления. Проводящие слои 53 могут использоваться в комбинации либо проводящих слоев 51, либо проводящих слоев 52 вместо обоих проводящих слоев 51 и 52, что представляет собой случай пятого примера. В частности, любая комбинация проводящих слоев 51, 52 и 53 является возможной.

Четвертый вариант осуществления

Четвертый вариант осуществления основан на компоновке запоминающих элементов 1, расположенных в вершинах и в центрах правильных шестиугольников, аналогично первому варианту осуществления. Четвертый вариант осуществления также связан со структурой, в которой направление компоновки запоминающих элементов 1 третьего варианта осуществления поворачивается в плоскости XY на 90 градусов.

Фиг. 39-41 иллюстрируют виды части запоминающего устройства по первому примеру четвертого варианта осуществления при виде сверху. Компоновка запоминающих элементов 1 по фиг. 39-41 повернута относительно компоновки по фиг. 2 и 5 так, как показано на фиг. 10 и т.д. Фиг. 39 иллюстрирует компоненты в слоях, включающих в себя самый нижний слой (уровень) вдоль оси Z, и иллюстрирует поверхность подложки 11, контактных столбиков 24 и компонентов между ними. Фиг. 40 в основном иллюстрирует компоненты в слоях выше фиг. 39 и иллюстрирует поверхность подложки 11, запоминающих элементов 1 и компонентов между ними. Фиг. 41 в основном иллюстрирует компоненты в слоях выше фиг. 40 и иллюстрирует линии 22 истока, разрядные линии и компоненты между ними. Фиг. 42 и 43 иллюстрируют виды вдоль линии XLII-XLII и линии XLIII-XLIII по фиг. 39-41, соответственно.

Запоминающие элементы 1 размещаются в направлении, повернутом относительно компоновки запоминающих элементов 1 по фиг. 2 и 4 на 90 градусов выше подложки 11 вдоль оси Z. Следовательно, запоминающие элементы 1 выстраиваются в линию вдоль оси Y и размещаются в столбцах.

Электроды 15 затвора продолжаются вдоль оси X, выстраиваются в линию вдоль оси Y с интервалом и продолжаются между строками запоминающих элементов. Электроды 15 затвора предоставляются в изоляторах 12 развязки элементов на поверхности подложки 11 с изоляторами 18 затвора между ними и закрываются в верхних частях с помощью колпачковых изоляторов 17, аналогично третьему варианту осуществления.

Линии 22 (22_1 и 22_2) истока расположены выше подложки 11 вдоль оси Z, продолжаются вдоль оси Y, выстраиваются в линию вдоль оси X с интервалом и продолжаются между столбцами запоминающих элементов. Линии 22 истока включают в себя линии 22_1 и 22_2 истока, которые размещаются попеременно вдоль оси X.

Активные области 13 являются независимыми друг от друга, разделяются и окружаются посредством изоляторов 12 развязки элементов и имеют прямоугольные формы в плоскости XY. Активные области 13 продолжаются, в плоскости XY, в направлении, которое соединяет области около двух конкретных запоминающих элементов 1. Подробности приводятся далее. Из числа запоминающих элементов 1 в вершинах правильного шестиугольника, два запоминающих элемента 1 на диагональной линии шестиугольника, которые не продолжаются вдоль оси Y или не проходят через центр, к примеру, запоминающие элементы 1_21 и 1_23, составляют пару. В направлении, продолжающемся над областями под и около такой пары запоминающих элементов 1 вдоль оси Z, продолжаются активные области 13. Следовательно, активные области 13 не являются параллельными с осью X или осью Y.

Активные области 13 (13_1 и 13_2) выстраиваются в линию вдоль оси Y с тем, чтобы составлять столбцы. В каждом из столбцов активных областей (столбцов активных областей), активные области 13 имеют регулярный интервал и обращены друг к другу, например, на концах в направлении вдоль оси X. Активные области 13 в конкретном столбце активных областей отличаются от активных областей 13 в смежном столбце активных областей по позиции или координате (центров) на оси Y.

Активные области 13 включают в себя активные области 13_1 и 13_2. Активные области 13_1 выстраиваются в линию вдоль линий 22_1 истока с интервалом. Каждая активная область 13_1 продолжается в плоскости XY поверх областей под и около двух конкретных запоминающих элементов 1 вдоль оси Z. Подробности приводятся далее. Следует обратить внимание на первый правильный шестиугольник запоминающих элементов и второй правильный шестиугольник запоминающих элементов, который совместно использует край в качестве своего верхнего правого края с нижним левым краем первого правильного шестиугольника. Запоминающий элемент 1 в верхней части первого правильного шестиугольника вдоль оси Y (запоминающий элемент 1_21) и запоминающий элемент 1 в центре второго правильного шестиугольника (запоминающий элемент 1_22) составляют первую пару. Каждая активная область 13_1 продолжается поверх соответствующих областей под и около первой пары запоминающих элементов 1 (первой запоминающей пары) вдоль оси Z.

Каждая активная область 13_1 продолжается за пределы двух смежных электродов 15 затвора, и через нее проходят два электрода 15 затвора таким образом, что она разделяется на три секции. В секциях каждой активной области 13_1, формируются области 14 истока/стока. Каждый электрод 15 затвора, в секции между парой областей 14 истока/стока на обеих сторонах, составляет транзистор ячейки с этими областями 14 истока/стока. Середина секций каждой активной области 13_1 соединяется с нижней частью контактного столбика 24_1. Контактные столбики 24_1 соединяются в верхних частях с линиями 22_1 истока. Области 14 истока/стока двух оставшихся секций каждой активной области 13_1 соединяются с соответствующими нижними частями запоминающих элементов 1_21 и 1_22 через соответствующие наборы контактного столбика 26 и проводящего слоя 51. Каждый проводящий слой 51 перекрывается в плоскости XY с контактным столбиком 26 и запоминающим элементом 1_21 или 1_22.

Активные области 13_2 выстраиваются в линию вдоль линий 22_2 истока с интервалом. Каждая активная область 13_2 продолжается в плоскости XY поверх областей под и около двух конкретных запоминающих элементов 1 вдоль оси Z. Подробности приводятся далее. Из числа запоминающих элементов 1 одной вершины правильного шестиугольника, два запоминающих элемента 1 в вершинах шестиугольника и на диагональной линии шестиугольника, которые не являются параллельными с осью Y (запоминающие элементы 1_23 и 1_24), составляют вторую пару. Каждая активная область 13_2 продолжается поверх соответствующих областей под и около второй пары запоминающих элементов 1 (второй запоминающей пары) вдоль оси Z.

Каждая активная область 13_2 продолжается за пределы двух смежных электродов 15 затвора, и через нее проходят два электрода 15 затвора таким образом, что она разделяется на три секции. В секциях каждой активной области 13_2, формируются области 14 истока/стока. Каждый электрод 15 затвора, в секции между парой областей 14 истока/стока на обеих сторонах, составляет транзистор ячейки с этими областями 14 истока/стока. Середина секций каждой активной области 13_2 соединяется с нижней частью контактного столбика 24_2. Контактные столбики 24_2 соединяются в верхних частях с линиями 22_2 истока. Области 14 истока/стока двух оставшихся секций каждой активной области 13_2 соединяются с соответствующими нижними частями запоминающих элементов 1_23 и 1_24 через соответствующие наборы контактного столбика 26 и проводящего слоя 51. Каждый проводящий слой 51 перекрывается в плоскости XY с контактным столбиком 26 и запоминающим элементом 1_23 или 1_24.

В результате компоновки активных областей 13_1 и 13_2, описанной выше, активные области 13_1 и 13_2 отличаются по позиции (или координате) на оси Y. В частности, верхний и нижний концы каждой активной области 13_1 и верхний и нижний концы активной области 13_2 не находятся на одной линии, соответственно.

Запоминающие элементы 1 разделяются на набор первых пар запоминающих элементов и набор вторых пар запоминающих элементов, как описано выше. Как результат, в каждом столбце запоминающих элементов, запоминающие элементы 1, принадлежащие первым парам запоминающих элементов, и запоминающие элементы 1, принадлежащие вторым парам запоминающих элементов, расположены попеременно.

Запоминающие элементы 1 соединяются в верхних частях с проводящими слоями 52. В частности, запоминающие элементы 1_21, 1_22, 1_23 и 1_24 соединяются в нижних частях с нижними частями проводящих слоев 52_21, 52_22, 52_23 и 52_24, соответственно. Проводящие слои 52 имеют, в плоскости XY, формы, аналогичные формам запоминающих элементов 1, и например, имеют плоские формы, меньшие плоских форм запоминающих элементов 1. Верхние части проводящих слоев 52 соединяются с нижними частями сквозных контактных столбиков 27.

Каждый сквозной контактный столбик 27 соединяется с нижней частью разрядной линии 21. Разрядные линии 21 продолжаются вдоль оси Y и размещаются в столбцах в плоскости XY. Разрядные линии 21 расположены в слое или на уровне выше линии 22 истока вдоль оси Z. Разрядные линии 21 включают в себя разрядные линии 21_1 и 21_2. Разрядные линии 21_1 расположены выше линий 22_1 истока вдоль оси Z, т.е. перекрываются с линиями 22_1 истока в плоскости XY. Разрядные линии 21_2 расположены выше линий 22_2 истока вдоль оси Z, т.е. перекрываются с линиями 22_2 истока в плоскости XY.

Каждые первые пары (1_21 и 1_22) запоминающих элементов электрически соединяются с разрядной линией 21_1 выше, вдоль оси Z, соответствующей линии 22_1 истока (или линии 22_1 истока, с которой эта первая пара запоминающих элементов электрически соединяется). С этой целью, два сквозных контактного столбика 27 (27_21 и 27_21) для первой пары запоминающих элементов имеют эллиптические формы, которые развертываются вдоль оси X в плоскости XY, и эллиптические формы перекрываются в плоскости XY с проводящим слоем 52_21 или 52_22 и разрядной линией 21_21. В частности, каждый сквозной контактный столбик 27_21, электрически соединенный с запоминающим элементом 1_21, перекрывается в плоскости XY в верхней правой части с проводящим слоем 52_21 для этого запоминающего элемента 1_21 и в центральной части с разрядной линией 21_1. Каждый сквозной контактный столбик 27_22, электрически соединенный с запоминающим элементом 1_22, перекрывается в плоскости XY в нижней левой части с проводящим слоем 52_22 для этого запоминающего элемента 1_22 и в центральной части с разрядной линией 21_1. Сквозные контактные столбики 27_21 и 27_22 электрически соединяются с разрядными линиями 21_1 через проводящие слои 54. В частности, каждый сквозной контактный столбик 27_21 и каждый сквозной контактный столбик 27_22 соединяются в верхней части с проводящим слоем 54, который соединяется в верхней части с разрядной линией 21_1.

Каждый сквозной контактный столбик 27_21 также совместно используется с запоминающим элементом 1 другой первой пары запоминающих элементов. В частности, сквозной контактный столбик 27_21, электрически соединенный с запоминающим элементом 1_21 конкретной первой пары запоминающих элементов, является идентичным сквозному контактному столбику 27_22, электрически соединенному с запоминающим элементом 1_22 другой первой пары запоминающих элементов. В частности, каждый сквозной контактный столбик 27_21 совместно используется посредством запоминающего элемента 1_21 и запоминающего элемента 1_22, смежного с этим запоминающим элементом 1_21, с линией 22_1 истока между ними. С этой целью, каждый сквозной контактный столбик 27_21 перекрывается в плоскости XY с запоминающим элементом 1_21 одной из двух первых пар запоминающих элементов и с запоминающим элементом 1_22 другой из пар.

Каждая вторая пара (1_23, 1_24) запоминающих элементов электрически соединяется с разрядной линией 21_2 выше, вдоль оси Z, соответствующей линии 22_2 истока (или линии 22_2 истока, с которой эта вторая пара запоминающих элементов электрически соединяется). С этой целью, два сквозных контактного столбика 27 (27_23 и 27_24) для этой второй пары запоминающих элементов имеют эллиптические формы, которые развертываются вдоль оси X в плоскости XY, и эллиптические формы перекрываются в плоскости XY с проводящим слоем 52_23 или 52-24 и разрядной линией 21_22. В частности, каждый сквозной контактный столбик 27_23, электрически соединенный с запоминающим элементом 1_23, перекрывается в плоскости XY в нижней правой части с проводящим слоем 52_23 для этого запоминающего элемента 1_23 и в центральной части с разрядной линией 21_2. Каждый сквозной контактный столбик 27_24, электрически соединенный с запоминающим элементом 1_24, перекрывается в плоскости XY в верхней левой части с проводящим слоем 52_24 для этого запоминающего элемента 1_24 и в центральной части с разрядной линией 21_2. Сквозные контактные столбики 27_23 и 27_24 электрически соединяются с разрядными линиями 21_2 через проводящие слои 54. В частности, каждый сквозной контактный столбик 27_23 и каждый сквозной контактный столбик 27_24 соединяются в верхней части с проводящим слоем 54, который соединяется в верхней части с разрядной линией 21_2.

Каждый сквозной контактный столбик 27_23 также совместно используется с запоминающим элементом 1 другой второй пары запоминающих элементов. В частности, сквозной контактный столбик 27_23, электрически соединенный с запоминающим элементом 1_23 конкретной второй пары запоминающих элементов, является идентичным сквозному контактному столбику 27_24, электрически соединенному с запоминающим элементом 1_24 другой второй пары запоминающих элементов. В частности, каждый сквозной контактный столбик 27_23 совместно используется посредством запоминающего элемента 1_23 и запоминающего элемента 1_24, смежного с этим запоминающим элементом 1_23, с линией 22_2 истока между ними. С этой целью, каждый сквозной контактный столбик 27_23 перекрывается в плоскости XY с запоминающим элементом 1_23 одной из двух вторых пар запоминающих элементов и с запоминающим элементом 1_24 другой из пар.

В результате компоновки сквозных контактных столбиков 27_21 и 27_22, описанных выше, сквозные контактные столбики 27_21 и сквозные контактные столбики 27_22 попеременно находятся вдоль оси Y, сквозные контактные столбики 27_21 выстраиваются в линию вдоль оси X, и сквозные контактные столбики 27_22 выстраиваются в линию вдоль оси X. Сквозные контактные столбики 27_21 и 27_22, которые выстраиваются в линию вдоль конкретной разрядной линии 21, соединяются в верхних частях с нижней частью этой разрядной линии 21.

Проводящие слои 51, 52 и/или 54 могут предоставляться или не предоставляться. Фиг. 44-46 иллюстрируют пример, который не включает в себя проводящие слои 51, 52 или 54. Фиг. 44 иллюстрирует вид части запоминающего устройства по второму примеру четвертого варианта осуществления при виде сверху. Фиг. 44 не иллюстрирует некоторые компоненты в целях прояснения чертежа. Фиг. 45 и 46 иллюстрируют виды вдоль линии XLV-XLV и линии XLVI-XLVI по фиг. 44, соответственно.

Как проиллюстрировано на фиг. 44-46, контактные столбики 26 соединяются в верхних частях с нижними частями запоминающих элементов 1. Запоминающие элементы 1 соединяются в верхних частях с нижними частями сквозных контактных столбиков 27.

Как описано выше, согласно четвертому варианту осуществления, запоминающие элементы 1 выполнены с возможностью располагаться в вершинах и в центрах правильных шестиугольников, и как результат, все смежные запоминающие элементы 1 имеют идентичный интервал, аналогично первому варианту осуществления. По этой причине, могут получаться преимущества, идентичные преимуществам первого варианта осуществления. Помимо этого, активные области 13, разрядные линии 21, линии 22 истока, контактные столбики 24 и 26 и сквозные контактные столбики 27 четвертого варианта осуществления также предоставляют возможность соединений активных областей 13, запоминающих элементов 1, разрядных линий 21 и линий 22 истока.

Пятый вариант осуществления

Пятый вариант осуществления основан на компоновке запоминающих элементов 1, расположенных в вершинах и в центрах правильных шестиугольников, аналогично первому варианту осуществления.