Результат интеллектуальной деятельности: УСТРОЙСТВО ПЕРВИЧНОЙ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и предназначено для цифровой обработки радиолокационных сигналов и управления аппаратурой в составе малогабаритного радиолокационного комплекса.

Из существующего уровня техники известен аналог - система Т2-РМС [1], представляющая собой мезонинный модуль, содержащий четыре цифровых сигнальных процессора (ЦСП) ADSP-TS201, микросхемы оперативных запоминающих устройств (ОЗУ) и постоянных запоминающих устройств (ПЗУ), PCI-контроллер, программируемую логическую интегральную схему (ПЛИС) Virtex-II Pro, при этом процессоры связаны между собой двунаправленной 64-разрядной кластерной шиной, которая соединена с ОЗУ и PCI-контроллером, в свою очередь, PCI-контроллер соединен с ПЗУ и контроллером ввода-вывода 8-разрядной периферийной шиной, причем 64-разрядная шина PCI-контроллера является 64-разрядной шиной PCI системы Т2-РМС, шина расширения РМС которой соединена с шиной РМС контроллера ввода-вывода.

Недостатком такой системы является общая для четырех процессоров 64-разрядная кластерная шина, обеспечивающая совместный доступ к ОЗУ. Таким образом, при одновременном обращении нескольких процессоров к ОЗУ возможно существенное снижение производительности системы.

Наиболее близкой к описываемому устройству системой является известная параллельная вычислительная система (ПВС) с программируемой архитектурой [2], принятая за прототип и содержащая микропроцессоры (сигнальный микропроцессор 1892 ВМ2Я) - 4 шт., микросхемы динамических оперативных запоминающих устройств (ДОЗУ) 64М×64 - 4 шт., микросхемы программируемых постоянных запоминающих устройств (ППЗУ) Flash 1М×32 - 4 шт., микросхемы ОЗУ 8 Мбайт - 2 шт., коммутатор LINK-интерфейсов - 2 шт., системный контроллер - 1 шт., генератор тактовой частоты 10 МГц - 1 шт., генератор тактовой частоты 106.25 МГц - 1 шт., генератор тактовой частоты 40 МГц - 1 шт., контроллер Fibre channel - 1 шт., контроллер мультиплексного канала обмена (МКО) - 1 шт., приемопередатчики LVDS - 4 шт., приемопередатчики TLK - 4 шт., приемопередатчики МКО HI-1574 - 2 шт. с соответствующими связями.

Недостатком такой системы является низкая производительность на задачах цифровой обработки сигналов в реальном режиме времени. При наличии высокоскоростных внутренних и внешних интерфейсов, позволяющих обмениваться информацией на скоростях порядка 50-100 Мбайт/с, суммарная производительность ПВС составляет менее 2 GFLOPS, что недостаточно для решения задач обработки оцифрованного на большой частоте дискретизации сигнала (требуются вычислительные мощности порядка 20-50 и более GFLOPS). Кроме того, нет возможности хранить на ПВС большие объемы данных.

Технический результат предлагаемого устройства - улучшение технических характеристик, а именно повышение производительности вычислительной системы и увеличение объема ПЗУ.

Повышение производительности вычислительной системы достигается тем, что в известное устройство, содержащее четыре процессора, дополнительно введены два процессора, при этом пиковая производительность применяемых в предлагаемом устройстве процессоров в 6-12 раз (в зависимости от обрабатываемых типов данных) больше, чем у процессоров, применяемых в прототипе.

Увеличение объема ПЗУ достигается тем, что в известное устройство дополнительно добавлена микросхема NAND флэш-памяти.

Микросхемы ДОЗУ, применяемые в известном устройстве, с целью импортозамещения и повышения надежности заменены на отечественные микросхемы статических оперативных запоминающих устройств (СОЗУ). К одному из вновь введенных процессоров подключено ДОЗУ, к другому - СОЗУ. В состав устройства дополнительно введены две микросхемы ПЗУ, подключенные к двум добавленным процессорам, и ПЛИС с подключенной к ней ППЗУ, реализующая интерфейсные функции. Все процессоры устройства имеют отладочный интерфейс JTAG, также интерфейсом JTAG оборудованы ПЛИС и контроллер. Интерфейс JTAG позволяет проводить полноценную отладку проектов, а также записывать информацию в ПЗУ / ППЗУ.

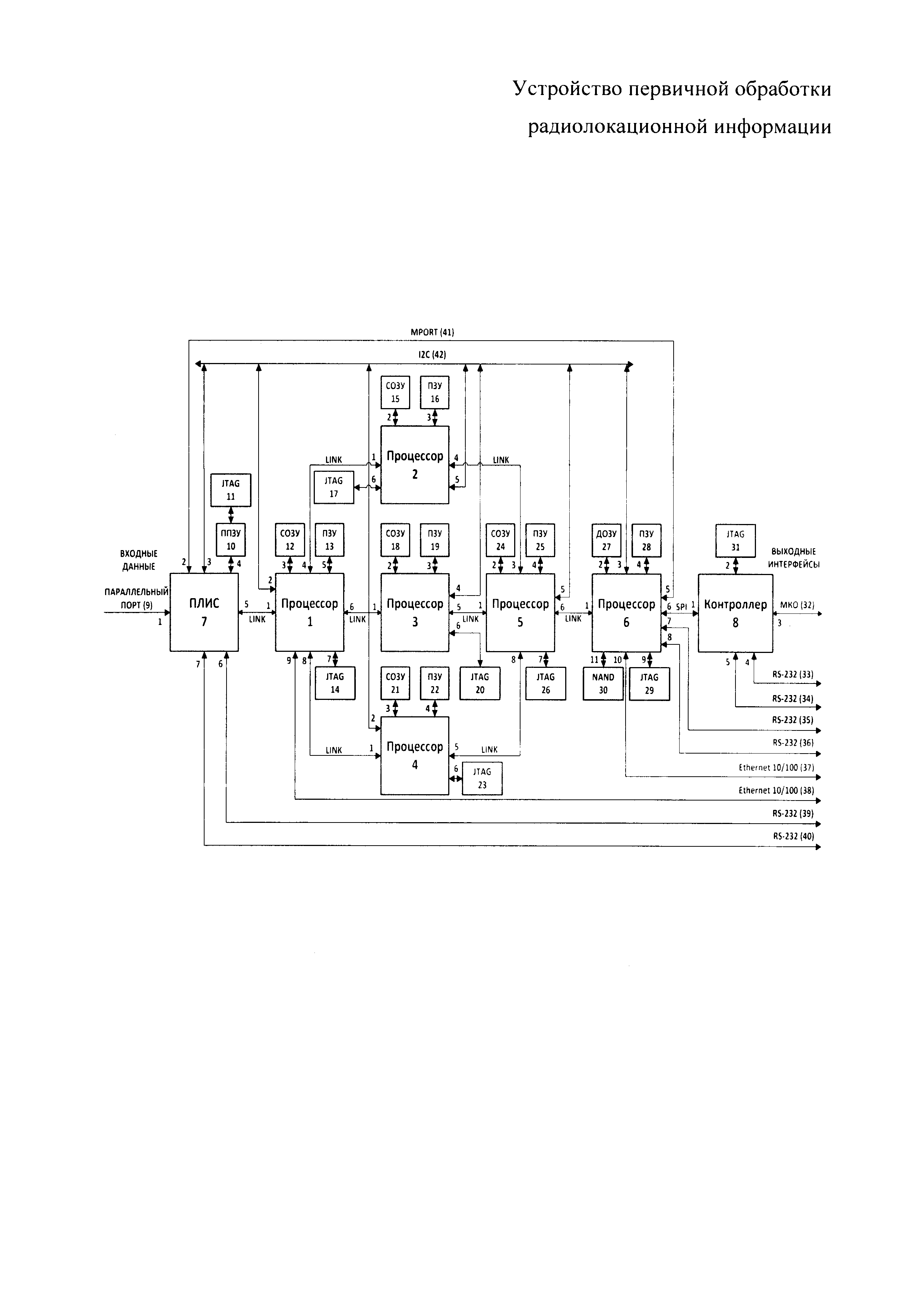

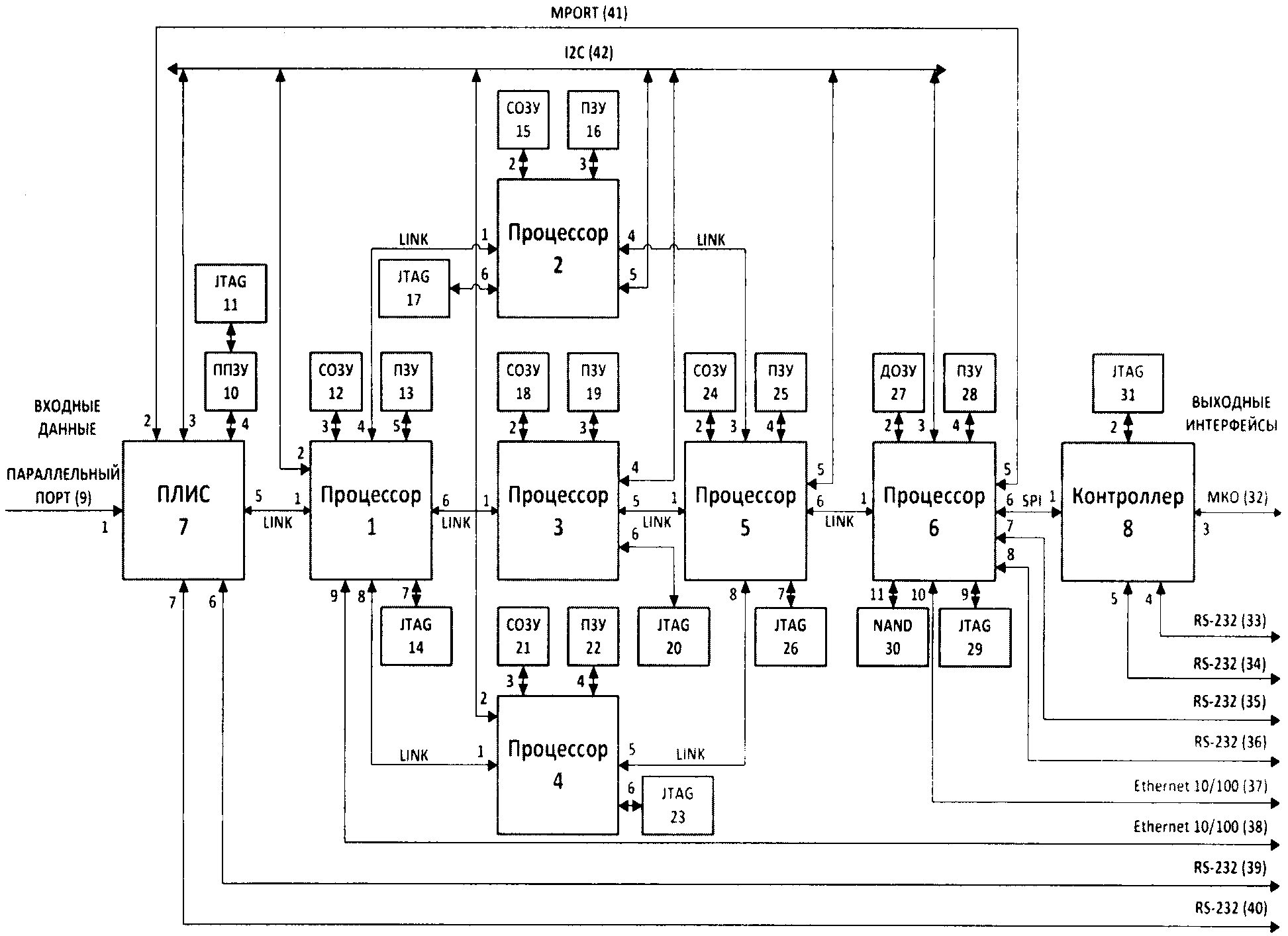

Структурная схема устройства первичной обработки радиолокационной информации представлена на фигуре.

В состав устройства первичной обработки входят:

|

Устройство первичной обработки содержит следующие внешние интерфейсы:

|

Основными вычислительными узлами устройства являются процессоры, например 1892ВМ10Я (ОАО НПЦ «ЭЛВИС») 1, 2, 3, 4, 5, 6, имеющие пиковую производительность не менее 4 GFLOPS при работе с плавающей точкой одинарной точности.

Обмен данными между процессорами ведется с помощью линк-портов (LINK), работающих в полудуплексном режиме на скорости 250 Мбит/с. Все процессоры имеют собственное поле памяти, состоящее из СОЗУ 4 Мбайт (две микросхемы, например, 1645РУ4У 1Мх16) и ПЗУ объемом 2 Мбайт (микросхема, например, 1636РР2У 2Мх8). К процессору 6 вместо СОЗУ подключено ДОЗУ 27 объемом 128 Мбайт. Также к процессору 6 подключено ПЗУ (NAND 30) объемом 128 Мбайт (организация 128Мх8). К ПЛИС 7 (микросхема, например, 5576ХС4Т) подключено загрузочное ППЗУ 10 объемом 4Мбит (микросхема, например, 5576РС1У). Контроллер 8 (микросхема, например, 1986ВЕ1Т) соединен с процессором 6 по интерфейсу SPI.

Через вход 1 ПЛИС 7 обеспечивается прием данных по параллельному 32-разрядному интерфейсу (параллельный порт 9), вход-выход 2 ПЛИС 7 подключен к входу-выходу 5 порта внешней памяти MPORT 41 процессора 6, через вход-выход 3 ПЛИС 7 обеспечивается подключение внешних устройств к шине I2C 42, вход-выход 4 ПЛИС 7 предназначен для подключения загрузочного ППЗУ 10 и программатора JTAG 11, вход-выход 6 ПЛИС 7 обеспечивает связь по интерфейсу RS-232 39, а вход-выход 7 ПЛИС 7 обеспечивает связь по интерфейсу RS-232 40, при этом через вход-выход 5 (LINK) ПЛИС 7 осуществляется обмен информацией в полудуплексном режиме с входом-выходом 1 (LINK) процессора 1, чей вход-выход 2 связан с шиной I2C 42, к входу-выходу 3 процессора 1 подключено СОЗУ 12, а к входу-выходу 5 процессора 1 подключено ПЗУ 13, также вход-выход 7 процессора 1 служит для подключения адаптера JTAG 14, в свою очередь, вход-выход 9 процессора 1 необходим для организации обмена по каналу Ethernet 10/100 38 с внешними абонентами, через вход-выход 4 (LINK) процессора 1 организован полудуплексный обмен данными с входом-выходом 1 (LINK) процессора 2, чей вход-выход 2 предназначен для подключения СОЗУ 15, а к входу-выходу 3 процессора 2 подключено ПЗУ 16, вход-выход 5 процессора 2 связан с шиной I2C 42, при этом к входу-выходу 6 процессора 2 подключается адаптер JTAG 17, а вход-выход 4 (LINK) процессора 2 подключен к входу-выходу 3 (LINK) процессора 5, вход-выход 2 которого подключен к СОЗУ 24, а вход-выход 4 - к загрузочному ПЗУ 25, вход-выход 5 процессора 5 подсоединен к шине I2C 42, при этом вход-выход 7 процессора 5 предназначен для подключения адаптера JTAG 26, а через вход-выход 1 (LINK) процессора 5 организуется полудуплексный обмен данными с входом-выходом 5 (LINK) процессора 3, вход-выход 2 которого предназначен для подключения СОЗУ 18, а к входу-выходу 3 процессора 3 подключено ПЗУ 19, вход-выход 4 процессора 3 предназначен для подключения к шине I2C 42, при этом к входу-выходу 6 процессора 3 подключается адаптер JTAG 20, в свою очередь, вход-выход 1 (LINK) процессора 3 отвечает за организацию полудуплексной связи с входом-выходом 6 (LINK) процессора 1, вход-выход 8 (LINK) которого отвечает за организацию полудуплексной связи с входом-выходом 1 (LINK) процессора 4, чей вход-выход 2 подключен к шине I2C 42, а вход-выход 3 процессора 4 предназначен для подключения СОЗУ 21, при этом к входу-выходу 4 процессора 4 подключено ПЗУ 22, а через вход-выход 6 процессора 4 организован интерфейс обмена с адаптером JTAG 23, при этом вход-выход 5 (LINK) служит для организации полудуплексного обмена данными с входом-выходом 8 (LINK) процессора 5, чей вход-выход 6 подключен к входу-выходу 1 (LINK) процессора 6, вход-выход 2 которого предназначен для подключения ДОЗУ 27, а с помощью входа-выхода 3 процессор 6 подключен к шине I2C 42, при этом для организации процедуры загрузки процессор 6 с помощью входа-выхода 4 подключен к ПЗУ 28, а входы-выхода 7 и 8 процессора 6 предназначены для реализации интерфейсов RS-232 35 и RS-232 36 соответственно, также вход-выход 9 процессора 6 используется для подключения адаптера JTAG 29, а для реализации подключения ПЗУ большого объема NAND-типа (NAND 30) служит вход-выход 11 процессора 6, при этом вход-выход 10 процессора 6 служит для организации обмена информацией с внешними потребителями через канал Ethernet 10/100 37, а вход-выход 6 (интерфейс SPI) процессора 6 подключен к входу-выходу 1 (интерфейс SPI) контроллера 8, чей вход-выход 2 используется для подключения программатора JTAG 31, а вход-выход 3 организует интерфейс обмена с помощью МКО (по ГОСТ Р52070-2003) 32, при этом входы-выходы 4 и 5 контроллера 8 предназначены для организации интерфейсов RS-232 33 и RS-232 34, соответственно.

Общая схема работы устройства первичной обработки радиолокационной информации выглядит следующим образом. Входной поток оцифрованных данных, прошедших децимацию и согласованную фильтрацию, через 32-разрядный параллельный интерфейс (параллельный порт 9) поступает в ПЛИС 7, которая преобразует и выдает его через линк-порт (вход-выход 5) на процессор 1. Процессор 1 осуществляет пространственную обработку входного сигнала, формирует пять угломестных каналов и канал подавления боковых лепестков (ПБЛ), осуществляет компенсацию активной шумовой помехи, корректирует амплитудно-фазовые искажения входного сигнала. Также на процессоре 1 реализован цифровой имитатор, позволяющий формировать различные типы целей и помех. В программное обеспечение процессора 1 встроена возможность регистрации полного потока входных данных через канал Ethernet 10/100 38 (соответствует входу-выходу 9 процессора 1). Помимо этого канал Ethernet 10/100 38 используется для обновления программного обеспечения процессоров 1, 2, 3, 4, 5, 6.

С процессора 1 обработанная информация через линк-порты (входы-выходы 4, 6 и 8) поступает в линк-порты (входы-выходы 1) процессоров 2, 3 и 4, осуществляющих временную межпериодную обработку данных. Каждый процессор временной межпериодной обработки данных обрабатывает данные из двух угломестных каналов, осуществляет подавление местных предметов и пассивных помех с помощью системы селекции движущихся целей (СДЦ), выполняет когерентное накопление сигнала с последующим амплитудным детектированием. С трех процессоров межпериодной обработки (процессоры 2, 3 и 4) данные через три линк-порта (входы-выходы 4, 5 и 5 соответственно) поступают в линк-порты (входы-выходы 3, 1 и 8) процессора 5, который выполняет алгоритм стабилизации уровня ложных тревог (СУЛТ), ищет максимумы, определяет точные координаты целей, по которым формирует целеуказания. Сформированные целеуказания выдаются через линк-порт (вход-выход 6) процессора 5 и поступают в линк-порт (вход-выход 1) процессора 6.

К процессору 6 подключена большая часть внешних интерфейсов, необходимых для обмена с потребителями информации и внешними устройствами. На процессоре 6 реализован программный диспетчер, выдающий через канал Ethernet 10/100 37 (соответствует входу-выходу 10 процессора 6) данные по целеуказаниям внешним потребителям, а также осуществляющий управление параметрами первичной обработки. Для реализации управления используется порт внешней памяти процессора 6 MPORT 41, подключенный непосредственно к ПЛИС 7. При получении диспетчером управляющей кодограммы необходимые данные подмешиваются во входной поток информации через ПЛИС 7.

Для организации консольного ввода-вывода на процессоре 6 используется интерфейс RS-232 35 (соответствует входу-выходу 7 процессора 6). В свою очередь, для обеспечения обмена с аппаратурной спутниковой навигации используется интерфейс RS-232 36 (соответствует входу-выходу 8 процессора 6).

С помощью порта внешней памяти MPORT 41 процессора 6 и ПЛИС 7 реализовано программно-аппаратное управление интерфейсом флэш-памяти NAND 30. Данная возможность используется для регистрации обработанных данных, поступающих на процессор 6.

Все процессоры устройства связаны между собой единой шиной I2C 42. Интерфейс I2C реализован на базе ПЛИС 7 и позволяет организовать канал обмена данными, а также консольный ввод-вывод с каждого процессора.

На ПЛИС 7 реализованы интерфейсы RS-232 (39, 40) (соответствуют входам-выходам 6 и 7 ПЛИС 7 соответственно), обеспечивающие обмен с радиостанциями.

Для организации обмена по интерфейсу МКО 32 и двух интерфейсов RS-232 (33, 34) в состав устройства включен контроллер 8. Интерфейс МКО 32 соответствует входу-выходу 3 контроллера 8 и предназначен для организации обмена с аналого-цифровой аппаратурой, выполняющей функции синхронизации и управления. Интерфейс RS-232 33 соответствует входу-выходу 4 контроллера 8 и предназначен для организации обмена с аппаратурой передачи данных (сопряжение с внешними устройствами). В свою очередь, интерфейс RS-232 34 соответствует входу-выходу 5 контроллера 8 и предназначен для организации обмена с аппаратурой передачи данных и управления.

Таким образом, применение в составе устройства высокопроизводительных цифровых сигнальных процессоров, замена микросхем ДОЗУ на быстродействующее СОЗУ, применение ПЛИС, реализующей интерфейсные функции, а также увеличение числа процессоров и включение в состав устройства ПЗУ большого объема типа NAND-флэш позволило достичь заявленного технического результата: улучшение технических характеристик, а именно повышение производительности вычислительной системы и увеличение объема ПЗУ.

Источники информации

1. Т2-РМС Bitt Ware, Inc products / DS-T2PM Rev. 0.8.2 January 2009.

2. Патент РФ №2486581, опубликован 27.06.2013, МПК G06F 11/16, G06F 15/16.

Устройство первичной обработки радиолокационной информации, содержащее четыре процессора, контроллер, микросхему динамического оперативного запоминающего устройства (ДОЗУ), четыре постоянных запоминающих устройства (ПЗУ), отладочные интерфейсы JTAG, при этом пятый вход-выход первого процессора подключен к ПЗУ, а седьмой вход-выход первого процессора соответствует отладочному интерфейсу JTAG, в свою очередь, третий вход-выход второго процессора подключен к ПЗУ, а шестой вход-выход второго процессора соответствует отладочному интерфейсу JTAG, помимо этого к третьему входу-выходу третьего процессора подключено ПЗУ, а шестой вход-выход третьего процессора соответствует отладочному интерфейсу JTAG, также к четвертому входу-выходу четвертого процессора подключено ПЗУ, а шестой вход-выход четвертого процессора соответствует отладочному интерфейсу JTAG, в свою очередь, второй вход-выход контроллера соответствует отладочному интерфейсу JTAG, отличающееся тем, что в него дополнительно введены пятый и шестой процессоры, при этом используемые в устройстве процессоры имеют на порядок большую производительность, также добавлено пять микросхем быстродействующих статических оперативных запоминающих устройств (СОЗУ), дополнительно введены два ПЗУ, помимо этого добавлена NAND флэш-память большой емкости и программируемая логическая интегральная схема (ПЛИС), первый вход которой соответствует входному параллельному порту, а второй вход-выход ПЛИС соединен с пятым входом-выходом шестого процессора (интерфейс MPORT), также третий вход-выход ПЛИС соответствует шине I2C, а к четвертому входу-выходу ПЛИС подключено загрузочное программируемое постоянное запоминающее устройство (ППЗУ), к которому подключен отладочный интерфейс JTAG, в свою очередь, шестой и седьмой входы-выходы ПЛИС соответствуют двум выходным интерфейсам RS-232, а пятый вход-выход ПЛИС соединен с первым входом-выходом первого процессора, второй вход-выход которого подключен к шине I2С, к третьему входу-выходу первого процессора подключено СОЗУ, а девятый вход-выход первого процессора соответствует интерфейсу Ethernet 10/100, также четвертый вход-выход первого процессора соединен с первым входом-выходом второго процессора, ко второму входу-выходу которого подключено СОЗУ, а пятый вход-выход второго процессора подключен к шине I2C, при этом четвертый вход-выход второго процессора соединен с третьим входом-выходом пятого процессора, ко второму входу-выходу которого подключено СОЗУ, а к четвертому входу-выходу пятого процессора подключена микросхема загрузочного ПЗУ, при этом пятый вход-выход пятого процессора подключен к шине I2C, а седьмой вход-выход пятого процессора соответствует отладочному интерфейсу JTAG, также первый вход-выход пятого процессора соединен с пятым входом-выходом третьего процессора, ко второму входу-выходу которого подключено СОЗУ, помимо этого четвертый вход-выход третьего процессора подключен к шине I2C, а первый вход-выход третьего процессора соединен с шестым входом-выходом первого процессора, восьмой вход-выход которого соединен с первым входом-выходом четвертого процессора, второй вход-выход которого подключен к шине I2C, а к третьему входу-выходу четвертого процессора подключено СОЗУ, в свою очередь, пятый вход-выход четвертого процессора соединен с восьмым входом-выходом пятого процессора, шестой вход-выход которого соединен с первым входом-выходом шестого процессора, ко второму входу-выходу которого подключено ДОЗУ, при этом третий вход-выход шестого процессора подключен к шине I2C, а к четвертому входу-выходу шестого процессора подключено загрузочное ПЗУ, также седьмой и восьмой входы-выходы шестого процессора соответствуют двум выходным интерфейсам RS-232, а девятый вход-выход шестого процессора соответствует отладочному интерфейсу JTAG, в свою очередь, десятый вход-выход шестого процессора соответствует выходному интерфейсу Ethernet 10/100, при этом к одиннадцатому входу-выходу шестого процессора подключена микросхема NAND флэш-памяти, также шестой вход-выход шестого процессора соединен с первым входом-выходом контроллера, третий вход-выход которого соответствует интерфейсу МКО (ГОСТ Р52070-2003), при этом четвертый и пятый входы-выходы контроллера соответствуют двум выходным интерфейсам RS-232.