Результат интеллектуальной деятельности: СХЕМА И СПОСОБ ДЛЯ ОПТИМИЗАЦИИ ДИАПАЗОНА ВХОДНОГО НАПРЯЖЕНИЯ ИНТЕГРАЛЬНОЙ МИКРОСХЕМЫ

Вид РИД

Изобретение

Область техники

Настоящее раскрытие относится к технологии переключения подачи электропитания и, в частности, к схеме и способу для оптимизации диапазона входного напряжения интегральной микросхемы.

Предпосылки для создания изобретения

После подачи электропитания на выход сигнала разрешения (EN) интегральной микросхемы в ней выполняется процесс инициализации. После завершения процесса инициализации внутренний уровень переключения (а именно разрешающий уровень) становится высоким, и интегральная микросхема соответственно начинает нормально работать. Во время нормальной работы интегральной микросхемы, если напряжение подводимого электропитания нестабильно и колеблется, уровень выхода сигнала разрешения EN может быть снижен, так что интегральная микросхема прекращает работать.

Раскрытие изобретения

Для решения вышеуказанной задачи настоящее раскрытие предлагает схему и способ для оптимизации диапазона входного напряжения интегральной микросхемы, чтобы обеспечить продолжение работы интегральной микросхемы в нормальном режиме, когда входное напряжение изменяется в определенных пределах.

Настоящее раскрытие предлагает схему для оптимизации диапазона входного напряжения интегральной микросхемы, которая включает:

блок повышения напряжения, вход которого электрически соединен с входным напряжением, для уравнивания уровня напряжения на его выходном выводе на основании входного напряжения;

триггерный блок, электрически подсоединенное между уравнивающим устройством и выходом сигнала разрешения интегральной микросхемы, для сравнения уровня напряжения на выходе блока повышения напряжения с заданным пороговым напряжением и подачи сигнала разрешения соответствующего уровня на выход сигнала разрешения интегральной микросхемы на основании результата сравнения, чтобы управлять включением/отключением интегральной микросхемы; и

блок стабилизатора напряжения, первый вход которого электрически соединен с выходом блока повышения напряжения, второй вход которого электрически соединен с выходом триггерного блока, и выход которого электрически соединен с управляющим входом блока повышения напряжения, для подачи напряжения соответствующего уровня на блок повышения напряжения на основании напряжений на выходах блока повышения напряжения и триггерного блока, чтобы уровень напряжения на выходе блока повышения напряжения был выше или равен пороговому напряжению и за счет этого включалась интегральная микросхема, или чтобы уровень напряжения на выходе блока повышения напряжения поддерживался на уровне выше или равном пороговому напряжению и за счет этого на работу интегральной микросхемы не влияли изменения во входном напряжении.

Вышеупомянутое блок повышения напряжения включает переключающий транзистор р-типа, подтягивающий резистор и резистор деления напряжения; исток переключающего транзистора р-тииа. электрически соединен с первым выводом подтягивающего резистора и используется как вход блока повышения напряжения для приема входного напряжения; сток переключающего транзистора р-типа используется как выход блока повышения напряжения и электрически заземлен через резистор деления напряжения; и затвор переключающего транзистора p-типа используется как управляющий вход блока повышения напряжения и электрически соединен со вторым выводом подтягивающего резистора.

Вышеупомянутое триггерный блок включает триггер Шмитта и инвертор, соединенные последовательно, при этом вход триггера Шмитта используется как вход триггерного блока и электрически соединен с выходом блока повышения напряжения, и выход инвертора используется как выход триггерного блока и электрически соединен с выходом сигнала разрешения интегральной микросхемы.

Вышеупомянутое блок стабилизатора напряжения включает первый, второй и третий полупроводниковые стабилитроны, соединенные последовательно, и первый, и второй переключающие транзисторы; катод первого стабилитрона электрически соединен с управляющим входом блока повышения напряжения, анод первого стабилитрона электрически соединен с катодом второго стабилитрона, анод второго стабилитрона электрически соединен с катодом третьего стабилитрона и анод третьего стабилитрона электрически заземлен; первый электрод и второй электрод первого переключающего транзистора электрически соединены с обоими выводами третьего стабилитрона соответственно, и затвор первого переключающего транзистора электрически соединен с выходом блока повышения напряжения; и первый электрод, и второй электрод второго переключающего транзистора электрически соединены с катодом второго стабилитрона и анодом третьего стабилитрона соответственно, и затвор второго переключающего транзистора электрически соединен с выходом триггерного блока.

Вышеупомянутые первый и второй переключающие транзисторы являются переключающими транзисторами n-типа.

Вышеупомянутые первый и второй переключающие транзисторы являются переключающими транзисторами р-типа.

Помимо этого, настоящее раскрытие также предлагает способ оптимизации схемы с диапазоном входного напряжения интегральной микросхемы, включающий следующие этапы:

получение блоком повышения напряжения входного напряжения с последующим выводом напряжения соответствующего уровня;

сравнение триггерным блоком уровня напряжения, выведенного блоком повышения напряжения, с заданным пороговым напряжением, и подача сигнала разрешения соответствующего уровня на выход сигнала разрешения интегральной микросхемы на основании результата сравнения, чтобы управлять включением/отключением интегральной микросхемы; и

получение блоком стабилизатора напряжения уровней напряжения, выведенных блоком повышения напряжения и триггерным блоком с последующим выводом напряжения соответствующего уровня на блок повышения напряжения на основании уровней напряжения, выведенных блоком повышения напряжения и триггерным блоком, чтобы уровень напряжения на выходе блока повышения напряжения был выше или равен пороговому напряжению и за счет этого включалась интегральная микросхема, или чтобы уровень напряжения на выходе блока повышения напряжения поддерживался на уровне выше или равном пороговому напряжению и за счет этого на работу интегральной микросхемы не влияли изменения во входном напряжении.

По сравнению с известным уровнем техники, схема и способ, предложенные в настоящем раскрытии, для оптимизации диапазона входного напряжения интегральной микросхемы обеспечивают продолжение работы ИС в нормальном режиме, когда входное напряжение изменяется в определенных пределах.

Краткое описание чертежей

Прилагаемые чертежи представлены для более глубокого понимания настоящего раскрытия и являются частью описания для толкования настоящего раскрытия вместе с вариантами осуществления настоящего изобретения, а не для ограничения настоящего изобретения. На прилагаемых чертежах показано следующее.

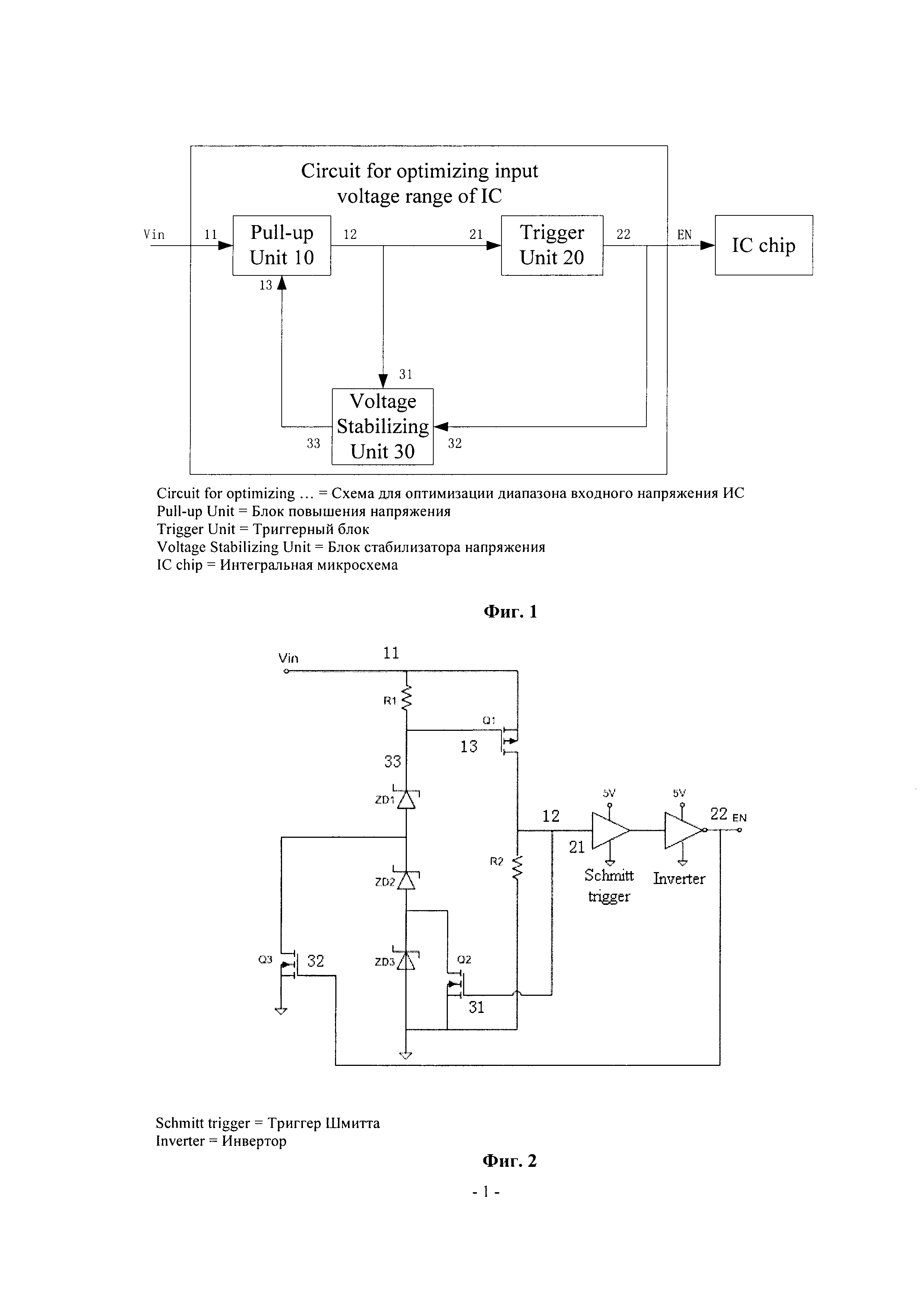

Фиг. 1 - принципиальная схема деталей схемы для оптимизации диапазона входного напряжения интегральной микросхемы согласно настоящему изобретению.

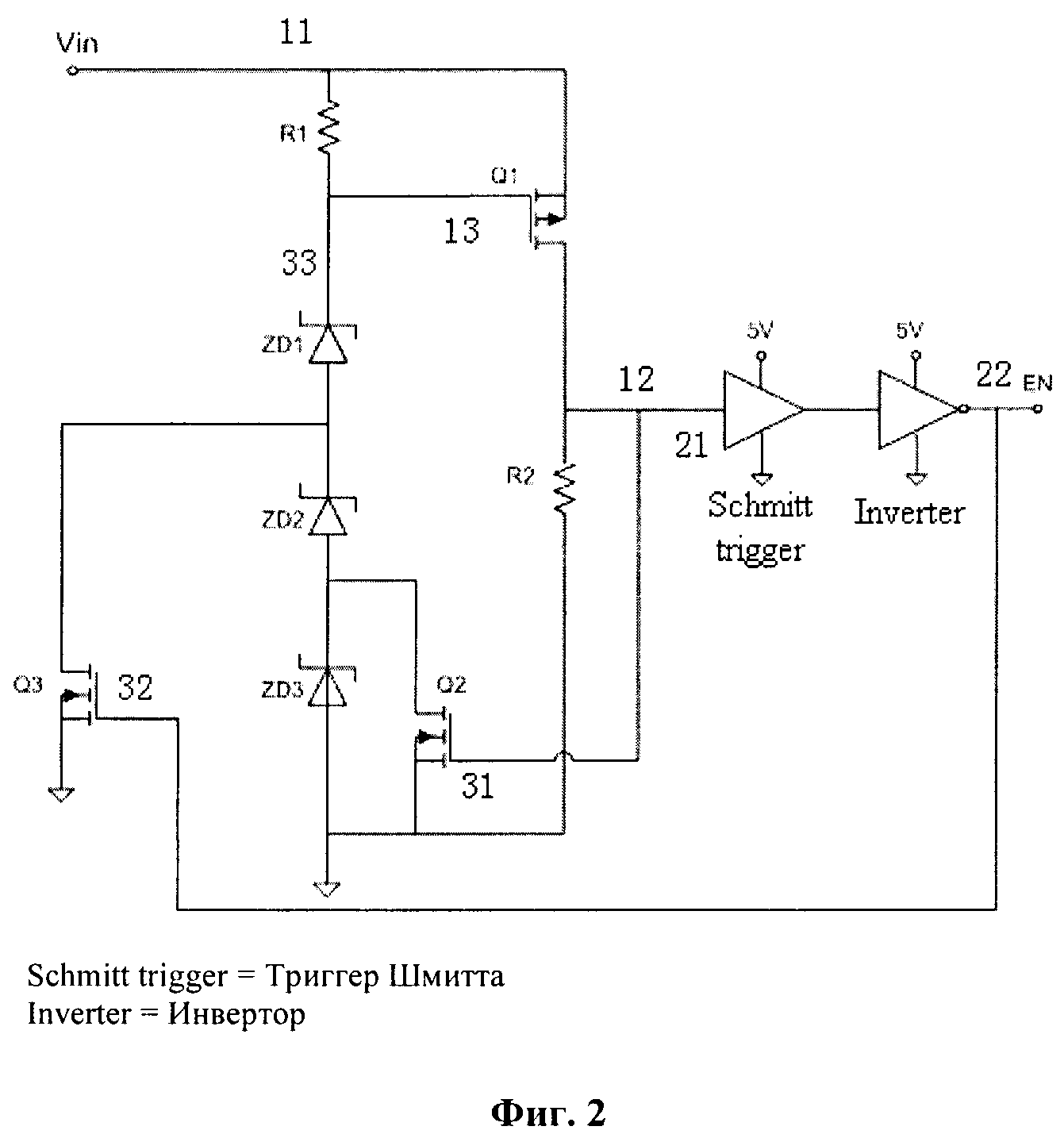

Фиг.2 - принципиальная схема соединений в одном варианте осуществления схемы для оптимизации диапазона входного напряжения интегральной микросхемы согласно настоящему изобретению.

Подробное описание вариантов осуществления

На Фиг. 1 показана принципиальная схема предложенной схемы для оптимизации диапазона входного напряжения Vin интегральной микросхемы согласно настоящему изобретению, при этом схема включает следующее.

Блок повышения напряжения 10, имеющее вход 11, электрически соединенный с входным напряжением Vin, и предназначенное для уравнивания уровня напряжения выхода 12 с входным напряжением Vin.

Триггерный блок 20, имеющее вход 21, электрически соединенный с выходом 12 блока повышения напряжения 10, и выход 22, электрически соединенный с выходом сигнала разрешения EN интегральной микросхемы, и предназначенное для сравнения уровня напряжения, выводимого блоком повышения напряжения 10, с заданным пороговым напряжением VT+, при этом:

сигнал разрешения низкого уровня выводится триггерным блоком 20 на выход сигнала разрешения EN интегральной микросхемы, когда уровень напряжения, выводимого блоком повышения напряжения 10, ниже заданного порогового напряжения VT+, так что интегральная микросхема не может работать, и

сигнал разрешения высокого уровня выводится триггерным блоком 20 на выход сигнала разрешения EN интегральной микросхемы, когда уровень напряжения, выводимого блоком повышения напряжения 10, выше или равен заданному пороговому напряжению VT+, так что интегральная микросхема начинает работать;

блок стабилизатора напряжения 30, имеющее первый вход 31, электрически соединенный с выходом 12 блока повышения напряжения 10, второй вход 32, электрически соединенный с выходом 22 триггерного блока 20, и выход 33, электрически соединенный с управляющим входом 13 блока повышения напряжения 10, и предназначенное для подачи стабилизирующего напряжения соответствующего уровня на блок повышения напряжения 10 согласно напряжениям, выведенным блоком повышения напряжения 10 и триггерным блоком 20, так что

на первой стадии уровень напряжения, выведенного блоком повышения напряжения 10, выше или равен пороговому напряжению VT+, так что интегральная микросхема начинает работать, и

на второй стадии уровень напряжения, выведенного блоком повышения напряжения 10, поддерживается на уровне выше или равном пороговому напряжению VT+, так что на работу интегральной микросхемы не влияют изменения во входном напряжении Vin.

На Фиг. 2 показана принципиальная схема соединений в одном варианте осуществления схемы для оптимизации входного напряжения Vin интегральной микросхемы согласно настоящему изобретению.

В данном случае блок повышения напряжения 10 включает переключающий транзистор p-типа Q1, подтягивающий резистор R1 и резистор деления напряжения R2. Исток переключающего транзистора p-типа Q1 электрически соединен с первым выводом подтягивающего резистора R1 и используется в качестве входа 11 блока повышения напряжения 10 для приема входного напряжения Vin. Сток переключающего транзистора p-типа Q1 используется как выход 12 блока повышения напряжения 10 и электрически заземлен через резистор деления напряжения R2. Затвор переключающего транзистора p-типа Q1 используется как управляющий вход 13 блока повышения напряжения 10 и электрически соединен со вторым выводом подтягивающего резистора R1.

В данном случае входное напряжение Vin составляет 20 В и колеблется в определенных пределах, например от 20 В до 6 В.

Триггерный блок 20 включает триггер Шмитта и инвертор NOT, соединенные последовательно друг с другом, вход триггера Шмитта используется как вход 21 триггерного блока 20 и электрически соединен с выходом 12 блока повышения напряжения 10, и выход инвертора NOT используется как выход 22 триггерного блока 20 и электрически соединен с выходом сигнала разрешения EN интегральной микросхемы.

В данном случае пороговое напряжение VT+ триггера Шмитта составляет 5 В. То есть, когда уровень напряжения, подводимого к триггеру Шмитта ниже чем 5 В, триггер Шмитта выводит напряжение высокого уровня, и затем, после того как это напряжение высокого уровня будет инвертировано инвертором NOT, сигнал разрешения низкого уровня подается на выход сигнала разрешения EN интегральной микросхемы. Когда уровень напряжения, подводимого к триггеру Шмитта, выше или равно 5 В, триггер Шмитта выводит напряжение низкого уровня, и после того, как это напряжение низкого уровня будет инвертировано инвертором NOT, сигнал разрешения высокого уровня подается на выход сигнала разрешения EN интегральной микросхемы.

Блок стабилизатора напряжения 30 включает первый, второй и третий стабилитроны ZD1, ZD2 и ZD3, соединенные последовательно, и первый, и второй переключающие транзисторы Q2 и Q3 n-типа.

В данном случае катод первого стабилитрона ZD1 электрически соединен с управляющим входом 13 блока повышения напряжения 10, а именно со вторым выводом подтягивающего резистора R1, анод первого стабилитрона ZD1 электрически соединен с катодом второго стабилитрона ZD2, анод второго стабилитрона ZD2 электрически соединен с катодом третьего стабилитрона ZD3 и анод третьего стабилитрона ZD3 электрически заземлен.

Исток первого переключающего транзистора Q2 n-типа электрически соединен с катодом третьего стабилитрона ZD3 в блоке стабилизатора напряжения 30, и его сток электрически заземлен, и затвор первого переключающего транзистора Q2 n-типа электрически соединен с выходом 12 блока повышения напряжения 10, так что катод третьего стабилитрона ZD3 соединяется с заземлением под действием напряжения высокого уровня, выводимого блоком повышения напряжения 10, то есть два вывода третьего стабилитрона ZD3 короткозамкнуты.

Исток второго переключающего транзистора Q3 n-типа электрически соединен с катодом второго стабилитрона ZD2 в блоке стабилизатора напряжения 30, и его сток электрически заземлен, и затвор второго переключающего транзистора Q3 n-типа электрически соединен с выходом 22 триггерного блока 20, так что катод второго стабилитрона ZD2 соединяется с заземлением под действием напряжения высокого уровня, выводимого триггерным блоком 20, то есть второй и третий стабилитроны ZD2 и ZD3 короткозамкнуты одновременно.

В данном случае напряжения обратного переключения первого, второго и третьего стабилитронов ZD1, ZD2 и ZD3 составляют 5,1 В. Первый и второй переключающие транзисторы Q2 и Q3 n-типа выполняют функции короткого замыкания соответствующих стабилитронов под управлением сигналов их затворов. Таким образом, также возможна замена на другие управляемые переключатели с такими же или сходными функциями.

Принцип работы вышеупомянутой схемы будет более подробно описан ниже.

На первой стадии:

1) когда блок повышения напряжения 10 начинает получать входное напряжение Vin (Vin = 20 В), первый, второй и третий стабилитроны ZD1, ZD2 и ZD3 в блоке стабилизатора напряжения 30 включаются для работы и ток протекает через подтягивающий резистор R1. Из-за действий первого, второго и третьего стабилитронов ZD1, ZD2 и ZD3 по стабилизации напряжения напряжение на втором выводе подтягивающего резистора R1 (а именно напряжение на затворе переключающего транзистора p-типа Q1) устанавливается на уровне приблизительно 15 В. В это время исток и сток переключающего транзистора p-типа соединены, затем ток истока-стока переключающего транзистора p-типа протекает через резистор деления напряжения R2 и напряжение на выходном выводе 12 блока повышения напряжения 10 начинает повышаться и становится выше нуля;

2) когда напряжение на выходном выводе 12 блока повышения напряжения 10 повышается, напряжение на затворе первого переключающего транзистора Q2 «-типа также повышается, и исток, и сток соединяются, чтобы закоротить два вывода третьего стабилитрона ZD3. В это время работают только первый и второй стабилитроны ZD1 и ZD2 в блоке стабилизатора напряжения 30. Из-за действий первого и второго стабилитронов ZD1 и ZD2 по стабилизации напряжения напряжение на втором выводе подтягивающего резистора R1 (а именно напряжение на затворе переключающего транзистора Q1 p-типа) устанавливается на уровне приблизительно 10 В, и за счет этого падение напряжения между двумя выводами подтягивающего резистора R1 увеличивается, то есть абсолютное значение разницы напряжений затвора-истока (ниже нуля) переключающего транзистора р-типа увеличивается. Согласно кривой рабочей характеристики переключающего транзистора р-типа, ток истока-стока переключающего транзистора p-типа также увеличивается, так что напряжение на выходном выводе 12 блока повышения напряжения 10 непрерывно повышается пока выходное напряжение ниже, чем пороговое напряжение VT+ триггера Шмитта. В данный период триггер Шмитта выводит напряжение высокого уровня, которое затем поступает в инвертор NOT, и, таким образом, сигнал разрешения низкого уровня подается на выход сигнала разрешения EN интегральной микросхемы, так что интегральная микросхема пока не начинает работать;

3) когда напряжение на выходном выводе 12 блока повышения напряжения 10 станет выше или равным пороговому напряжению VT+ триггера Шмитта, триггер Шмитта выводит напряжение низкого уровня, которое затем поступает в инвертор NOT, и, таким образом, сигнал разрешения высокого уровня выводится на выход сигнала разрешения EN интегральной микросхемы, так что интегральная микросхема начинает работать.

На второй стадии:

поскольку напряжение на выходном выводе 22 триггерного блока 20 высокое, исток и сток второго переключающего транзистора Q3 n-типа соединяются, чтобы закоротить второй и третий стабилитроны ZD2 и ZD3 одновременно. В это время работает только один первый стабилитрон ZD1 в блоке стабилизатора напряжения 30. Из-за действия первого стабилитрона ZD 1 по стабилизации напряжения напряжение на втором выводе подтягивающего резистора R1 (а именно напряжение на затворе переключающего транзистора Q1 р-типа) устанавливается на уровне приблизительно 5 В. В это время, даже в случае большого колебания входного напряжения Vin, например, падению с 20 В до 6 В, ток протекает через подтягивающий резистор R1 и переключающий транзистор Q1 р-типа поэтому находится во включенном состоянии, пока входное напряжение Vin выше, чем напряжение обратного переключения 5,1 В первого стабилитрона ZD1, при этом первый стабилитрон ZD1 остается включенным. В это время напряжение на выходном выводе 12 блока повышения напряжения 10 приблизительно равно входному напряжению Vin, но выше или равно пороговому напряжению VT+ триггера Шмитта, и триггерный блок 20, таким образом, подает сигнал разрешения высокого уровня на вывод EN интегральной микросхемы, так что интегральная микросхема продолжает работать в нормальном режиме, и на нее не влияет колебание входного напряжения. Конечно, входное напряжение Vin не должно быть неопределенно низким. Когда входное напряжение ниже, чем напряжение обратного переключения 5,1 В первого стабилитрона ZD1, переключающий транзистор Q1 р-типа отключается и напряжение на выходном выводе 12 блока повышения напряжения 10 становится ниже, чем пороговое напряжение VT+ триггера Шмитта, так что интегральная микросхема прекращает работать.

Из вышесказанного следует, что схема, предложенная настоящим изобретением для оптимизации диапазона входного напряжения интегральной микросхемы, может обеспечивать продолжение работы интегральной микросхемы в нормальном режиме, когда входное напряжение изменяется в определенных пределах.

Вышеприведенное описание относится к одному варианту осуществления, касающемуся использования схемы для оптимизации диапазона входного напряжения интегральной микросхемы с целях стабилизации работы, например интегральной микросхемы жидкокристаллического дисплея. Конечно, настоящее изобретение также может использоваться для питания ИС других типов. Обычный уровень входного напряжения Vin также может быть не ограничен значением 20 В и колебания также могут быть не ограничены диапазоном 20 В - 6 В, при этом выбор соответствующих деталей схемы и их параметров может быть отрегулирован и изменен согласно конкретным требованиям. Например, число стабилитронов в блоке стабилизатора напряжения может быть не ограничено тремя, и для блока стабилизатора напряжения могут быть выбраны стабилитроны с другими напряжениями обратного переключения.

Выше описаны просто предпочтительные конкретные варианты осуществления настоящего изобретения, но они не ограничивают объем охраны настоящего изобретения. Любые изменения или замены в объеме технического раскрытия настоящего изобретения, легко понятные для специалиста в данной области техники, считаются включенными в объем охраны настоящего изобретения. Соответственно, объем охраны настоящего изобретения должен определяться объемом охраны формулы изобретения.