Результат интеллектуальной деятельности: БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и связи и может быть использовано в различных функциональных узлах приемо-передающей аппаратуры.

Быстродействие операционных усилителей (ОУ), которое характеризуется максимальной скоростью нарастания выходного напряжения (ϑвых.) и временем установления переходного процесса определяет динамические параметры многих аналоговых интерфейсов датчиков, буферных каскадов, АЦП, драйверов линий связи и т.п.

В современной радиоэлектронной аппаратуре находят применение ОУ, реализованные по классической архитектуре на биполярных или полевых транзисторах с тремя токовыми зеркалами и буферным усилителем [1-11]. Такое схемотехническое решение наиболее популярно как в зарубежных [11], так и в российских [10] аналоговых микросхемах. Оно обеспечивает широкий диапазон изменения выходного напряжения (практически - от отрицательной шины питания до положительной шины питания).

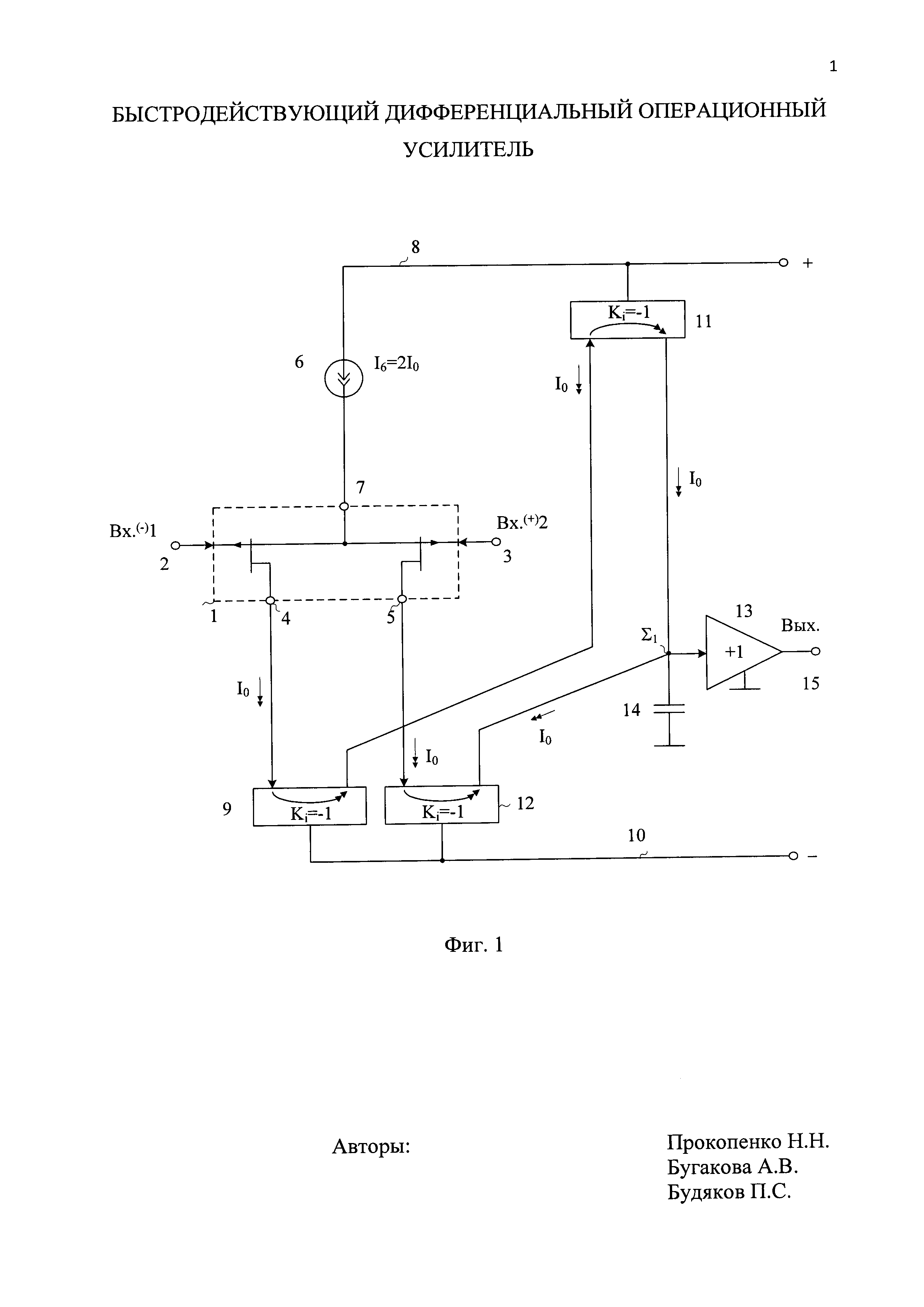

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный операционный усилитель по заявке на патент US 2010/0253433 (fig. 1). Он содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 противофазными токовыми выходами, первый источник опорного тока 6, включенный между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и первой 8 шиной источника питания, первое токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого соединен с первым 4 токовом выходом входного дифференциального каскада 1, а выход подключен ко входу второго 11 токового зеркала, согласованного с первой 8 шиной источника питания, третье 12 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого соединен со вторым 5 токовым выходом входного дифференциального каскада 1, а выход связан с выходом второго 11 токового зеркала и входом буферного усилителя 13, корректирующий конденсатор 14, связанный со входом буферного усилителя 13.

Существенный недостаток известного ОУ состоит в том, что при работе его входного каскада в режиме микротоков (1-10 мкА) его максимальная скорость нарастания выходного напряжения получается небольшой (1÷2 В/мкс).

Основная задача предполагаемого изобретения состоит в повышении (на 1-3 порядка) максимальной скорости нарастания выходного напряжения в ОУ на основе трех токовых зеркал при работе входных транзисторов ОУ с микроамперными статическими токами (1÷10 мкА).

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 противофазными токовыми выходами, первый источник опорного тока 6, включенный между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и первой 8 шиной источника питания, первое токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого соединен с первым 4 токовом выходом входного дифференциального каскада 1, а выход подключен ко входу второго 11 токового зеркала, согласованного с первой 8 шиной источника питания, третье 12 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого соединен со вторым 5 токовым выходом входного дифференциального каскада 1, а выход связан с выходом второго 11 токового зеркала и входом буферного усилителя 13, корректирующий конденсатор 14, связанный со входом буферного усилителя 13, предусмотрены новые элементы и связи - в схему введен дополнительный дифференциальный каскад 16, содержащий первый 17 и второй 18 входы, первый 19 и второй 20 противофазные токовые выходы, согласованные с первой 8 шиной источника питания, вспомогательный вход 21 дополнительного дифференциального каскада 16 для установления его статического режима по току, причем первый 17 вход дополнительного дифференциального каскада 16 связан с первым 2 входом входного дифференциального каскада 1, второй 18 вход дополнительного дифференциального каскада 16 связан со вторым 3 входом входного дифференциального каскада 1, между вспомогательным входом 21 дополнительного дифференциального каскада 16 для установления его статического режима по току и второй 10 шиной источника питания включен второй 22 источник опорного тока, между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и вспомогательным входом 21 дополнительного дифференциального каскада 16 для установления его статического режима по току включен второй 23 корректирующий конденсатор.

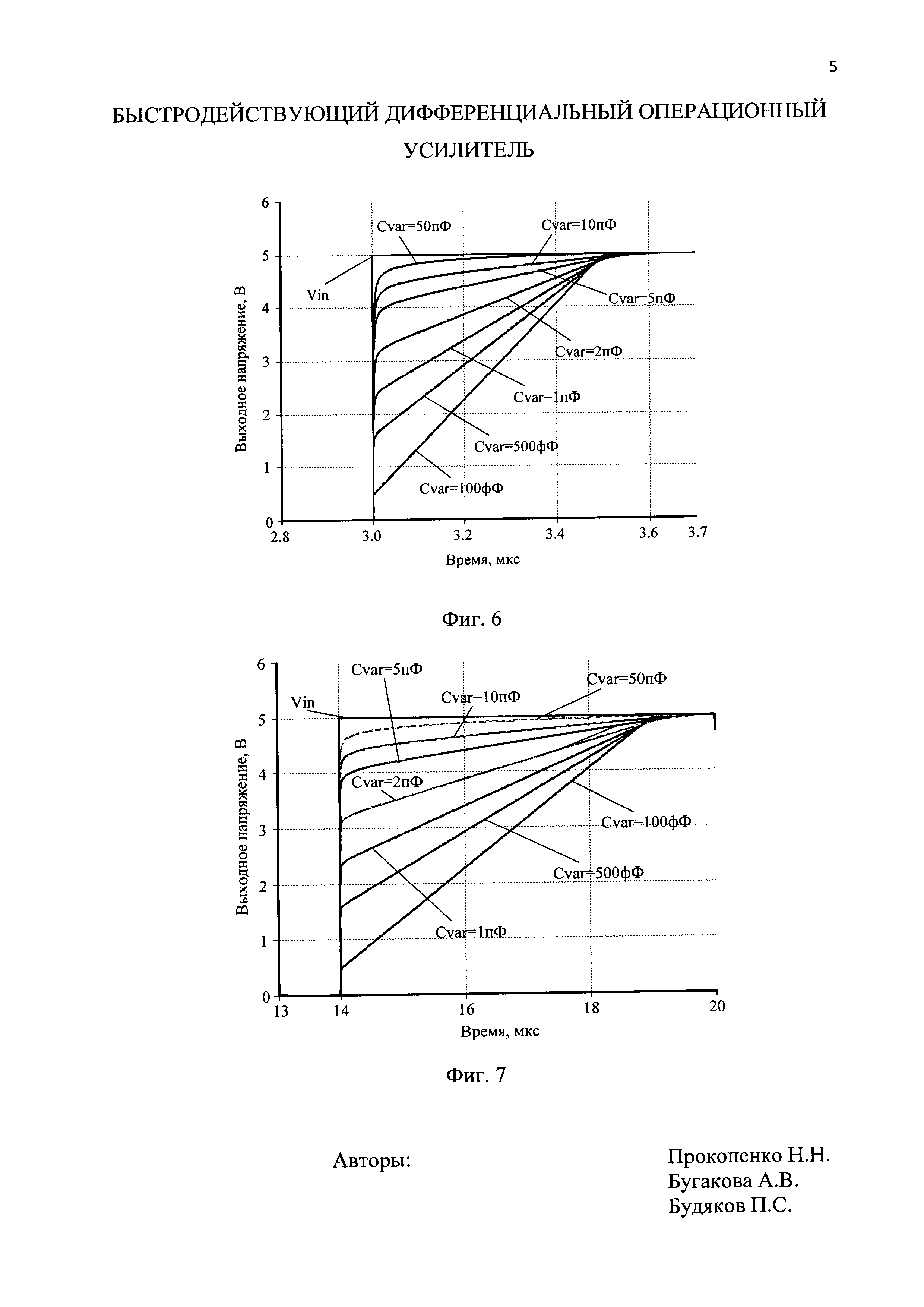

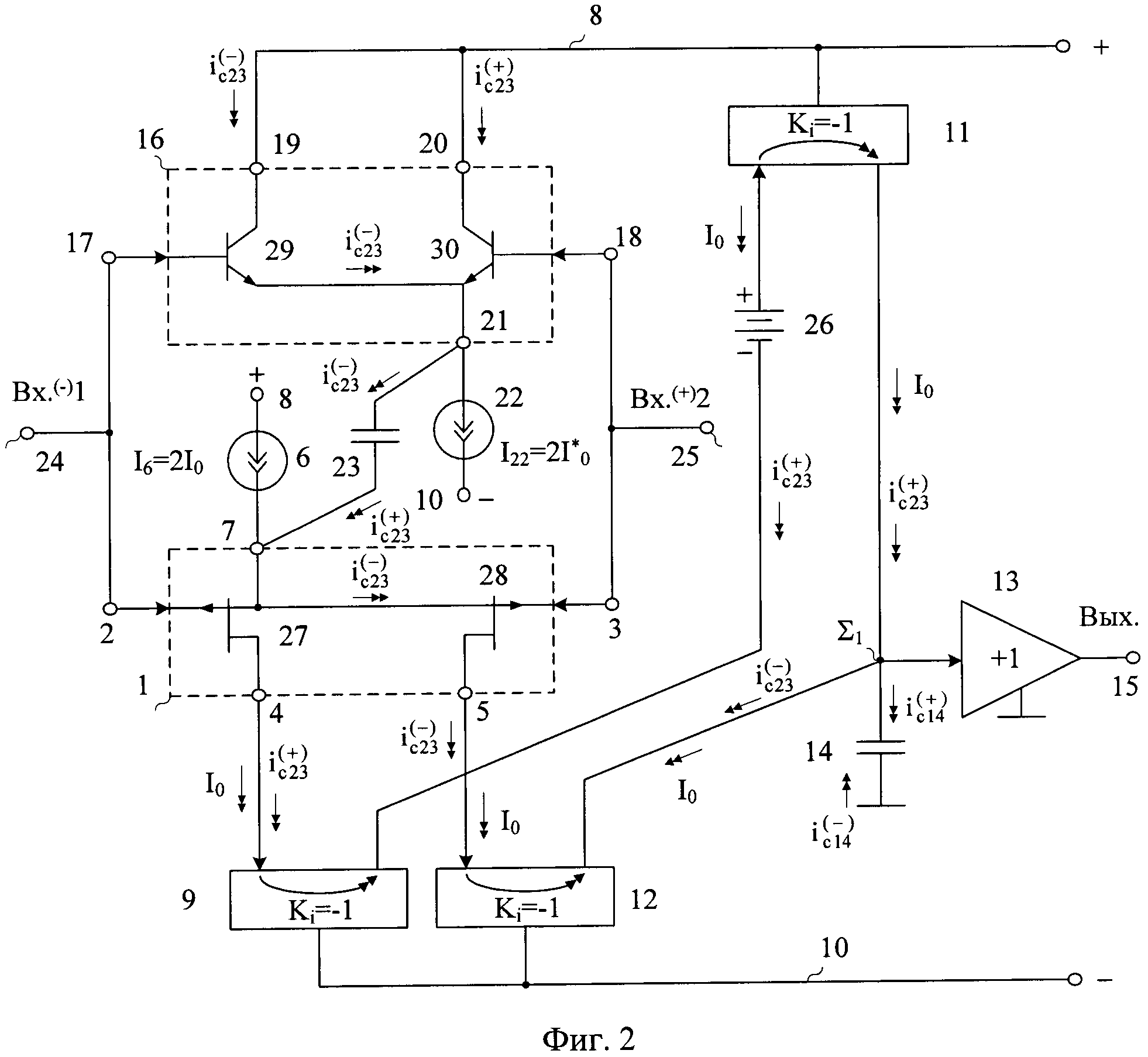

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

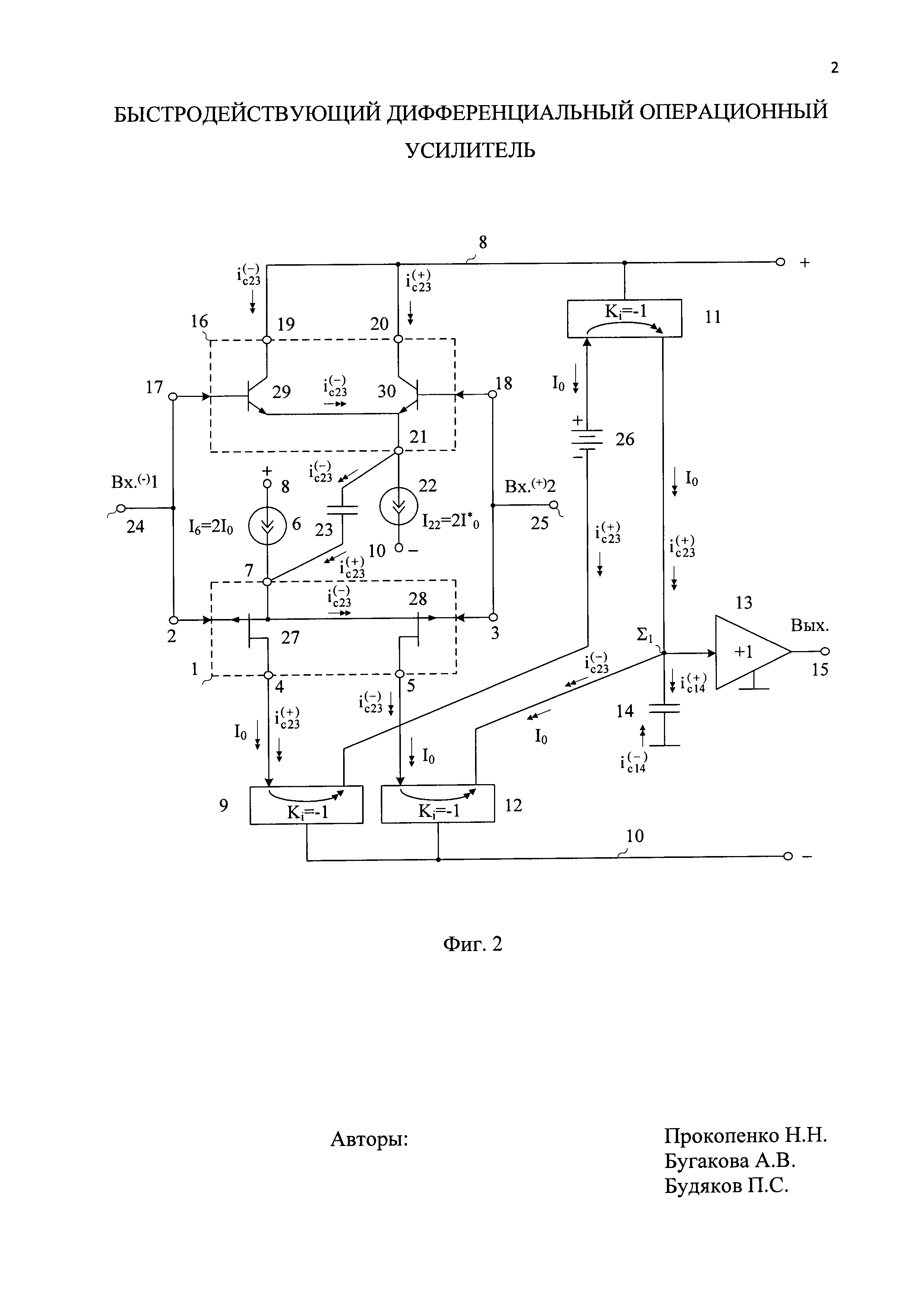

На чертеже фиг. 3 приведена схема заявляемого устройства фиг. 2 в соответствии с п. 3 и п. 4 формулы изобретения.

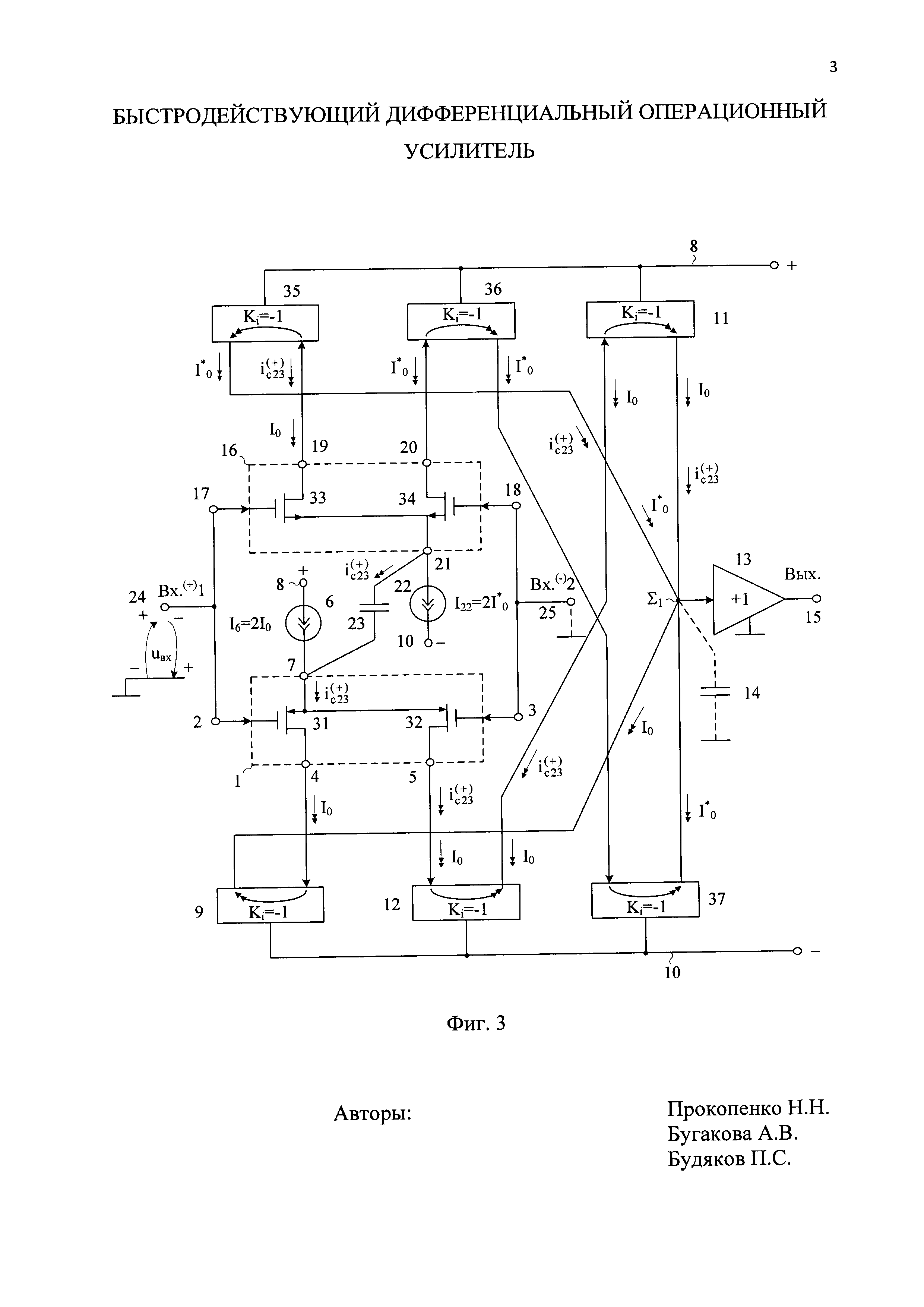

На чертеже фиг. 4 приведена схема заявляемого ОУ фиг. 2 в среде компьютерного моделирования Orcad на моделях транзисторов tsmc_035_t65.

На чертеже фиг. 5 представлена АЧХ коэффициента усиления схемы разомкнутого ОУ фиг. 4 при токах источников I1=I2=Ivar=2 мА, С1=1 пФ.

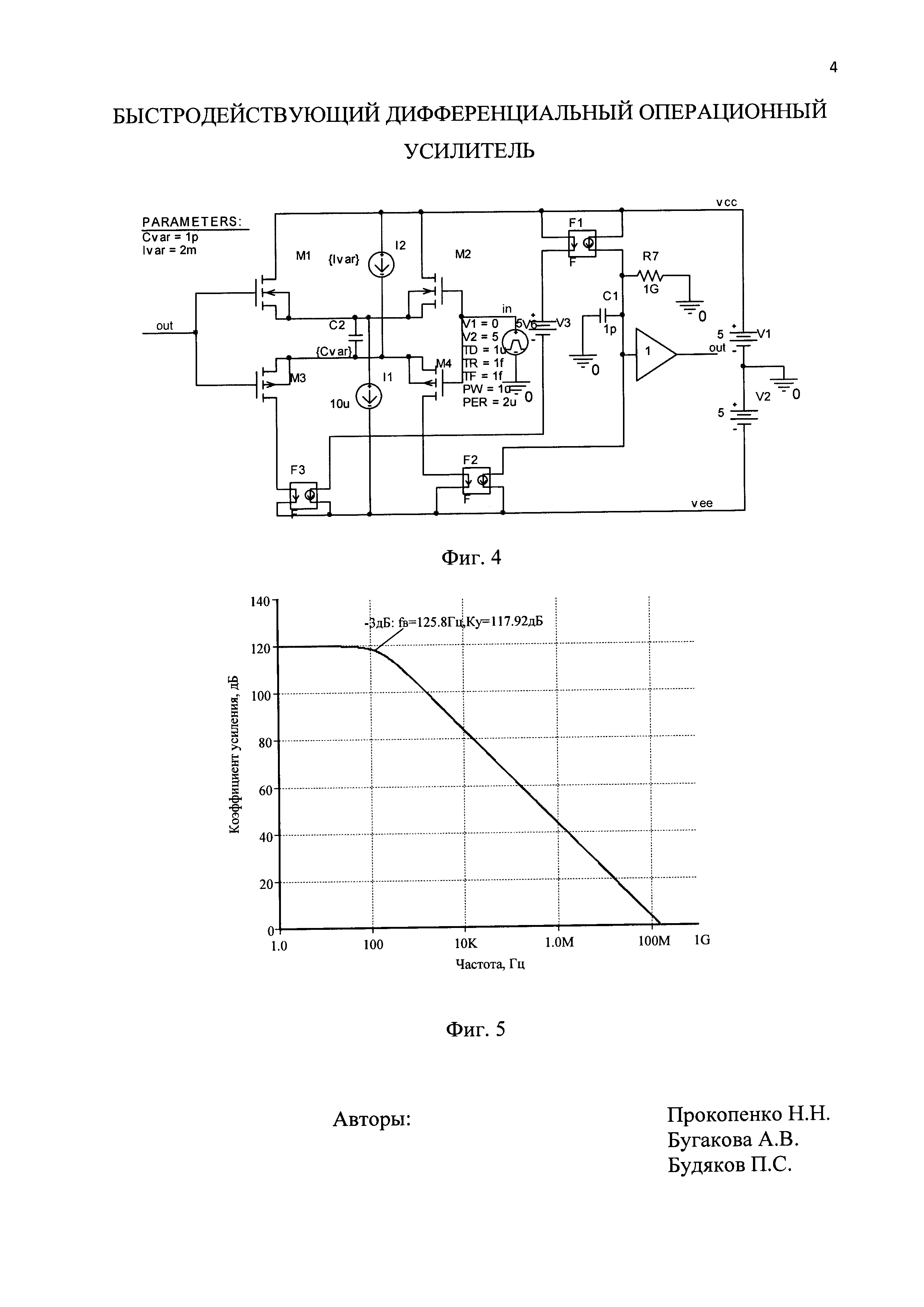

На чертеже фиг. 6 приведены осциллограммы входного и выходного напряжений ОУ фиг. 4 (передний фронт, ширина импульса 6 мкс) при разных значениях емкости C2=C23=Cvar и токах источников I1=I2=Ivar=10 мкА.

На чертеже фиг. 7 показаны осциллограммы входного и выходного напряжений ОУ фиг. 4 (передний фронт) при разных значениях емкости C2=C23=Cvar, I1=I2=Ivar=1 мкА (ширина импульса 6 мкс).

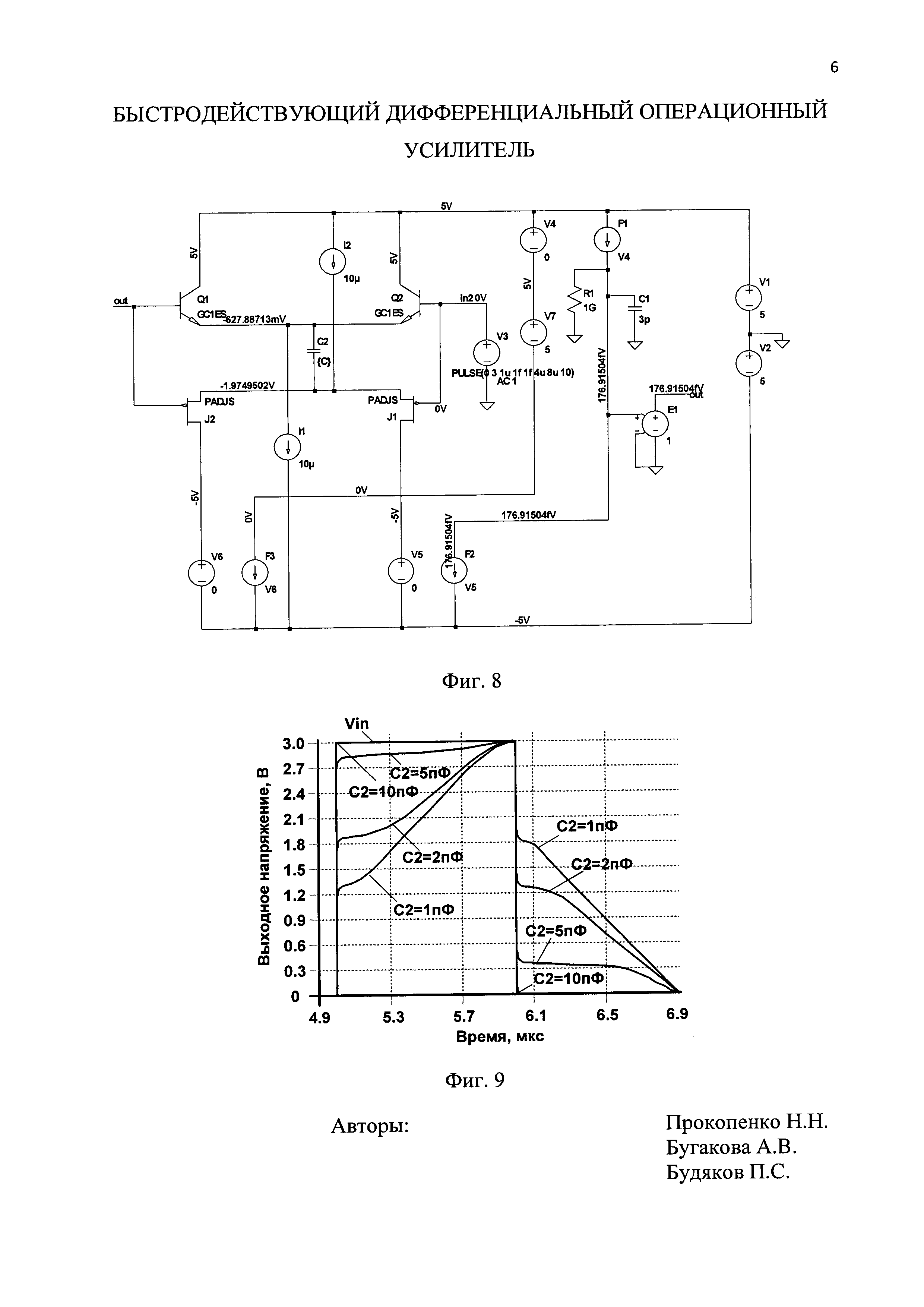

На чертеже фиг. 8 приведена схема BiJFet ОУ фиг. 2 в среде компьютерного моделирования LTSpice, использующей авторские низкотемпературные модели BiJFet транзисторов [12].

На чертеже фиг. 9 представлены осциллограммы входного и выходного напряжений BiJFet ОУ фиг. 8 (передний и задний фронты) при I1=I2=10 мкА, C1=3 пФ и разных емкостях второго 23 корректирующего конденсатора (C2=C23=Cvar) (ширина импульса 1 мкс, амплитуда входного напряжения 3 В, комнатная температура t=27°С).

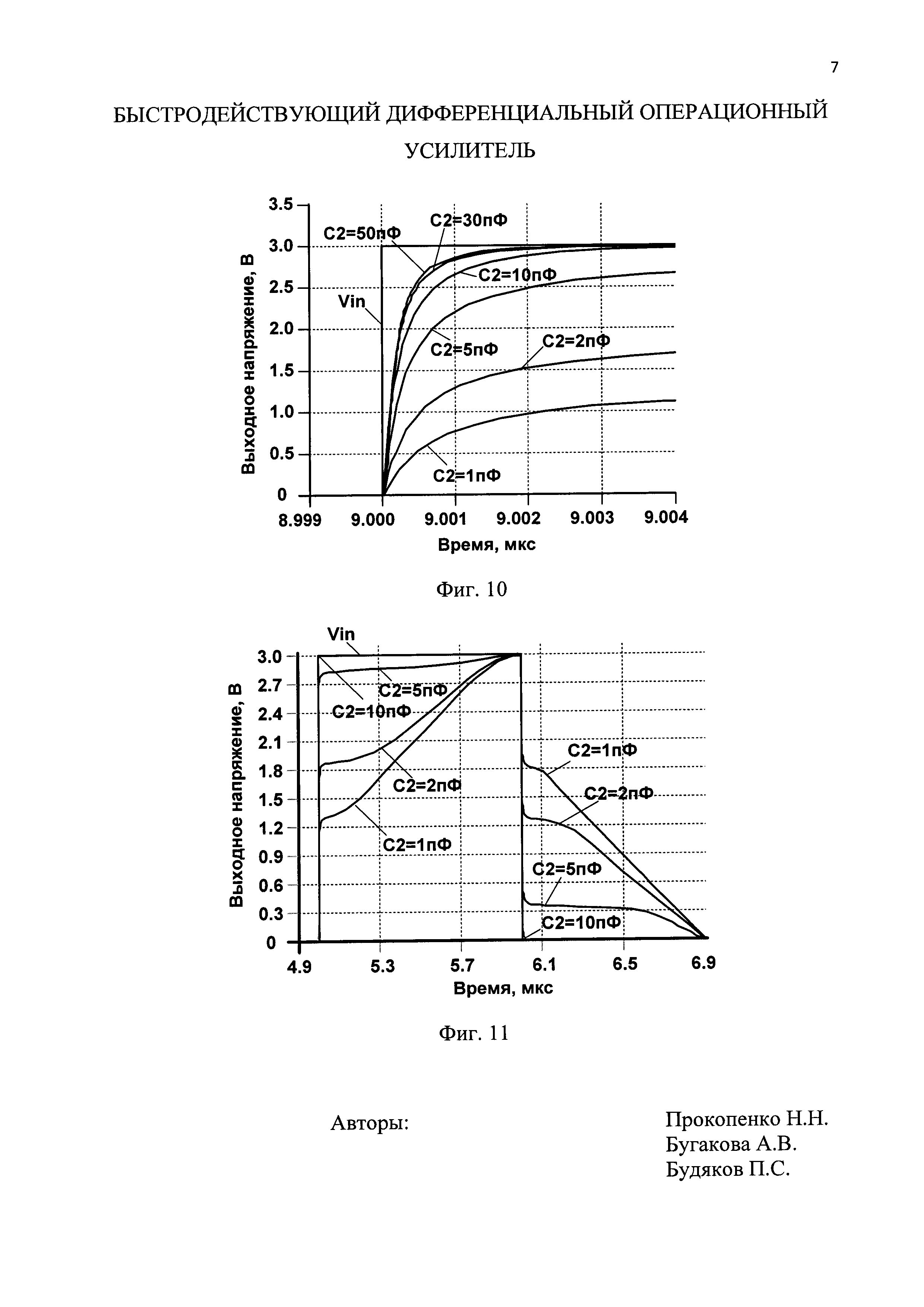

На чертеже фиг. 10 приведены (в увеличенном масштабе) осциллограммы входного и выходного напряжений BiJFet ОУ фиг. 8 (передний фронт) при I1=I2=1 мкА, C1=3 пф и разных емкостях второго 23 корректирующего конденсатора C2=C23=Cvar (ширина импульса 1 мкс, амплитуда входного напряжения 3 В, комнатная температура t=27°С).

На чертеже фиг. 11 показаны осциллограммы входного и выходного напряжений ОУ (передний и задний фронты) при I1=I2=10 мкА, C1=3 пф и разных емкостях второго 23 корректирующего конденсатора C2=C23=Cvar, (ширина импульса I мкс, амплитуда входного напряжения 3 В, низкая температура t=-190°С).

Быстродействующий дифференциальный операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 противофазными токовыми выходами, первый источник опорного тока 6, включенный между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и первой 8 шиной источника питания, первое токовое зеркало 9, согласованное со второй 10 шиной источника питания, вход которого соединен с первым 4 токовом выходом входного дифференциального каскада 1, а выход подключен ко входу второго 11 токового зеркала, согласованного с первой 8 шиной источника питания, третье 12 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого соединен со вторым 5 токовым выходом входного дифференциального каскада 1, а выход связан с выходом второго 11 токового зеркала и входом буферного усилителя 13, корректирующий конденсатор 14, связанный со входом буферного усилителя 13, имеющего потенциальный выход 15. В схему введен дополнительный дифференциальный каскад 16, содержащий первый 17 и второй 18 входы, первый 19 и второй 20 противофазные токовые выходы, согласованные с первой 8 шиной источника питания, вспомогательный вход 21 дополнительного дифференциального каскада 16 для установления его статического режима по току, причем первый 17 вход дополнительного дифференциального каскада 16 связан с первым 2 входом входного дифференциального каскада 1, второй 18 вход дополнительного дифференциального каскада 16 связан со вторым 3 входом входного дифференциального каскада 1, между вспомогательным входом 21 дополнительного дифференциального каскада 16 для установления его статического режима по току и второй 10 шиной источника питания включен второй 22 источник опорного тока, между входом 7 входного дифференциального каскада 1 для установления его статического режима по току и вспомогательным входом 21 дополнительного дифференциального каскада 16 для установления его статического режима по току включен второй 23 корректирующий конденсатор.

На чертеже фиг. 2 первый 2 вход входного дифференциального каскада 1 и первый 17 вход дополнительного дифференциального каскада 16 образуют инвертирующих вход заявляемого ОУ 24, а второй 3 вход входного дифференциального каскада 1 и второй 18 вход дополнительного дифференциального каскада 16 образуют неинвертирующий вход 25 заявляемого ОУ. Цепь согласования потенциалов 26 может включаться в схему ОУ для уменьшения его напряжения смещения нуля, вызванное асимметрией статического режима по напряжению первого 9 и третьего 12 токовых зеркал.

Кроме этого на чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, входной дифференциальный каскад 1 содержит первый 27 и второй 28 полевые транзисторы, объединенные истоки которых подключены ко входу 7 входного дифференциального каскада 1 для установления его статического режима по току, затвор первого 27 полевого транзистора соединен с первым 2 входом входного дифференциального каскада 1, затвор второго 28 полевого транзистора соединен с вторым 3 входом входного дифференциального каскада 1, сток первого 27 полевого транзистора соединен с первым 4 токовом выходом входного дифференциального каскада 1, сток второго 28 полевого транзистора соединен со вторым 5 токовым выходом входного дифференциального каскада 1.

В частном случае на чертеже фиг. 2 дополнительный дифференциальный каскад 16 содержит биполярные транзисторы 29 и 30, связанные с его выводами (17, 18, 19, 20, 21) в соответствии со схемой фиг. 2.

На чертеже фиг. 3 входной дифференциальный каскад 1 реализован на полевых транзисторах 31 и 32. Связи выводов этих транзисторов с первым 2 и вторым 3 входами входного дифференциального каскада 1, а также первым 17 и вторым 18 входами дополнительного дифференциального каскада 16 обозначены на чертеже фиг. 3.

Кроме этого, на чертеже фиг. 3 приведена схема заявляемого устройства в соответствии с п. 3 формулы изобретения, в котором дополнительный дифференциальный каскад 16 содержит третий 33 и четвертый 34 полевые транзисторы, объединенные истоки которых подключены к вспомогательному входу 21 дополнительного дифференциального каскада 16 для установления его статического режима по току, затвор третьего 33 полевого транзистора соединен с первым 17 входом дополнительного дифференциального каскада 16, затвор четвертого 34 полевого транзистора соединен со вторым 18 входом дополнительного дифференциального каскада 16, сток третьего 33 полевого транзистора соединен с первым 19 токовом выходом дополнительного дифференциального каскада 16, сток четвертого 34 полевого транзистора соединен со вторым 20 токовом выходом дополнительного дифференциального каскада 16.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, первый 19 токовый выход дополнительного дифференциального каскада 16 соединен со входом четвертого 35 токового зеркала, согласованного с первой 8 шиной источника питания, выход которого соединен со входом буферного усилителя 13, второй 20 токовый выход дополнительного дифференциального каскада 16 соединен со входом пятого 36 токового зеркала, согласованного с первой 8 шиной источника питания, выход которого соединен со входом шестого 37 токового зеркала, согласованного с второй 10 шиной источника питания, причем выход шестого 37 токового зеркала подключен ко входу буферного усилителя 13.

Рассмотрим работу заявляемого ОУ на примере анализа схемы фиг. 2.

Максимальная скорость нарастания выходного напряжения ОУ фиг. 2 определяется скоростью перезаряда емкости первого 14 корректирующего конденсатора. Так как ток первого 6 источника опорного тока измеряется микроамперами, то и скорость перезаряда первого 14 корректирующего конденсатора будет крайне мала. При введении дополнительных элементов (в соответствии с п. 1 формулы изобретения) скорость перезаряда первого 14 корректирующего конденсатора существенно возрастает. Это объясняется тем, что при положительном «скачке» входного напряжения, поданного на неинвертирующий вход 25 устройства, через второй 23 корректирующий конденсатор формируется сравнительно большой импульс тока, который передается через транзистор 27, первое 9 и второе 11 токовые зеркала в первый 14 корректирующий конденсатор.

Аналогично при отрицательном импульсном сигнале на неинвертирующем входе 25 устройства при 100% отрицательной обратной связи через второй 23 корректирующий конденсатор формируется большой импульс тока, который через транзистор 28 и токовое зеркало 12 поступает в высокоимпедансный узел ∑1 и форсирует процесс перезаряда первого 14 корректирующего конденсатора. В конечном итоге, в предлагаемом ОУ фиг. 2 существенно повышается максимальная скорость выходного напряжения.

Построение ОУ в соответствии с п. 4 формулы изобретения (фиг. 3) обеспечивает более высокие значения максимальной скорости нарастания выходного напряжения в сравнении со схемой фиг. 2. Данный эффект обеспечивается многоканальной передачей токов через второй 23 корректирующий конденсатор в высокоимпедансный узел ∑1, что позволяет более эффективно форсировать процесс перезаряда первого 14 корректирующего конденсатора.

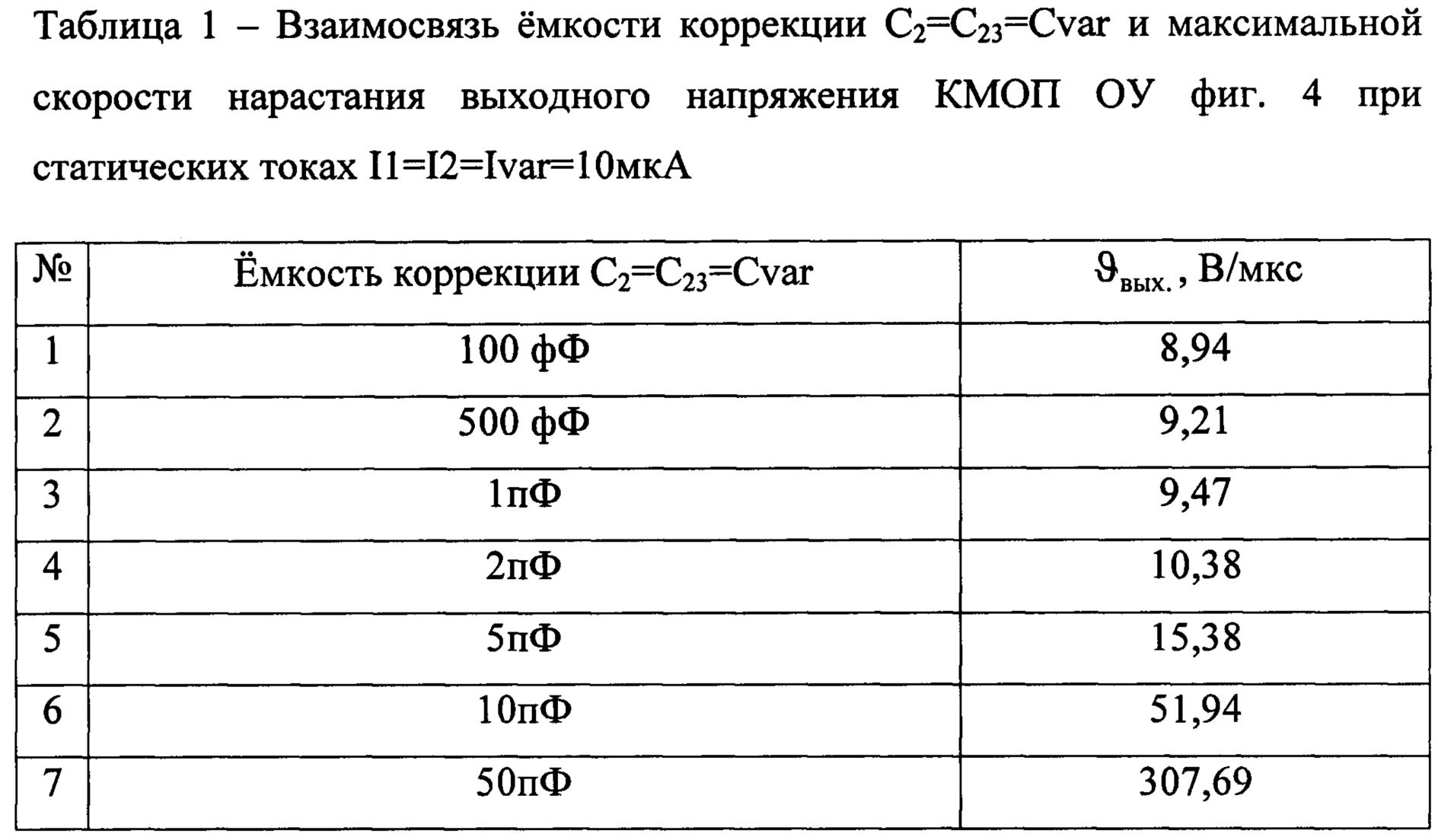

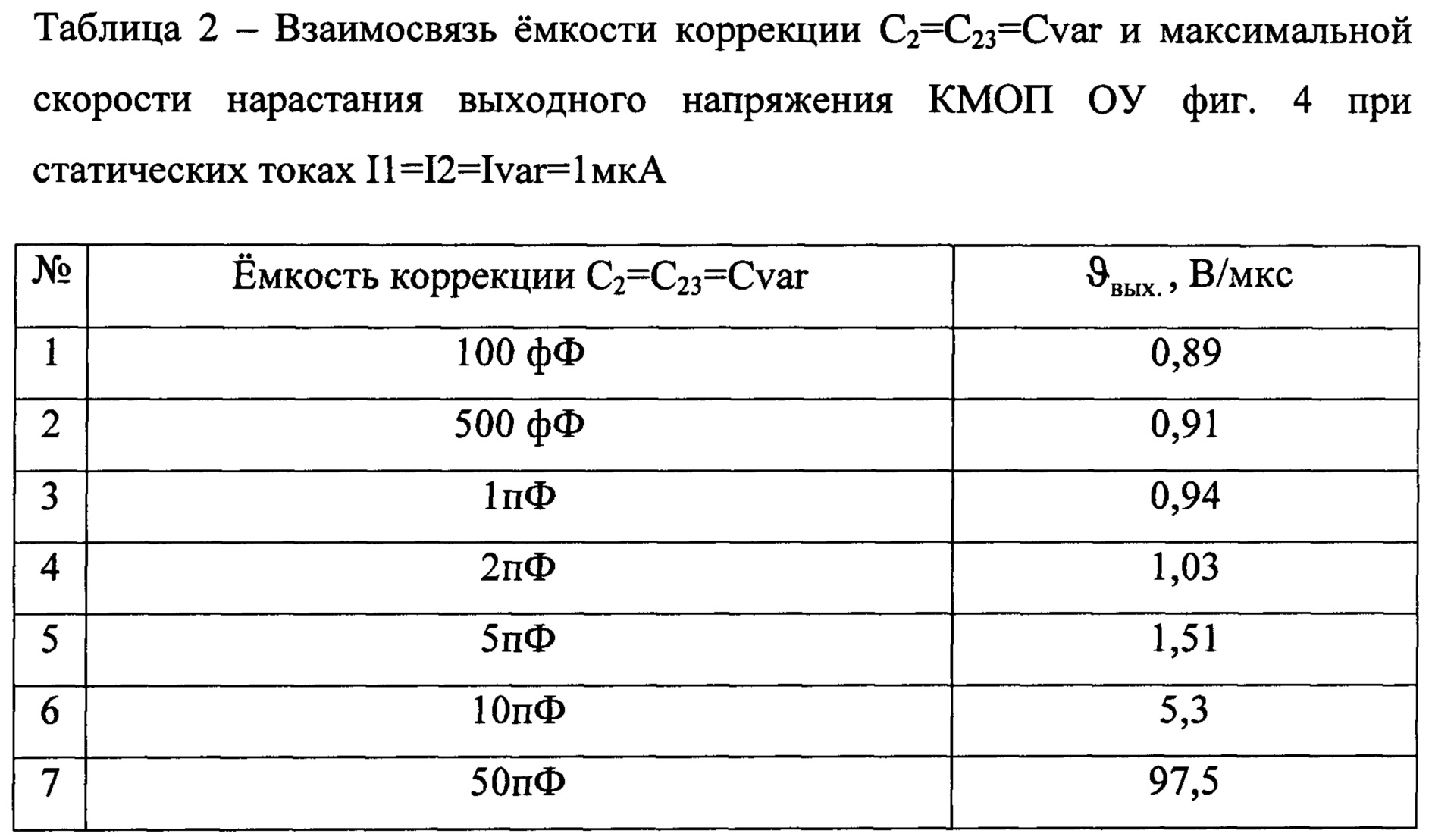

В таблицах 1-2 приведены результаты компьютерного моделирования (фиг. 6, фиг. 7) влияния емкости второго 23 корректирующего конденсатора КМОП ОУ фиг. 4 на максимальную скорость нарастания выходного напряжения при I1=I2=10 мкА и С1=3 пФ (табл. 1), а также I1=I2=1 мкА и С1=3 пФ (табл. 2).

Анализ данных таблиц 1-2 показывает, что быстродействие заявляемого ОУ фиг. 4 при работе его КМОП входных транзисторов в микрорежиме повышается (в сравнении с прототипом) более чем в 30 раз (при I1=I2=10 мкА) и более чем в 100 раз (при I1=I2=1 мкА).

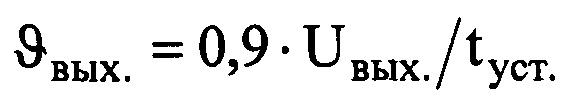

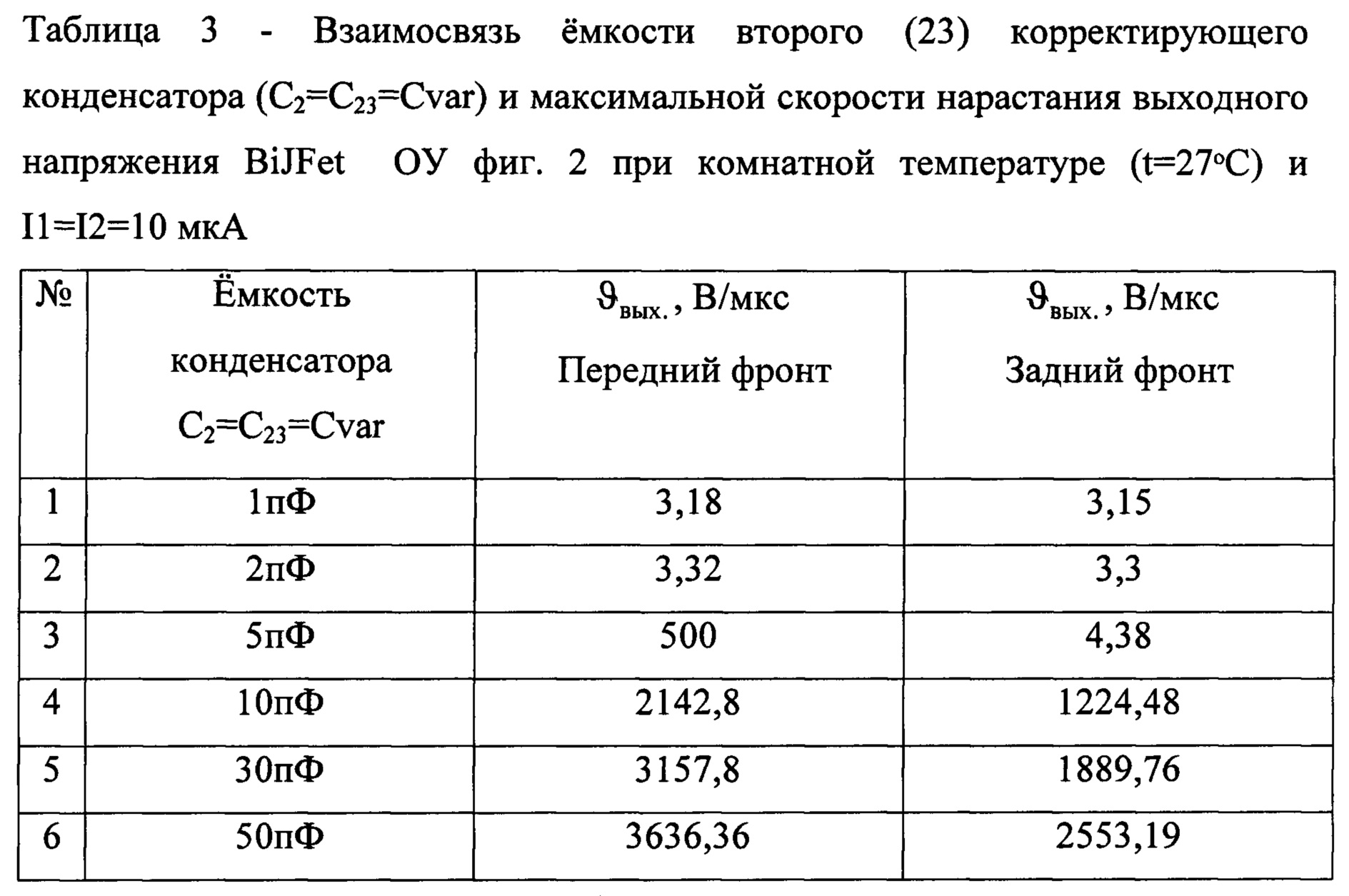

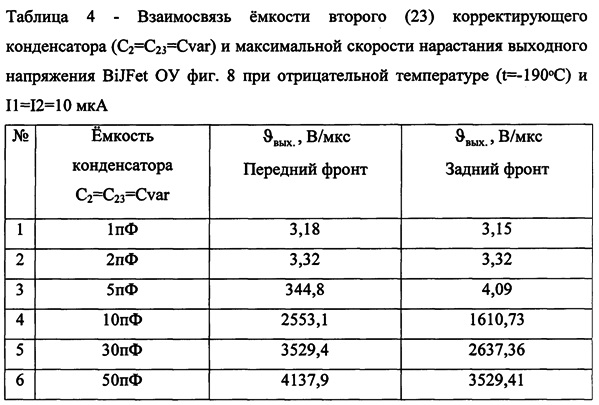

В таблицах 3-4 приведены результаты компьютерного моделирования (фиг. 9 - фиг. 11) влияния емкости второго 23 корректирующего конденсатора BiJFet ОУ фиг. 8 (С23=С2) на максимальную скорость нарастания выходного напряжения при I1=I2=10 мкА, C1=C14=3 пф (t=27°С, табл. 3) и (t=-190°С, табл. 4). При этом среднее значение ϑвых. определяется по формуле  , где tуст. - время установления переходного процесса, Uвых. - выходное напряжение ОУ.

, где tуст. - время установления переходного процесса, Uвых. - выходное напряжение ОУ.

Анализ таблиц 3-4 показывает, что быстродействие заявляемого ОУ для BiJFet технологического процесса (фиг. 8) при работе его входных транзисторов в микрорежиме повышается на 3 порядка. Причем, низкие температуры (-190°С) не оказывают существенного влияния на ϑвых, что обусловлено особенностями схемотехники заявляемого ОУ и BiJFet технологическим процессом ОАО «Интеграл» (г. Минск).

Таким образом, заявляемое устройство обладает существенными преимуществами по сравнению с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 7,701,291, фиг. 1

2. Заявка на патент US 2010/0253433, фиг. 1

3. Патент US 6,138,363

4. Патент US 6,750,714, фиг. 1

5. Патент US 4,843,341

6. Заявка на патент US 2010/0085790

7. Заявка на патент US 2009/0058529

8. Патент ЕР 2472723

9. Заявка на патент US 2005/0218983, фиг. 1

10. Микросхема Операционного усилителя 1427УД1

(http://ic-info.ru/upload/iblock/203/1427%D0%A3%D0%941.pdf)

11. Микросхема Операционного усилителя NE5517

(http://www.onsemi.ru.com/PowerSolutions/document/NE5517-D.PDF)

12. The Accounting of the Simultaneous Exposure of the Low Temperatures and the Penetrating Radiation at the Circuit Simulation of the BiJFET Analog Interfaces of the Sensors / O.V. Dvornikov, V.L. Dziatlau, N.N. Prokopenko, K.O. Petrosiants, N.V. Kozhukhov, V.A. Tchekhovski // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 29-30.06.17 DOI: 10.1109/SIBCON.2017.7998507 .