Результат интеллектуальной деятельности: ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ИДЕНТИФИКАЦИИ ИНСТРУКЦИЙ ДЛЯ УДАЛЕНИЯ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ С ИЗМЕНЕНИЕМ ПОСЛЕДОВАТЕЛЬНОСТИ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Настоящее изобретение относится к области логики обработки информации, микропроцессорам и ассоциированной с ними архитектуре набора команд, которые при выполнении процессором или другой логической схемой обработки информации, выполняют логические, математические или другие функциональные операции.

Уровень техники

Многопроцессорные системы становятся все более и более распространенным явлением. Способ применения многопроцессорных систем включает в себя динамический домен, структурируя вплоть до настольных компьютеров. Для того чтобы воспользоваться преимуществами многопроцессорных систем, код потока, подлежащий выполнению, может быть разделен посредством планировщиков на множество потоков для выполнения посредством различных устройств обработки. Каждый поток может быть обработан параллельно с другим потоком. Более того, чтобы увеличить функциональность устройства обработки может быть использован способ выполнения с изменением последовательности команд. Способ выполнения с изменением последовательности команд может выполнять инструкции, когда необходимо обеспечить доступность ввода таких инструкций. Таким образом, инструкция, которая появляется позже в кодовой последовательности, может быть выполнена перед инструкцией, появляющейся ранее в кодовой последовательности.

Краткое описание чертежей

Варианты осуществления проиллюстрированы в качестве примера, и не ограничены на прилагаемых чертежах:

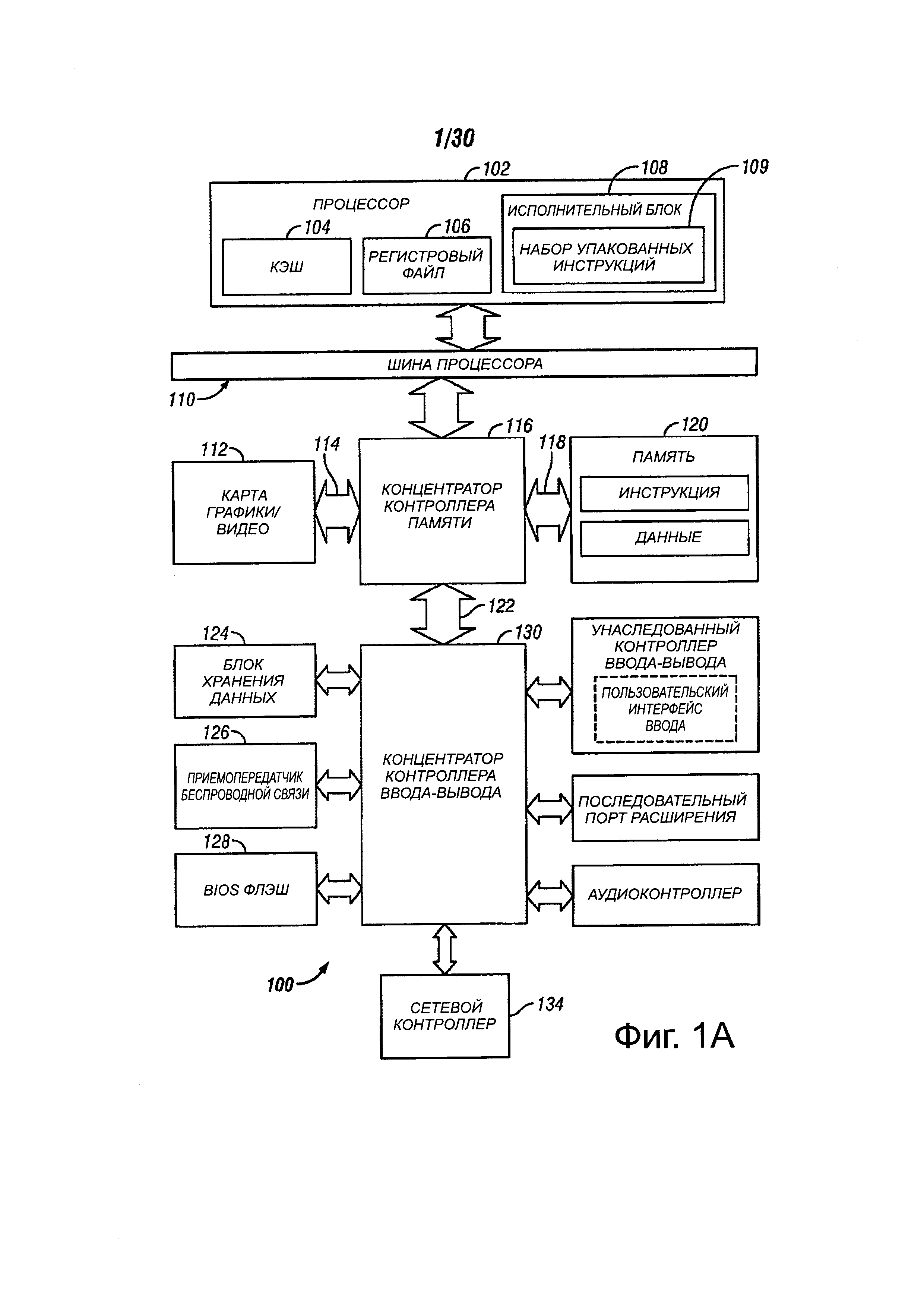

Фиг. 1А показывает блок-схему иллюстративной компьютерной системы, сформированной процессором, который может включать в себя исполнительные блоки для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения;

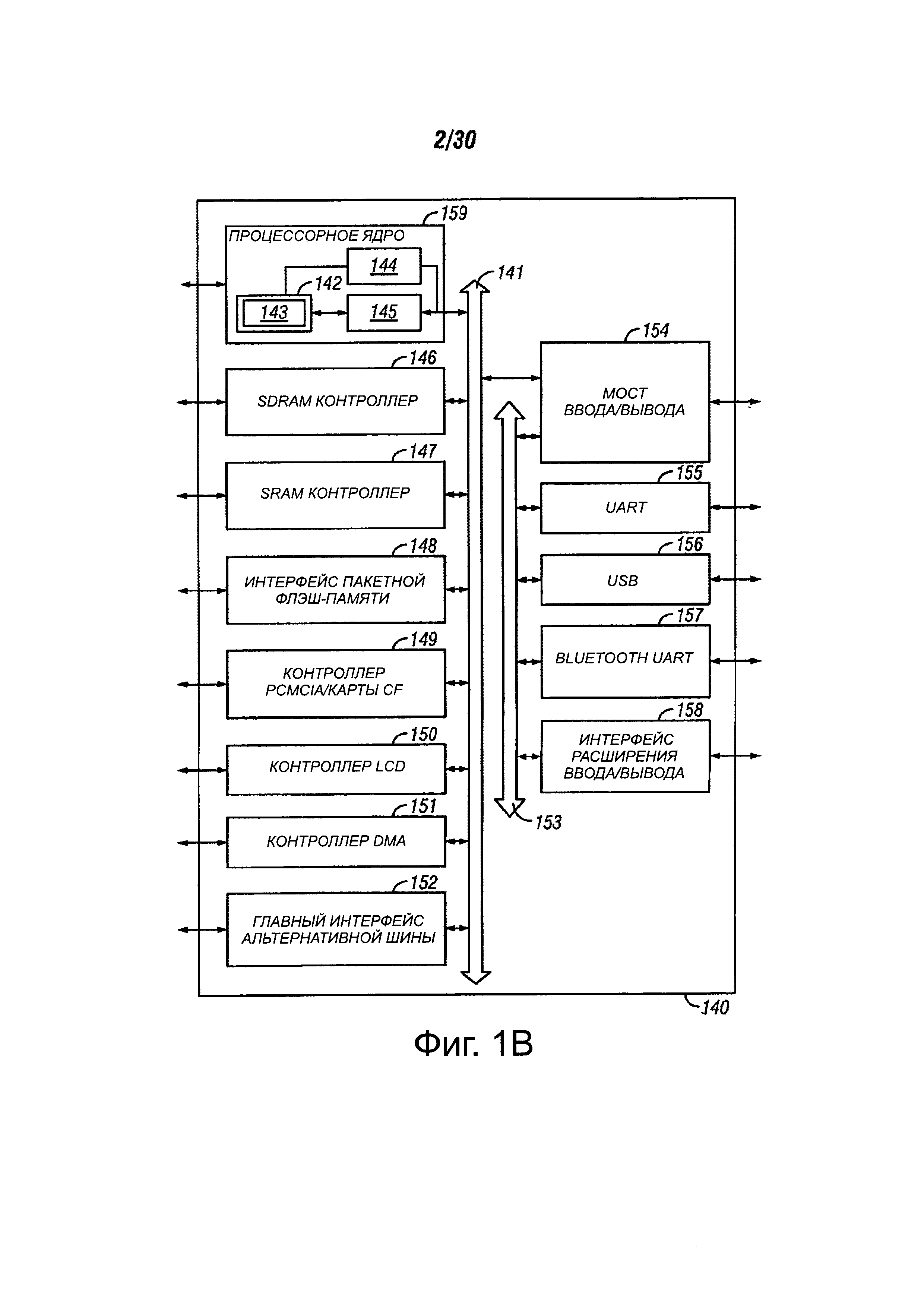

Фиг. 1B иллюстрирует систему обработки данных в соответствии с вариантами осуществления настоящего изобретения;

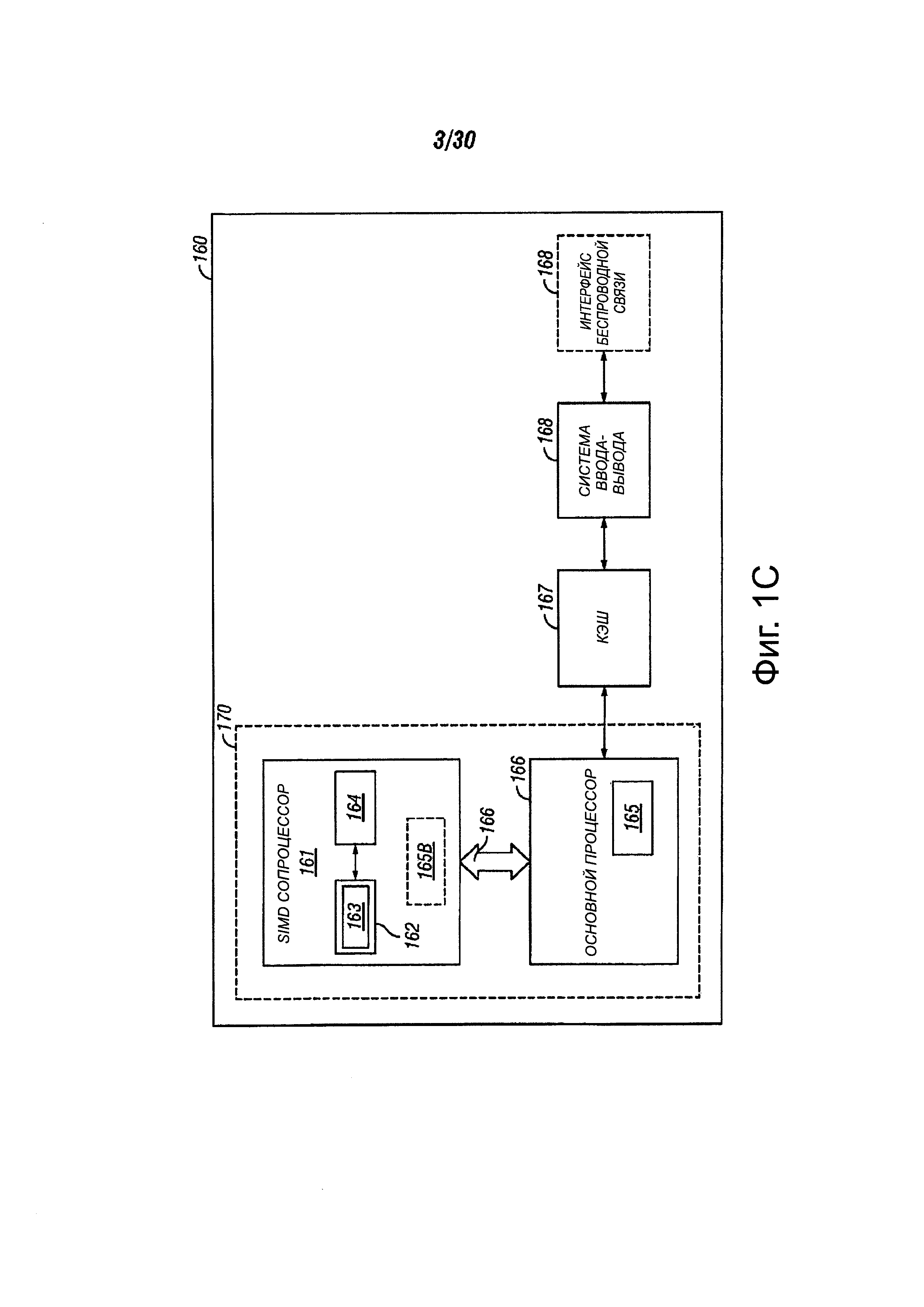

Фиг. 1С иллюстрирует другие варианты осуществления системы обработки данных для выполнения операций сравнения текстовой строки;

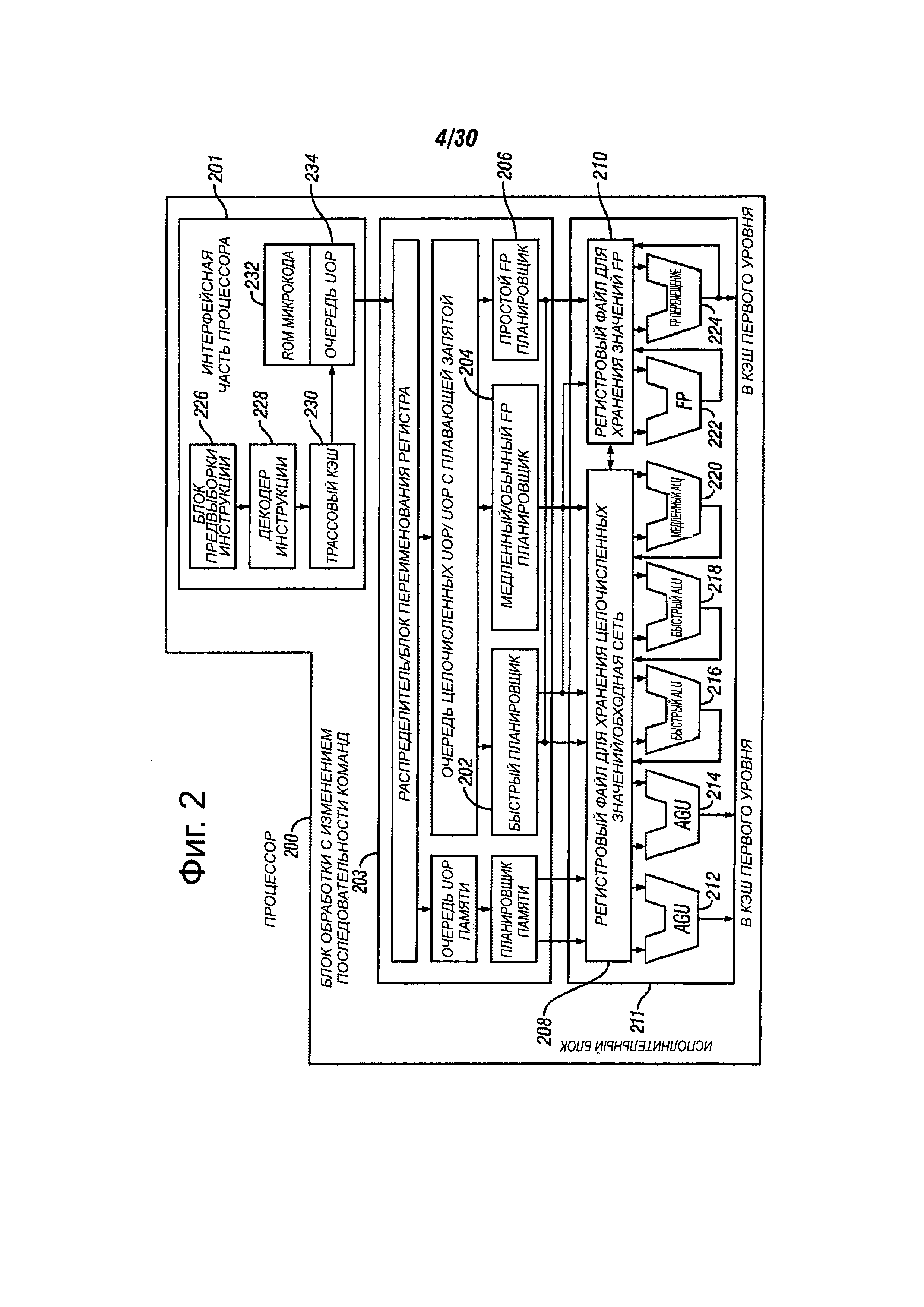

Фиг. 2 показывает блок-схему микроархитектуры для процессора, который может включать в себя логические схемы для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения;

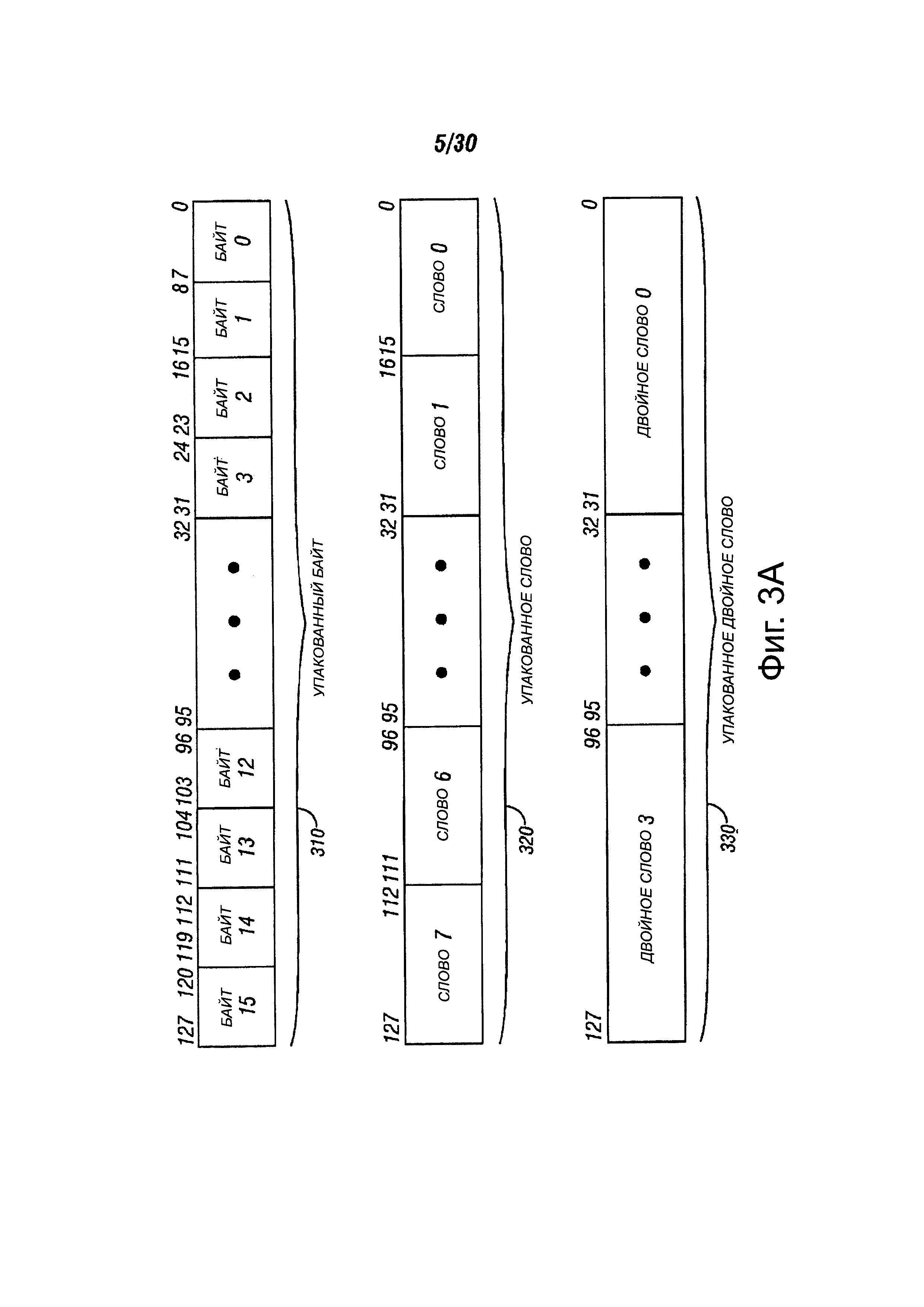

Фиг. 3A иллюстрирует различные представления типа упакованных данных в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

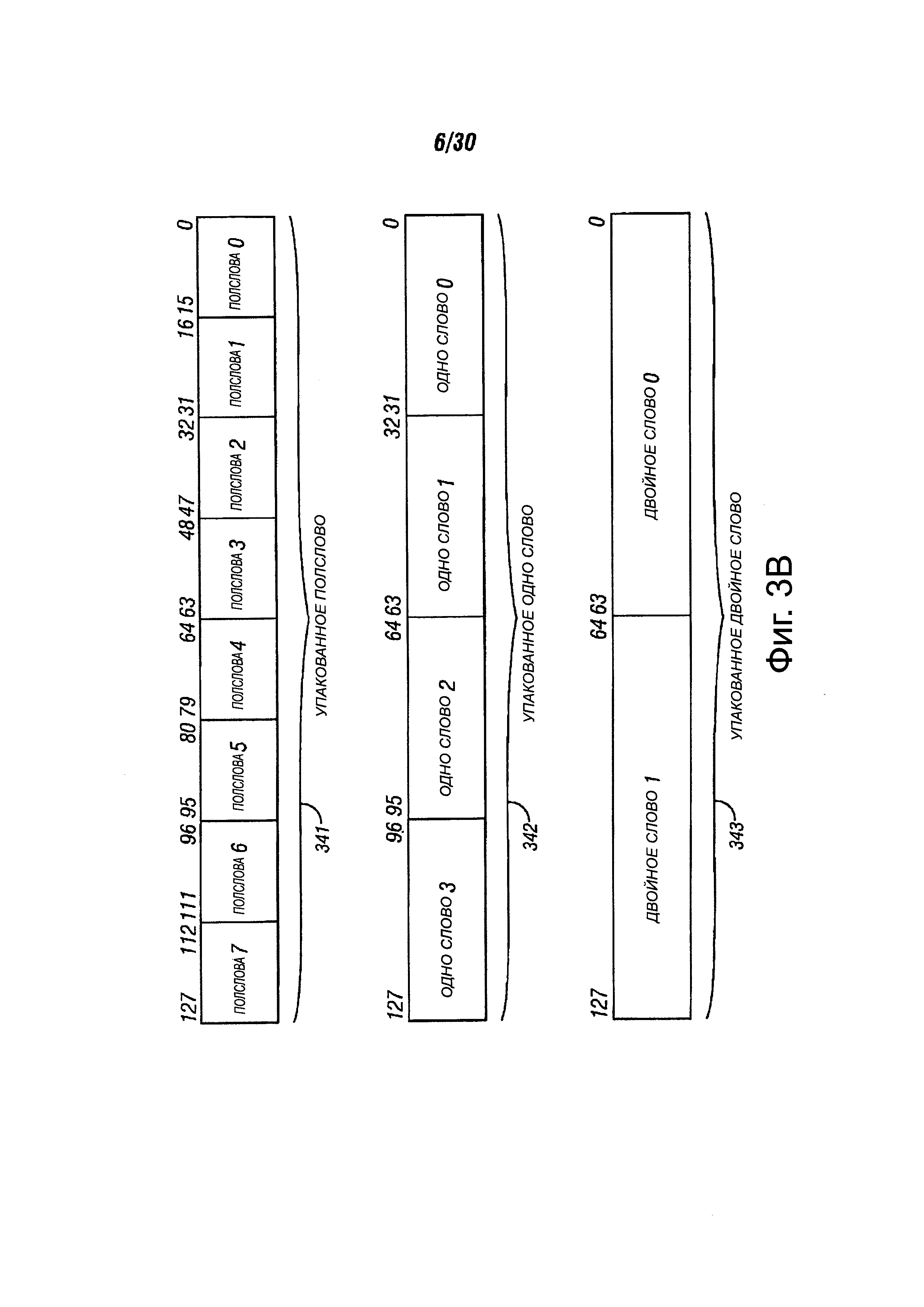

Фиг. 3B иллюстрирует возможные форматы хранения данных в регистре, в соответствии с вариантами осуществления настоящего изобретения;

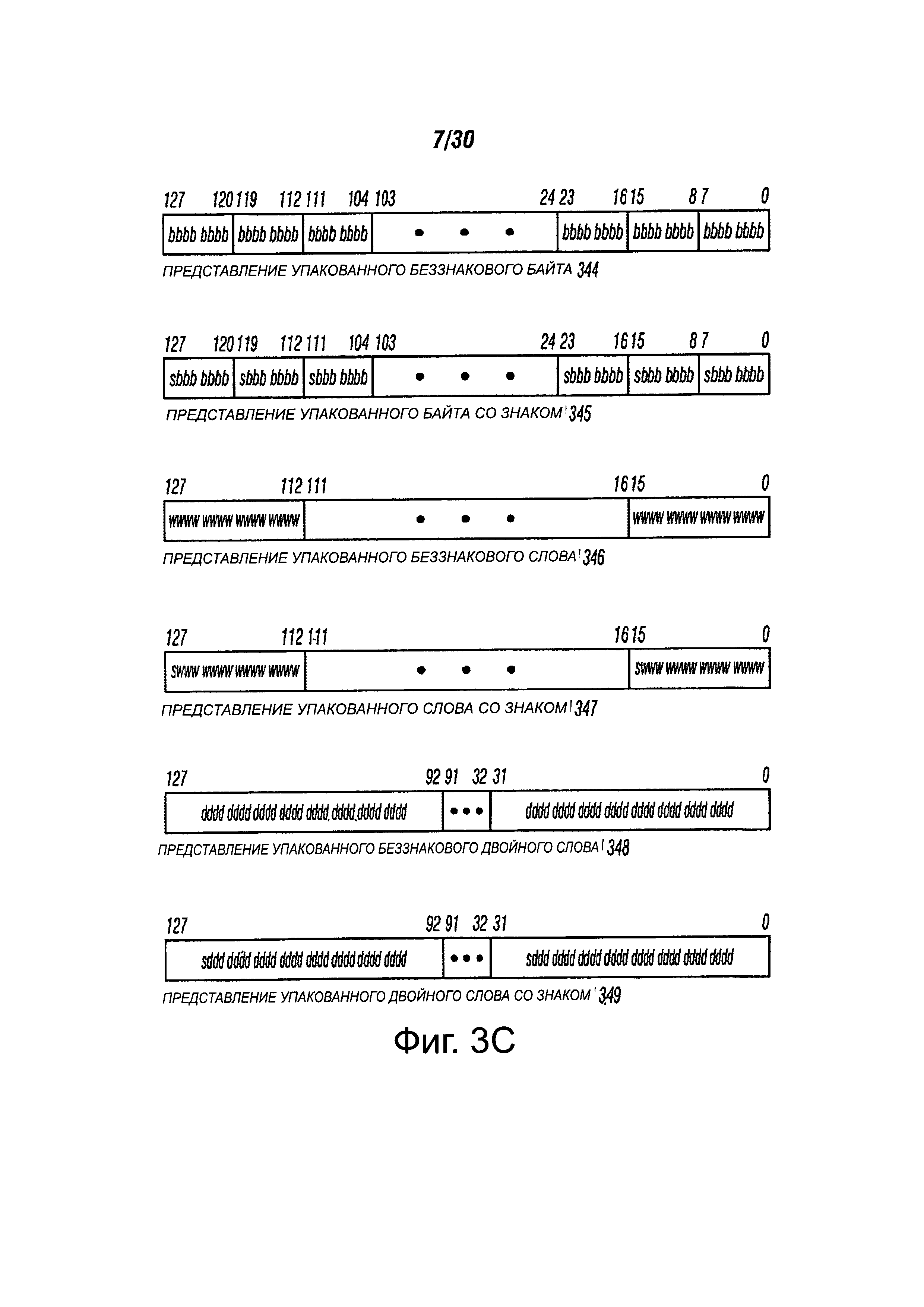

Фиг. 3C показывает различные представления типов упакованных данных со знаком и беззнаковые в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

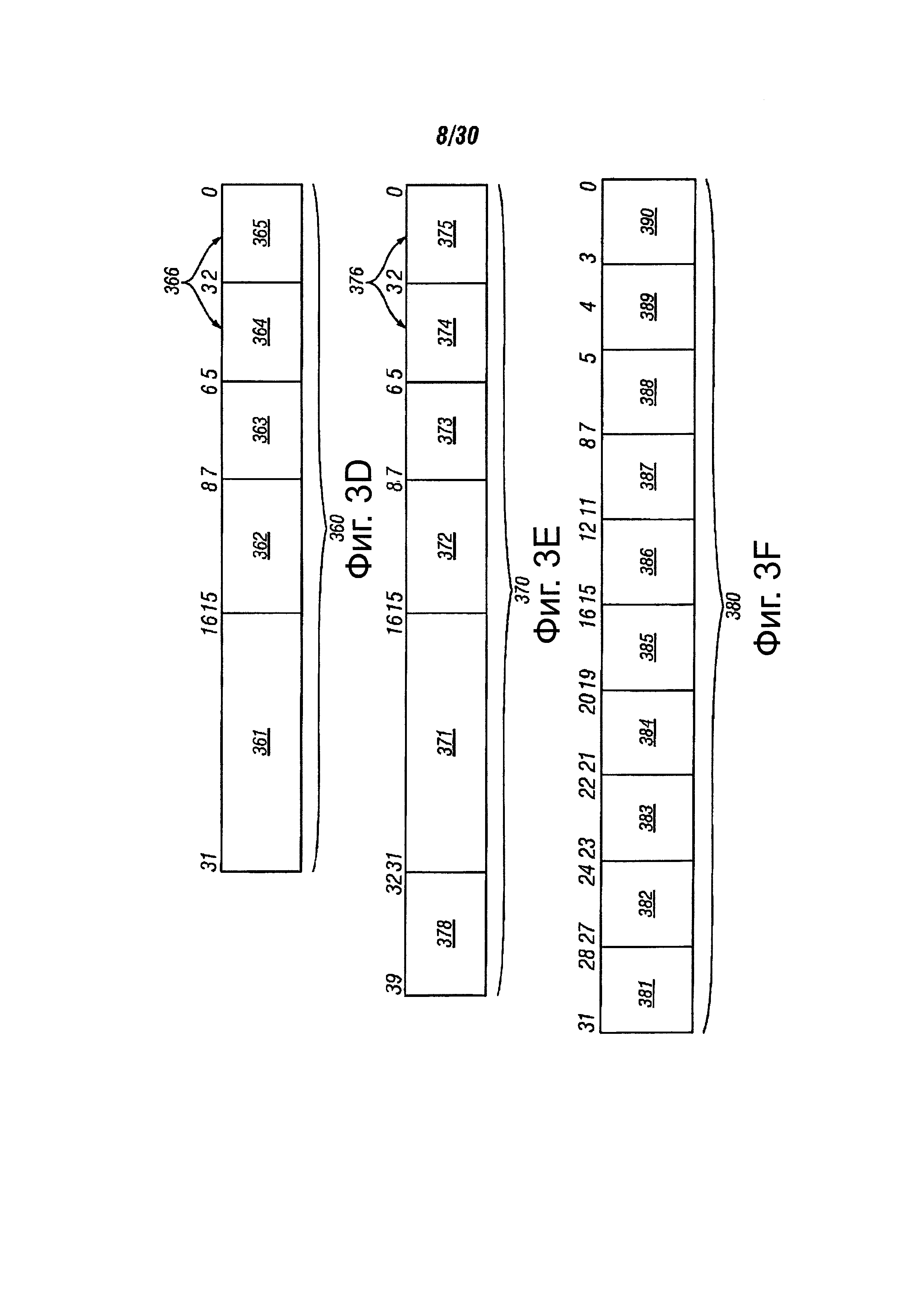

Фиг. 3D показывает вариант осуществления формата кодирования операции;

Фиг. 3E показывает другой возможный формат кодирования операции, имеющий сорок или больше битов, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 3F иллюстрирует еще один возможный формат кодирования операции, в соответствии с вариантами осуществления настоящего изобретения;

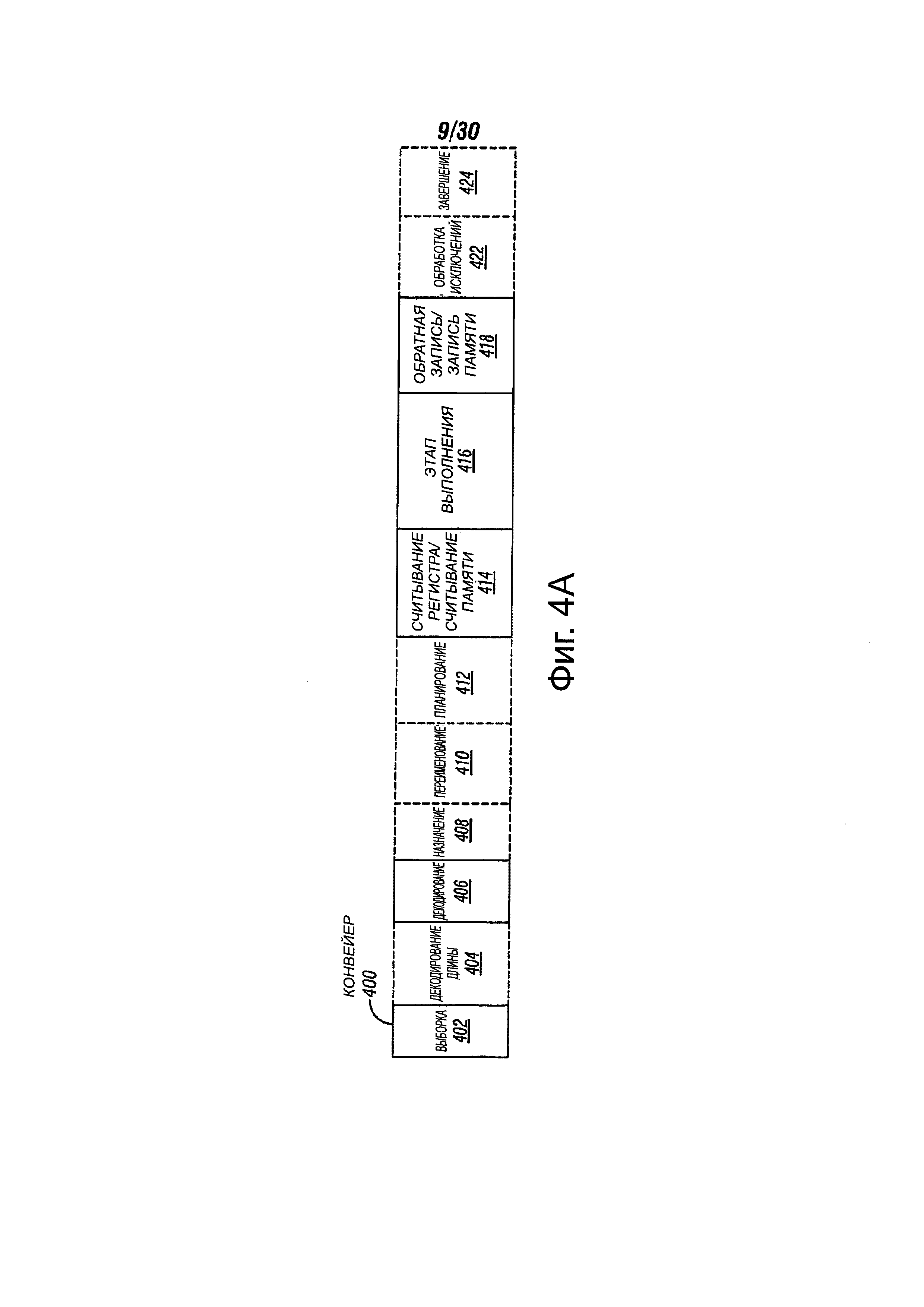

Фиг. 4А представляет собой блок-схему, иллюстрирующую упорядоченный конвейер и этап переименования регистра, конвейер с изменением последовательности команд, в соответствии с вариантами осуществления настоящего изобретения;

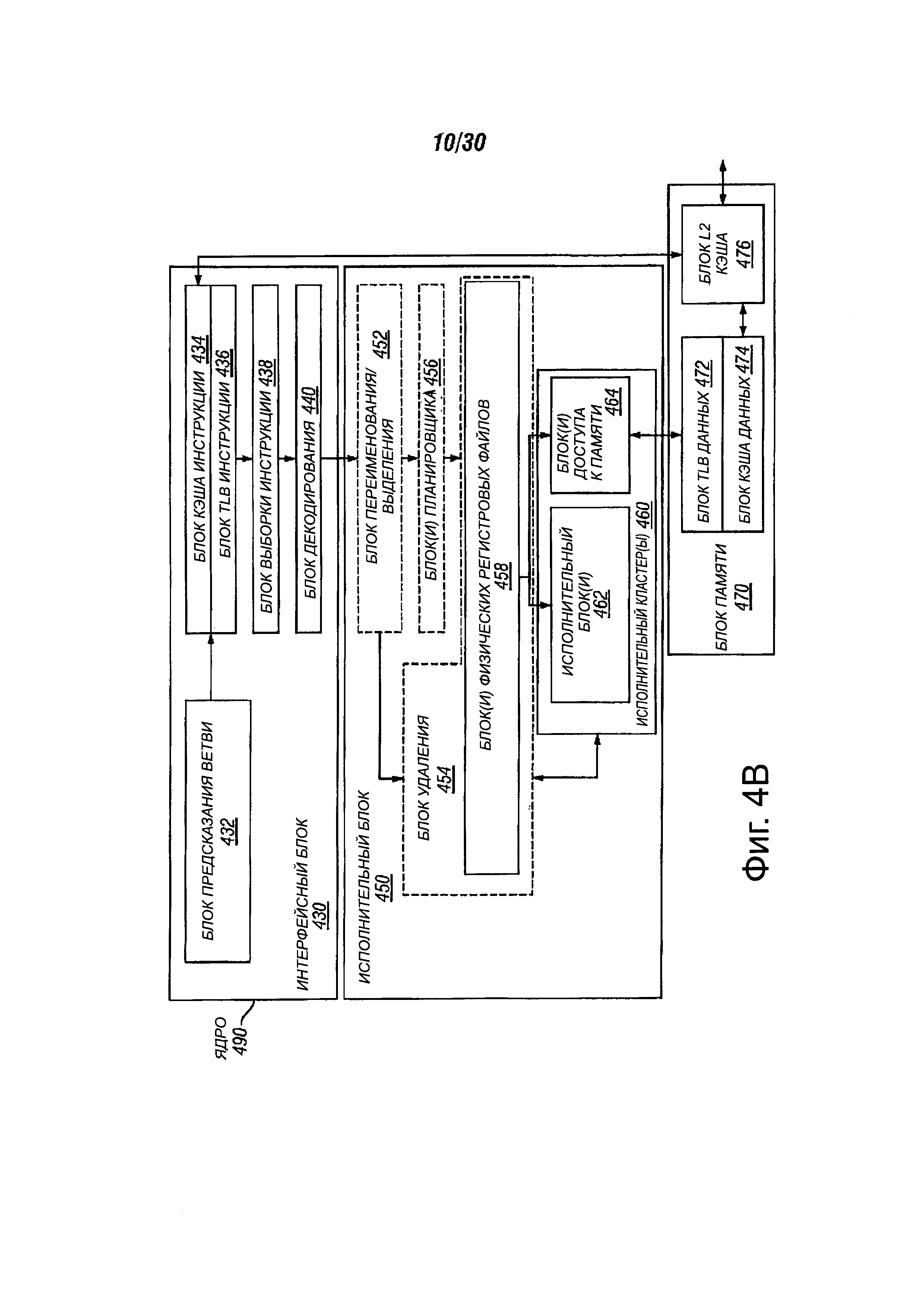

Фиг. 4B показывает блок-схему, иллюстрирующую упорядоченную архитектуру ядра и логику переименования регистров, логику с изменением последовательности команд, включенную в состав процессора, в соответствии с вариантами осуществления настоящего изобретения;

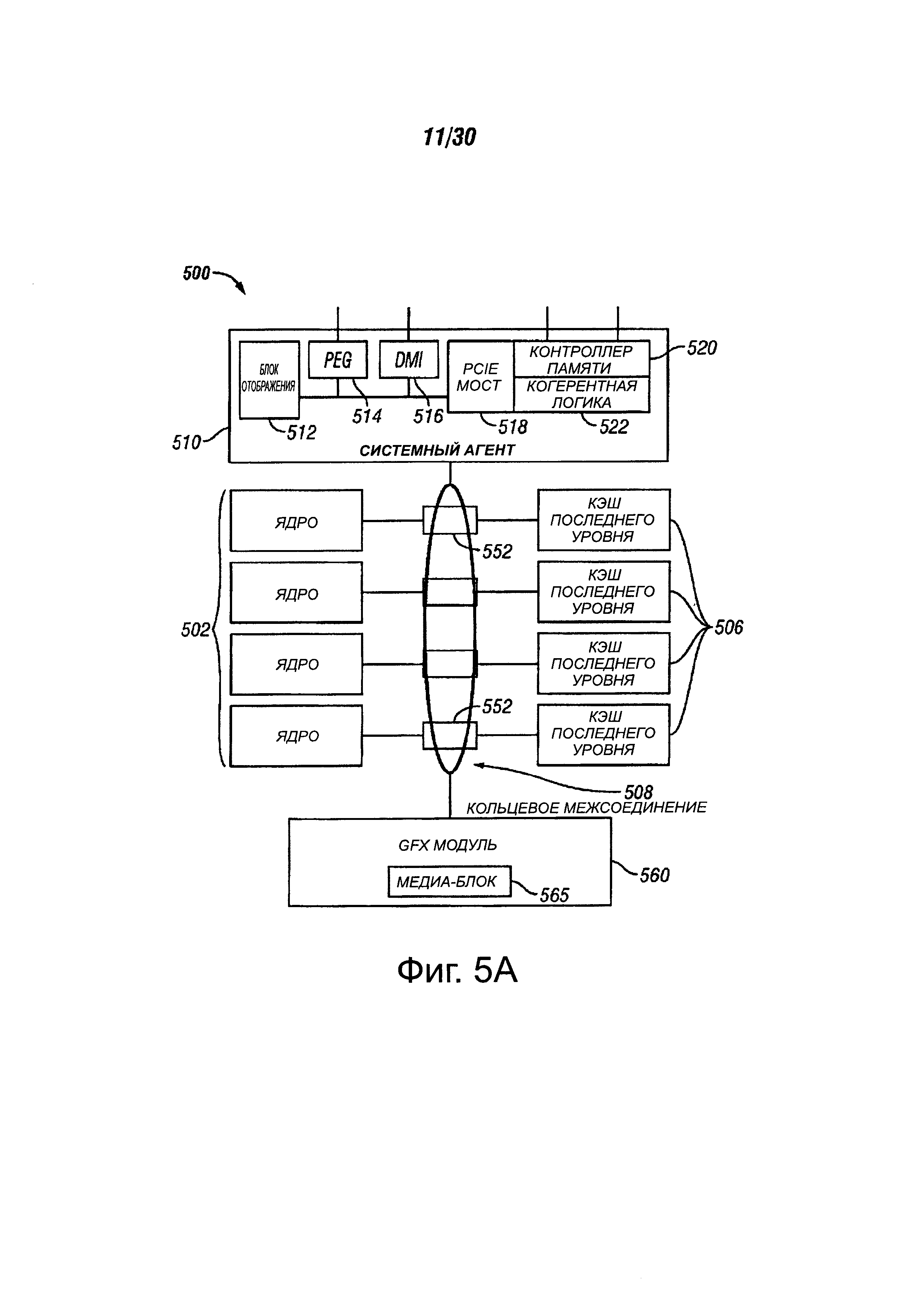

Фиг. 5А показывает блок-схему процессора, в соответствии с вариантами осуществления настоящего изобретения;

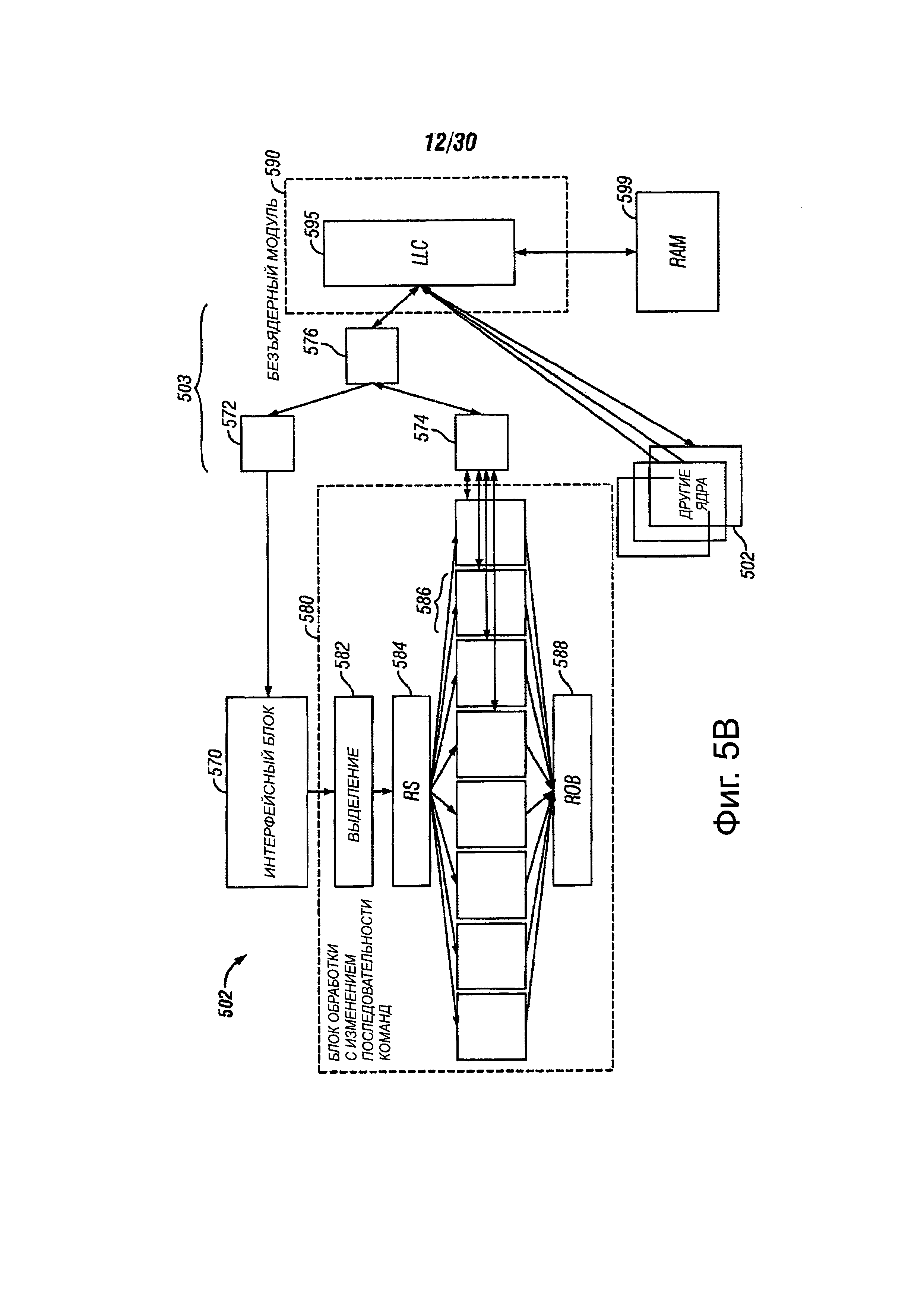

Фиг. 5B показывает блок-схему примерной реализации ядра, в соответствии с вариантами осуществления настоящего изобретения;

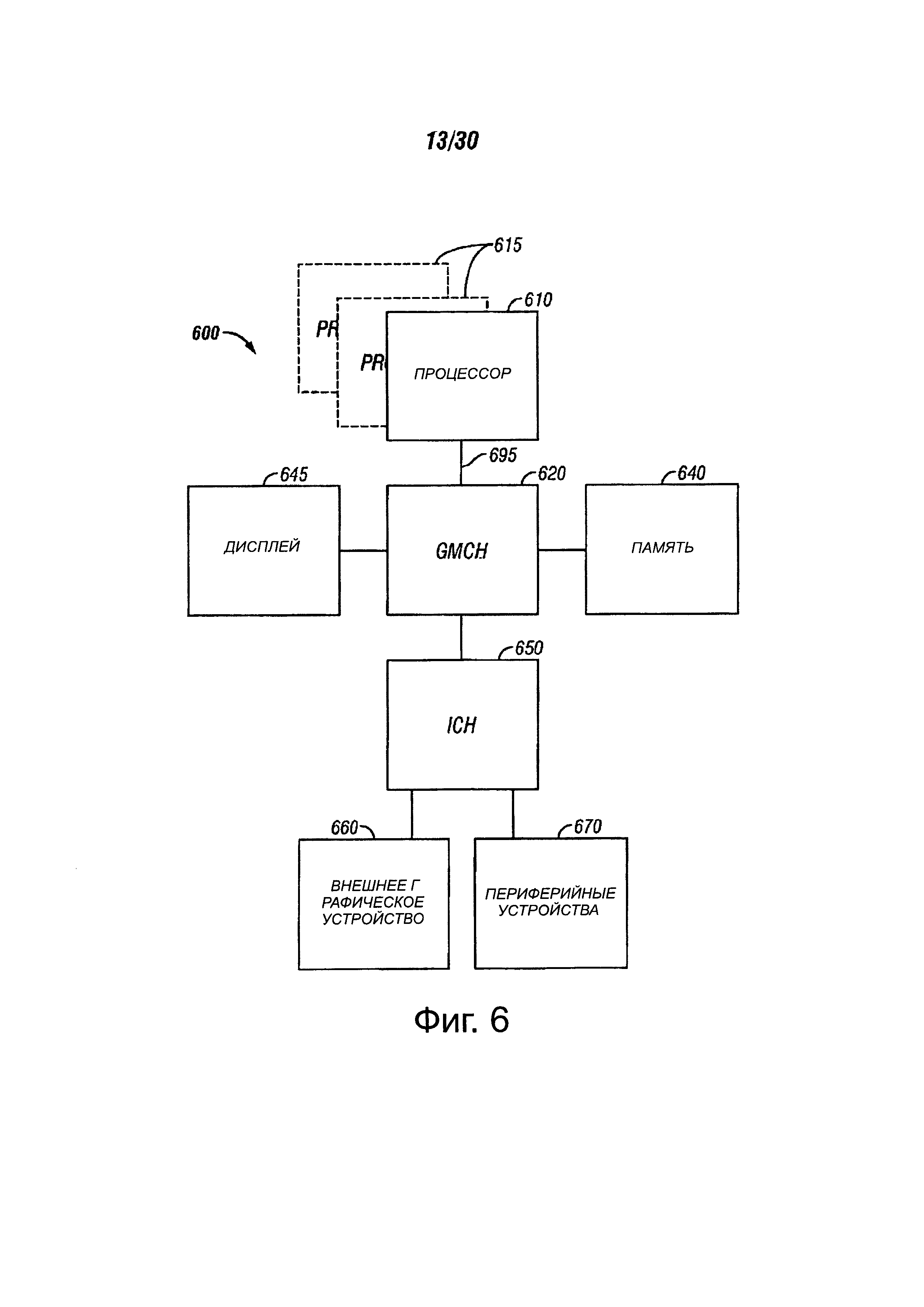

Фиг. 6 показывает блок-схему системы, в соответствии с вариантами осуществления настоящего изобретения;

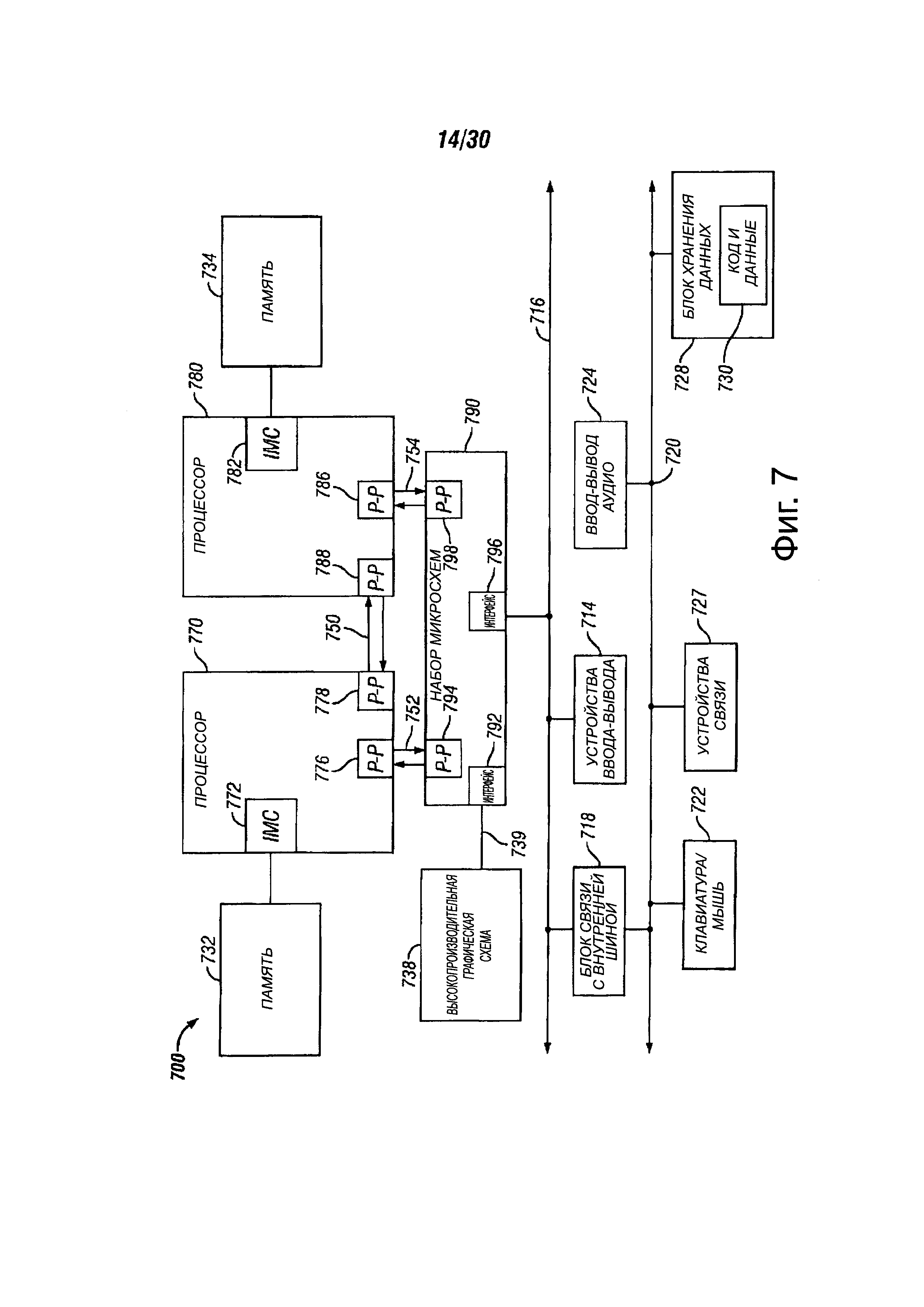

Фиг. 7 показывает блок-схему второй системы, в соответствии с вариантами осуществления настоящего изобретения;

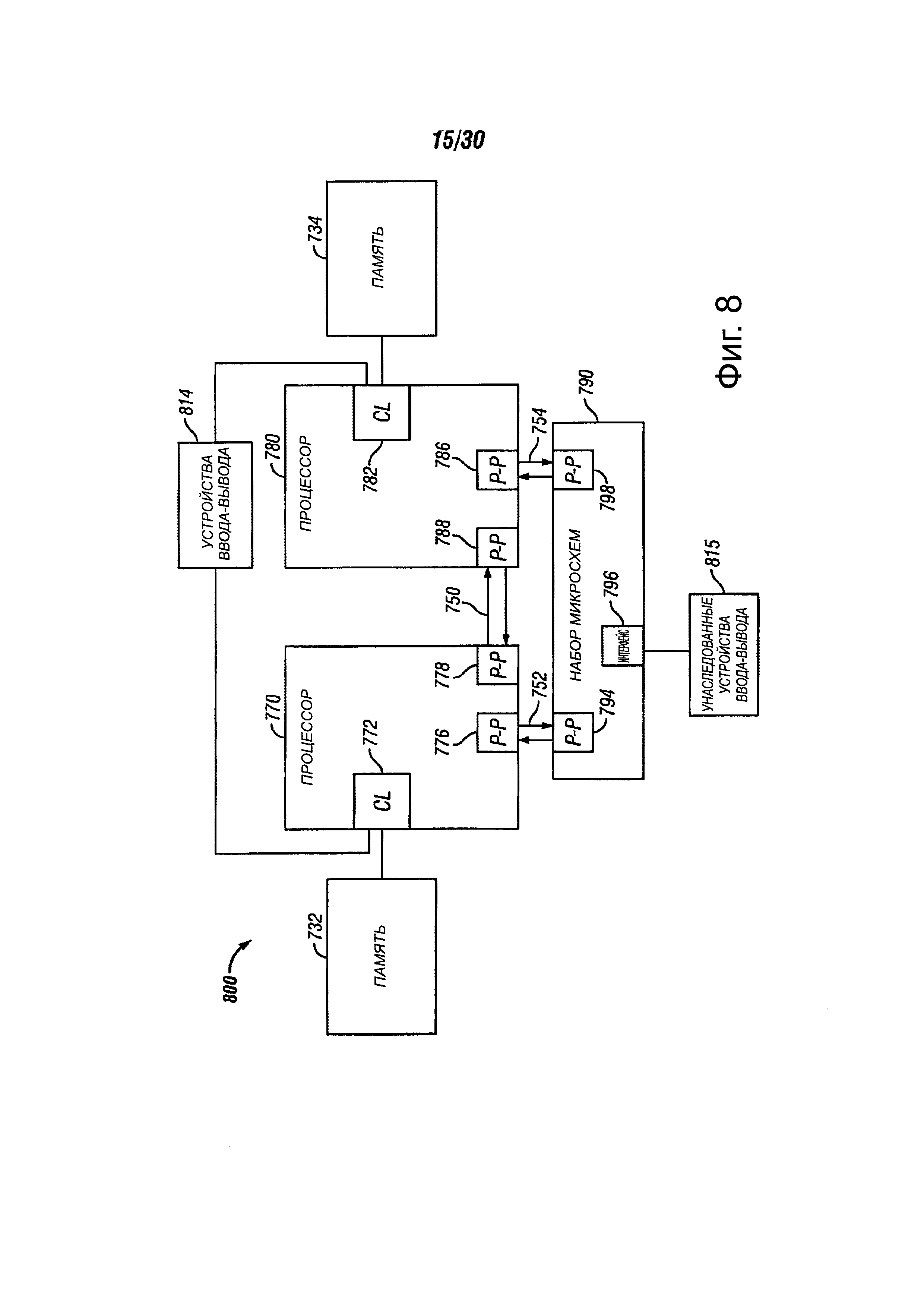

Фиг. 8 показывает блок-схему третьей системы в соответствии с вариантами осуществления настоящего изобретения;

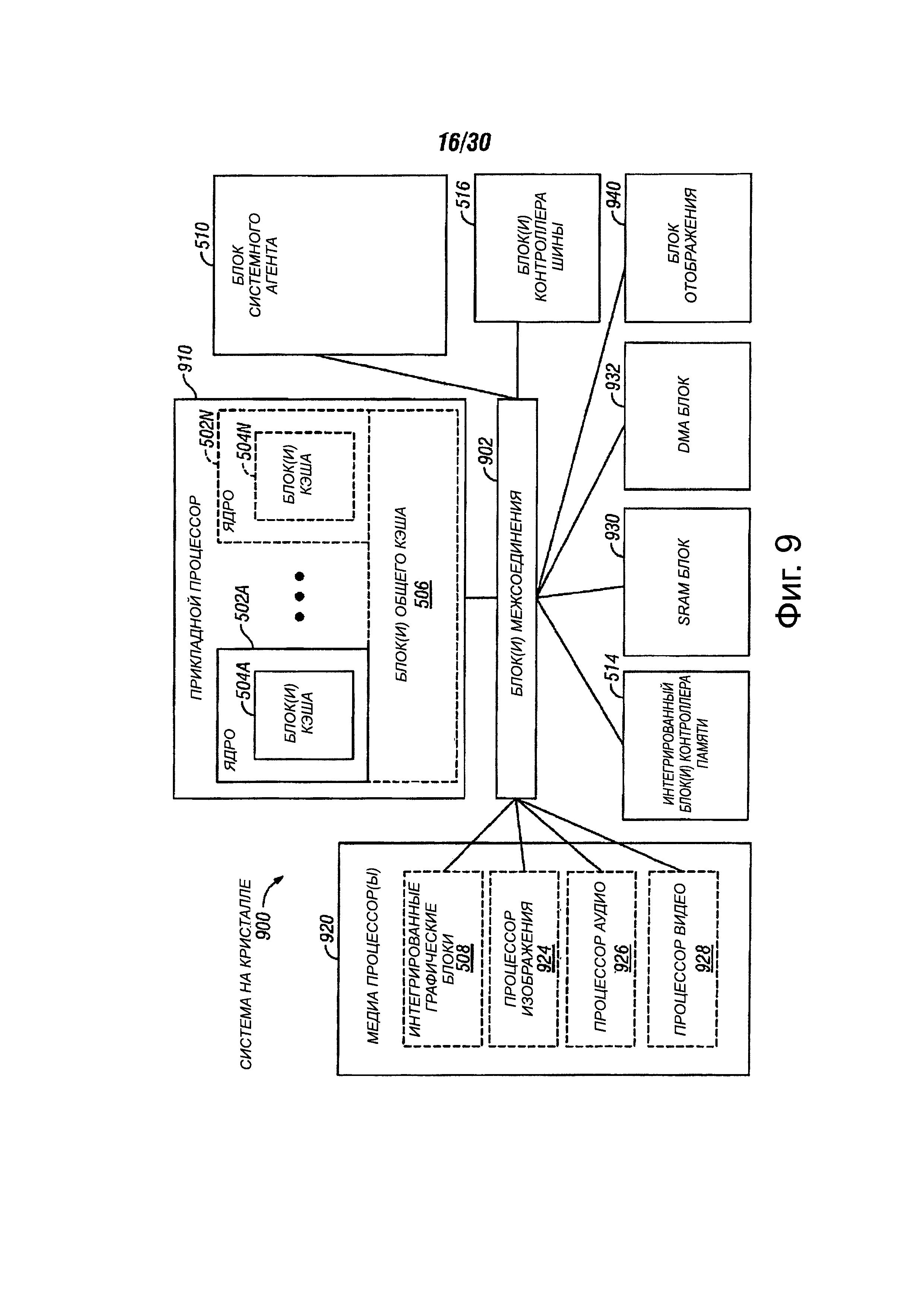

Фиг. 9 показывает блок-схему системы-на-кристалле, в соответствии с вариантами осуществления настоящего изобретения;

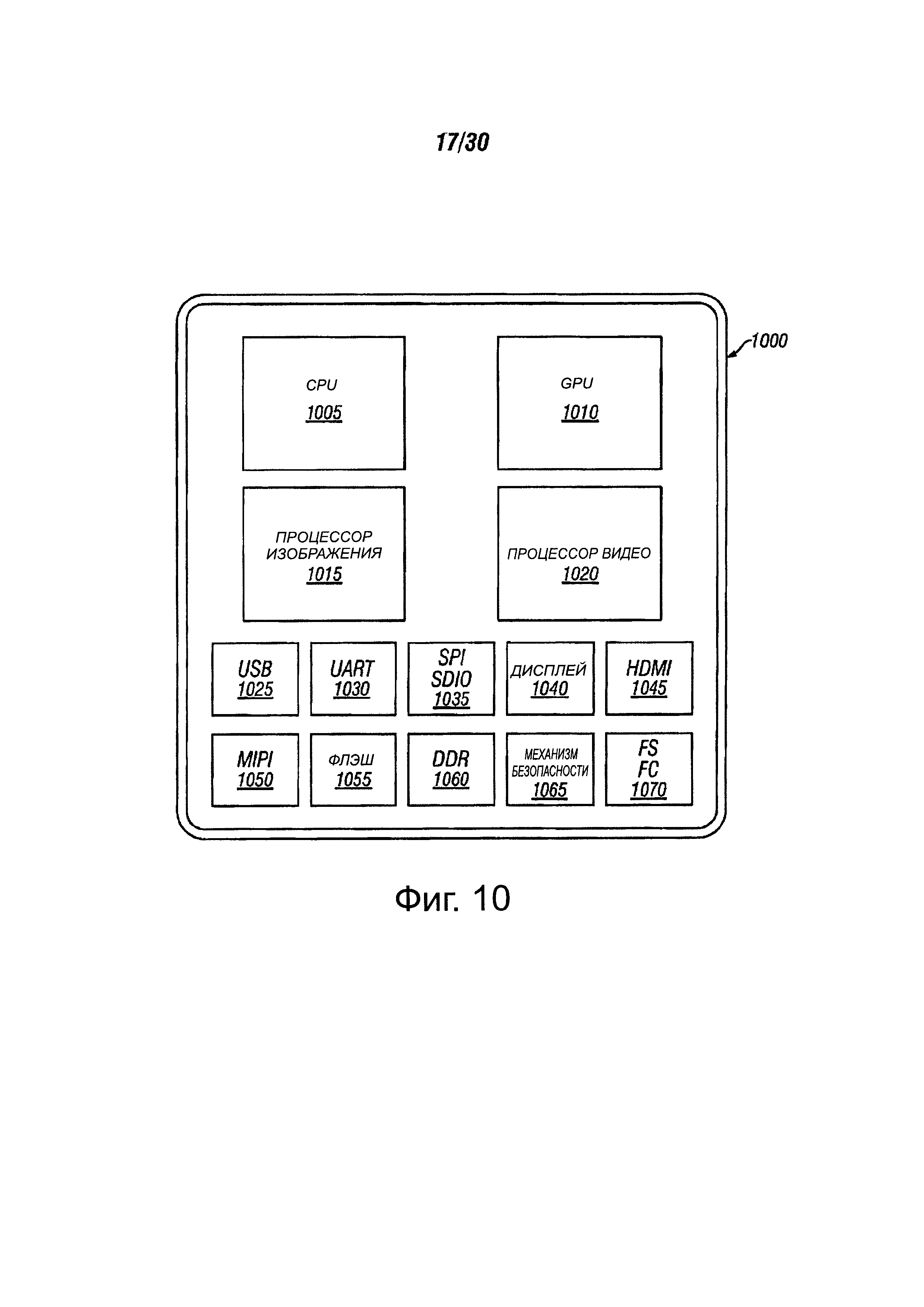

Фиг. 10 показывает процессор, содержащий центральный блок обработки и блок обработки графики, который может выполнять, по меньшей мере, одну инструкцию, в соответствии с вариантами осуществления настоящего изобретения;

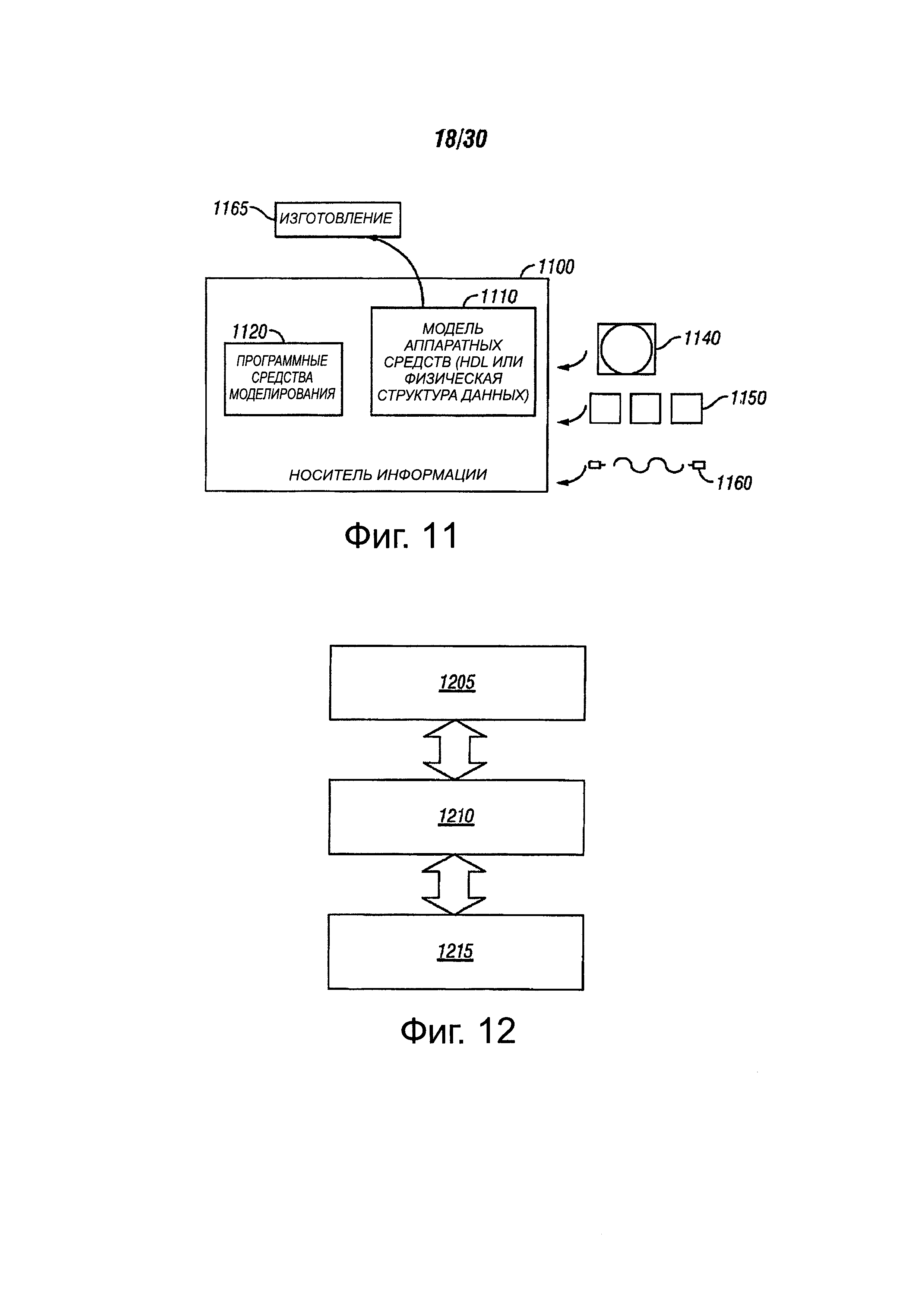

Фиг. 11 показывает блок-схему, иллюстрирующую разработку IP ядер, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 12 показывает, как инструкция первого типа может быть эмулирована процессором другого типа, в соответствии с вариантами осуществления настоящего изобретения;

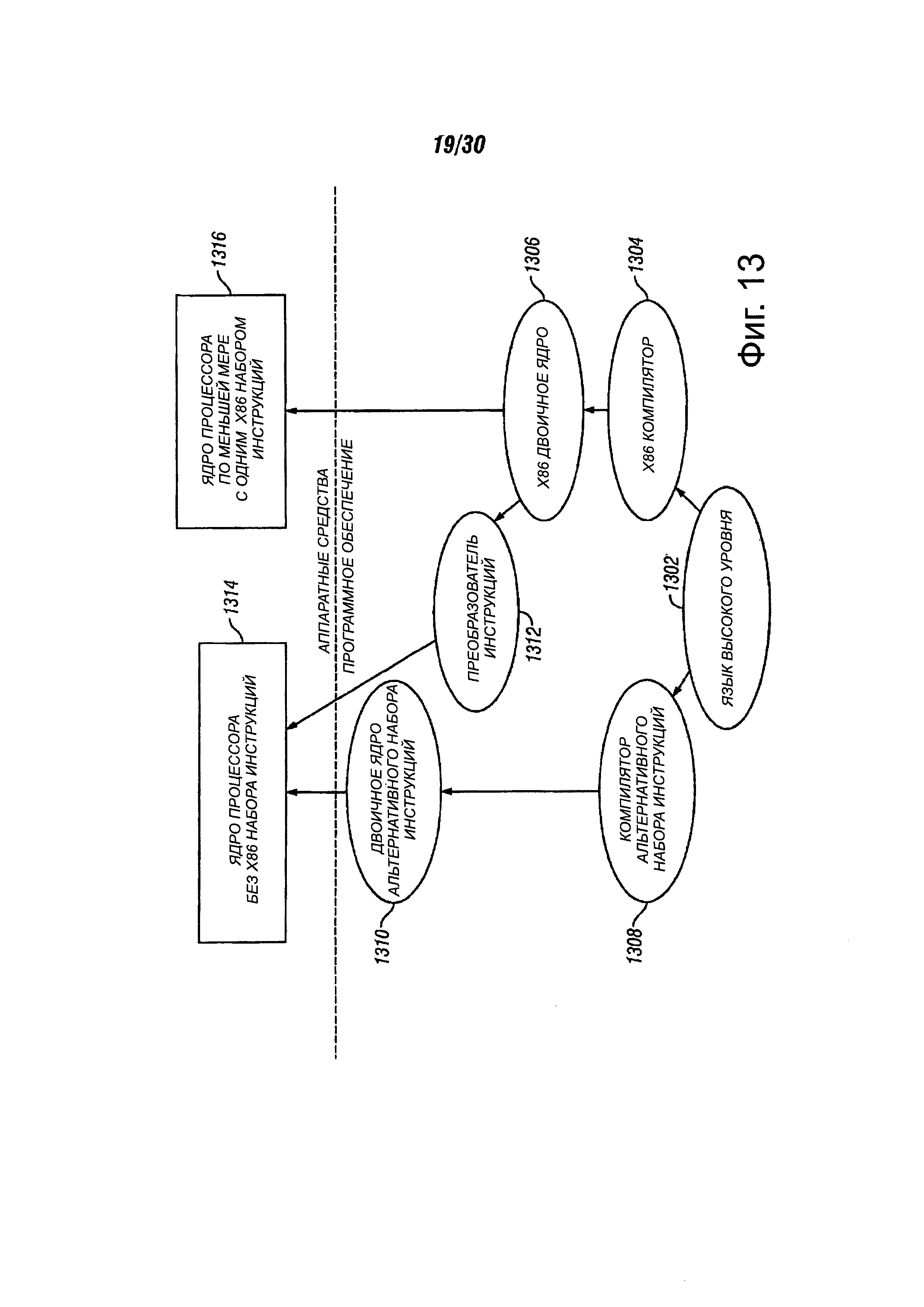

Фиг. 13 показывает блок-схему, различающую использование конвертора команд программного обеспечения для преобразования двоичных инструкций в наборе источника команды в двоичные инструкции в целевом наборе команд, в соответствии с вариантами осуществления настоящего изобретения;

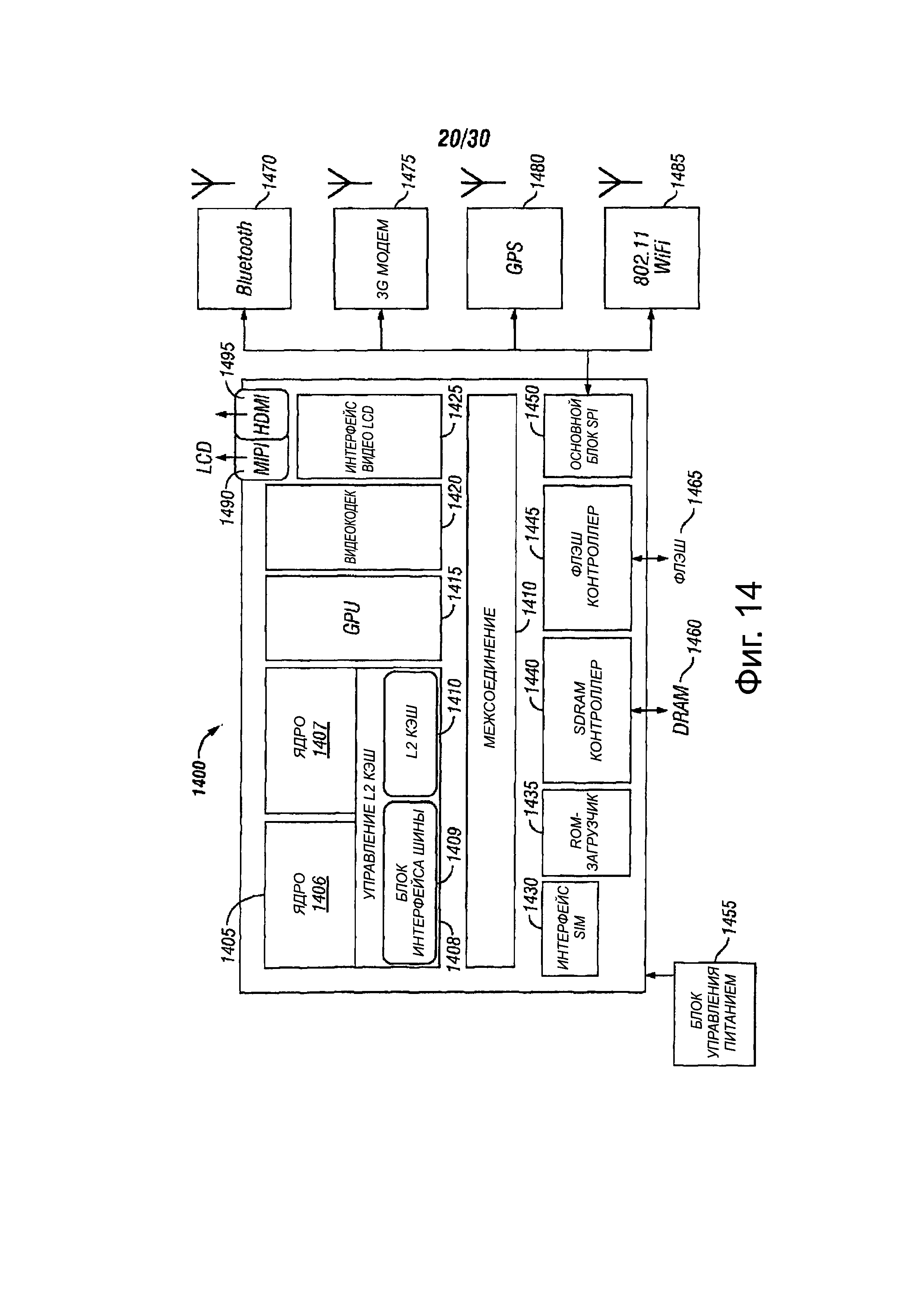

Фиг. 14 представляет собой блок-схему архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

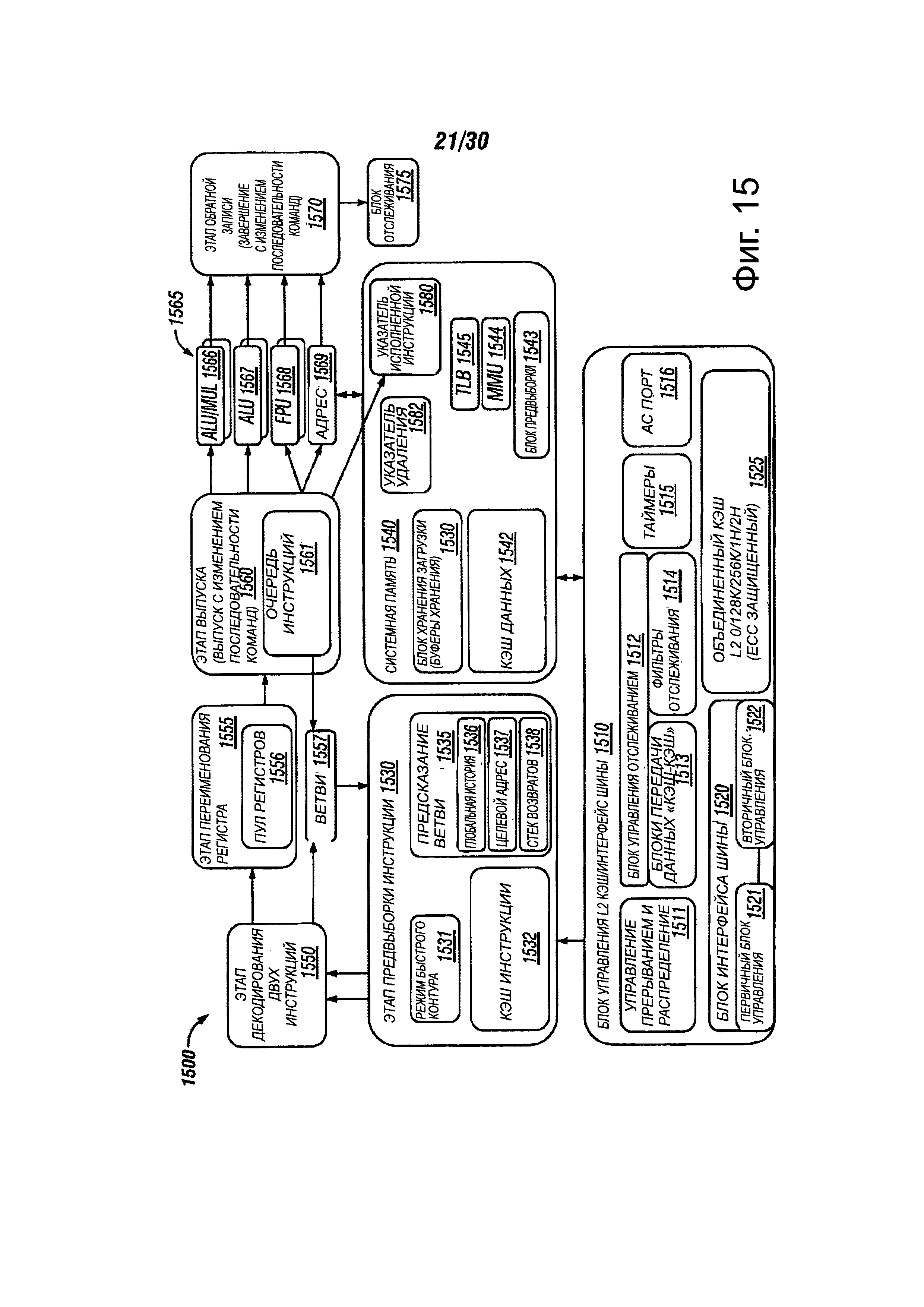

Фиг. 15 представляет собой более подробную блок-схему архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

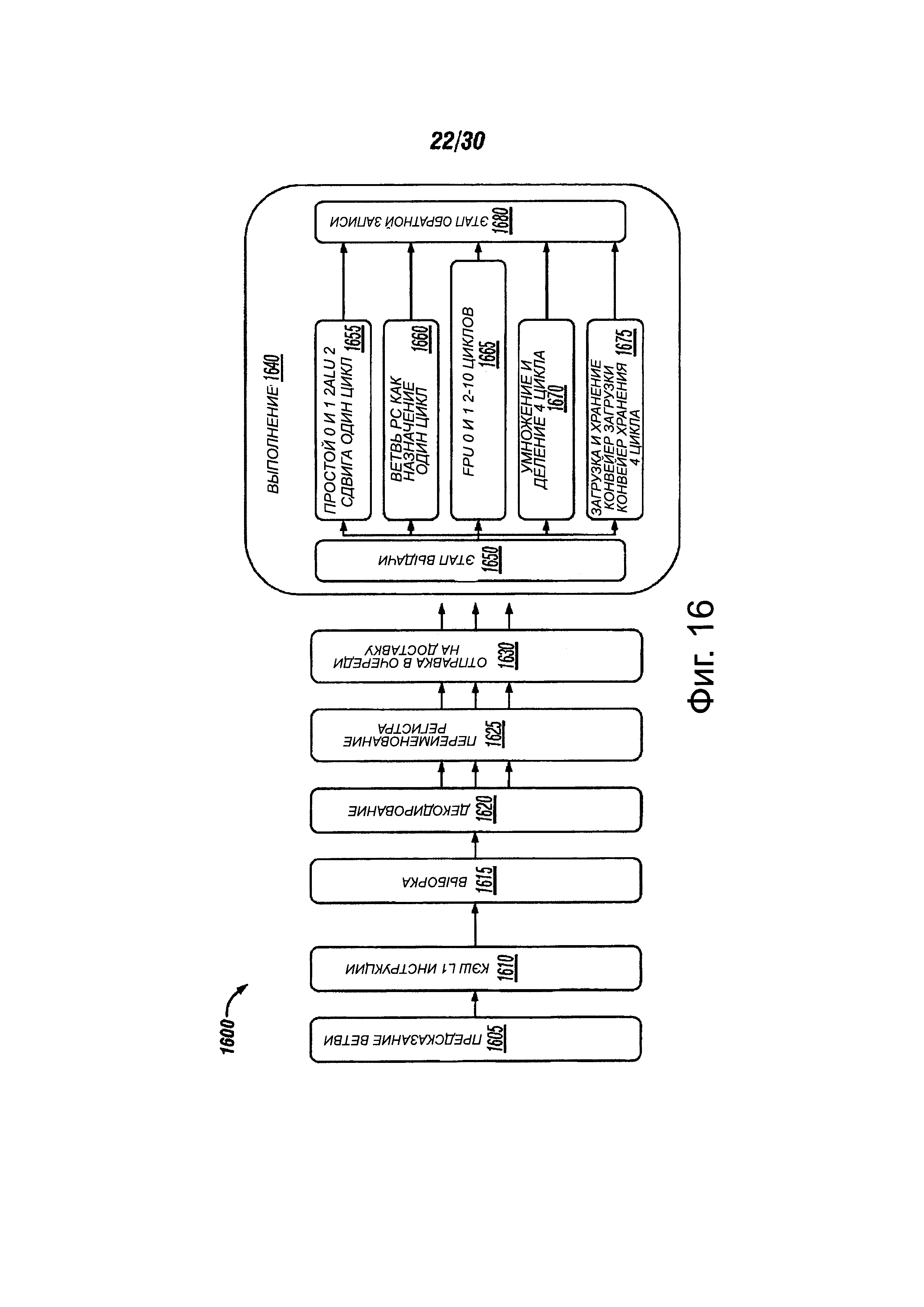

Фиг. 16 показана блок-схема конвейера для выполнения команд для процессора, в соответствии с вариантами осуществления настоящего изобретения;

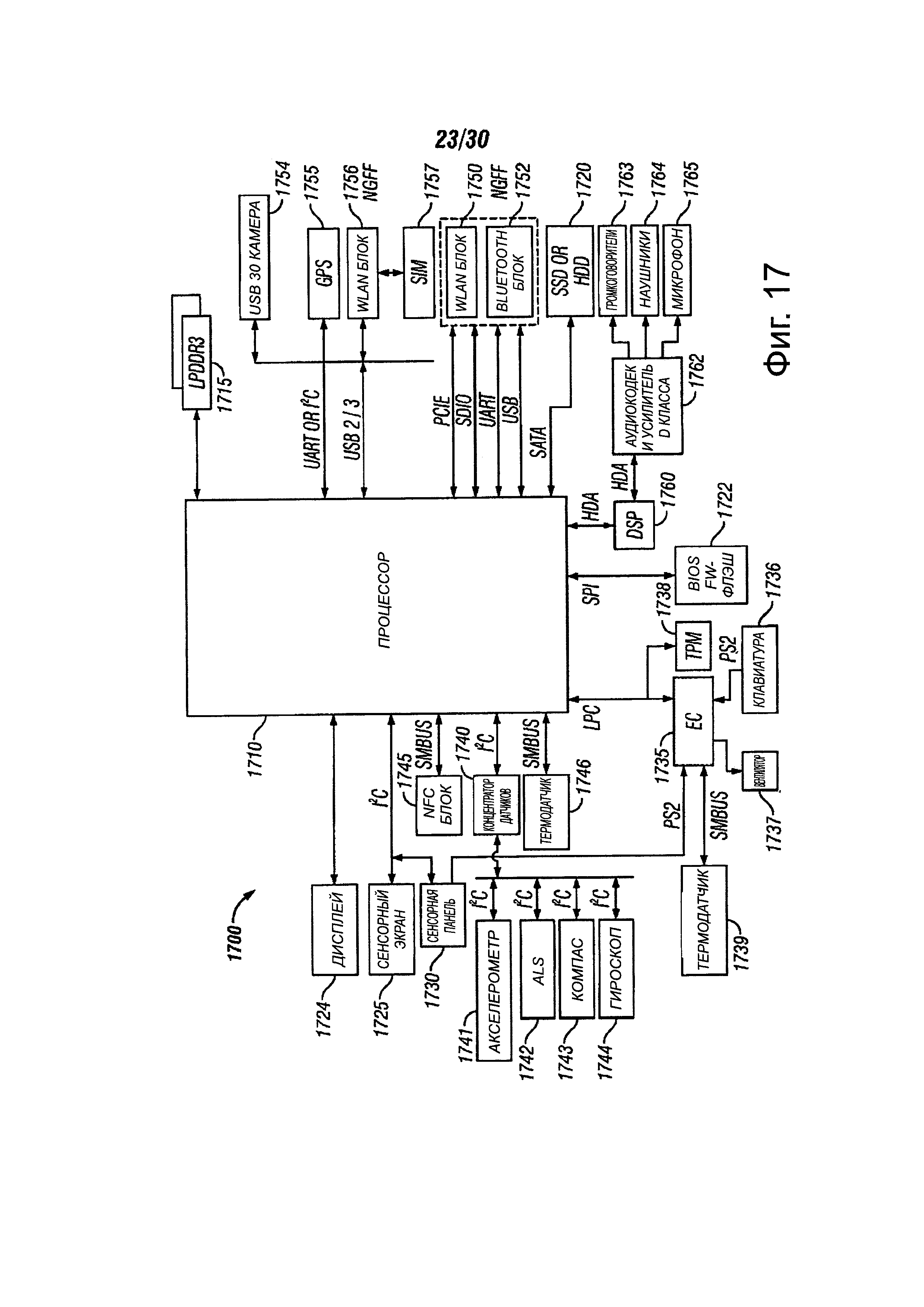

Фиг. 17 показывает блок-схему электронного устройства для использования процессора, в соответствии с вариантами осуществления настоящего изобретения;

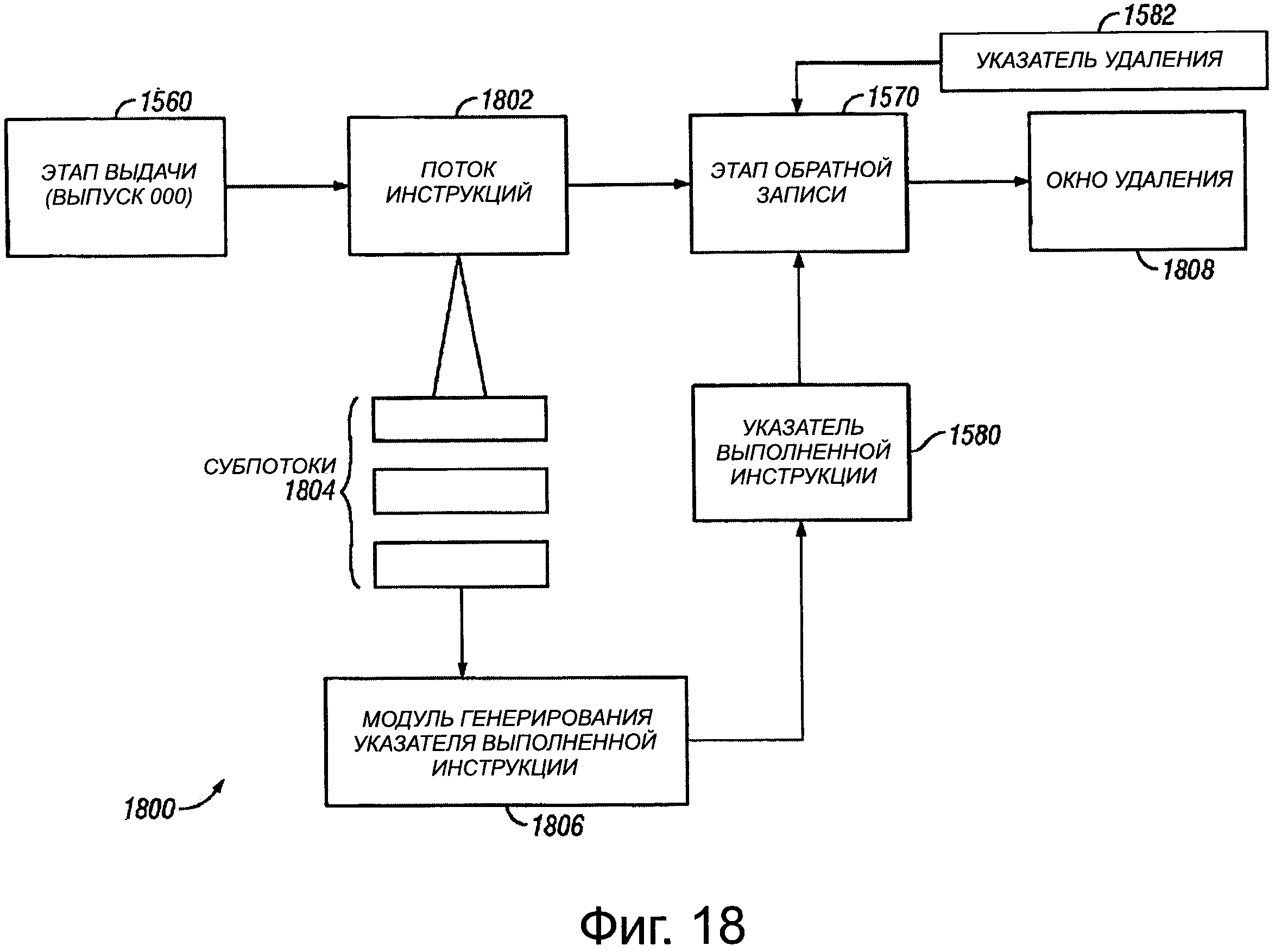

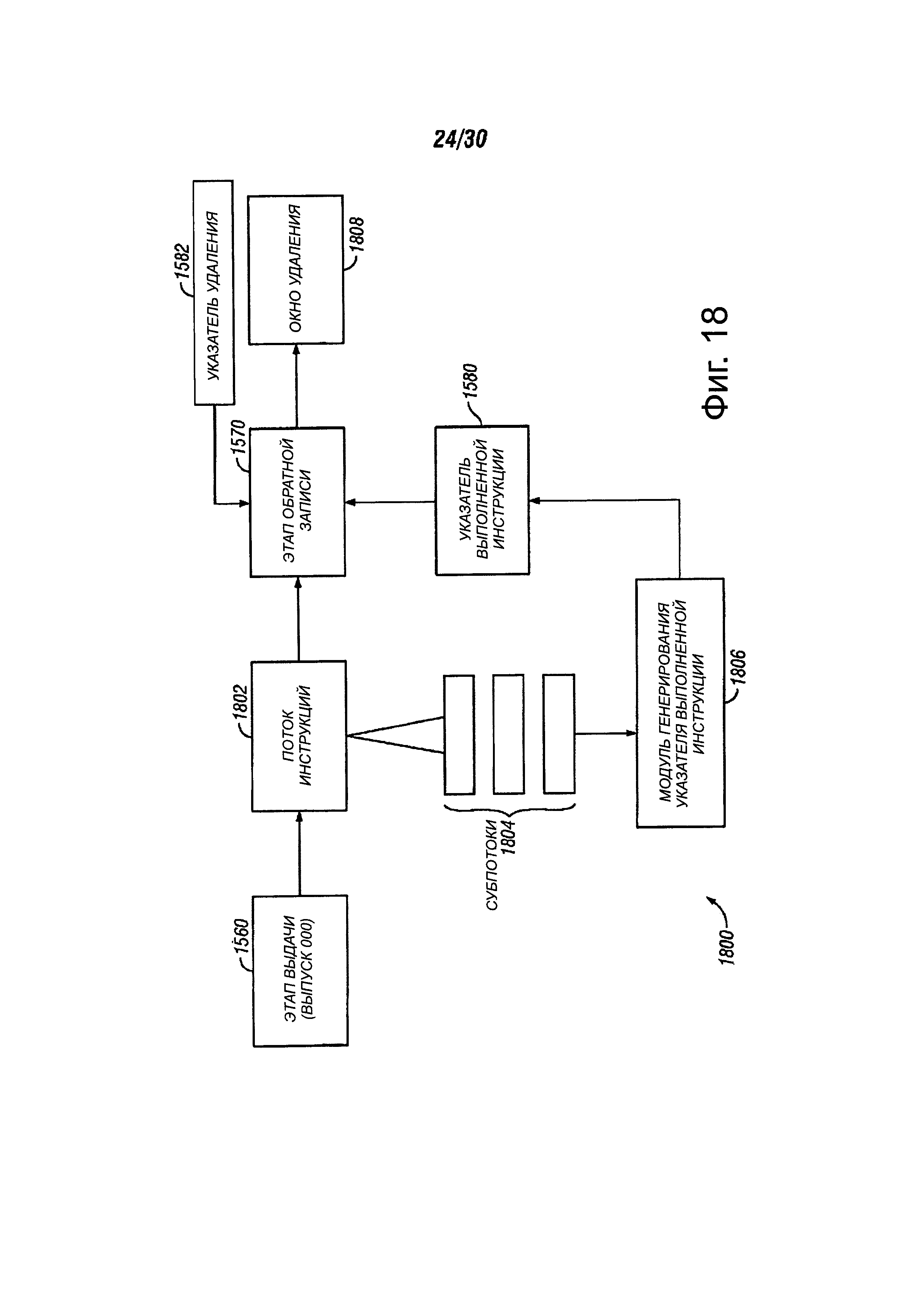

Фиг. 18 показывает функциональную блок-схему системы для выполнения инструкции и логику для идентификации инструкций, подходящих для удаления, в соответствии с вариантами осуществления настоящего изобретения;

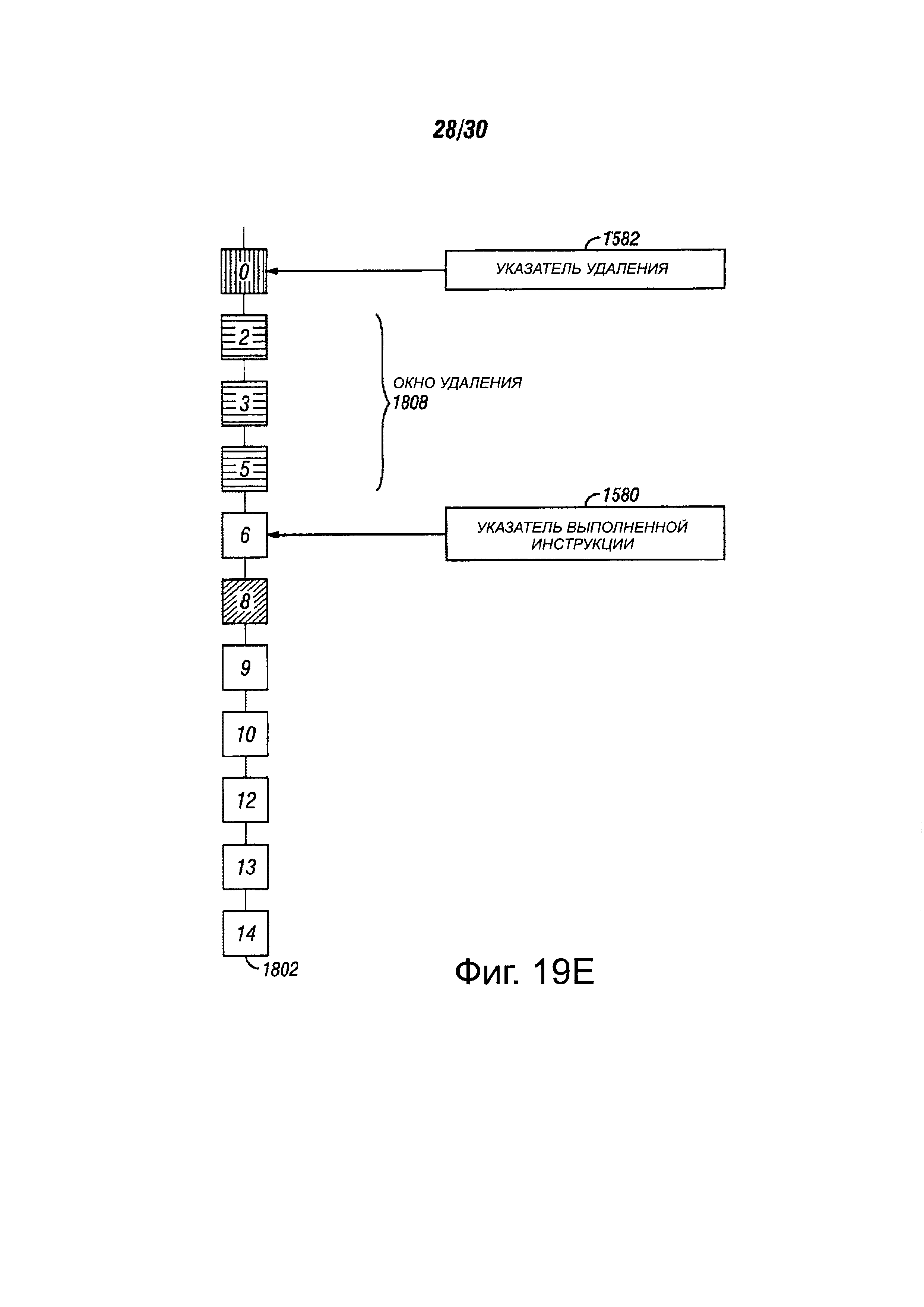

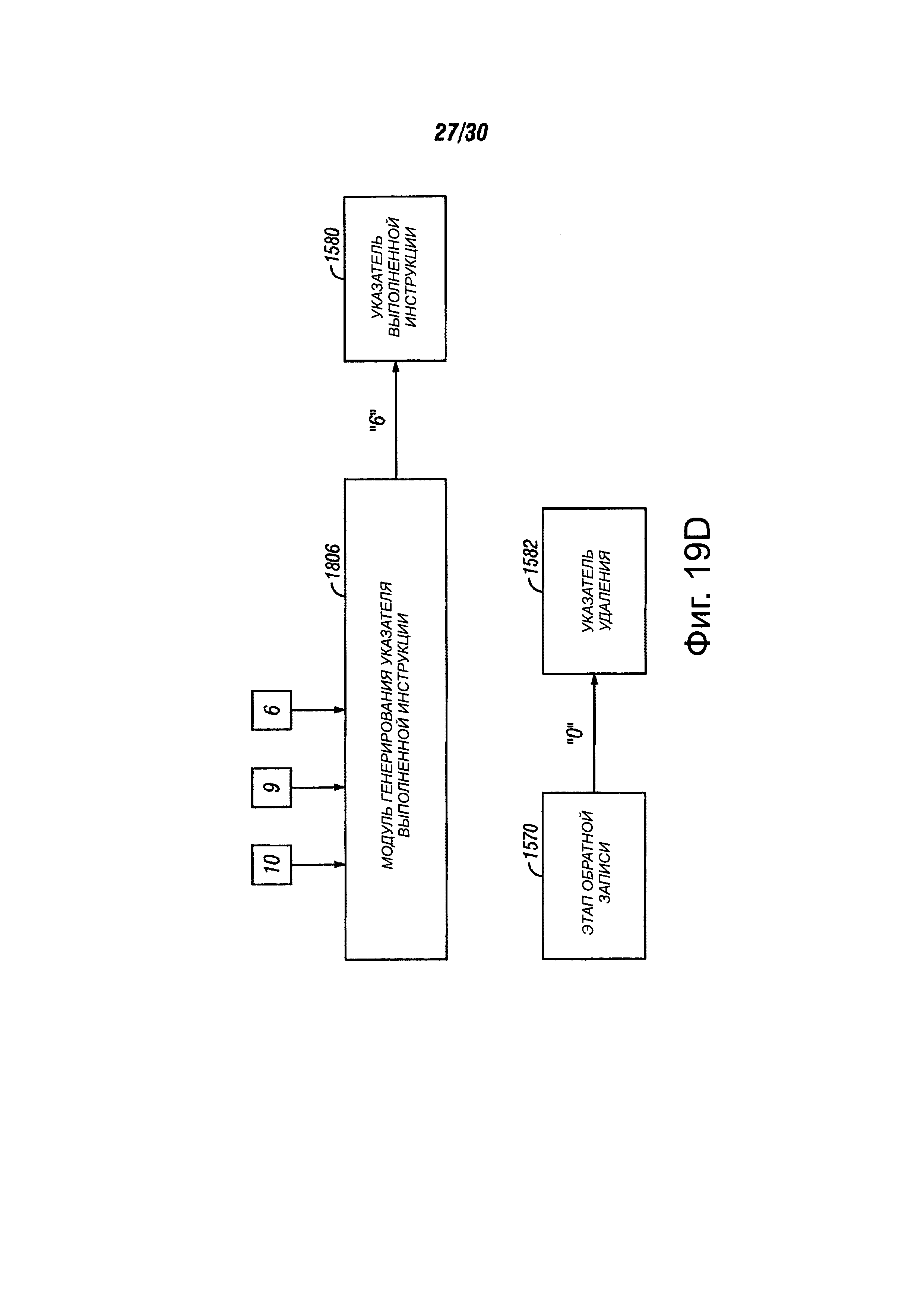

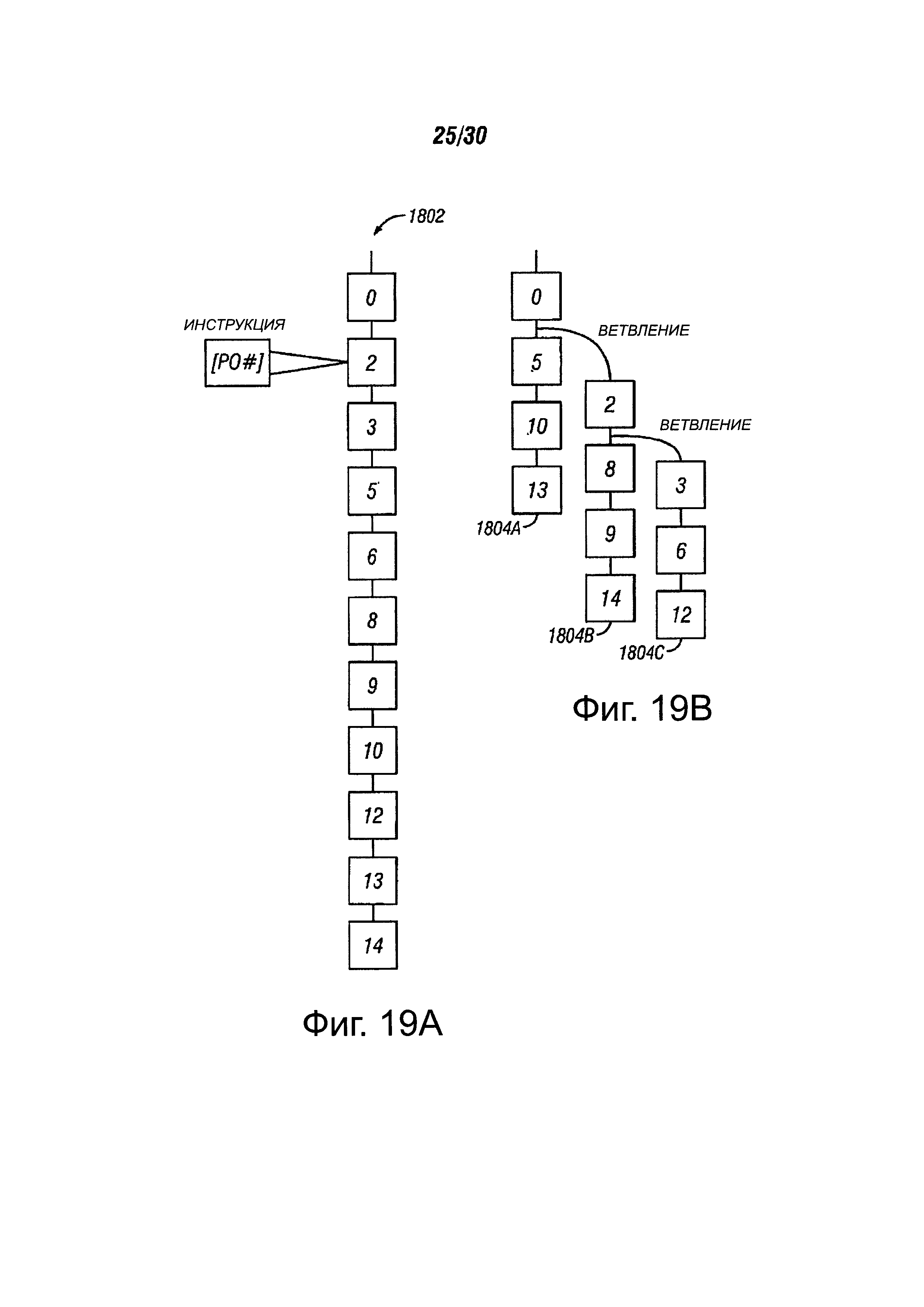

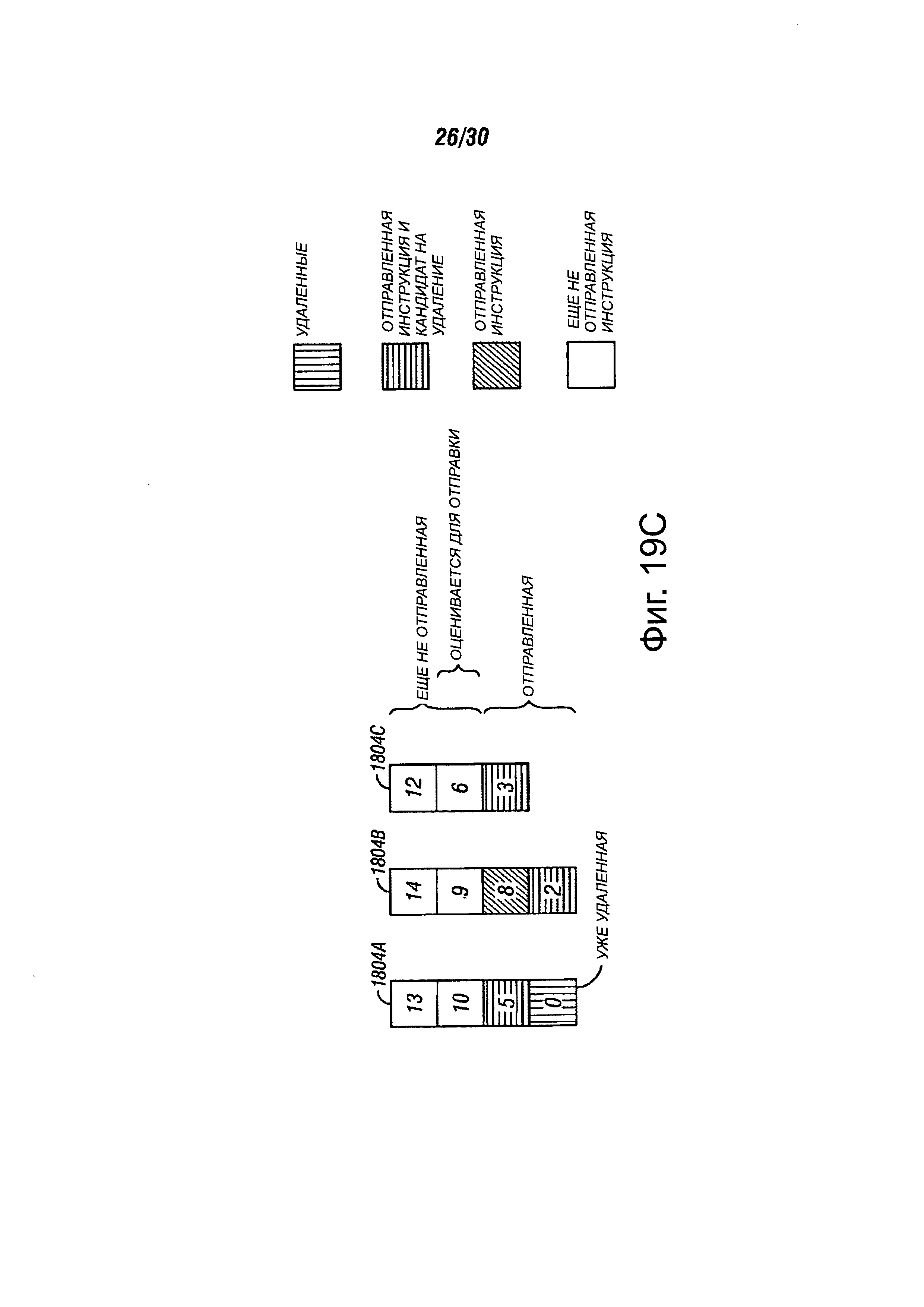

Фиг. 19А-19Е показывают более детальный вид системы для выполнения инструкции и логики для идентификации инструкций, подходящих для удаления, в соответствии с вариантами осуществления настоящего изобретения;

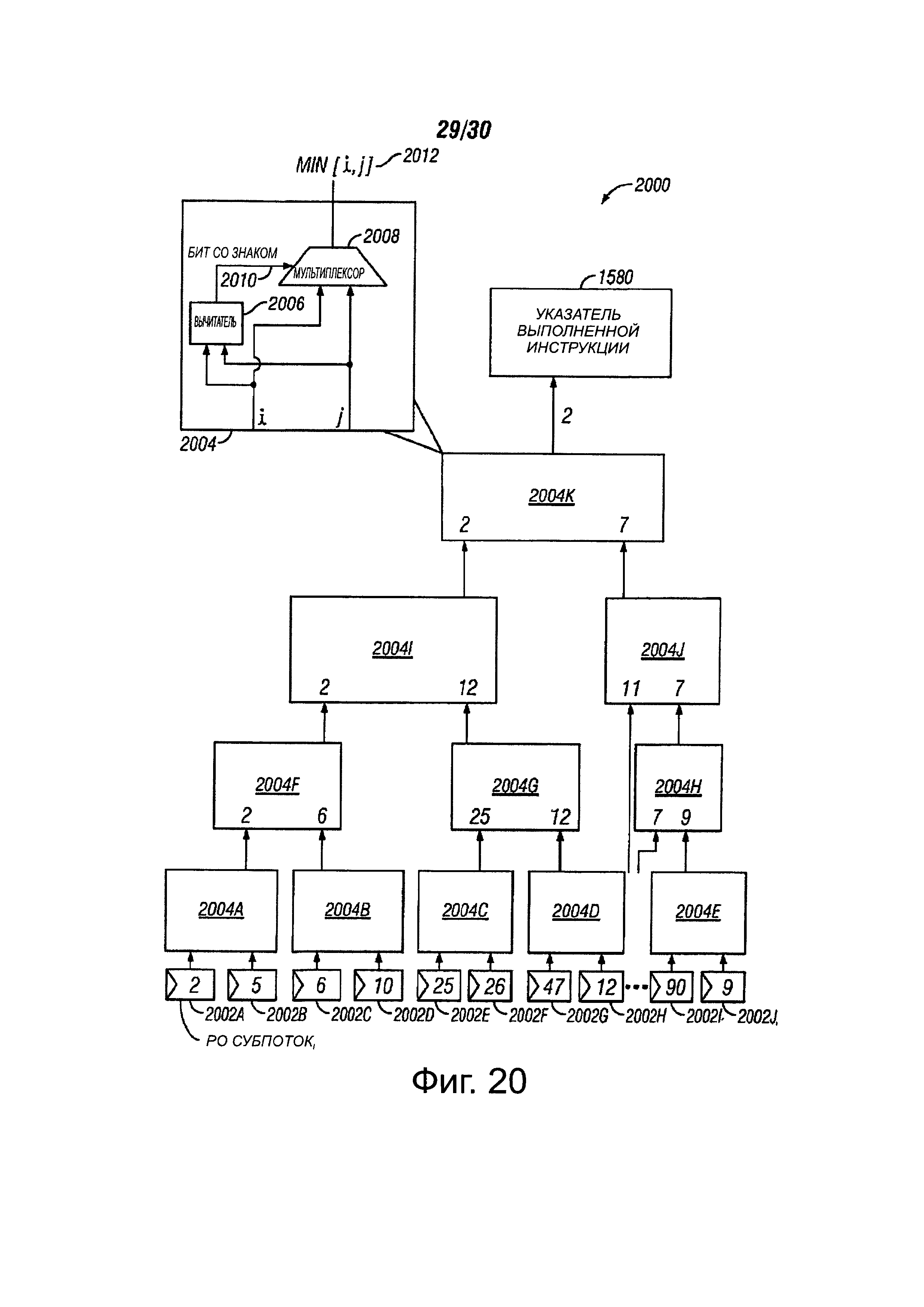

Фиг. 20 является иллюстрацией примера аппаратной логики для определения минимального значения порядка программы среди множества потоков в соответствии с вариантами осуществления настоящего изобретения; и

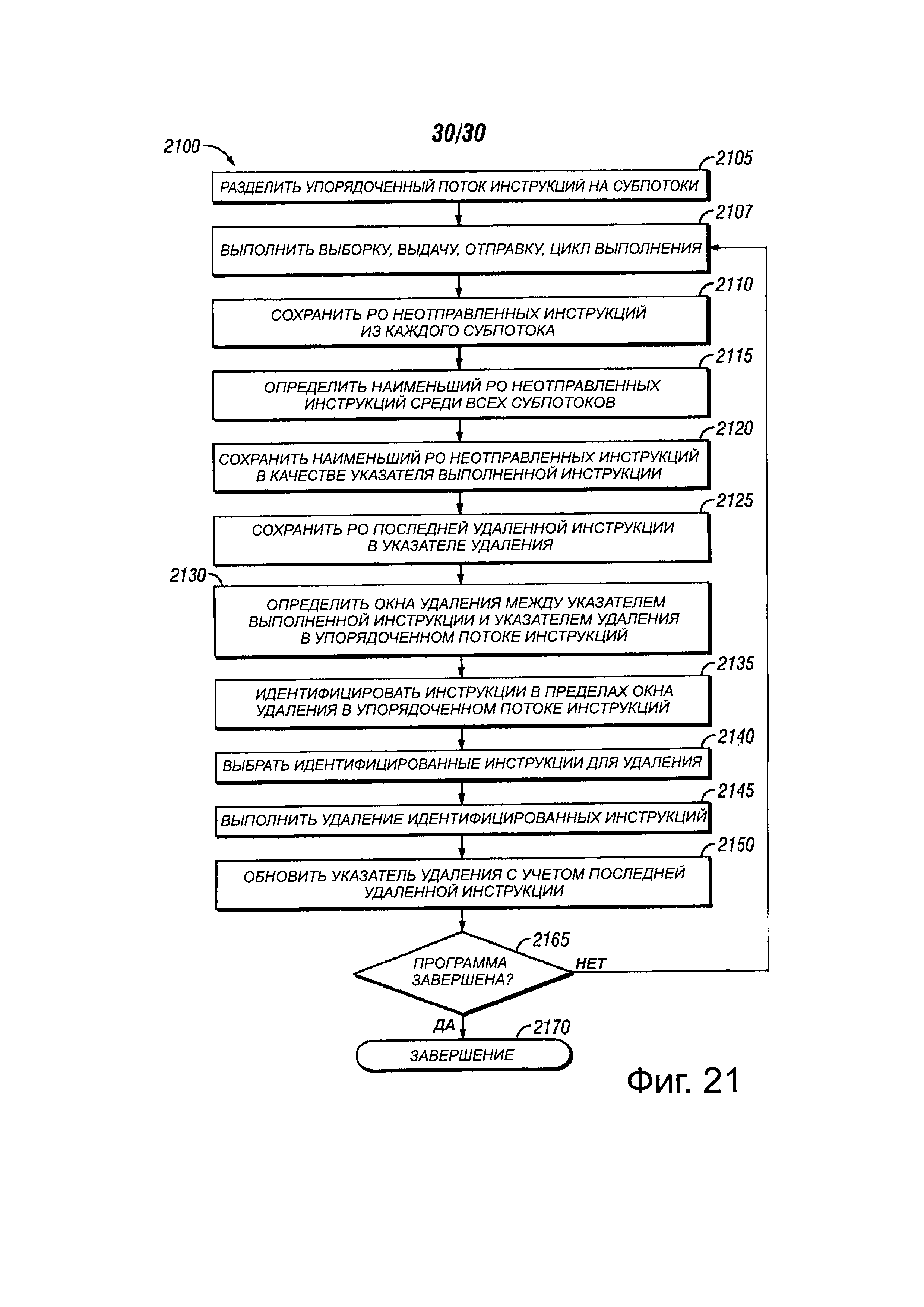

Фиг. 21 является иллюстрацией примера способа для идентификации инструкций, подходящих для удаления, в соответствии с вариантами осуществления настоящего изобретения.

Подробное описание

Следующее описание описывает инструкцию и логику обработки для идентификации инструкций, подходящие для удаления, в пределах или совместно с процессором, виртуальным процессором, пакете, компьютерной системой или другими устройствами обработки. Такое устройство обработки может включать в себя процессор с изменением последовательности команд. Более того, такое устройство обработки может включать в себя многопоточный процессор с изменением последовательности команд. В последующем описании многочисленные конкретные детали, такие как логическая схема обработки, типы процессоров, микроархитектурные условия, события, механизмы решений и тому подобное изложены для обеспечения более полного понимание вариантов осуществления настоящего изобретения. Следует принять во внимание специалистам в данной области техники, что варианты осуществления могут быть реализованы без таких конкретных деталей. Кроме того, некоторые хорошо известные структуры, схемы и тому подобное не показаны подробно для упрощения описания вариантов осуществления настоящего изобретения.

Несмотря на то, что следующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы к другим типам интегральных схем и логических устройств. Подобные способы и идеи вариантов осуществления настоящего изобретения могут быть применены к другим типам схем или полупроводниковым устройствам, которые могут получить выгоду от более высокой пропускной способности конвейерной обработки и улучшенной производительности. Идеи вариантов осуществления настоящего раскрытия применимы к любому процессору или машине, которая выполняет обработку данных. Однако варианты осуществления не ограничены процессорами или машинами, которые выполняют 512-битные, 256-битные, 128-битные, 64-битные, 32-битные или 16-битные операции с данными и могут быть применены к любому процессору и машине, в которой может быть осуществлено манипуляция или управление данными. Кроме того, в последующем описании, приведенные примеры и прилагаемые чертежи показывают различные примеры для целей иллюстрации. Однако эти примеры не следует рассматривать в ограничительном смысле, так как они предназначены только для обеспечения примеров вариантов осуществления настоящего изобретения, а не с целью дать исчерпывающий перечень всех возможных вариантов реализации вариантов осуществления настоящего изобретения.

Хотя, приведенные ниже примеры описывают процесс обработки команд и распределение в контексте исполнительных блоков и логических схем, другие варианты осуществления настоящего изобретения, могут быть получены путем передачи данных или инструкций, хранящихся на машиночитаемом, материальном носителе, которые, когда выполняются машиной, предписывают машине выполнять функции, в соответствии, по меньшей мере, с одним из вариантов осуществления изобретения. В одном из вариантов осуществления функции, ассоциированные с вариантами осуществления настоящего изобретения, воплощены в машиноисполняемые инструкции. Инструкции могут быть использованы для вызова процессора общего назначения или процессора специального назначения, которые могут быть запрограммированы инструкциями для выполнения этапов настоящего изобретения. Варианты осуществления настоящего изобретения могут быть представлены в виде компьютерного программного продукта или программного обеспечения, которое может включать в себя машину или компьютерно-считываемый носитель, имеющий сохраненные на нем команды, которые могут быть использованы для программирования компьютера (или других электронных устройств) для выполнения одной или более операций в соответствии с вариантами осуществления настоящего изобретения. Кроме того, этапы осуществления настоящего изобретения могут быть выполнены с помощью специальных компонентов аппаратных средств, которые содержат фиксированные логические функции для выполнения этапов, или любой комбинацией программируемых компьютерных компонентов и аппаратных компонентов с фиксированными функциями.

Инструкции, используемые для программной логики, для выполнения вариантов осуществления настоящего изобретения могут быть сохранены в памяти в системе, такой как DRAM, кэш, флэш-память или другое запоминающее устройство. Кроме того, инструкции могут быть распределены по сети или посредством другого считываемого компьютером носителя информации. Таким образом, машиночитаемый носитель информации может включать в себя любой механизм для хранения или передачи информации в форме, считываемой машиной (например, компьютером), но не ограничиваясь этим, гибкие диски, оптические диски, компакт-диск, компакт-диск постоянной памяти (CD-ROMs) и магнитооптические диски, память только для чтения (ROMs), оперативное запоминающее устройство (RAM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карты, флэш-память, или материальный машиночитаемый носитель информации, используемый при передаче информации через интернет с помощью электрических, оптических, акустических или других форм распространяющихся сигналов (например, несущие волны, инфракрасные сигналы, цифровые сигналы и т.д.). Соответственно, считываемый компьютером носитель информации может включать в себя любой тип материального машиночитаемого носителя информации, пригодный для хранения или передачи электронных инструкций или информации в форме, считываемой машиной (например, компьютером).

Разработка может осуществляться посредством реализации различных этапов, от создания до компьютерного моделирования и до изготовления. Данные, представляющие конструкцию, могут представлять конструкцию в цифровом виде. Во-первых, как это может быть полезно при моделировании, аппаратные средства могут быть представлены с использованием языка описания аппаратных средств или другого функционального языка описания. Кроме того, модель уровня схемы с логическим и/или транзисторным затвором могут быть изготовлены на некоторых этапах процесса проектирования. Кроме того, конструкции, на каком-то этапе, может достичь уровня данных, представляющие физическое размещение различных устройств в аппаратной модели. В тех случаях, в которых некоторые способы полупроводникового производства используются, данные, представляющие модель аппаратных средств, могут быть данными, указывающими на наличие или отсутствие различных признаков на различных уровнях маски для масок, используемых для производства интегральных схем. В любом представлении конструкции данные могут быть сохранены в любой форме машиночитаемого носителя. Память или магнитные или оптические запоминающие устройства, такие как диск, может быть машиночитаемым носителем информации для хранения информации, передаваемой с помощью модулированной оптической или электрической волны или иным образом генерироваться для передачи такой информации. При передаче электрической несущей волны с указанием или несущая код или информации о структуре, при этой осуществляется копирование, буферизация или повторная передача электрического сигнала, может быть сделана новая копия. Таким образом, провайдер связи или сетевой провайдер может хранить на материальном машиночитаемом носителе информации, по меньшей мере, временно, в статье, такой как, информация, закодированная на несущей волне, реализуя способы вариантов осуществления настоящего изобретения.

В современных процессорах могут быть использованы различные исполнительные блоки для обработки и выполнения различных кодов и инструкций. Некоторые инструкции могут быть обработаны быстрее, в то время как другие могут занять несколько тактовых циклов для завершения. Чем выше производительность команд, тем лучше общая производительность процессора. Таким образом, было бы выгодно иметь, на сколько это возможно, больше быстродействующих инструкций. Тем не менее, могут существовать определенные инструкции, которые имеют большую сложность и требуют больше с точки зрения времени выполнения и ресурсов процессора, такие как инструкции с плавающей запятой, операции загрузки/сохранения, перемещение данных и т.д.

Поскольку все больше компьютерных систем используются в интернете, в текстовых и мультимедийных приложениях, была использована дополнительная поддержка процессора в течение долгого времени. В одном варианте осуществления набор инструкций может быть связан с одной или более компьютерных архитектур, включающая в себя типы данных, инструкции, архитектуру регистра, режимы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод/вывод (I/O).

В одном варианте осуществления архитектура системы команд (ISA) может быть реализована с помощью одной или нескольких микроархитектур, которые могут включать в себя логику и схемы процессора, используемые для реализации одного или нескольких наборов команд. Соответственно, процессоры с различными микроархитектурами могут совместно использовать, по меньшей мере, часть общего набора инструкций. Например, Intel® Pentium 4 процессоры, процессоры Intel® Core™ и процессоры, изготовленные Advanced Micro Devices, Inc. Саннивейл CA реализовывают почти идентичные версии набора инструкций x86 (с некоторыми расширениями, которые были добавлены в более новые версии), но имеют различные внутренние конструкции. Аналогично, процессоры, разработанные другими компаниями в области разработки процессоров, такие как ARM Holdings, Ltd., MIPS или их лицензиаты или соразработчики, могут совместно использовать, по меньшей мере, часть общего набора команд, но могут включать в себя различные конструкции процессора. Например, та же архитектура регистра ISA может быть реализована по-разному в разных микроархитектурах с использованием новых или хорошо известных технологий, включающие в себя специализированные физические регистры, один или более динамически выделенных физических регистров с использованием механизма переименования регистра (например, использование таблицы псевдонимов регистров (RAT), буфера переупорядочения (ROB) и файла удаления регистра). В одном из вариантов осуществления регистры могут включать в себя один или несколько регистров, архитектуры регистров, регистровые файлы или другие наборы регистров, которые могут или не могут быть переадресованы с помощью программного обеспечения.

Инструкция может включать в себя один или несколько форматов команд. В одном варианте осуществления формат команд может указывать на различные поля (число битов, расположение битов и т.д.), чтобы указать, среди прочего, какая операция должна быть выполнена, и операнды, на которых будут выполняться, что операция. В дополнительном варианте осуществления, некоторые форматы команд могут быть дополнительно определены с помощью шаблонов команд (или субформаты). Например, шаблоны команд заданного формата команд могут быть определены, чтобы иметь различные подмножества полей формата команды и/или определены, чтобы иметь заданное поле, которое интерпретируется иным образом. В одном варианте осуществления команда может быть выражена с помощью формат команд (и, если определено, в данном одном из шаблонов команд этого формата инструкции) и устанавливает или указывает на операцию и операнды, на которых операция будет работать.

Научные, финансовые, автовекторные общего назначения, RMS (распознавание, анализ и синтез) и визуальные и мультимедийные приложения (например, 2D/3D графика, обработка изображений, сжатие/распаковка видео, алгоритмы распознавания голоса и аудио манипуляции) могут быть обработаны посредством одной и той же операции на большом количестве элементов данных. В одном из вариантов осуществления архитектура с одним потоком команд и несколькими потоками данных (SIMD) относится к типу инструкции, которая вызывает процессор выполнить операции с множеством элементов данных. Технология SIMD может использоваться в процессорах, которые могут логически разделить биты в регистре на ряд с фиксированной величиной или переменной величиной элементов данных, каждое из которых представляет собой отдельное значение. Например, в одном варианте осуществления биты в 64-битовом регистре могут быть организованы как операнд-источника, содержащий четыре отдельных 16-битовых элементов данных, каждый из которых представляет собой отдельное 16-битное значение. Этот тип данных может упоминаться как "упакованный" тип данных, или "вектор" типа данных, и операнды этого типа данных могут упоминаться как операнды упакованных данных или векторные операнды. В одном варианте осуществления элемент упакованных данных или вектор может представлять собой последовательность из элементов упакованных данных, сохраненных в одном регистре, и операнд упакованных данных или вектор операнд может быть исходным или конечным операндом SIMD инструкции (или 'инструкции упакованных данных' или 'инструкции вектора'). В одном варианте осуществления SIMD инструкция определяет одну векторную операцию, выполняемую на двух исходных векторных операндах, чтобы сгенерировать операнд вектора назначения (также называемый как операнд результирующего вектора) одного и того же или разного размера, с тем же или другим числом элементов данных, и в таком же или другом порядке элементов данных.

SIMD технологии, такие как, применяемые процессорами Intel® Core™, имеющие набор команд, включающий в себя х86, MМХ™, потоковые SIMD-расширения (SSE), SSE2, SSE3, инструкции SSE4.1 и SSE4.2, ARM процессоры, такие как ARM Cortex® семейства процессоров, имеющие набор команд, включающий в себя вектор с плавающей точкой (VFP) и/или инструкций NEON, и процессоры MIPS, такие как семейство Loongson процессоров, разработанных Институтом вычислительной техники (ICT) в китайской академии наук, позволили значительное повысить производительность приложений (Core™ и MМХ™ являются зарегистрированными товарными знаками или товарными знаками корпорации Intel в Санта-Клара, штат Калифорния).

В одном из вариантов осуществления регистры/данные источника и назначения могут быть общими терминами для представления источника и назначения соответствующих данных или операции. В некоторых вариантах осуществления они могут быть реализованы с помощью регистров, памяти или других мест хранения, имеющих другие названия или функции, чем те, которые представлены. Например, в одном варианте осуществления, "DEST1" может быть регистром временного хранения или другой областью хранения данных, в то время, как "SRC1" и "SRC2" могут быть первым и вторым регистром исходного хранения или другой областью памяти и так далее. В других вариантах осуществления, два или более SRC и DEST областей хранения могут соответствовать разным элементам хранения данных в пределах одной области хранения (например, SIMD регистр). В одном из вариантов осуществления один из исходных регистров может также выступать в качестве регистра назначения, например, посредством обратной записи результата операции, выполняемой на первых и вторых исходных данных, на один из двух исходных регистров, служащих в качестве регистров назначения.

На фиг. 1А показана блок-схема иллюстративной компьютерной системы, сформированной процессором, который может включать в себя исполнительные блоки для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения. Система 100 может включать в себя компонент, такой как процессор 102, применяя исполнительные блоки, включающие в себя логику для выполнения алгоритмов для обработки данных, в соответствии с настоящим изобретением, например, в варианте осуществления, описанном в данном документе. Система 100 может быть примером систем обработки, основанные на Pentium® III, Pentium® 4, Xeon™, Itanium®, XScale™ и/или микропроцессорам StrongARM™, которые обеспечиваются Intel Corporation Санта-Клара, штат Калифорния, хотя другие системы (включающие в себя персональные компьютеры, имеющие другие микропроцессоры, инженерные рабочие станции, телевизионные приставки и тому подобное) могут быть использованы. В одном варианте осуществления примерная система 100 может использовать версию операционной системы WINDOWS™, предоставляемую Microsoft Corporation в Редмонде, штат Вашингтон, хотя другие операционные системы (UNIX и Linux, например), встроенное программное обеспечение и/или графические пользовательские интерфейсы, также могут использоваться. Таким образом, варианты осуществления настоящего изобретения не ограничены какой-либо конкретной комбинацией схем аппаратного и программного обеспечения.

Варианты осуществления не ограничиваются компьютерными системами. Варианты осуществления настоящего изобретения могут быть использованы и в других устройствах, таких как портативные устройства и встроенные приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства интернет протокола, цифровые камеры, персональные цифровые помощники (PDA) и карманные ПК. Встроенные приложения могут включать в себя микроконтроллер, цифровой сигнальный процессор (DSP), систему на кристалле, сетевые компьютеры (NetPC), телеприставки, сетевые концентраторы, переключатели глобальной сети (WAN) или любую другую систему, которая может выполнять одну или несколько инструкций в соответствии, по меньшей мере, с одним вариантом осуществления.

Компьютерная система 100 может включать в себя процессор 102, который может включать в себя один или более исполнительных блоков 108 для выполнения алгоритма для выполнения, по меньшей мере, одной инструкции, в соответствии с одним из вариантов осуществления настоящего изобретения. Один вариант осуществления изобретения может быть описан в контексте одного настольного процессора или серверной системы, но другие варианты осуществления могут быть включены в состав многопроцессорной системы. Система 100 может быть примером архитектуры системы "хаба". Система 100 может включать в себя процессор 102 для обработки сигналов данных. Процессор 102 может включать в себя микропроцессор со сложным набором команд (CISC), микропроцессор с сокращенным набором команд (RISC), микропроцессор с командными словами очень большой длины (VLIW), процессор, реализующий комбинацию наборов инструкций или любой другой процессор, например, такой как процессор цифровых сигналов, например. В одном варианте осуществления, процессор 102 может быть соединен с шиной 110 процессора, которая может передавать сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 могут выполнять обычные функции, которые хорошо известны специалистам в данной области техники.

В одном варианте осуществления, процессор 102 может включать в себя LI внутренний кэш 104 первого уровня. В зависимости от архитектуры, процессор 102 может иметь один внутренний кэш или множество уровней внутреннего кэша. В другом варианте осуществления, кэш-память может находиться вне процессора 102. Другие варианты осуществления могут также включать в себя комбинацию внутренних и внешних кэшей в зависимости от конкретной реализации и потребностей. Регистровый файл 106 может хранить различные типы данных в различных регистрах, включающие в себя целочисленные регистры, регистры с плавающей запятой, регистры состояния и регистр указателя инструкций.

Исполнительный блок 108, включающий в себя логику для выполнения целочисленных операций и вычислений с плавающей запятой, также находится в процессоре 102. Процессор 102 также может включать в себя микрокод (UCODE) ROM, которое хранит микрокод для некоторых макрокоманд. В одном варианте осуществления исполнительный блок 108 может включать в себя логику для обработки набора 109 упакованных команд. Включением набора 109 упакованных команд в набор команд процессора 102 общего назначения, а также с соответствующей схемой для выполнения команд, операции, используемые многими мультимедийными приложениями, могут выполняться с использованием упакованных данных в процессоре 102 общего назначения. Таким образом, многие мультимедийные приложения могут быть ускорены и выполняться более эффективно при использовании полной ширины шины данных процессора для выполнения операций с упакованными данными. Это может устранить необходимость передачи более мелких блоков данных по шине передачи данных процессора для выполнения одной или более операций одного элемента данных за один раз.

Варианты осуществления исполнительного блока 108 также могут быть использованы в микроконтроллерах, встроенных процессорах, графических устройствах, DSPs и в других типах логических схем. Система 100 может включать в себя память 120. Память 120 может быть реализована в виде устройства динамической памяти с произвольным доступом (DRAM), устройства статической оперативной памяти (SRAM), устройства флэш-памяти или другого устройства памяти. Память 120 может хранить инструкции и/или данные, представленные сигналами данных, которые могут быть выполнены процессором 102.

Системная логическая микросхема 116 может быть соединена с шиной НО процессора и памятью 120. Системная логическая микросхема 116 может включать в себя концентратор контроллера памяти (МСН). Процессор 102 может осуществлять связь с МСН 116 через шину 110 процессора. МСН 116 может обеспечить тракт 118 памяти с высокой пропускной способностью к памяти 120 для передачи и хранения данных и для хранения графических команд, данных и текстур. МСН 116 может направлять сигналы данных между процессором 102, памятью 120 и другими компонентами в системе 100 и служит мостом для сигналов данных между шиной 110 процессора, памятью 120 и системой 122 ввода/вывода. В некоторых вариантах осуществления системная логическая микросхема 116 может обеспечивать графический порт для соединения с графическим контроллером 112. МСН 116 может быть соединен с памятью 120 через интерфейс 118 памяти. Графическая карта 112 может быть соединена с МСН 116 через межсоединение 114 быстродействующего графического порта (AGP).

Система 100 может использовать шину 122 интерфейса собственного концентратора для соединения МСН 116 с концентратором 130 I/O контроллера (ICH). В одном варианте осуществления МСН 130 может обеспечить прямое подключение с некоторыми устройствами ввода/вывода через локальную шину ввода/вывода. Локальная шина ввода/вывода может включать в себя высокоскоростную шину ввода/вывода для подключения периферийных устройств к памяти 120, набору микросхем и процессору 102. Примеры могут включать в себя аудио контроллер, концентратор 128 встроенного программного обеспечения (флэш-BIOS), беспроводной приемопередатчик 126, блок 124 хранения данных, унаследованный контроллер ввода/вывода, содержащий пользовательские интерфейсы ввода и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB) и сетевой контроллер 134. Блок 124 хранения данных может содержать жесткий диск, флоппи-дисковод, CD-ROM, устройство флэш-памяти или другое запоминающее устройство.

В качестве другого варианта осуществления системы, инструкция в соответствии с одним вариантом осуществления, может быть использована с системой на кристалле. Один из вариантов осуществления системы на кристалле включает в себя процессор и память. Память для одной такой системы может включать в себя флэш-память. Флэш-память может быть расположена на том же кристалле, что и процессор, и другие компоненты системы. Кроме того, другие логические блоки, такие как контроллер памяти или графический контроллер также могут быть расположены в системе на кристалле.

Фиг. 1B изображает систему 140 обработки данных, которая реализует принципы вариантов осуществления настоящего изобретения. Как очевидно для специалистов в данной области техники, варианты осуществления, описанные здесь, могут работать с альтернативными системами обработки данных без отхода от сущности и объема вариантов осуществления изобретения.

Компьютерная система 140 содержит процессорное ядро 159 для выполнения, по меньшей мере, одной инструкции, в соответствии с одним вариантом осуществления. В одном из вариантов осуществления процессорное ядро 159 представляет собой блок обработки любого типа архитектуры, включающей в себя, но не ограничиваясь этим, CISC, RISC или VLIW тип архитектуры. Процессорное ядро 159 также может быть изготовлено посредством одного или нескольких технологических процессов, и посредством представления на машиночитаемом носителе информации достаточно подробно, может быть пригодно для облегчения упомянутого производства.

Процессорное ядро 159 содержит исполнительный блок 142, набор регистровых файлов 145 и декодер 114. Процессорное ядро 159 может также включать в себя дополнительные схемы (не показаны), которые могут быть ненужными для понимания вариантов осуществления настоящего изобретения. Исполнительный блок 142 может выполнять инструкции, полученные процессорным ядром 159. В дополнение к выполнению типовых инструкций процессора, исполнительный блок 142 может выполнять инструкции в наборе 143 упакованных команд для выполнения операций над форматами упакованных данных. Набор 143 упакованных команд может включать в себя инструкции для выполнения вариантов осуществления изобретения и других упакованных инструкций. Исполнительный блок 142 может быть соединен с регистровым файлом 145 с помощью внутренней шины. Регистровый файл 145 может представлять собой область хранения на процессорном ядре 159 для хранения информации, в том числе данных. Как упоминалось ранее, следует понимать, что область для хранения может хранить упакованные данные, но это не является критическим. Исполнительный блок 142 может быть соединен с декодером 144. Декодер 144 может декодировать инструкции, полученные процессорным ядром 159 в управляющие сигналы и/или точки входа микрокода. В ответ на эти сигналы управления и/или точек входа микрокода, исполнительный блок 142 выполняет соответствующие операции. В одном варианте осуществления декодер может интерпретировать опкод инструкции, который будет указывать на то, что операция должна выполняться на соответствующих данных, указанных в инструкции.

Процессорное ядро 159 может быть соединено с шиной 141 для связи с различными другими системными устройствами, которые могут включать в себя, но не ограничиваются ими, например, блок 146 управления синхронным динамическим оперативным запоминающим устройством (SDRAM), блок 147 управления статическим оперативным запоминающим устройством (SRAM), интерфейс 148 пакетной флэш-памяти, блок управления 149 картой памяти персонального компьютера международной ассоциации (РСМС1А)/карта памяти (CF), блок управления 150 жидкокристаллическим дисплеем (LCD), контроллер 151 прямого доступа к памяти (DMA) и главный интерфейс 152 альтернативной шины. В одном из вариантов осуществления, система 140 обработки данных также может включать в себя мост 154 ввода/вывода для связи с различными устройствами ввода/вывода через шину 153 ввода/вывода. Такие устройства ввода/вывода могут включать в себя, но не ограничиваются ими, например, универсальный асинхронный приемник/передатчик (UART) 155, универсальную последовательную шину (USB) 156, Bluetooth беспроводного UART 157 и интерфейс 158 расширения ввода/вывода.

Один из вариантов осуществления системы 140 обработки данных обеспечивает для мобильных устройств, сетевой и/или беспроводной связи и процессорного ядра 159, которые могут выполнять SIMD операции, включающую в себя операцию сравнения текстовой строки. Процессорное ядро 159 может быть запрограммировано с помощью различных аудио, видео, изображений и алгоритмов коммуникаций, включающие в себя дискретные преобразования, такие как преобразование Уолша-Адамара, быстрое преобразование Фурье (FFT), дискретное косинусное преобразование (DCT) и их соответствующие обратные преобразования; способы сжатия/распаковки, такие как преобразование цветового пространства, оценка движения кодирования видео или компенсация движения декодирования видео; и функции модуляции/демодуляции (МОДЕМ), такие как импульсно-кодовая модуляция (РСМ).

На фиг. 1С показаны другие варианты осуществления системы обработки данных, которая выполняет SIMD-операции сравнения текстовых строк. В одном из вариантов осуществления, система 160 обработки данных может включать в себя центральный процессор 166, а SIMD сопроцессор 161, кэш-память 167 и систему 168 ввода/вывода. Система 168 ввода/вывода может быть дополнительно соединена с беспроводным интерфейсом 169. SIMD-сопроцессор 161 может выполнять операции, включающие в себя инструкции согласно одному варианту осуществления изобретения. В одном из вариантов осуществления процессорное ядро 170 может быть пригодным для производства посредством одного или нескольких технологических процессов, а также представлено на машинно-читаемом носителе информации достаточно подробно, что может быть пригодным для облегчения изготовления всей или части системы 160 обработки данных, включающей в себя процессорное ядро 170.

В одном из вариантов осуществления, SIMD-сопроцессор 161 содержит исполнительный блок 162 и набор регистровых файлов 164. Один из вариантов основного процессора 165 содержит декодер 165, чтобы распознавать команды из набора 163 инструкций, включающие в себя инструкции, в соответствии с одним вариантом осуществления для исполнения исполнительным блоком 162. В других вариантах осуществления, SIMD-сопроцессор 161 также включает в себя, по меньшей мере, часть декодера 165 для декодирования инструкций набора 163 инструкций. Процессорное ядро 170 может также включать в себя дополнительные схемы (не показаны), которые могут быть излишними для понимания вариантов осуществления настоящего изобретения.

В процессе работы основной процессор 166 выполняет обработку потока данных посредством инструкций, которые управляют операциями обработки данных общего типа, включающую в себя взаимодействие с кэш-памятью 16, и системой 168 ввода/вывода. Находящиеся в потоке инструкции обработки данных могут быть инструкциями SIMD сопроцессора. Декодер 165 основного процессора 166 распознает эти инструкции SIMD-сопроцессора, как тип, который должен быть выполнен посредством подключенного SIMD-сопроцессора 161. Соответственно, основной процессор 166 выдает эти инструкции SIMD сопроцессора (или управляющие сигналы, представляющие инструкции SIMD сопроцессора) на шину 166 сопроцессора. Из шины 166 сопроцессора эти инструкции могут быть приняты любыми присоединенными SIMD сопроцессорами. В этом случае, SIMD-сопроцессор 161 может принимать и исполнять любые принятые инструкции SIMD сопроцессора, предназначенные для него.

Данные могут быть приняты с помощью беспроводного интерфейса 169 для обработки инструкций посредством SIMD сопроцессора. Для одного примера, голосовая связь может быть принята в виде цифрового сигнала, который может быть обработан с помощью инструкций SIMD сопроцессора для генерирования цифровой выборки аудио, характерной для речевой коммуникации. В качестве другого примера, сжатые аудио и/или видео могут быть приняты в виде цифрового потока битов, который может быть обработан с помощью инструкций SIMD сопроцессора для генерирования цифровых выборок аудио и/или видеокадров движения. В одном из вариантов осуществления процессорное ядро 170, главный процессор 166 и SIMD-сопроцессор 161 могут быть интегрированы в единое процессорное ядро 170, содержащее исполнительный блок 162, набор регистровых файлов 164 и декодер 165 для распознавания команд из набора 163 инструкций, включающий в себя инструкции в соответствии с одним вариантом осуществления.

На фиг. 2 представлена блок-схема микроархитектуры для процессора 200, который может включать в себя логические схемы для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения. В некоторых вариантах осуществления инструкции в соответствии с одним из вариантов осуществления может быть реализован для работы на элементах данных, имеющих размеры байта, слова, сдвоенного слова, учетверенного слова и т.д., а также типов данных, таких как одинарной и двойной точности целого числа и типов данных с плавающей запятой. В одном варианте осуществления, упорядоченный коммуникационный процессор 201 может реализовать часть процессора 200, который может выбрать инструкции для исполнения и подготавливает инструкции, которые будут использоваться позже в конвейере процессора. Коммуникационный процессор 201 может включать в себя несколько блоков. В одном варианте осуществления, устройство 226 предвыборки инструкций выбирает инструкции из памяти и поставляет инструкции в декодер 228 инструкций, который, в свою очередь, декодирует или интерпретирует инструкции. Например, в одном варианте осуществления декодер декодирует принятую инструкцию в одну или несколько операций, называемых "микроинструкциями" или "микрооперациями" (также называемые как ор или uops), так что машина может выполнять. В других вариантах осуществления настоящего изобретения декодер выполняет синтаксический разбор инструкции на опкод, соответствующие данные и поля управления, которые могут быть использованы микроархитектурой для выполнения операций в соответствии с одним вариантом осуществления. В одном варианте осуществления, трассовый кэш 230 может собрать декодированные uops в программу упорядоченных последовательностей или трассировать в uops последовательность 234 для исполнения. Когда трассовый кэш 230 наталкивается на сложную инструкцию, ROM 232 микрокода обеспечивает uops, необходимые для завершения операции.

Некоторые инструкции могут быть преобразованы в единую микрооперацию, в то время, как другие требуют нескольких микроопераций для завершения полной операции. В одном варианте осуществления, если более чем четыре микро-ops необходимы для выполнения инструкции, декодер 228 может получить доступ к ROM 232 микрокода для выполнения инструкции. В одном варианте осуществления инструкция может быть декодирована на небольшое число микроопераций для обработки инструкций в декодере 228. В другом варианте осуществления инструкция может быть сохранена в ROM 232 микрокода, где необходимо иметь ряд микроопераций для выполнения операции. Трассовый кэш 230 относится к точке входа программируемой логической матрицы (PLA) для определения корректного указателя микроинструкции для считывания последовательности микрокода для выполнения одной или нескольких инструкций в соответствии с одним вариантом осуществления, из ROM 232 микрокода. После того, как ROM 232 микрокода заканчивает операцию управления выполнением микрокоманды для инструкции, коммуникационный процессор 201 машины может возобновить выборку микроопераций из трассового кэша 230.

Исполнительный блок 203 с изменением последовательности команд может подготовить инструкции для выполнения. Логическая схема с изменением последовательности команд имеет ряд буферов для сглаживания и переупорядочивания потока инструкций для оптимизации процесса функционирования, при прохождении по конвейеру и являются запланированными для выполнения. Логический распределитель выделяет буферы машины и ресурсы, которые нужны каждой uop для выполнения. Логика переименования регистров переименовывает логические регистры на записях в файле регистров. Распределитель также выделяет запись для каждой uop в одной из двух uop очередей, одну для операций с памятью и одну для операций без памяти, перед планировщиками инструкции: планировщик памяти, быстрый планировщик 202, медленный / общий с плавающей запятой планировщик 204 и планировщик 206 с простой плавающей точкой. Uop планировщики 202, 204, 206 определить, когда uop готова к выполнению, на основе готовности их зависимого входного регистра источников операндов и наличия исполнительных ресурсов uop для завершения свой работы. Быстрый планировщик 202 одного варианта осуществления может планировать на каждую половину основного тактового цикла, в то время как другие планировщики могут только планировать один раз на тактовый цикл основного процессора. Атрибут планировщиков для портов отправки планируют uops для исполнения.

Регистровые файлы 208, 210 могут быть расположены между планировщиками 202, 204, 206 и исполнительные блоки 212, 214, 216, 218, 220, 222, 224 в исполнительном блоке 211. Каждый из регистровых файлов 208, 210 выполняет целочисленную операцию и операцию с плавающей точкой, соответственно. Каждый регистровый файл 208, 210, может включать в себя перепускную сеть, которая может обойти или пересылать только завершенные результаты, которые еще не были записаны в регистровый файл новые зависимые uop. Целочисленный регистровый файл 208 и регистровый файл 210 с плавающей точкой могут обмениваться данными с другими. В одном из вариантов осуществления, целочисленный регистровый файл 208 может быть разделен на два отдельных регистровых файла, один регистровый файл для низкого порядка тридцати двух битных данных, и второй регистровый файл для высокого порядка тридцати двух битных данных. Регистровый файл 210 с плавающей точкой может включать в себя 128-битные записи, так как инструкции с плавающей запятой обычно имеют операнды от 64 до 128 бит в ширину.

Исполнительный блок 211 может содержать исполнительные блоки 212, 214, 216, 218, 220, 222, 224. Исполнительные блоки 212, 214, 216, 218, 220, 222, 224 могут выполнять инструкции. Исполнительный блок 211 может включать в себя регистровые файлы 208, 210, которые хранят целочисленные значения и значения операндов данных с плавающей точкой, микроинструкций для выполнения. В одном варианте осуществления процессор 200 может включать в себя ряд исполнительных блоков: блок формирования адреса (AGU) 212, AGU 214, быстрый ALU 216, быстрый ALU 218, медленный ALU 220, с плавающей точкой ALU 222, блок 224 перемещения с плавающей точкой. В другом варианте воплощении исполнительные блоки 222, 224 с плавающей точкой могут выполнять ММХ, SIMD и SSE или другие операции. В еще одном варианте ALU 222 с плавающей точкой может включать в себя делитель с плавающей точкой 64-бит на 64-бит для выполнения операции деления, излечения квадратного корня и вычет микроопераций. В различных вариантах осуществления инструкции, включающие в себя значение с плавающей точкой, могут быть обработаны посредством аппаратных средств с плавающей точкой. В одном варианте осуществления ALU операции могут быть переданы в высокоскоростные исполнительные блоки ALU 216, 218. Высокоскоростные ALU 216, 218 могут выполнять операции с высокой скоростью с эффективной задержкой в половину тактового цикла. В одном из вариантов осуществления наиболее сложные целочисленные операции обрабатываются медленным ALU 220, так как медленный ALU 220 может включать в себя аппаратное обеспечение для выполнения целочисленных операций для выполнения длиннолатентных операций, таких как умножение, сдвиги, флаг логики и разветвления. Операции загрузки/сохранения памяти могут быть выполнены посредством ALUs 212, 214. В одном варианте осуществления, целочисленные ALUs 216, 218, 220 могут выполнять целочисленные операции на 64-разрядных данных операндов. В других вариантах осуществления ALUs 216, 218, 220 могут быть реализованы для поддержки различных размеров битовых данных, включающие в себя шестнадцати, тридцать двух, 128, 256 и т.д. Аналогично, блоки 222, 224 с плавающей точкой могут быть реализованы для поддержки диапазона операндов, имеющие биты различной ширины. В одном варианте осуществления блоки 222, 224 с плавающей точкой могут работать на 128-битовой ширине упакованных данных операндов в сочетании с SIMD и мультимедийными инструкциями.

В одном из вариантов осуществления, uops планировщики 202, 204, 206, отправляют зависимые операции до того, как родительская загрузка завершит выполнение. Как только микрооперации могут быть спекулятивно запланированы и выполнены в процессоре 200, процессор 200 может также включать в себя логику для обработки выпадения в памяти. Если нагрузка данных выпадает из кэша данных, могут быть зависимые операции, проходящие в конвейере, которые покинули планировщик с временно неправильными данными. Механизм воспроизведения отслеживает и повторно выполняет инструкции, которые используют некорректные данные. Только зависимые операции, возможно, должны быть воспроизведены, и независимые могут быть завершены. Планировщики и механизм воспроизведения одного варианта осуществления процессора также могут быть предназначены для захвата последовательностей инструкций для операций сравнения текстовых строк.

Термин «регистры» может относиться к местам хранения встроенного процессора, которые могут быть использованы в качестве части инструкций для идентификации операндов. Другими словами, регистры могут быть те, которые могут быть пригодны для использования вне процессора (с точки зрения программиста). Тем не менее, в некоторых вариантах осуществления регистры могут не быть ограничены конкретным типом схемы. Скорее всего, регистр может хранить данные, предоставлять данные и выполнять функции, описанные в настоящем документе. Регистры, описанные здесь, могут быть реализованы с помощью схемы в пределах процессора с использованием любого числа различных технологий, таких как выделенные физические регистры, динамически распределяемые физические регистры, используя переименование регистров, комбинации выделенных и динамически выделенных физических регистров и т.д. В одном варианте осуществления целочисленные регистры хранят 32-разрядные целочисленные данные. Регистровый файл одного варианта осуществления также содержит восемь мультимедийных SIMD регистров для упакованных данных. Далее приведено описание регистров, которые могут быть описаны, как регистры данных, предназначенные для хранения упакованных данных, такие как 64-битные ММХ™ регистры (также называемые "мм" регистры в некоторых случаях) в микропроцессорах с поддержкой технологии ММХ от Intel Corporation Санта-Клара, штат Калифорния. Эти ММХ регистры, доступные в обоих формах целочисленные и с плавающей точкой, могут работать с элементами упакованных данных, которые сопровождают SIMD и SSE инструкции. Аналогичным образом, 128-битные ХММ регистры, относящиеся к SSE2, SSE3, SSE4 или неописанные (именуемые обобщенно "SSEx") технологией, могут удерживать такие операнды упакованных данных. В одном варианте осуществления при хранении упакованных данных и целочисленных данных, нет необходимости регистрам различать эти два типа данных. В одном из вариантов осуществления и целочисленные, а также и с плавающей точкой могут содержаться в одном регистровом файле или разных регистровых файлах. Кроме того, в одном варианте осуществления целочисленные данные и данные с плавающей точкой могут быть сохранены в различных регистрах или в тех же регистрах.

В примерах, проиллюстрированных на следующих чертежах, описывается количество операндов данных. Фиг. 3A иллюстрирует различные представления упакованных данных в мультимедийных регистрах в соответствии с вариантами осуществления настоящего изобретения. Фиг. 3A иллюстрирует типы данных для упакованного байта 310, упакованного слова 320 и упакованного двойного слова (DWORD) 330 для 128-битных операндов. Формат 310 упакованного байта в этом примере может иметь длину 128 битов и содержит шестнадцать элементов данных упакованного байта. Байт может быть определен, например, как восемь битов данных. Информация для каждого байтового элемента данных может быть сохранена в бите 7 по бит 0 для байта 0, бит 15 по бит 8 для байта 1, бит 23 по бит 16 для байта 2 и, наконец, бит 120 по бит 127 для байта 15. Таким образом, все доступные биты могут быть использованы в регистре. Такая компоновка для хранения повышает эффективность хранения процессора. А также, посредством доступных шестнадцати элементов данных одна операция теперь может быть выполнена на шестнадцати элементах данных параллельно.

В общем случае, элемент данных может включать в себя отдельный элемент данных, который хранится в одном регистре или в ячейке памяти с другими элементами данных такой же длины. В последовательностях упакованных данных, относящихся к технологии SSEx, число элементов данных, сохраненных в регистре ХММ, может быть 128 бит, деленные на длину в битах отдельного элемента данных. Аналогичным образом, в последовательностях упакованных данных, относящихся к ММХ и SSE технологии, число элементов данных, сохраненных в регистре ММХ, может быть 64 бит, деленным на длину в битах отдельного элемента данных. Хотя типы данных, показанные на фиг. 3A, могут быть 128 битовыми в длину, варианты осуществления настоящего изобретения могут также работать с 64-битными или других размеров операндами. Формат 320 упакованного слова этого примера может быть длиной 128 битов и содержит восемь элементов упакованных данных слова. Каждое упакованное слово содержит шестнадцать битов информации. Формат 330 упакованного двойного слова, показанный на фиг. 3A, может иметь длину 128 битов и содержать четыре элемента упакованных данных двойного слова. Каждый упакованный элемент данных двойного слова содержит тридцать два бита информации. Упакованное учетверенное слово может быть длиной 128 битов и содержит два элемента упакованных данных учетверенного слова.

Фиг. 3B иллюстрирует возможные форматы регистрового хранения данных, в соответствии с вариантами осуществления настоящего изобретения. Каждые упакованные данные могут включать в себя более одного независимого элемента данных. Три формата упакованных данных проиллюстрированы; упакованное полуслово 341, упакованное одно слово 342 и упакованное двойное слово 343. В одном из вариантов осуществления упакованное полуслово 341, упакованное одно слово 342 и упакованное двойное слово содержат элементы данных с фиксированной точкой. В качестве другого варианта осуществления упакованное полуслово 341, упакованное одно слово 342 и упакованное двойное слово 343 могут содержать элементы данных с плавающей точкой. Один вариант осуществления упакованного полуслова 341 может быть 128 битный размер, содержащий восемь элементов 16-битовых данных. Один вариант осуществления упакованного одного слова 342 может иметь длину 128 битов и содержит четыре 32-битовых элемента данных. Один вариант осуществления упакованного двойного слова 343 может быть длиной 128 битов и содержит два элемента 64-битовых данных. Следует принять во внимание, что такие форматы упакованных данных могут быть дополнительно распространены на другие длины регистра, например, до 96-бит, 160 бит, 192 бит, 224 бит, 256-бит или более.

Фиг. 3C иллюстрирует различные типы представлений упакованных данных со знаком и беззнаковые в мультимедийных регистрах в соответствии с вариантами осуществления настоящего изобретения. Представление 344 беззнакового упакованного байта иллюстрирует хранение беззнакового упакованного байта в SIMD регистре. Информация для каждого байтового элемента данных может быть сохранена в бите 7 по бит 0 для байта 0, бит 15 по бит 8 для байта 1, бит 23 по бит 16 для байта 2 и, наконец, бит 120 по бит 127 для байта 15. Таким образом, все доступные биты могут быть использованы в регистре. Такая схема компоновки хранения данных может повысить эффективность хранения процессора. А также, посредством доступных шестнадцати элементов данных, одна операция теперь может быть выполнена на шестнадцати элементах данных параллельным способом. Представление 345 упакованного байта со знаком иллюстрирует хранение упакованного байта со знаком. Обратите внимание, что восьмой бит каждого элемента данных байта может быть знаковым индикатором. Представление 346 беззнакового упакованного слова иллюстрирует, как слово семь по слово ноль может храниться в регистре SIMD. Представление 347 упакованного слова со знаком может быть аналогично представлению 346 беззнакового упакованного слова в регистре. Обратите внимание, что шестнадцатый бит каждого элемента данных слова может быть знаковым индикатором. Представление 348 беззнакового упакованного двойного слова показывает, как хранятся элементы данных двойного слова. Представление 349 упакованного двойного слова со знаком может быть аналогично представлению 348 беззнакового упакованного двойного слова в регистре. Обратите внимание, что необходимый знак бита может быть тридцать вторым битом каждого элемента данных двойного слова.

На фиг. 3D показан вариант выполнения операции кодирования (кода операции). Кроме того, формат 360 может включать в себя режимы операнда адресации регистра/памяти, соответствующие типу формата опкода, описанный в "Руководстве том 2 IA-32 разработчика архитектуры программного обеспечения Intel: Описание набора основных команд", которое предоставлено Intel Corporation, Санта-Клара, штат Калифорния во Всемирной паутине (WWW) на intel.com/design/litcentr. В одном из вариантов осуществления инструкция может быть закодирована с помощью одного или нескольких из полей 361 и 362. Может быть идентифицировано до двух местоположений операндов на инструкцию, включающие в себя до двух идентификаторов 364 и 365 источника операндов. В одном варианте осуществления идентификатор 366 операнда назначения может быть таким же, как идентификатор 364 операнда источника, в то время как в других вариантах осуществления они могут быть различными. В другом варианте осуществления идентификатор 366 операнда назначения может быть таким же, как идентификатор 365 операнда источника, в то время как в других вариантах они могут быть разными. В одном из вариантов осуществления, один из операндов источника, идентифицированных идентификаторами 364 и 365 операнда источника, могут быть перезаписаны по результатам операции сравнения текстовой строки, тогда как в других вариантах осуществления идентификатор 364 соответствует элементу исходного регистра, и идентификатор 365 соответствует элементу регистра назначения. В одном варианте осуществления идентификаторы 364 и 365 операндов могут идентифицировать 32-битный или 64-битный операнды источника и назначения.

На фиг. 3E показан другой возможный формат 370 операции кодирования (код операции), имеющий сорок или более битов, в соответствии с вариантами осуществления настоящего изобретения. Формат 370 кода операции соответствует формату 360 кода операции и содержит возможный байт 378 префикса. Инструкция, согласно одному варианту осуществления, может кодироваться одним или несколькими из полей 378, 371 и 372. Могут быть идентифицированы до двух местоположений операндов на инструкцию с помощью идентификаторов 374 и 375 операнда источника и префиксом байта 378. В одном варианте префикс байт 378 может быть использован для идентификации 32-битных или 64-битных операндов источника и назначения. В одном варианте осуществления идентификатор 376 операнда назначения может быть таким же, как идентификатор 374 операнда источника, в то время как в других вариантах осуществления они могут быть различными. В качестве другого варианта осуществления, идентификатор 376 операнда назначения может быть таким же, как идентификатор 375 операнда источника, в то время как в других вариантах осуществления они могут быть различными. В одном варианте осуществления, инструкция работает на одном или нескольких операндах, идентифицированных посредством идентификаторов 374 и 375 операндов, и на одном или более операндах, идентифицированных посредством идентификаторов 374 и 375 операндов, которые могут быть перезаписаны результатами инструкции, в то время как в других вариантах осуществления, операнды, идентифицированные идентификаторами 374 и 375, могут быть записаны на другой элемент данных в другой регистр. Форматы 360 и 370 опкода позволяют записывать в регистр, память в регистр, записывать посредством памяти, записывать посредством регистра, записывать немедленно, записывать посредством получения адресация памяти, указанной в части MOD полей 363 и 373, и возможно масштабированием и смещением байтов.

На фиг. 3F иллюстрируется еще один возможный формат операции кодирования (код операции), в соответствии с вариантами осуществления настоящего изобретения. 64-разрядные арифметические операции архитектуры с одним потоком команд и многими потоками данных (SIMD) могут выполняться с помощью инструкции обработки данных сопроцессора (CDP). Формат 380 операции кодирования (код операции) изображает одну такую CDP инструкцию, имеющую поля 382- 389 CDP опкода. Тип инструкции CDP, для другого варианта осуществления, операции может быть закодирован с помощью одного или нескольких из полей 383, 384, 387 и 388. Могут быть идентифицированы вплоть до трех мест операндов на инструкцию, включающие в себя до двух идентификаторов 385 и 390 операнда источника и один идентификатор 386 операнда назначения. Один из вариантов осуществления сопроцессора может работать на восьми, шестнадцати, тридцати двух и 64-битовых значениях. В одном варианте осуществления инструкция может быть выполнена на целочисленных элементах данных. В некоторых вариантах осуществления инструкция может быть выполнена условно, используя поле 381 условия. В некоторых вариантах осуществления размеры данных источника могут быть закодированы с помощью поля 383. В некоторых вариантах осуществления направления ноль (Z), отрицательный (N), нести (С) и переполнение (V) могут быть выполнены на SIMD полях. Для некоторых инструкций тип насыщения может кодироваться полем 384.

На фиг. 4А представлена блок-схема, иллюстрирующая упорядоченный конвейер и этап переименования регистров, конвейер с изменением последовательности команд, в соответствии с вариантами осуществления настоящего изобретения. На фиг. 4B показана блок-схема, иллюстрирующая упорядоченную архитектуру ядра и логику переименования регистров, логику с изменением последовательности команд, которые будут включены в состав процессора, в соответствии с вариантами осуществления настоящего изобретения. Квадраты, очерченные сплошной линией на фиг. 4А, иллюстрируют упорядоченный конвейер, в то время как квадраты, очерченные пунктирной линией, иллюстрируют переименование регистров, конвейер с изменением последовательности команд. Точно так же, квадраты, очерченные сплошной линией на фиг. 4B иллюстрируют упорядоченную архитектуру логики, в то время как квадраты, очерченные пунктирной линией, иллюстрируют логику переименования регистров и логику с изменением последовательности команд.

На фиг. 4А, процессор конвейера 400 может включать в себя этап 402 выборки, этап 404 декодирования длины, этап 406 декодирования, этап 408 выделения, этап 410 переименования, этап 412 планирования (также известный, как отправки или выдачи), этап 414 чтения регистра чтение/память, этап 416 выполнения, этап 418 обратной записи/запись памяти, этап 422 обработки исключений и этап 424 завершения.

На фиг. 4B стрелки обозначают соединения между двумя или более блоками и направление стрелки указывает направление потока данных между этими блоками. Фиг. 4B показывает ядро 490 процессора, включающее в себя коммуникационный процессор 430, соединенный с исполнительным блоком 450, и оба они могут быть соединены с блоком 470 памяти.

Ядро 490 может быть ядром с сокращенным набором команд (RISC), ядром со сложным набором команд (CISC), ядром с очень длинным командным словом (VLIW) или гибридным или альтернативным типом ядра. В одном варианте осуществления ядро 490 может быть ядром специального назначения, таким как, например, сетевым или коммуникационным ядром, устройством сжатия, графическим ядром или тому подобное.

Коммуникационный процессор 430 может включать в себя блок 432 предсказания ветвлений, соединенный с блоком 434 кэш команд. Блок 434 кэш команд может быть соединен с буфером 436 быстрого преобразования адреса (TLB). TLB 436 может быть соединен с блоком 438 выборки инструкций, который соединен с блоком 440 декодирования. Блок 440 декодирования может декодировать инструкции и генерировать в качестве выходной одной или нескольких микроопераций, точки входа микрокода, микрокоманды, другие инструкции или другие управляющие сигналы, которые могут быть декодированы, или иным образом отражать, или могут быть получены из исходных инструкций. Декодер может быть реализован с использованием различных механизмов. Примеры подходящих механизмов включают в себя, но не ограничиваются ими, просмотровые таблицы, аппаратные реализации, программируемые логические матрицы (PLAs), постоянная память микрокода (ROM) и т.п. В одном варианте осуществления блок 434 кэш команд может быть дополнительно соединен с блоком 476 уровня 2 (L2) кэш в блоке 470 памяти. Блок 440 декодирования может быть соединен с блоком 452 переименования/распределителя в исполнительном блоке 450.

Исполнительный блок 450 может включать в себя блок 452 переименования/распределителя, соединенный с блоком 454 удаления и набором из одного или нескольких блоков 456 планировщика. Блоки 456 планировщика представляют любое количество различных планировщиков, включающие в себя резервирование станций, окно центральной инструкции и т.д. Блоки 456 планировщика могут быть соединены с блоками 458 физического регистрового файла. Каждый из блоков 458 физического регистрового файла представляет один или несколько физических регистровых файлов, отличные от тех, которые хранят один или несколько различных типов данных, таких как скалярное целое, скалярное с плавающей точкой, упакованное целое, упакованное с плавающей точкой, вектор целое, вектор с плавающей точкой и т.д., статус (например, указатель команд, т.е. адрес следующей инструкции для выполнения) и т.д. Блоки 458 физического регистрового файла могут быть перекрыты блоком 154 удаления для иллюстрации различных способов, в которых используется переименование регистров и изменение последовательности команд (например, используя один или несколько будущих файлов, буферов переупорядочивания и один или более регистровых файлов удаления, используя один или несколько схем размещения файлов, один или несколько буферов истории; и пул регистров; и т.д.). Как правило, архитектурные регистры могут быть видны вне процессора или с точки зрения программиста. Регистры не могут быть ограничены каким-либо известным конкретным типом схемы. Различные типы регистров могут быть пригодны до тех пор, как они хранят и предоставляют данные, как описано в настоящем документе. Примеры подходящих регистров включают в себя, но не могут быть ограничены, выделенные физические регистры, динамически выделенные физические регистры с использованием переименование регистров, комбинации выделенных и динамически выделенных физических регистров и т.д. Блок 454 удаления и блоки 458 физического регистрового файла могут быть соединены с исполнительными кластерами 460. Исполнительные кластеры 460 могут включать в себя набор из одного или нескольких исполнительных блоков 162 и набор из одного или нескольких блоков 464 доступа к памяти. Исполнительные блоки 462 могут выполнять различные операции (например, сдвиги, сложение, вычитание, умножение) и на различных типах данных (например, скалярное число с плавающей точкой, упакованное целое, упакованное с плавающей точкой, вектор-целое, вектор с плавающей точкой). В то время, как некоторые варианты осуществления могут включать в себя ряд исполнительных блоков, предназначенных для выполнения определенных функций или набора функций, другие варианты осуществления могут включать в себя только один исполнительный блок или несколько исполнительных блоков, которые все выполняют все функции. Блоки 456 планировщика, блоки 458 физического регистрового файла и исполнительные кластеры 460 показаны как, возможно, во множественном числе, потому что некоторые варианты осуществления создают отдельные конвейеры для определенных типов данных/операций (например, конвейер скалярного целого, конвейер скалярного с плавающей точкой/упакованного целого/ упакованного с плавающей точкой/вектор целого/вектор с плавающей точкой и/или конвейер доступа к памяти, что у каждого есть свой собственный блок планировщик, блок физического регистрового файла и/или исполнительный кластер - и в случае отдельного конвейера доступа к памяти, некоторые варианты осуществления могут быть реализованы, в которых только исполнительный кластер этого конвейера имеет блоки 464 доступа к памяти). Следует также понимать, что там, где используются отдельные конвейеры, один или несколько из этих конвейеров может быть с изменением последовательности команд и остальные являются упорядоченными.

Набор блоков 464 доступа к памяти может быть соединен с блоком 470 памяти, который может включать в себя TLB блок 472 данных, соединенный с блоком 474 кэша данных, соединенный с блоком 476 2-го уровня (L2) кэш. В одном примерном варианте осуществления, блоки 464 доступа к памяти могут включать в себя блок нагрузки, блок адреса хранения и блок хранения данных, каждый из которых может быть связан с TLB блоком 472 данных в блоке 470 памяти. Блок 476 L2 кэш может быть соединен с одним или более других уровнях кэш-памяти и, в конечном счете, с основной памятью.

В качестве примера, примерное переименование регистров, архитектура ядра с изменением последовательности команд может реализовать конвейер 400 следующим образом: 1) блок 438 выборки команд может выполнять выборку и этапы 402 и 404 выборки и декодирования длины 402 и 404; 2) блок 440 декодирования может выполнять этап 406 декодирования; 3) блок 452 переименования/распределитель может выполнить этап 408 распределения и этап 410 переименования; 4) блоки 456 планировщика могут выполнять этап 412 планирования; 5) блоки 458 физического регистрового файла и блок 470 памяти могут выполнять этап 414 чтения регистра чтения/памяти; исполнительный кластер 460 может выполнять этап 416 выполнения; 6) блок 470 памяти и блоки 458 физического регистрового файла могут выполнять этап 418 обратной записи/записи памяти; 7) различные блоки могут быть вовлечены в выполнение этапа 422 исключения; и 8) блок 454 удаления и блоки 458 физического регистрового файла могут выполнять этап 424 завершения.

Ядро 490 может поддерживать один или несколько наборов команд (например, набор команд х86 (с некоторыми расширениями, которые были добавлены в более новые версии); MIPS набор инструкций, MIPS Technologies Sunnyvale, СА; набор команд ARM (с возможными дополнительными расширениями, такими как NEON) ARM Holdings Sunnyvale, СА).

Следует понимать, что ядро может поддерживать многопоточный режим передачи данных (выполняя два или более параллельных набора операций или потоков) различными способами. Поддержка многопоточной передачи данных может быть выполнена, например, посредством многопоточной обработки с квантованием времени, одновременной многопоточной обработкой (где одно физическое ядро обеспечивает логическое ядро для каждого из потоков, где физическое ядро одновременно выполняет многопоточный режим) или их комбинации. Такое сочетание может включать в себя, например, выборку с квантованием времени, декодирование и одновременный многопоточный режим, например, в технологии Intel® Hyperthreading.

В то время, как переименование регистров может быть описано в контексте выполнения операций с изменением последовательности команд, следует понимать, что переименование регистров может быть использовано в упорядоченной архитектуре. Хотя показанный вариант осуществления процессора может также включать в себя отдельные блоки 434/474 инструкций и кэш данных и совместно использовать блок 476 L2 кэша, другие варианты осуществления могут иметь один внутренний кэш, как для инструкций, так и для данных, таких как, например, уровень 1 (LI) внутренний кэш или множество уровней внутреннего кэша. В некоторых вариантах осуществления система может включать в себя комбинацию внутреннего кэша и внешнего кэша, которая может быть внешним по отношению к ядру и/или процессору. В других вариантах осуществления все из кэша может быть внешним по отношению к ядру и/или процессору.

На фиг. 5А показана блок-схема процессора 500, в соответствии с вариантами осуществления настоящего изобретения. В одном варианте осуществления, процессор 500 может включать в себя многоядерный процессор. Процессор 500 может включать в себя системного агента 510, соединенного с возможностью взаимодействия с одним или более ядер 502. Кроме того, ядра 502 и системный агент 510 могут быть коммуникативно соединены с одним или более кэшей 506. Ядра 502, системный агент 510 и кэш 506 могут быть функционально подсоединены с помощью одного или нескольких блоков 552 управления памятью. Кроме того, ядра 502, системный агент 510 и кэш 506 могут быть коммуникативно соединены с модулем 560 графики с помощью блоков 552 управления памятью.

Процессор 500 может включать в себя любой подходящий механизм для соединения ядер 502, системного агента 510, кэша 506 и модуля 560 графики. В одном варианте осуществления процессор 500 может включать в себя блок 508 кольцевого межсоединения для соединения ядер 502, системного агента 510, кэш 506 и модуля 560 графики. В других вариантах осуществления процессор 500 может включать в себя любое число хорошо известных способов для взаимного соединения таких блоков. Блок 508 кольцевого межсоединения может использовать блоки 552 управления памятью для облегчения взаимосвязи.

Процессор 500 может включать в себя иерархию памяти, содержащую один или несколько уровней кэшей внутри ядер, одно или несколько общих блоков кэша, таких как кэш 506 или внешняя память (не показано), соединенную с набором блоков 552 интегрированного контроллера памяти. Кэш 506 может включать в себя любой подходящий кэш. В одном варианте осуществления кэш 506 может включать в себя один или несколько кэш среднего уровня, такие как 2-го уровня (L2), 3-го уровня (L3), 4-го уровня (L4) или другие уровни кэша, кэш последнего уровня (LLC) и/или их комбинации.

В различных вариантах осуществления одно или более ядер 502 может выполнять многопоточную передачу данных. Системный агент 510 может включать в себя компоненты для координации действий и операционные ядра 502. Блок 510 системного агента может включать в себя, например, блок управления мощностью (PCU). PCU может представлять собой или включать в себя логическую схему и компоненты, необходимые для регулирования состояния питания ядер 502. Системный агент 510 может включать в себя блок 512 отображения для управления одним или несколькими подключенными внешними дисплеями или модулем 560 графики. Системный агент 510 может включать в себя интерфейс 1214 для шины связи для графики. В одном варианте осуществления интерфейс 1214 может быть реализован с помощью PCI Express (PCIe). В еще одном варианте осуществления интерфейс 1214 может быть реализован с помощью шины PCI Express Graphics (PEG). Системный агент 510 может включать в себя прямой медиа-интерфейс (DMI) 516. DMI 516 может обеспечивать связь между различными мостами на материнской плате или другой части компьютерной системы. Системный агент 510 может включать в себя PCIe мост 1218 для обеспечения PCIe связи с другими элементами вычислительной системы. PCIe мост 1218 может быть реализован с помощью контроллера 1220 памяти и логикой 1222 когерентности.

Ядра 502 могут быть реализованы любым подходящим образом. Ядра 502 могут быть гомогенными или гетерогенными с точки зрения архитектуры и/или набора команд. В одном из вариантов осуществления, некоторые из ядер 502 могут быть упорядоченными, в то время как другие могут быть с изменением последовательности команд. В другом варианте осуществления два или более ядер 502 могут выполнять один и тот же набор команд, в то время как другие могут выполнять только подмножество этого набора команд или другого набора команд.

Процессор 500 может включать в себя процессор общего назначения, например, Core™ i3, i5, i7, 2 Duo и Quad, Xeon™, Itanium™, XScale™ или процессор StrongARM™, который может быть предоставлен Intel Corporation, Санта-Клара, Калифорния. Процессор 500 может быть получен из другой компании, такой как ARM Holdings, Ltd, MIPS и т.д. Процессор 500 может быть процессором специального назначения, такие как, например, сетевой или коммуникационный процессор, сжатия, графический процессор, сопроцессор, встроенный процессор или тому подобное. Процессор 500 может быть реализован на одном или более микросхемах. Процессор 500 может быть частью и/или может быть реализован на одной или более подложках с использованием любого из ряда технологических процессов, таких как, например, BiCMOS, CMOS или NMOS.

В одном варианте осуществления заданный один из кэшей 506 может использоваться несколькими ядрами 502. В другом варианте осуществления заданный один кэш 506 может быть выделен одному из ядер 502. Назначение кэшей 506 ядрам 502 может быть обработано с помощью контроллера кэша или другого подходящего механизма. Заданный один из кэшей 506 может быть совместно использован двумя или более ядрами 502 путем осуществления квантования времени заданного кэша 506.

Графический модуль 560 может реализовать интегрированную подсистему обработки графики. В одном варианте осуществления модуль 560 графики может включать в себя графический процессор. Кроме того, графический модуль 560 может включать в себя медиа-блок 565. Медиа-блок 565 может обеспечить кодирование медиа информации и декодирование видео.

На фиг. 5B показана блок-схема примерного варианта реализации ядра 502, в соответствии с вариантами осуществления настоящего изобретения. Ядро 502 может включать в себя магистральный процессор 570, соединенный, с возможностью взаимодействия, с блоком 580 выполнения с изменением последовательности команд. Ядро 502 может быть коммуникативно соединено с другими частями процессора 500 через иерархию 503 кэш-памяти.

Магистральный процессор 570 может быть реализован любым подходящим способом, таким как полностью или частично магистральным процессором 201, как описано выше. В одном из вариантов осуществления, магистральный процессор 570 может осуществлять связь с другими частями процессора 500 через иерархию кэш-памяти 503. В другом варианте осуществления магистральный процессор 570 может извлекать инструкции из частей процессора 500 и подготовить инструкции, которые будут использованы в дальнейшем в процессоре конвейера, поскольку они передаются в блок 580 выполнения с изменением последовательности команд.

Блок 580 выполнения с изменением последовательности команд может быть реализован любым подходящим способом, таким как полностью или частично блока 203 выполнения с изменением последовательности команд, как описано выше. Блок 580 выполнения с изменением последовательности команд может подготовить инструкции, полученные от магистрального процессора 570 для исполнения. Блок 580 выполнения с изменением последовательности может включать в себя модуль 1282 распределения. В одном из вариантов осуществления модуль 1282 распределения может распределять ресурсы процессора 500 или других ресурсов, таких, как регистры или буферы, чтобы выполнить данную инструкцию. Модуль 1282 распределения может выполнить распределение в планировщиках, таких как планировщик памяти, быстрый планировщик, или планировщик с плавающей точкой. Такие планировщики могут быть представлены на фиг. 5B планировщиками 584 ресурсов. Модуль 1282 распределения может быть полностью или частично реализован посредством логики распределения, описанной на фиг. 2. Планировщики 584 ресурсов реализуются, когда инструкция готова к выполнению, на основании готовности заданных источников ресурсов и наличием исполнительных ресурсов, необходимых для выполнения инструкции. Планировщики 584 ресурсов могут быть реализованы, например, планировщиками 202, 204, 206, как описано выше. Планировщики 584 ресурсов могут запланировать выполнение инструкций относительно одного или нескольких ресурсов. В одном варианте осуществления такие ресурсы могут быть внутренними по отношению к ядру 502, и могут быть проиллюстрированы, например, как ресурсы 586. В другом варианте осуществления такие ресурсы могут быть внешними по отношению к ядру 502 и могут быть доступны, например, посредством иерархии 503 кэша. Ресурсы могут включать в себя, например, память, кэш, файлы регистров или регистры. Внутренние ресурсы для ядра 502 могут быть представлены ресурсами 586 на фиг. 5B. По мере необходимости, значения, записываемые или считываемые из ресурсов 586, могут быть согласованы с другими частями процессора 500 с помощью, например, иерархии 503 кэш. Так как инструкции назначены ресурсами, они могут быть помещены в буфер 588 переупорядочивания. Буфер 588 переупорядочивания может отслеживать инструкции, как они выполняются, и может выборочно изменять порядок их выполнения, основываясь на любых подходящих критериях процессора 500. В одном варианте осуществления, буфер 588 переупорядочивания может идентифицировать инструкции или последовательности инструкций, которые могут быть выполнены независимо друг от друга. Такие инструкции или последовательности инструкций могут выполняться параллельно с другими такими инструкциями. Параллельное выполнение в ядре 502 может быть выполнено любым подходящим количеством отдельных исполнительных блоков или виртуальных процессоров. В одном из вариантов осуществления, совместно используемые ресурсы, такие как память, регистры и кэш могут быть доступны для нескольких виртуальных процессоров в пределах данного ядра 502. В других вариантах осуществления, совместно используемые ресурсы могут быть доступны для нескольких объектов обработки в процессоре 500.