Результат интеллектуальной деятельности: УПРАВЛЕНИЕ ПАМЯТЬЮ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Настоящее изобретение в целом относится к области электроники. Более конкретно, некоторые варианты осуществления изобретения в целом относятся к управлению памятью в электронных устройствах.

Уровень техники

Многие электронные устройства включают в себя системы памяти, которые могут быть реализованы с использованием локальной быстродействующей памяти, которая часто реализуется в виде энергозависимой памяти, например, динамическая оперативная память (DRAM) или тому подобное. Отключение питания электронного устройства вызывает сброс энергозависимой памяти в устройстве, как правило, до нуля. Таким образом, с большой вероятностью можно утверждать, что при перезагрузке операционных систем устройства локальная быстродействующая память не будет содержать данных.

Краткое описание чертежей

Подробное описание приведено со ссылками на прилагаемые чертежи. Одинаковые ссылочные позиции на различных чертежах указывают подобные или идентичные элементы.

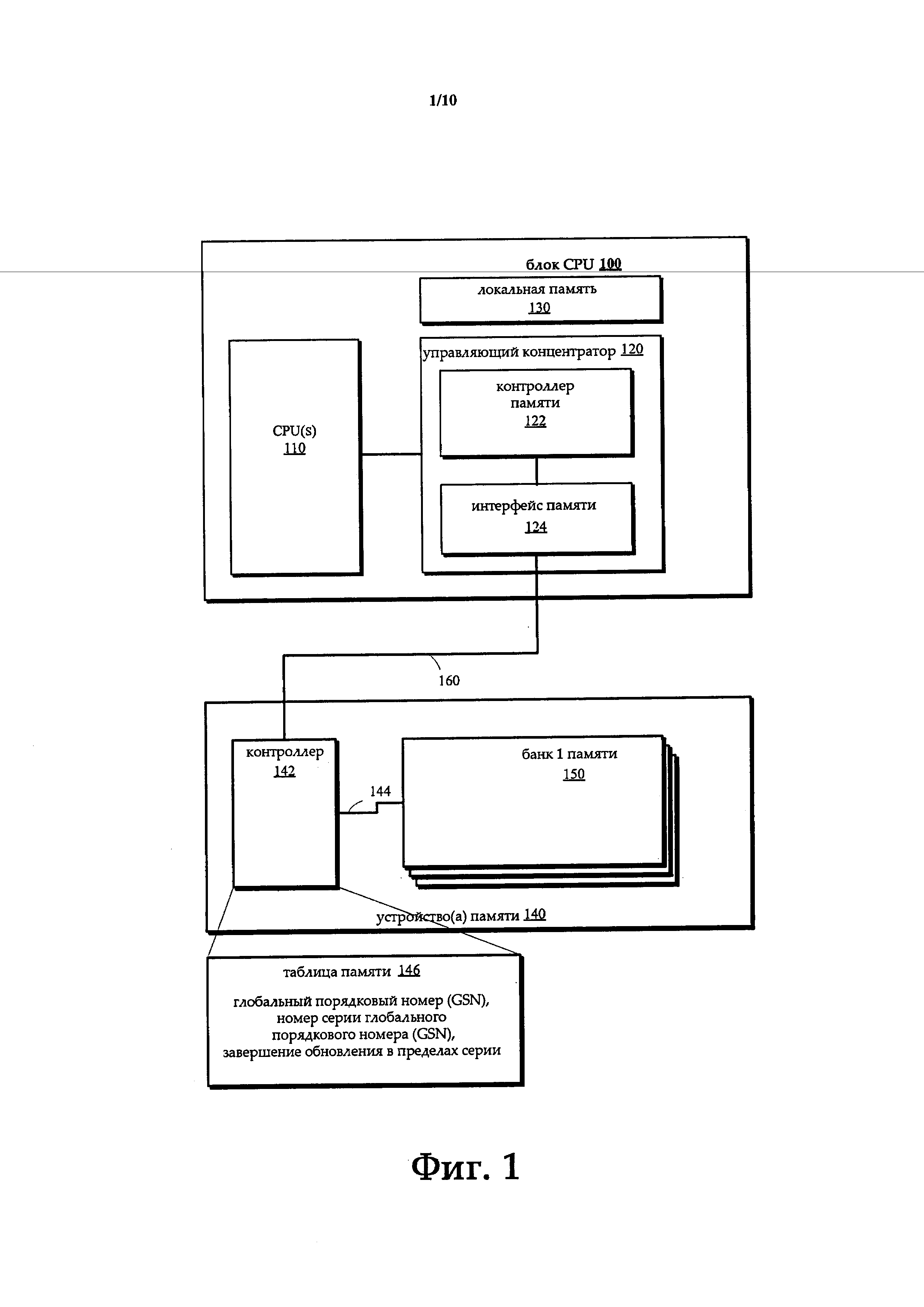

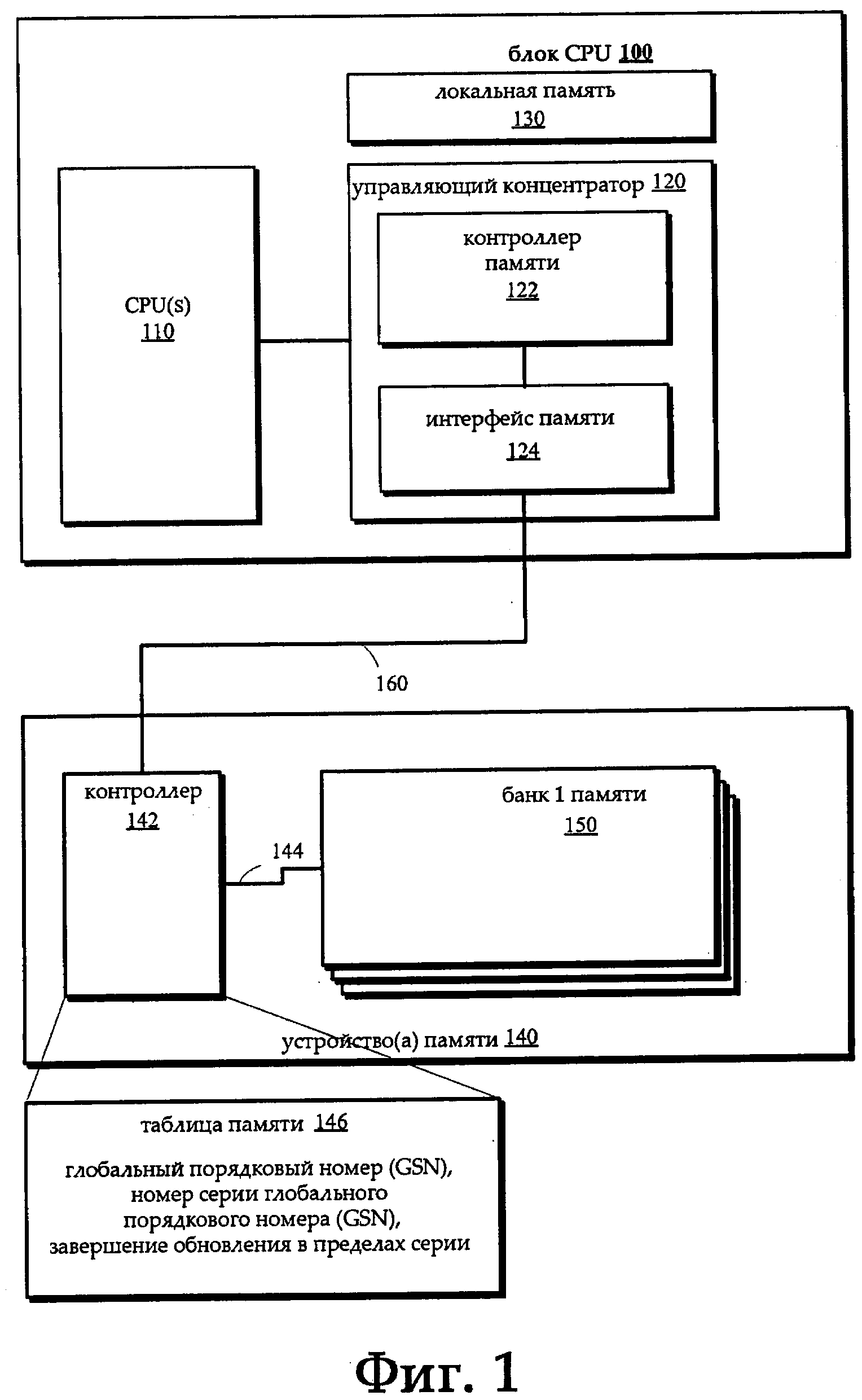

Фиг. 1 представляет собой схематическую блок-схему, иллюстрирующую компоненты устройства для осуществления управления памятью в соответствии с описанными здесь различными вариантами осуществления.

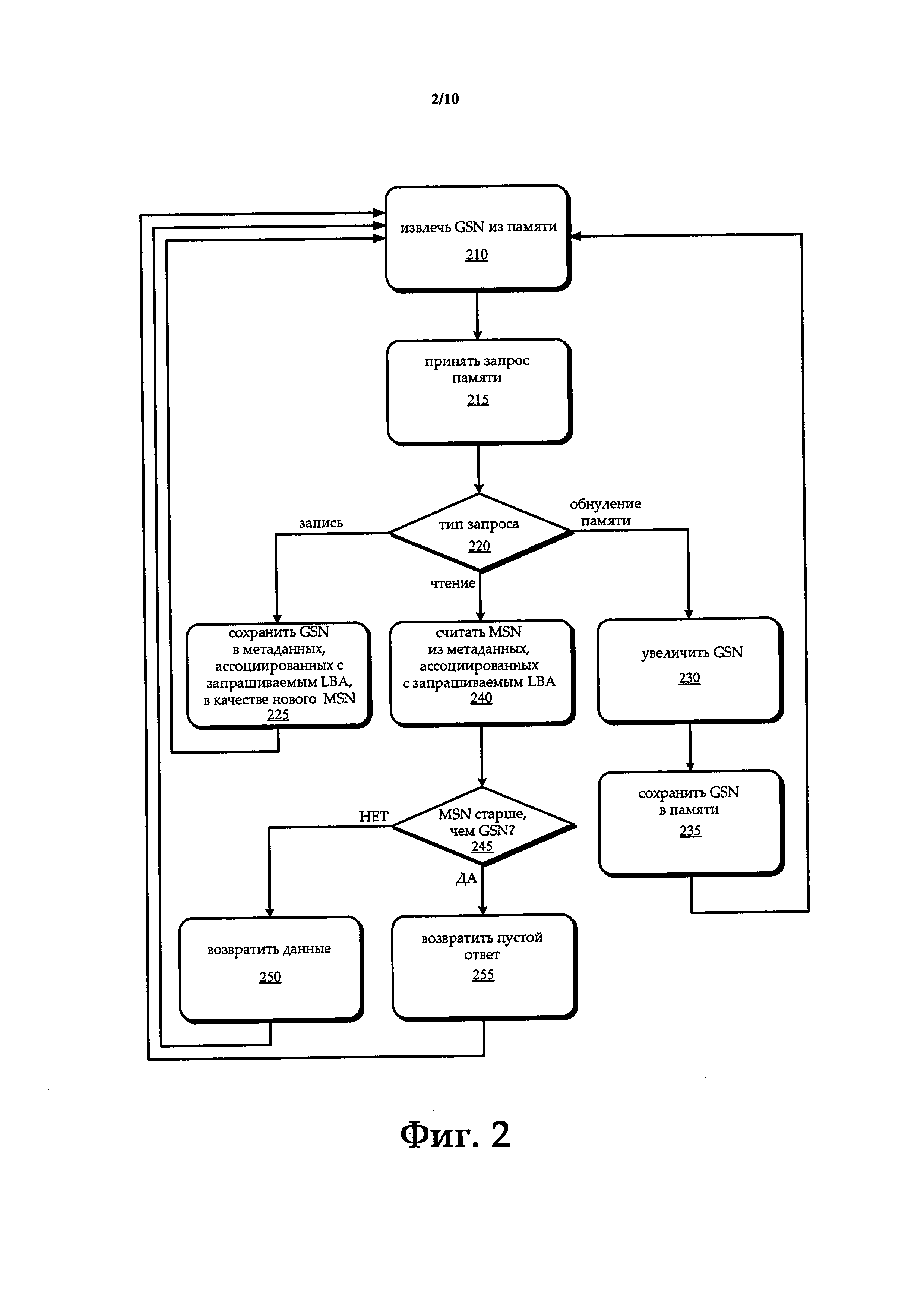

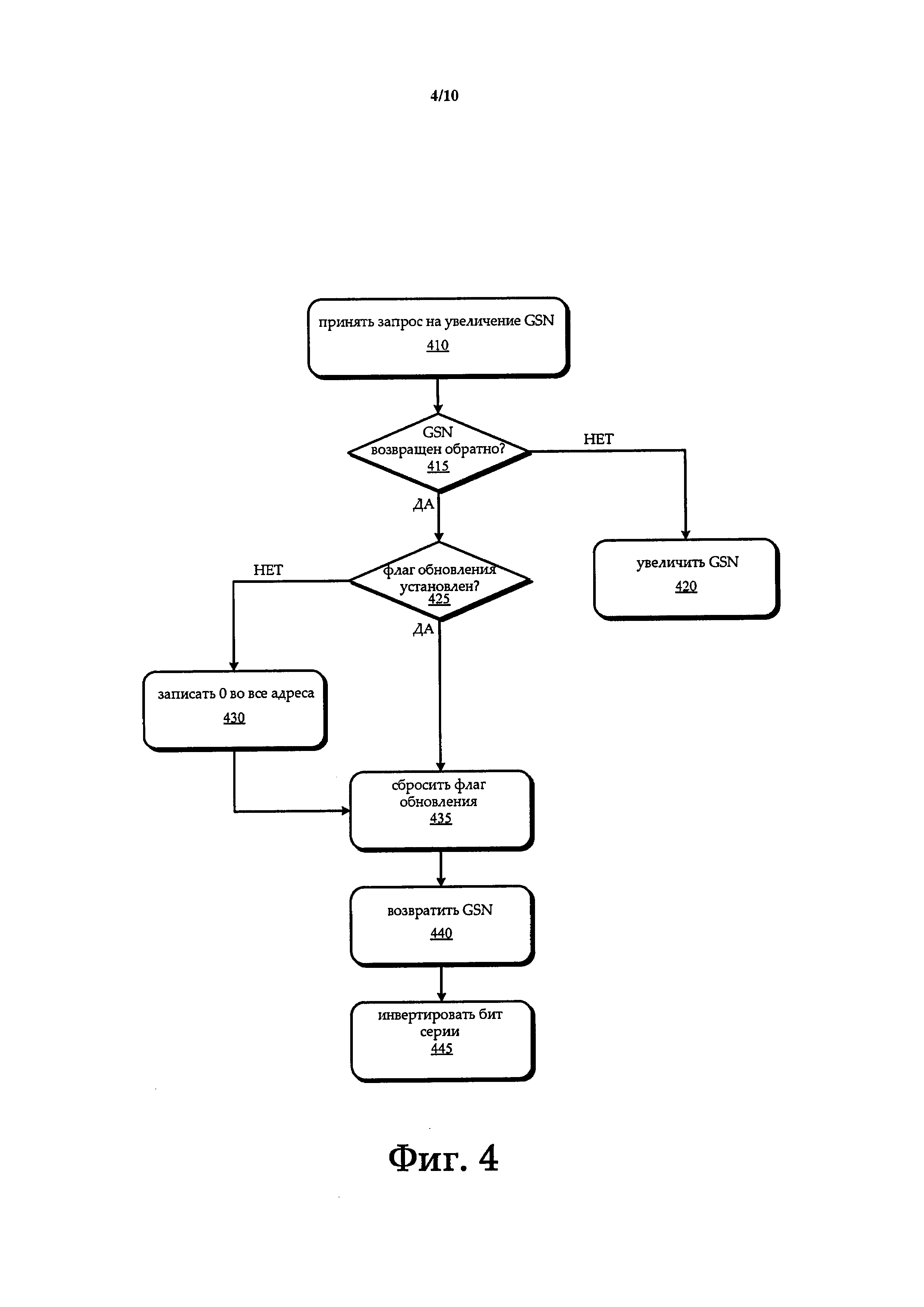

Фиг. 2 и 4 являются блок-схемами алгоритма, иллюстрирующие операции способа управления памятью в соответствии с описанными здесь различными вариантами осуществления.

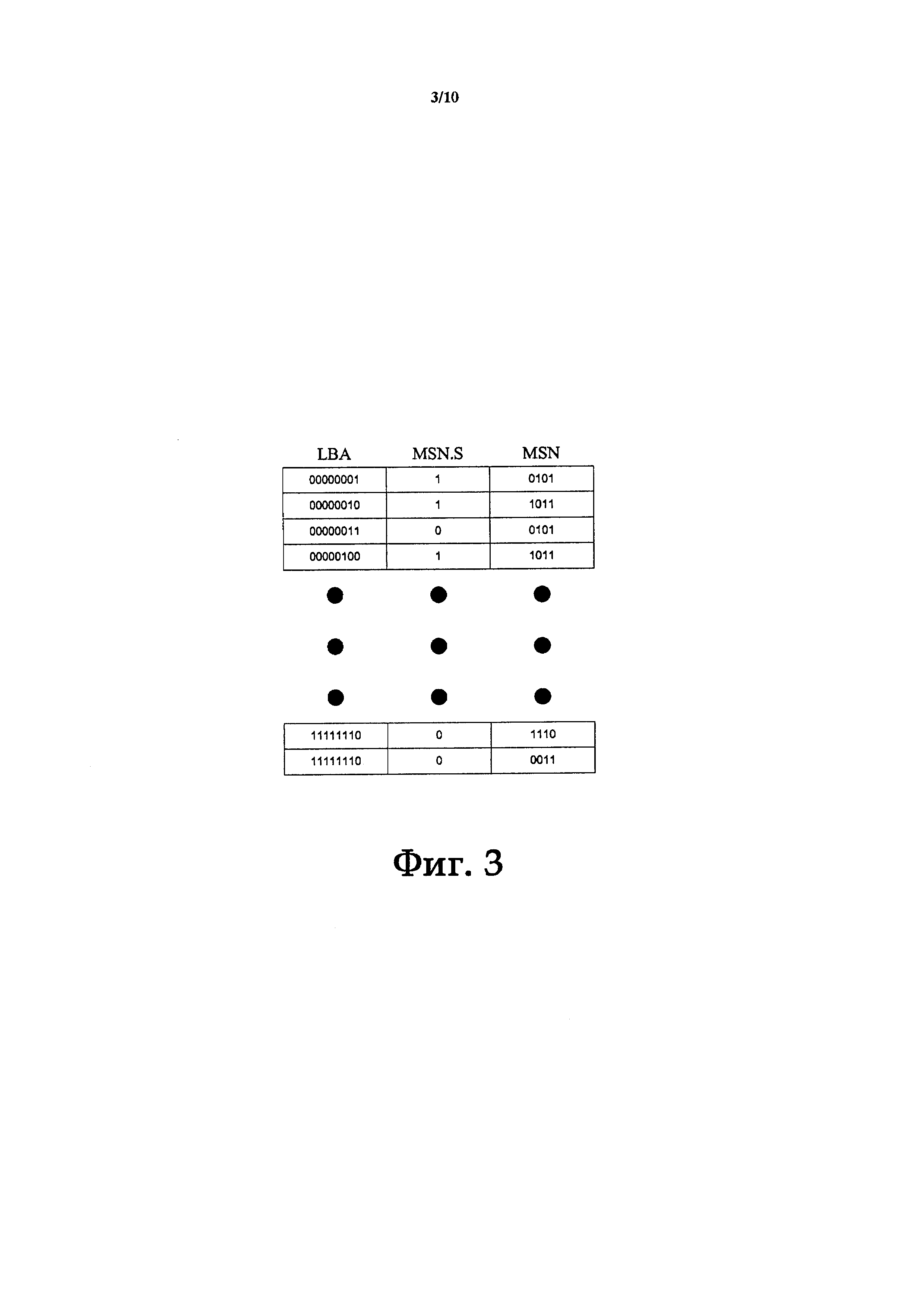

Фиг. 3 показывает таблицу метаданных, которые могут быть использованы для реализации управления памятью в соответствии с описанными здесь различными вариантами осуществления.

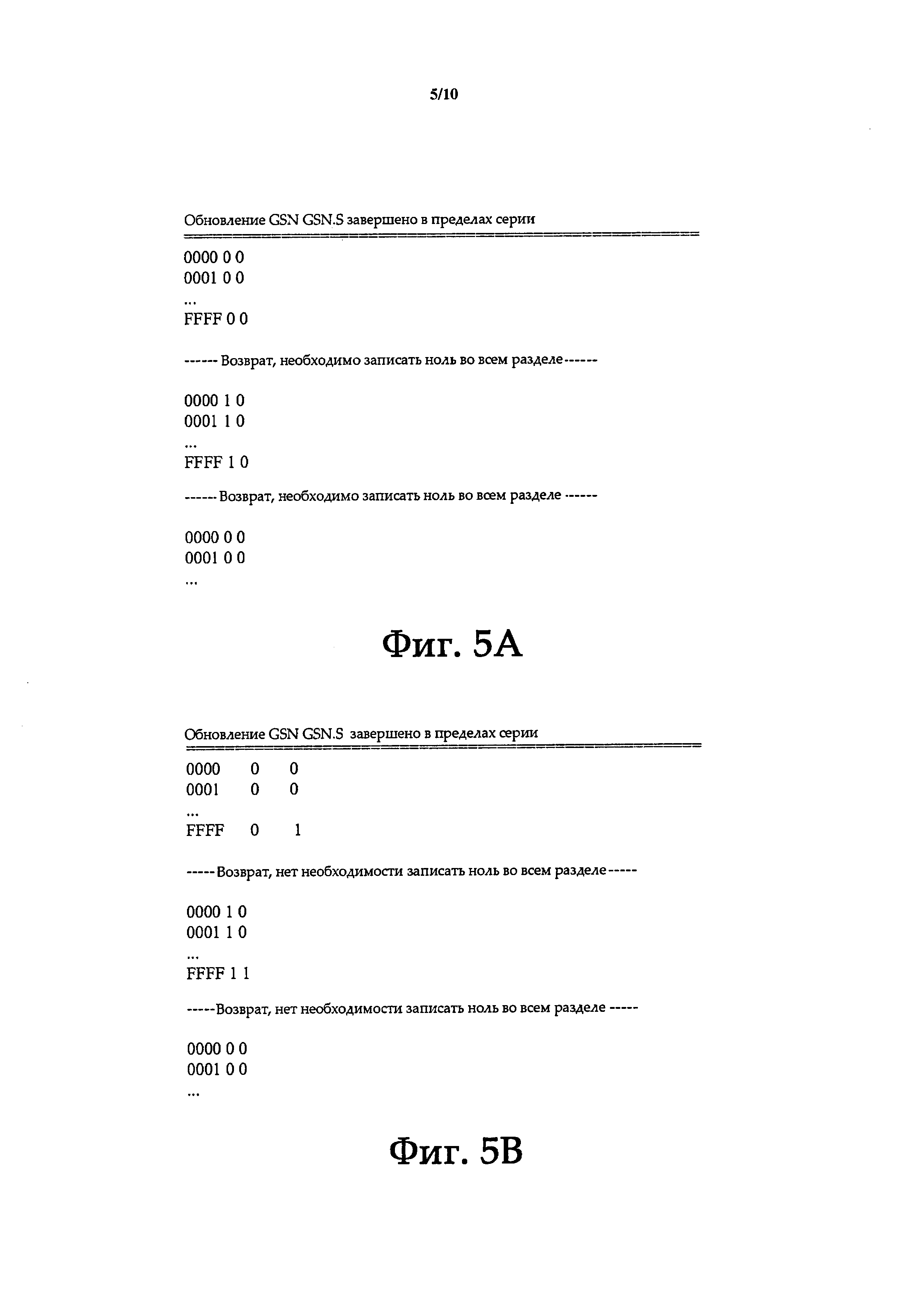

Фиг. 5 и 5B изображают схематические иллюстрации порядковых номеров, которые могут быть использованы в операциях способа осуществления управления задержкой доступа к памяти в соответствии с описанными здесь различными вариантами осуществления.

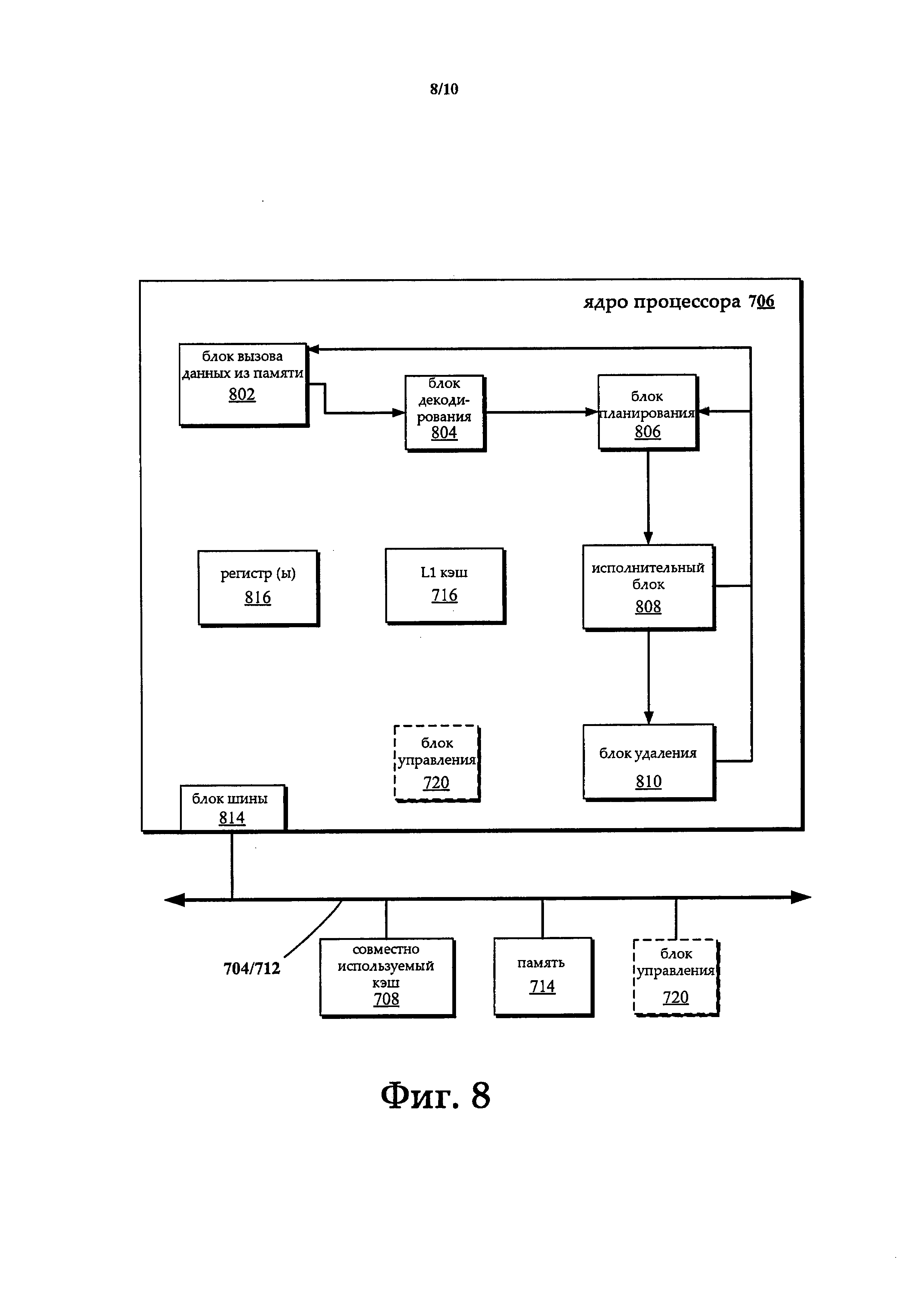

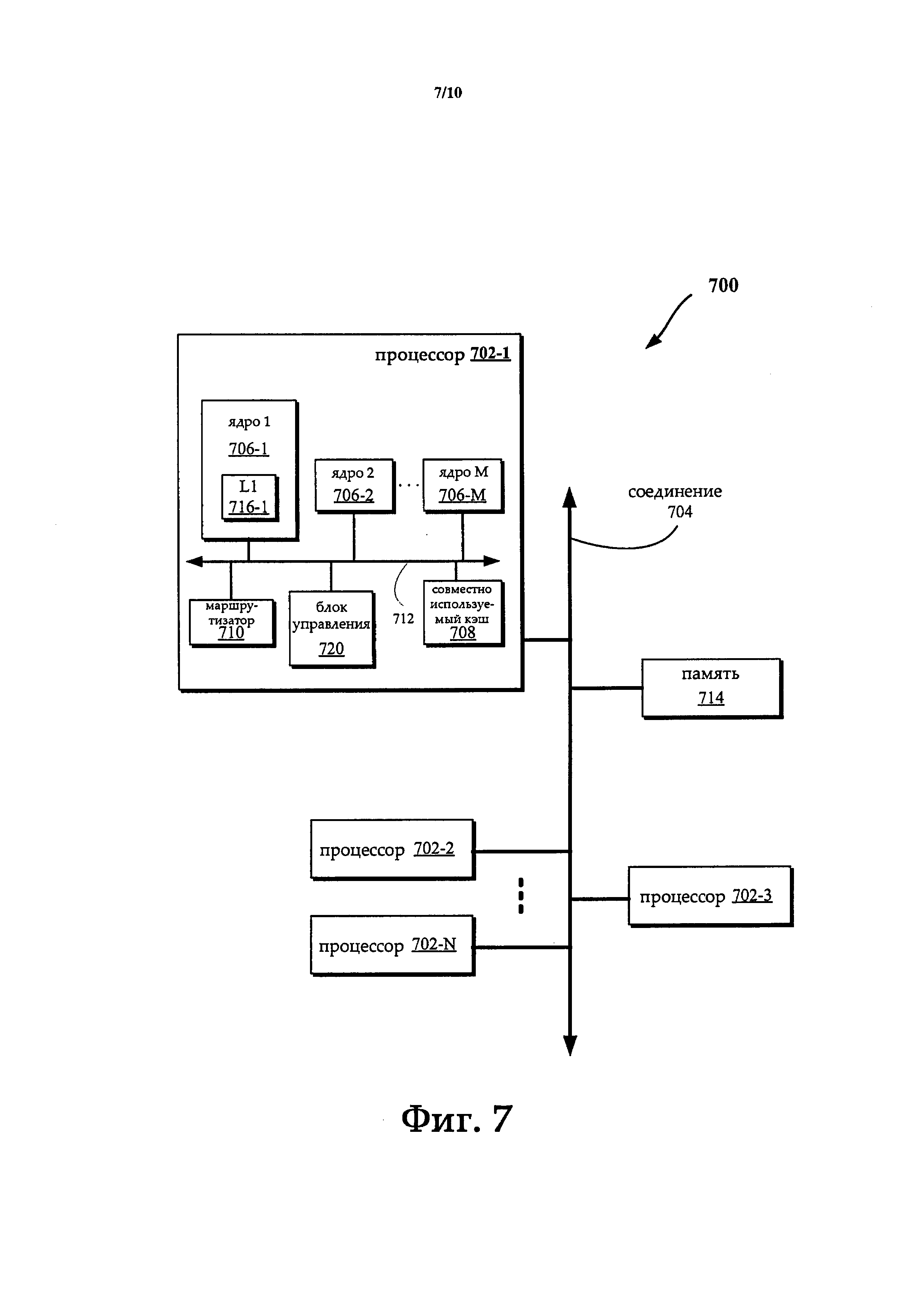

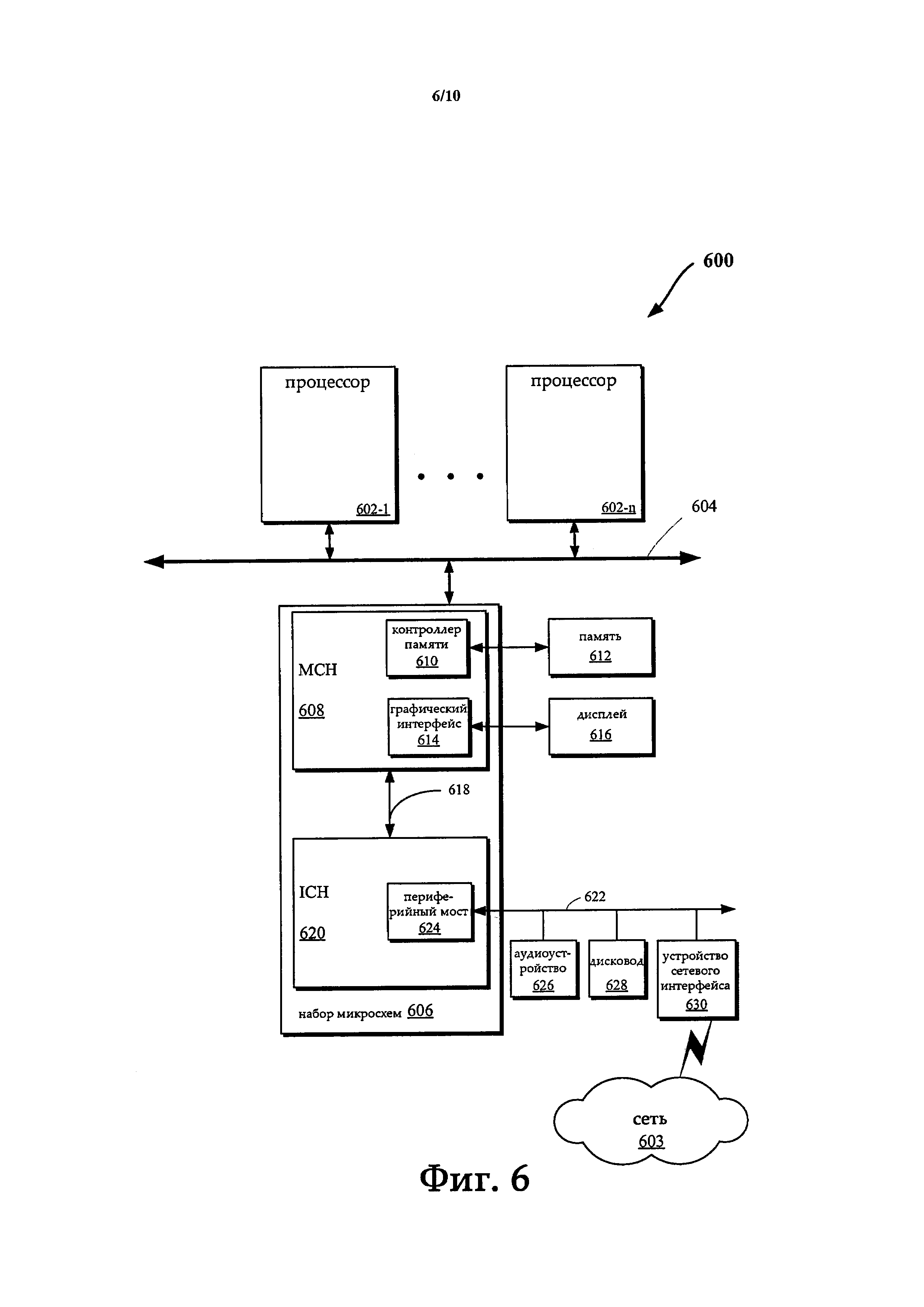

Фиг. 6-10 являются схематичными блок-схемами иллюстраций электронных устройств, которые могут быть выполнены с возможностью реализовывать управление задержкой доступа к памяти в соответствии с описанными здесь различными вариантами осуществления.

Подробное описание

В следующем описании многочисленные конкретные детали изложены для того, чтобы обеспечить полное понимание различных вариантов осуществления. Тем не менее, различные варианты осуществления изобретения могут быть осуществлены без конкретных деталей. В других случаях хорошо известные способы, процедуры, компоненты и схемы не описаны подробно, чтобы не загромождать конкретные варианты осуществления настоящего изобретения. Кроме того, различные аспекты вариантов осуществления изобретения могут быть выполнены с использованием различных средств, таких как интегральные полупроводниковые схемы ("аппаратные средства"), машиночитаемые команды, находящиеся в одной или нескольких программах («программное обеспечение») или некоторой комбинацией аппаратного и программного обеспечения. С целью описания, ссылка "логика" означает либо аппаратные средства, программное обеспечение, либо некая их комбинация.

Системы энергонезависимой памяти в настоящее время разрабатываются с целью увеличения скорости обработки, которые могут быть использованы в качестве локальных систем доступа к энергозависимой памяти. В отличие от энергозависимой памяти, энергонезависимая память автоматически не сбрасывается в ноль при отключении питания. Соответственно, способы управления локальным доступом к энергозависимой памяти могут использоваться в способе быстрого обнуления, например, в системах памяти для электронных устройств.

Фиг. 1 представляет собой схематическую структурную схему, иллюстрирующую компоненты устройства для осуществления управления памятью в соответствии с описанными здесь различными вариантами осуществления. Как показано на фиг. 1, в некоторых вариантах осуществления блок 100 центрального процессора (CPU), который может содержать один или более процессоров 110, соединенный с управляющим концентратором 120 и локальной памятью 130. Управляющий концентратор 120 включает в себя контроллер 122 памяти и интерфейс 124 памяти.

Интерфейс 124 памяти соединен с одним или несколькими удаленными устройствами 140 памяти через коммуникационную шину 160. Устройство 140 памяти может содержать контроллер 142 и один или более банков 150 памяти. В различных вариантах осуществления, по меньшей мере, некоторые из банков 150 памяти могут быть реализованы используя энергонезависимую память, например, память на фазовых переходах, NAND (флэш) память, сегнетоэлектрическая память с произвольным доступом (FeTRAM), энергонезависимая память на основе нанопроволоки, память, которая инкорпорирует мемристор, статическую память случайного доступа (SRAM), трехмерную (3D) перекрестную память, например, память на фазовых переходах (PCM), память на основе переноса спинового момента (STT-RAM) или NAND память. В качестве примера, в некоторых вариантах осуществления устройство(а) 140 памяти может включать в себя один или несколько модулей памяти с прямой линией связи (DIMMs), соединенный с каналом 144 памяти, который обеспечивает линию связи с контроллером 142. Конкретная конфигурация банка(ов) 150 памяти в устройстве(ах) 140 памяти не является критичным.

Как описано выше, в некоторых вариантах осуществления логическая схема в контроллере 122 памяти в устройстве(ах) 140 памяти. Более конкретно, в некоторых вариантах осуществления операции контроллер 122 памяти выполняет операции, которые позволяют энергонезависимой памяти устройств 150 памяти эмулировать энергозависимую память, в меньшей мере, в том смысле, что операции ввода/вывода на чтение энергонезависимой памяти устройства 140 памяти возвращает нули после операции сброса питания. Вкратце, контроллер 122 памяти выполняет эту операцию путем определения, были ли записаны данные в логическом блоке, которые предназначались для чтения, до самой последней операции сброса питания. Если данные в логическом блоке были записаны до самой последней операции сброса питания, контроллер памяти возвращает ответ на операцию чтения, что включает в себя нули вместо данных, которые находятся в логическом блоке. В отличие от этого, если данные в логический блок были записаны после последнего сброса питания, то контроллер памяти возвращает ответ на операцию считывания, что включает в себя данные, находящиеся в логическом блоке. Таким образом, контроллер 122 памяти позволяет энергонезависимой памяти эмулировать атрибуты энергозависимой памяти при сбросе питания.

В некоторых вариантах осуществления контроллер 122 памяти поддерживает следующие параметры в таблице 146 памяти:

Глобальный порядковый номер (GSN): это числовой параметр, который увеличивается каждый раз, когда система подвергается операции сброса питания. Контроллер памяти сохраняет GSN в таблице 146 памяти. В некоторых вариантах осуществления GSN может быть реализован в виде 8-битового двоичного числа так, что GSN может переключаться с 256 шагом увеличения, прежде чем он вернется в нулевое значение.

Серийный номер глобального порядкового номера (GSN.S). В некоторых вариантах осуществления GSN может принадлежать к одной из множества серий. Серийный номер глобального порядкового номера показывает серию, к которой принадлежит GSN. В некоторых вариантах осуществления GSN.S может быть реализован как наивысший бит глобального порядкового номера.

Медиа порядковый номер (MSN): Всякий раз, при выполнении операции записи на устройстве(ах) 140 памяти, текущий GSN записывается в метаданных для секции медиа, к которой применяется операция записи, и становится MSN для этой медиа секции.

Серийный номер медиа порядкового номера (MSN.S) - В некоторых вариантах осуществления MSN могут принадлежать к одной из множества серий. Серийной номер медиа порядковый номер указывает на серию, к которой принадлежит MSN. В некоторых вариантах осуществления MSN.S может быть реализован как наивысший бит MSN, скопированный из GSN.S, когда записывается медиа секция.

Флаг завершения обновления в пределах серии: флаг, указывающий, если полное обновление (например, фоновая обработка, которая считывает и записывает все адреса в памяти устройства) началось и завершилось в одной серии. Это может быть сохранено на устройстве(ах) 140 памяти.

Операции, осуществляемые контроллером 122 памяти, будут описаны со ссылкой на фиг. 2 и фиг. 4. Обратимся сначала к фиг. 2, когда электронное устройство, которое включает в себя систему памяти, изображенную на фиг. 1, подвергают операции сброса питания контроллера 122 памяти, на этапе 210, то считывает текущий глобальный порядковый номер (GSN) из таблицы 146 памяти.

На этапе 215 контроллер 122 памяти принимает запрос памяти из электронного устройства, которое включает в себя систему памяти, изображенную на фиг. 1. Если на этапе 220 контроллер 122 принимает запрос на запись, то управление переходит на этап 225 и контроллер 122 сохраняет порядковый номер в метаданных, ассоциированных с запрашиваемым адресом логического блока, как медиа порядковый номер для этого адреса логического блока. Как показано на фиг. 3, в некоторых вариантах осуществления MSA может быть сохранен в таблице памяти совместно с адресом логического блока.

Возвращаясь к фиг. 2, если на этапе 220 контроллер 122 принимает запрос на запись нулей в память в устройстве(ах) 140 памяти, то управление переходит на этап 230 и контроллер 122 увеличивает глобальный порядковый номер, и на этапе 235 контроллер 122 сохраняет глобальный порядковый номер в устройстве 140 (ах) памяти. Отдельно, контроллер 122 может осуществлять фоновую обработку, чтобы написать все нули в памяти в устройстве(ах) 140 памяти.

В противоположность этому, на этапе 220 контроллер 122 принимает запрос на считывание данных с устройства 140 памяти, когда управление переходит на этап 240 и контроллер 122 считывает медиа порядковый номер, ассоциированный с адресом логического блока, указанного в операции чтения из таблицы, изображенной на фиг. 3.

На этапе 245 контроллер 122 определяет, является ли медиа порядковый номер, ассоциированный с адресом логического блока, указанный в операции чтения, предыдущим, чем глобальный порядковый номер. В большинстве случаев, это определение, может быть выполнено путем сравнения медиа порядкового номера с глобальным порядковым номером. Если медиа порядковый номер меньше, чем глобальный порядковый номер, то медиа порядковый номер является предыдущим, чем глобальный порядковый номер.

Если на этапе 245 медиа порядковый номер не старше глобального порядкового номера, то управление переходит на этап 250 и контроллер 250 возвращает данные, хранящиеся в адресе логического блока, определенные в операции чтения. Напротив, если на этапе 245 медиа порядковый номер старше глобального порядкового номера, то управление переходит на этап 255 и контроллер 122 возвращает нулевой ответ вместо данных, хранящихся в адресе логического блока, указанного в запросе на чтение. Например, нулевой ответ может содержать все нули или заданную структуру битов. Затем управление переходит обратно на этап 210 и контроллером 122 ожидает следующего запроса памяти из электронного устройства.

Таким образом, операции, изображенные на фиг. 2, обеспечивают возможность контроллеру иметь энергонезависимую память в устройстве(ах) 140 памяти, что эмулируют работу энергозависимой памяти, по меньшей мере, в том смысле, что операции чтения, выполняемая в памяти, которая не была записана, чтобы с момента последнего сброса питания вернуть нули, а не фактические данные, которые находятся в адресе логического блока.

Ограничение памяти диктует необходимость того, что глобальный порядковый номер должен иметь конечное предельное значение. В некоторых вариантах осуществления, когда глобальный порядковый номер достигает своего конечного предельного значения, то он возвращается к нулю. Этот возврат может привести к ситуации, в которой медиа порядковый номер может быть выше, чем глобальный порядковый номер, даже если адрес логического блока не принял операцию записи с момента последней операции сброса питания. Определение, осуществляемое на этапе 245, должно учитывать то обстоятельство, что глобальный порядковый номер возвращается к нулю. Например, при обнаружении возврата порядкового номера медиа контроллер может вручную написать все нули.

В некоторых вариантах осуществления контроллер использует серийный номер глобального порядкового номера и серийный номер медиа последовательности для ситуации, когда возвращается глобальный порядковый номер. Логическая последовательность осуществления управления этой ситуации представлена на фиг. 4. Как показано на фиг. 4, на этапе 410 контроллер 122 принимает запрос на увеличение глобального порядкового номера.

Если на этапе 410 приращение не вызывает возвращение глобального порядкового номера к нолю, то управление переходит на этап 420, и глобальный порядковый номер увеличивается в нормальном режиме. Напротив, если на этапе 415 увеличение глобального порядкового номера вызывает возврат глобального порядкового номера, то управление переходит к операции на этапе 425, где статус флага завершения обновления в пределах серии проверяется, чтобы определить, если установлен флаг завершения обновления в пределах серии.

В некоторых вариантах осуществления контроллер 122 выполняет отдельный процесс, который контролирует операции записи на устройство(а) 140 памяти и устанавливает флаг обновления, когда все адреса логического блока в устройстве(ах) 140 памяти были написаны посредством данных с момента последней операции сброса питания. Таким образом, установленный флаг обновления показывает, что все адреса логического блока в устройстве(ах) 140 памяти были написаны с помощью новых данных с момента самой последней операции сброса питания.

Если на этапе 425 флаг обновления не установлен, то некоторые из данных в устройстве(ах) 140 памяти не был написаны с момента последней операции сброса питания. В этом случай управление переходит к операции на этапе 430 и контроллер 122 записывает нули по всем адресам в логическом адресном пространстве устройства 140 памяти, по существу, заставляя энергонезависимую память устройства 140 памяти эмулировать функцию обнуления энергозависимой памяти в ответ на сброс питания. Это показано на фиг. 5A.

Затем управление переходит к операции на этапе 435, и сбрасывается флаг обновления. На этапе 440 глобальный порядковый номер возвращается к нолю, и на этапе 445 бит серии инвертируется.

В отличие от этого, если при операции на этапе 425 флаг обновления установлен, то нет необходимости писать нули в энергонезависимой памяти в устройстве(ах) 140 памяти и управление может перейти непосредственно к операции на этапах 435-445. Это показано на рис. 5B.

Таким образом, выполнение операций, изображенных на фиг. 4, позволяет глобальному порядковому номеру вернуться на ноль, что не приводит к ошибочному чтению данных из адресов логического блока в устройстве(ах) 140 памяти, которые имеют медиа порядковые номера, которые выше, чем глобальный порядковый номер.

Как описано выше, в некоторых вариантах осуществления электронное устройство может быть реализовано в виде компьютерной системы. Фиг. 6 иллюстрирует блок-схему вычислительной системы 600 в соответствии с вариантом осуществления настоящего изобретения. Вычислительная система 600 может включать в себя один или более центральный процессор(ы) (CPU) 602 или процессоры, которые взаимодействуют через сеть 604 внутренней коммутации (или шину). Процессоры 602 могут включать в себя процессор общего назначения, процессор сети (который обрабатывает данные, переданные через компьютерную сеть 603) или другие типы процессора (включающие в себя процессор компьютера с сокращенным набором команд (RISC) или компьютер с архитектурой полного набора команд (CISC). Кроме того, процессоры 602 могут иметь одно или несколько ядер. Многоядерные процессоры 602 могут включать в себя различные типы ядер процессора на кристалле интегральной схемы (IC). Кроме того, многоядерные процессоры 602 могут быть реализованы как симметричные или асимметричные мультипроцессоры. В одном варианте осуществления один или более процессоров 602 могут быть одинаковыми или аналогичными процессорами 102 на фиг. 1. Например, один или более процессоров 602 могут включать в себя блок 120 управления, описанный со ссылкой на фиг. 1-3. Кроме того, операции, описанные со ссылкой на фиг. 3-5, могут быть выполнены с помощью одного или более компонентов системы 600.

Набор 606 микросхем может также взаимодействовать с сетью 604 внутренней коммутации. Набор 606 микросхем может включать в себя управляющий концентратор 608 памяти (MCH). MCH 608 может включать в себя контроллер 610 памяти, который взаимодействует с памятью 612 (которая может быть той же или аналогичной памяти 130 на фиг. 1). Память 412 может хранить данные, включающие в себя последовательность команд, которые могут выполняться процессором 602 или любым другим устройством, включенным в состав вычислительной системы 600. В одном варианте осуществления настоящего изобретения, память 612 может включать в себя одно или более энергозависимое (или память) запоминающее устройство, такое как оперативное запоминающее устройство (RAM), динамическое RAM (DRAM), синхронное динамическое DRAM (SDRAM), статическое RAM (SRAM) или другие типы запоминающих устройств. Энергонезависимая память может также использоваться, например, в качестве жесткого диска. Дополнительные устройства могут осуществлять связь через сеть 604 внутренней коммутации, например, с несколькими процессорами и/или несколькими системами памяти.

MCH 608 может также включать в себя графический интерфейс 614, который взаимодействует с устройством 616 отображения. В одном варианте осуществления изобретения, графический интерфейс 614 может осуществлять связь с устройством 616 отображения через ускоренный графический порт (AGP). В варианте осуществления изобретения, дисплей 616 (например, плоскопанельный дисплей) может взаимодействовать с графическим интерфейсом 614 через, например, преобразователь сигнала, который преобразует цифровое представление изображения, сохраненного в запоминающем устройстве, таком как видеопамяти или системной памяти, в сигналы отображения, которые интерпретируются и отображаются на дисплее 616. Сигналы отображения, вырабатываемые устройством отображения, могут проходить через различные устройства управления до их обработки, и затем отображаются на дисплее 616.

Интерфейс 618 концентратора может взаимодействие МСН 608 и управляющего концентратора 620 (ICH) ввода/вывода. ICH 620 может обеспечивать интерфейс для I/O устройств, которые взаимодействуют с вычислительной системой 600. ICH 620 может взаимодействовать с шиной 622 через периферийный мост (или контроллер) 624, такой как мостовое соединение периферийных компонентов (PCI), контроллер универсальной последовательной шины (USB) или другие типы периферийных мостов или контроллеров. Мост 624 может обеспечить тракт для передачи данных между процессором 602 и периферийными устройствами. Другие типы топологий могут быть использованы. Кроме того, несколько шин могут взаимодействовать с ICH 620, например, через несколько мостов или контроллеров. Более того, другие периферийные устройства, взаимодействующие с ICH 620, могут включать в себя, в различных вариантах осуществления изобретения, встроенный интерфейс накопителей (IDE) или жесткий диск(и) интерфейса малых компьютерных систем (SCSI), USB порт(ы), клавиатуру, мышь, параллельный порт(ы), последовательный порт(ы), флоппи-дисковод(ы), поддержку цифрового выхода (например, цифровой видео интерфейс (DVI)) или другие устройства.

Шина 622 может взаимодействовать с аудиоустройством 626, одним или более диском(ми) 628 и устройством 630 сетевого интерфейса (который находится во взаимодействии с компьютерной сетью 603). Другие устройства могут взаимодействовать через шину 622. Кроме того, различные компоненты (такие как устройство 630 сетевого интерфейса) могут взаимодействовать с MCH 608 в некоторых вариантах осуществления настоящего изобретения. Кроме того, процессор 602 и один или несколько других компонентов, описанных здесь, могут быть объединены в единую микросхему (например, чтобы обеспечить систему на кристалле (SoC)). Кроме того, графический ускоритель 616 может быть включен в состав MCH 608 в других вариантах осуществления изобретения.

Кроме того, вычислительная система 600 может включать в себя энергозависимую и/или энергонезависимую память (или запоминающее устройство). Например, энергонезависимая память может включать в себя одно или более из следующих: постоянное запоминающее устройство (ROM), программируемое ROM (PROM), стираемое PROM (EPROM), электрически EPROM (EEPROM), дисковод (например, 628), флоппи-диск, компакт-диск ROM (CD-ROM), цифровой универсальный диск (DVD), флэш-память, магнитооптический диск или другие типы энергонезависимых машинно-считываемых носителей, которые способны хранить электронные данные (например, включающие в себя команды).

Фиг. 7 иллюстрирует блок-схему вычислительной системы 700, в соответствии с вариантом осуществления настоящего изобретения. Система 700 может включать в себя один или несколько процессоров с 702-1 по 702-N (обычно называется здесь, как "процессоры 702" или "процессор 702"). Процессоры 702 могут взаимодействовать через сеть внутренней коммутации или шину 704. Каждый процессор может включать в себя различные компоненты, некоторые из которых описаны только со ссылкой на процессор 702-1 для ясности. Соответственно, каждый из остальных процессоров с 702-2 по 702-N может включать в себя те же или подобные компоненты, описанные со ссылкой на процессор 702-1.

В одном варианте осуществления процессор 702-1 может включать в себя одноядерный или многоядерный процессор с 706-1 по 706-M (называемый здесь "ядра 706" или в более общем смысле, как "ядро 706"), совместная кэш-память 708, маршрутизатор 710 и/или управляющий логический блок процессора или блок 720. Ядра 706 процессора могут быть реализованы на одной микросхеме (IC). Кроме того, микросхема может включать в себя одну или более совместную кеш-память и/или индивидуальную кэш-память (такую, как кэш 708), шины или соединения (например, шина или сеть 712 внутренней коммутации), контроллеры памяти или другие компоненты.

В одном варианте осуществления маршрутизатор 710 может быть использован для обмена данными между различными компонентами процессора 702-1 и/или системы 700. Кроме того, процессор 702-1 может включать более, чем один маршрутизатор 710. Более того, множество маршрутизаторов 710 может взаимодействовать с данными маршрутизации между различными компонентами внутри или за пределами процессора 702-1.

Совместная кэш-память 708 может хранить данные (например, включающие в себя команды), которые используются одним или несколькими компонентами процессора 702-1, такими как ядра 706. Например, совместная кэш-память 708 может локально кэшировать данные, сохраненные в памяти 714 для более быстрого доступа компонентами процессора 702. В одном варианте осуществления кэш 708 может включать в себя кэш среднего уровня (например, уровня 2 (L2), уровня 3 (L3), уровня 4 (L4) или другие уровни кэша), кэш последнего уровня (LLC) и/или их комбинации. Кроме того, различные компоненты процессора 702-1 могут взаимодействовать с совместной кэш-памятью 708 708 непосредственно через шину (например, шину 712) и/или контроллер памяти или концентратор. Как показано на фиг. 7, в некоторых вариантах осуществления одно или более ядер 706 могут включать в себя кеш 716-1 первого уровня 1 (LI) (как правило, называют здесь "кэш 716 первого уровня"). В одном варианте осуществления блок 720 управления может включать в себя логический блок для выполнения операции, описанные выше со ссылкой на контроллер 122 памяти на фиг. 2.

Фиг. 8 иллюстрирует блок-схему частей ядра 706 процессора и других компонентов вычислительной системы в соответствии с вариантом осуществления настоящего изобретения. В одном варианте осуществления, как показано стрелками на фиг. 8, иллюстрируются направление потока прохождения команд через ядро 706. Один или несколько ядер процессора (например, ядро 706 процессора) могут быть реализованы интегральной схемой на одном кристалле, как описано со ссылкой на фиг. 7. Кроме того, микросхема может включать в себя одну или несколько совместную и/или индивидуальную кэш-память (например, кэш 708 на фиг. 7), соединения (например, соединения 704 и/или 112 на фиг. 7), блоки управления, контроллеры памяти или другие компоненты.

Как показано на фиг. 8, ядро 706 процессора может включать в себя блок 802 выборки для извлечения команд (включающие в себя команды условных переходов) для исполнения ядром 706. Команды могут быть выбраны из любых устройств хранения данных, таких как память 714. Ядро 706 также может включать в себя блок 804 декодирования для декодирования выбранной команды. Например, блок 804 декодирования может декодировать выбранную команду из множества микроопераций (микрооперации).

Кроме того, ядро 706 может включать в себя блок 806 планирования. Блок 806 планирования может выполнять различные операции, ассоциированные с хранением декодированных команд (например, принятые из блока 804 декодирования) до тех пор, команды не готовы к отправке, например, пока все исходные значения декодированной команды, станут доступны. В одном варианте осуществления блок 806 планирования может планировать и/или выводить (или отправлять) декодированные команды в исполнительный блок 808 исполнения для исполнения. Исполнительный блок 808 может выполнять передаваемые инструкции после декодирования (например, с помощью блока 804 декодирования) и направленные, например, блоком 806 планирования. В одном варианте осуществления исполнительный блок 808 может включать в себя более, чем один исполнительный блок. Исполнительный блок 808 также может выполнять различные арифметические операции, такие как сложение, вычитание, умножение и/или деление, и может включать в себя один или более арифметических логических блоков (ALUs). В одном варианте осуществления сопроцессор (не показан) может выполнять различные арифметические операции совместно с исполнительным блоком 808.

Дополнительно, исполнительный блок 808 может выполнять команды не в порядке поступления. Таким образом, процессор 706 может быть ядром процессора, выполняющий команды с изменением их очередности, в одном варианте осуществления. Ядро 706 может также включать в себя блок 810 удаления. Блок 810 удаления может удалить выполненные команды после их выполнения. В одном варианте осуществления удаление выполненных команд позволяет процессору не выполнять данные команды, физические регистры, используемые в командах, не будет назначаться и т.д.

Ядро 706 может также включать в себя блок 714 шины для обеспечения связи между компонентами ядра 706 процессора и другими компонентами (например, компонентами, описанными со ссылкой на фиг. 8) с помощью одной или нескольких шин (например, шины 804 и/или 812). Ядро 706 может также включать в себя один или более регистров 816 для хранения данных, доступных для различных компонентов ядра 706 (например, значения, относящиеся к установкам состояния потребления электроэнергии).

Кроме того, несмотря на то, что фиг. 7 иллюстрирует блок 720 управления, соединенный с ядром 706 с помощью соединения 812, в различных вариантах осуществления блок 720 управления может быть расположен в другом месте, например, внутри ядра 706, соединенный с ядром через шину 704 и т.д.

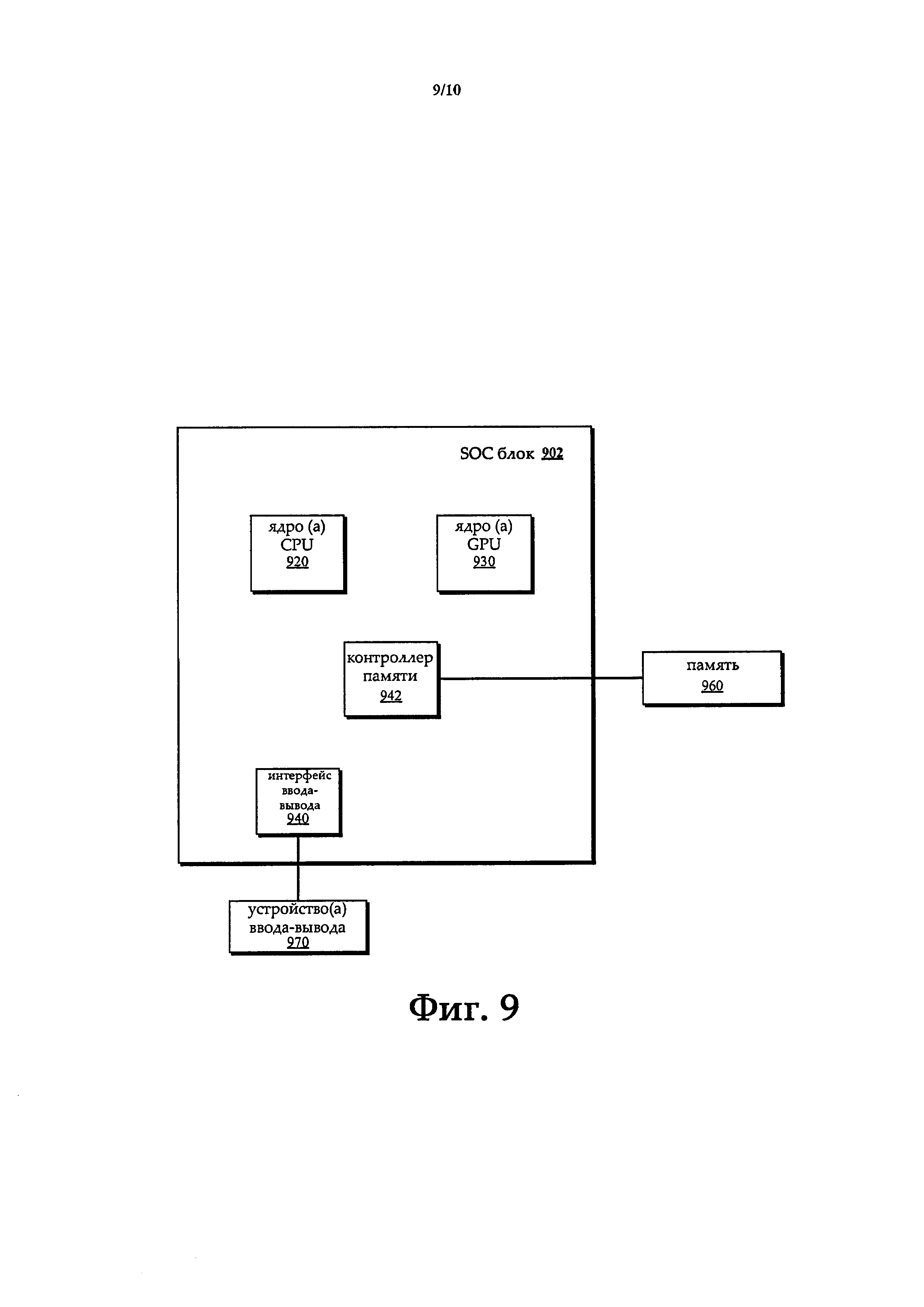

В некоторых вариантах осуществления один или более компонентов, описанных здесь, могут быть воплощены как устройство система на кристалле (SOC). Фиг. 9 иллюстрирует блок-схему SOC устройства в соответствии с вариантом осуществления. Как показано на фиг. 9, SOC 902 включает в себя одно или более ядер 920 центрального процессора (CPU), одно или более ядер 930 графического процессора (GPU), (I/O) интерфейс 940 ввода/вывода и контроллер 942 памяти. Различные компоненты SOC устройства 902 могут быть соединены с соединениями или шиной, таким как описано здесь со ссылкой на другие чертежи. Кроме того, SOC устройство 902 может включать в себя больше или меньше компонентов, таких как те, которые описывались в данном документе со ссылкой на другие чертежи. Кроме того, каждый компонент SOC устройства 902 может включать в себя один или более других компонентов, например, как описано со ссылкой на друге чертежи в данном документе. В одном варианте осуществления SOC устройство 902 (и его компоненты) предусмотрено на одном или более интегральных схем (IC) на кристалле, например, которые размещены в одном полупроводниковом устройстве.

Как показано на фиг. 9, SOC устройство 902 соединено с памятью 960 (которое может быть аналогично тому, как описано здесь, со ссылкой на другие чертежи) с помощью контроллера 942 памяти. В одном варианте осуществления память 960 (или его часть) может быть интегрирована в SOC устройство 902.

Интерфейс 940 ввода/вывода может быть соединен с одним или более I/O устройствами 970, например, с помощью соединения и/или шины, такой как описано здесь со ссылкой на другие чертежи. I/O устройство(а) 970 может включать в себя одно или более из клавиатуру, мышь, сенсорный экран, дисплей, устройство захвата изображения/видео (например, камеру или видеокамеру/видеомагнитофон), динамик или т.п.

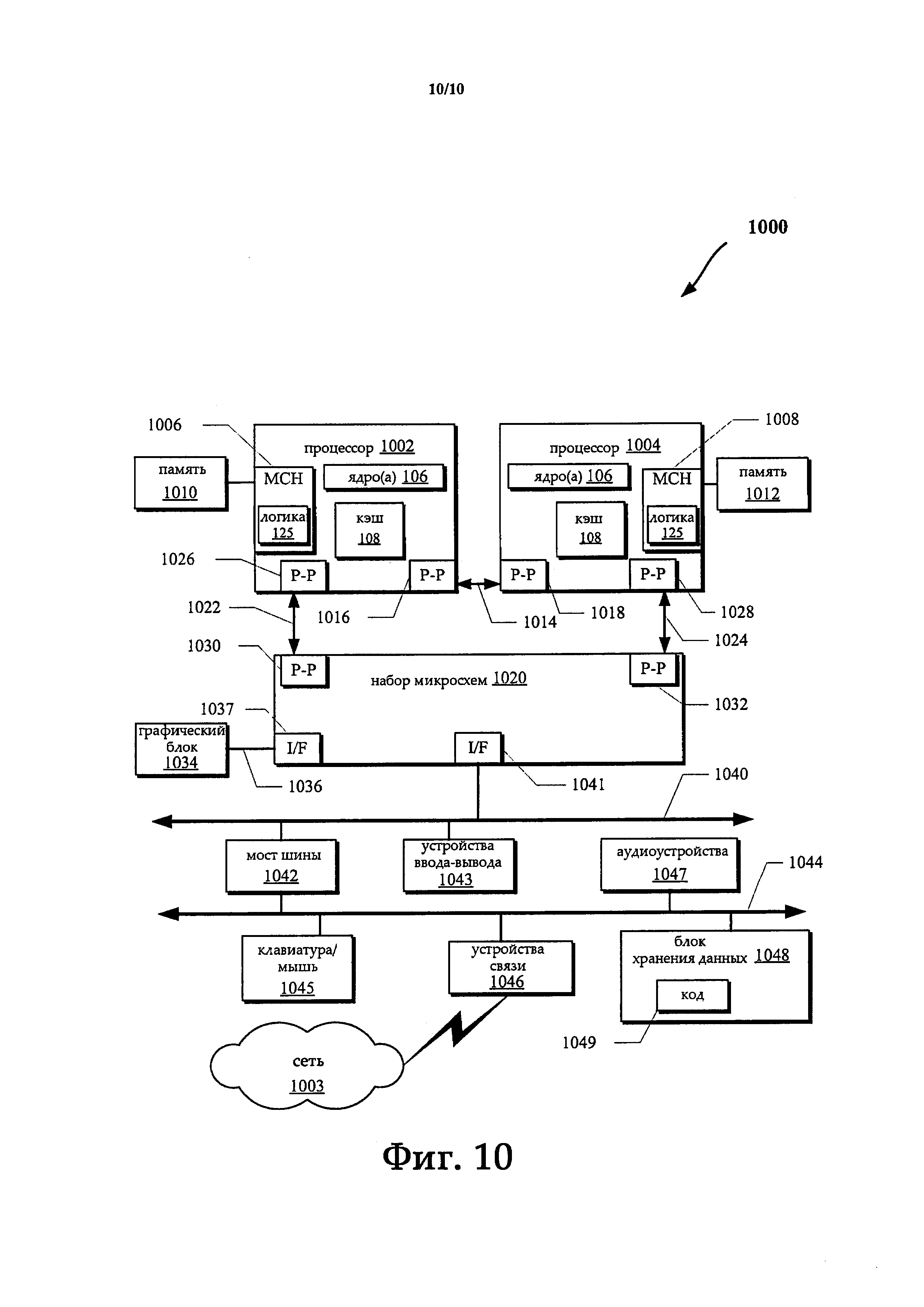

Фиг. 10 иллюстрирует вычислительную систему 1000, которая реализована в двухточечной (PtP) конфигурации, в соответствии с вариантом осуществления настоящего изобретения. В частности, на фиг. 10. показана система, где процессоры, память и устройства ввода/вывода соединены между собой посредством нескольких двухточечных интерфейсов. Операции, описанные со ссылкой на фиг. 2, могут быть выполнены посредством одного или нескольких компонентов системы 1000.

Как показано на фиг. 10, система 1000 может включать в себя несколько процессоров, из которых только два процессора 1002 и 1004 показаны для ясности. Процессоры 1002 и 1004 могут каждый включать в себя локальный концентратор контроллера памяти (MCH) 1006 и 1008, чтобы обеспечить связь с памятью 1010 и 1012. MCH 1006 и 1008 могут включать в себя контроллер 120 памяти и/или логический блок 125, как показано на фиг. 1, в некоторых вариантах осуществления.

В одном варианте осуществления, процессоры 1002 и 1004 могут быть одним из процессоров 702, обсуждаемых со ссылкой на фиг. 7. Процессоры 1002 и 1004 могут обмениваться данными через двухточечный (PtP) интерфейс 1014, используя схемы 1016 и 1018 (PtP) интерфейса, соответственно. Кроме того, процессоры 1002 и 1004 могут каждый осуществлять обмен данными с набором 1020 микросхем через PtP отдельные интерфейсы 1022 и 1024, использующие схемы 1026, 1028, 1030 и 1032 двухточечного интерфейса. Набор 1020 микросхем может дополнительно обеспечить обмен данными с высокопроизводительной графической схемой 1034 с помощью высокопроизводительного графического интерфейса 1036, например, с использованием PtP схемы 1037 интерфейса.

Как показано на фиг. 10, одно или более ядер 106 и/или кэш 108 на фиг. 1 может быть расположено внутри процессоров 902 и 904. Другие варианты осуществления изобретения, однако, могут существовать в других схемах, логических устройствах или устройствах в системе 900, как показано на фиг. 9. Кроме того, другие варианты осуществления изобретения могут быть распределены по нескольким схемам, логическим блокам или устройствам, показанные на фиг. 9.

Набор 920 микросхем может осуществлять связь с шиной 940 с помощью PtP схемы 941 интерфейса.

Шина 940 может иметь одно или несколько устройств, которые взаимодействуют с ней, такие как шинный мост 942 и I/O устройства 943. Посредством шины 944, шинный мост 943 может взаимодействовать с другими устройствами, такими как клавиатура/мышь 945, устройства 946 связи (например, модемы, сетевой интерфейс или другие устройства связи, которые могут обмениваться данными с компьютерной сетью 803), аудио I/O устройство и/или устройство 948 хранения данных. Устройство 948 хранения данных (которое может быть жестким диском или флэш-памятью NAND на основе твердотельного накопителя) может хранить код 949, который может быть выполнен с помощью процессоров 902 и/или 904.

Следующие примеры относятся к дополнительным вариантам осуществления.

Пример 1 представляет собой контроллер памяти, содержащий логику для получения глобального порядкового номера из памяти устройства, принимает запрос на чтение данных, хранящихся в адресе логического блока в устройстве памяти, извлекает медиа порядковый номер из адреса логического блока в устройстве памяти и возвращает нулевой ответ вместо данных, хранящихся в адресе логического блока, когда медиа порядковый номер старше глобального порядкового номера.

В примере 2, объект изобретения по примеру 1 может, возможно, включать в себя логику для возврата ответа, содержащего данные, хранящиеся в адресе логического блока в устройстве памяти, когда медиа порядковый номер не старше глобального порядкового номера.

В примере 3, объект изобретения по любому из примеров 1-2 может, возможно, включать в себя логику для приема запроса на запись для записи данных в адрес логического блока в устройстве памяти, и сохранения глобального порядкового номера в метаданных, ассоциированных с запрошенным адресом логического блока, медиа порядковый номер.

В примере 4, объект изобретения по любому из примеров 1-3 может, возможно, включать в себя логику для приема запроса нулевой памяти, и, в ответ на команду нулевой памяти, увеличивать глобальный порядковый номер, и хранить глобальный порядковый номер в устройстве памяти.

В примере 5, объект изобретения по любому из примеров 1-4 может, возможно, включать в себя структуру, в котором глобальный порядковый номер содержит номер серии глобального порядкового номера, который идентифицирует серию, к которой глобальный порядковый номер принадлежит, и медиа порядковый номер содержит номер серии медиа порядкового номера, который идентифицирует серию, к которой медиа порядковый номер принадлежит.

В примере 6, объект изобретения по любому из примеров 1-5 может, возможно, включать в себя логику, чтобы возвращать нулевой ответ вместо данных, сохраненных в адресе логического блока, когда номер серии медиа порядкового номера равен номеру серии глобального порядкового номера, и медиа порядковый номер меньше, чем глобальный порядковый номер.

В примере 7, объект изобретения по любому из примеров 1-6 может, возможно, включать в себя логику, чтобы вернуть ответ, содержащий данные, хранящиеся в адресе логического блока в устройстве памяти, когда номер серии медиа порядкового номера равен номеру серии глобального порядкового номера и медиа порядковый номер меньше глобального порядкового номера.

В примере 8, объект изобретения по любому из примеров 1-7 может, возможно, включать в себя логику, чтобы возвращать нулевой ответ вместо данных, сохраненных в адресе логического блока, когда серийный номер медиа порядкового номера не равен серийному номеру глобального порядкового номера,

Пример 9 представляет собой электронное устройство, содержащее процессор и логику управления памятью для получения глобального порядкового номера из устройства памяти, приема запроса на чтение данных, хранящихся в адресе логического блока в устройстве памяти, извлечения медиа порядкового номера из адреса логического блока в устройстве памяти, и возврата нулевого ответа вместо данных, хранящихся в адресе логического блока, когда медиа порядковый номер старше глобального порядкового номера.

В примере 10, объект изобретения по примеру 9 может, возможно, включать в себя логику, чтобы принять из устройства запрос данных и генерировать в ответ на запрос из устройства, запрос данных из удаленного устройства памяти.

В примере 11, объект изобретения по любому из примеров 9-10 может, возможно, включать в себя логику для возврата ответа, содержащего данные, хранящиеся в адресе логического блока в устройстве памяти, когда медиа порядковый номер не старше глобального порядкового номера.

В примере 12, объект изобретения по любому из примеров 9-11 может, возможно, включать в себя логику для приема запроса записи для записи данных в адрес логического блока в устройстве памяти, и сохранение глобального порядкового номера в метаданных, ассоциированных с запрошенным адресом логического блока, как медиа порядковый номер.

В примере 13, объект изобретения по любому из примеров 9-12 может, возможно, включать в себя логику для приема запроса нулевой памяти, и, в ответ на команду нулевой памяти, увеличивать глобальный порядковый номер и хранить глобальный порядковый номер в устройстве памяти.

В примере 14, объект изобретения по любому из примеров 9-12 может, возможно, включать в себя структуру, в которой глобальный порядковый номер содержит номер серии глобального порядкового номера, который идентифицирует серию, к которой глобальный порядковый номер принадлежит, и медиа порядковый номер содержит номер серии медиа порядкового номера, который идентифицирует серию, к которой медиа порядковый номер принадлежит.

В примере 15, объект изобретения по любому из примеров 9-14 может, возможно, включать в себя логику для возврата нулевого ответа вместо данных, сохраненных в адресе логического блока, когда номер серии медиа порядкового номера равен номеру серии глобального порядкового номера, и медиа порядковый номер меньше глобального порядкового номера.

В примере 16, объект изобретения по любому из примеров 9-15 может, возможно, включать в себя логику для возврата ответа, содержащего данные, хранящиеся в адресе логического блока в устройстве памяти, когда номер серии медиа порядкового номера равен серийному номеру глобального порядкового номера и медиа порядковый номер меньше глобального порядкового номера.

В примере 17, объект изобретения по любому из примеров 9-16 может, возможно, включать в себя логику для возврата нулевого ответа вместо данных, сохраненных в адресе логического блока, когда серийный номер медиа последовательности не равен серийному номеру глобальной последовательности.

Пример 18 является компьютерным программным продуктом, содержащий логические команды, хранящиеся на непреходящем машиночитаемом носителе, которые при выполнении процессором, конфигурируют процессор извлечь глобальный порядковый номер из устройства памяти, принять запрос на чтение для данных, хранящихся в адресе логического блока в устройстве памяти, извлекать медиа порядковый номер из адреса логического блока в устройстве памяти, и возвратить нулевой ответ вместо данных, хранящихся в адресе логического блока, когда медиа порядковый номер старше глобального порядкового номера.

В примере 19, объект изобретения по примеру 18 может, возможно, включать в себя логику для возврата ответа, содержащего данные, хранящиеся в адресе логического блока в устройстве памяти, когда медиа порядковый номер не старше глобального порядкового номера.

В примере 20, объект изобретения по любому из примеров 18-19 может, возможно, включать в себя логику для приема запроса на запись для записи данных в адрес логического блока в устройстве памяти и хранить глобальный порядковый номер в метаданных, ассоциированных с запрашиваемым адресом логического блока, как медиа порядковый номер.

В примере 21, объект изобретения по любому из примеров 18-20 может, возможно, включать в себя логику для приема запроса нулевой памяти, и, в ответ на команду нулевой памяти, увеличивать глобальный порядковый номер и хранить глобальный порядковый номер в устройстве памяти.

В примере 22, объект изобретения по любому из примеров 18-21 может, возможно, включать в себя структуру, в которой глобальный порядковый номер содержит номер серии глобального порядкового номера, который идентифицирует серию, к которой глобальный порядковый номер принадлежит, и медиа порядковый номер включает в себя номер серии медиа порядкового номера, который идентифицирует серию, к которой медиа порядковый номер принадлежит.

В примере 23, объект изобретения по любому из примеров 18-22 может, возможно, включать в себя логику для возврата нулевого ответ вместо данных, сохраненных в адресе логического блока, когда номер серии медиа последовательности равен серийному номеру глобальной последовательности, и медиа порядковый номер меньше глобального порядкового номера.

В примере 24, объект изобретения по любому из примеров 18-23 может, возможно, включать в себя логику для возврата ответа, содержащего данные, хранящиеся в адресе логического блока в устройстве памяти, когда номер серии медиа последовательности равен серийному номеру глобальной последовательности и медиа порядковый номер меньше глобального порядкового номера.

В примере 25, объект изобретения по любому из примеров 18-24 может, возможно, включать в себя логику для возврата нулевого ответа вместо данных, сохраненных в адресе логического блока, когда серийный номер медиа последовательности не равен серийному номеру глобальной последовательности.

В различных вариантах осуществления изобретения, операции, описанные здесь, например, со ссылкой на фиг. 1-9, могут быть реализованы в виде аппаратных средств (например, схемой), программного обеспечения, аппаратно-программного обеспечения, микрокода или их комбинации, которые могут быть представлены в виде компьютерный программный продукт, например, включающий в себя материальный (например, непреходящий) машиночитаемый носитель информации, имеющий сохраненные на нем команды (или программное обеспечение), используемые для программирования компьютера для выполнения процесса, описанного здесь. Кроме того, термин "логика" может включать в себя, в качестве примера, программное обеспечение, аппаратные средства или комбинации программного обеспечения и аппаратных средств. Машиночитаемый носитель информации может включать в себя устройство хранения данных, такое как описанное в данном документе.

Ссылка в описании на "один вариант осуществления" или "вариант осуществления" означает, что конкретный признак, структура или характеристика, описанные в связи с вариантом осуществления, могут быть включены в состав, по меньшей мере, в варианте реализации. Использование фразы "в одном варианте осуществления" в различных местах в описании, может быть или не быть осуществлено со ссылкой на тот же вариант осуществления.

Кроме того, в описании и формуле изобретения термины «соединенный» и «подключенный», а также их производные, могут быть использованы. В некоторых вариантах осуществления настоящего изобретения, термин "подключен" может быть использован для указания того, что два или более элементов находятся в прямом физическом или электрическом контакте друг с другом. Тем не менее, термин "соединенный" может означать, что два или более элементов могут не находиться в прямом физическом контакте друг с другом, но все еще могут взаимодействовать друг с другом.

Таким образом, хотя варианты осуществления изобретения были описаны на специфическом языке для структурных признаков и/или методологических действий, должно быть понятно, что заявленный предмет изобретения не может быть ограничен конкретными признаками или описанными действиями. Напротив, конкретные признаки и действия раскрыты как примерные формы реализации заявленного предмета изобретения.