Результат интеллектуальной деятельности: СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ

Вид РИД

Изобретение

Изобретение относится к технике связи, в частности к синхронизации в системах с шумоподобными сигналами, использующими "длинные" псевдослучайные последовательности, и предназначено для быстрой апериодической синхронизации при наличии частотной и временной неопределенностей.

Известен способ синхронизации и система связи со скачкообразным изменением частоты /1/, в которой включение передатчика возбуждает передачу заданного числа циклов синхронизируемого сигнала, состоящего из некоторого числа разных частот. Приемник включается на этих же частотах с относительно небольшой скоростью, так что синхросигнал будет приниматься на каждой частоте приемника. При распознавании синхронизируемого сигнала и цикла, в котором он принимается, приемник предваряет конец последнего цикла синхронизирующего сигнала синхронно с передатчиком и перестраивается в соответствии с заданным псевдослучайным кодом. Затем синхронизирующие сигналы периодически передаются для корректировки разницы в скорости тактовых импульсов на передатчике и приемнике. В конце передачи выдается сигнал конца сообщения, который после распознавания индицирует приемнику, что синхронизм сохраняется на протяжении заданного времени вслед за передачей для получения ответа без восстановления синхронизма, или что синхронизм не будет поддерживаться, так что приемник и передатчик немедленно возвращаются в режим поиска. Приемопередатчик, реализующий этот способ синхронизации, содержит антенну, разрядник защиты приемника, модулятор, демодулятор, микрофон, громкоговоритель, блок управления, блоки программ быстрой синхронизации, медленной синхронизации и переключения частоты.

Достоинством способа синхронизации и приемопередатчика является их простота. Недостатком является низкая помехозащищенность, так как при синхронизации используется только часть (1/8 часть) синхросигнала.

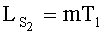

Наиболее близкими по технической сущности к предлагаемому способу и устройству выбранные в качестве прототипа являются способ и устройство для быстрой синхронизации в системах с шумоподобными сигналами, использующими "длинные" псевдослучайные последовательности (последовательности с большим периодом) /2/, в которых применяется специальный сигнал синхронизации, передаваемый в начале сеанса связи непосредственно перед информационными сигналами, модулированных псевдослучайным кодом с "длинным" периодом. Сигнал синхронизации состоит из двух частей. Первая часть сигнала синхронизации модулируется "коротким" псевдослучайным кодом S2, а вторая - кодом S, образованным суммированием по mod2 кода S2 и закодированного кодером разностной модуляции "короткой" псевдослучайной последовательности S1. Длина  последовательности S2 равна

последовательности S2 равна

,

,

где Т1 - длительность одного бита последовательности S1,

m=1, 2 ….

На приемной стороне синхронизация производится в два этапа. На первом этапе по первой части сигнала производится периодическая синхронизация по коду S2. На втором этапе по второй части - апериодическая синхронизация по коду S1. После апериодической синхронизации начинается прием информации, модулированной "длинной" псевдослучайной последовательностью.

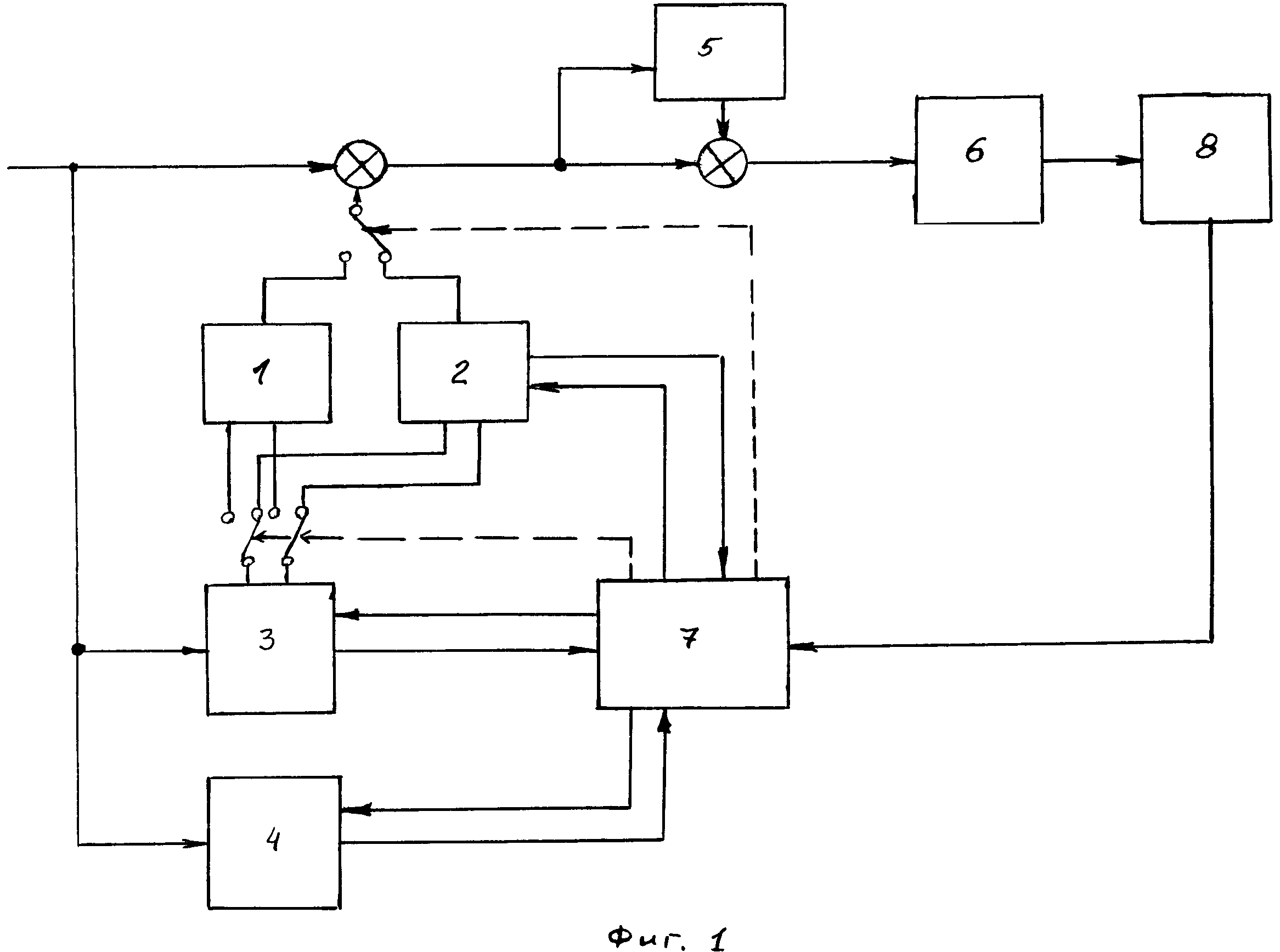

Приемник, реализующий данный способ синхронизации, содержит (фиг. 1) генератор 1 "длинное" псевдослучайной последовательности, генератор 2 "короткой" псевдослучайной последовательности S2, блок 3 следящей системы за задержкой, блок 4 синхронизации кода S2, блок 5 восстановления несущей, демодулятор 6, блок 7 управления и синхронизации и блок 8 синхронизации кода S1. В приемнике синхронизация осуществляется в два этапа.

На первом этапе код S2 обнаруживается и затем начинается слежение за задержкой кода S2. Для обнаружения кода S2 используется согласованный фильтр. При поступлении на вход согласованного фильтра сигнала синхронизации на его выходе появляется периодическая последовательность корреляционных пиков, которая детектируется при помощи порогового детектора. Детектированные корреляционные пики используются для выработки временных сигналов, которые вызывают запуск процесса синхронизации. Достижение синхронизации по коду S2 проверяется путем подсчета числа превышений порога в пороговом детекторе за фиксированный период времени. Если наличие корреляционных пиков подтверждается, то производится установка и запуск генератора 2 последовательности S2 следящей системы по задержке. Вначале следящая система по задержке имеет широкую полосу, что позволяет обеспечить быстрый захват сигнала, а затем ее полоса уменьшается для хорошего слежения за сигналом. Для устранения ложного захвата сигнала применяется синхронный детектор, содержащий корреляционный детектор и решающую схему.

На втором этапе с помощью коррелятора и декодера разностной модуляции производится синхронизация по коду S1. После достижения синхронизации по коду S1 производится установка, запуск генератора 1 "длинной" псевдослучайной последовательности и начинается прием информации.

Достоинством способа и устройства для быстрой синхронизации является высокая помехоустойчивость, которая достигается путем соответствующего выбора модулирующих псевдослучайных последовательностей S1, S2 и многократными проверками правильности синхронизации на этапе поиска сигнала.

Недостатком способа и устройства является, во-первых, то, что их невозможно использовать для поддержания синхронизма в подвижных системах связи с "прерывистым" режимом передачи информации, так как при прекращении передачи информации синхронизм между приемником и передатчиком может нарушаться, что приводит к необходимости проведения нового цикла синхронизации, во-вторых, низкая энергетическая скрытность сигнала синхронизации, вызванная большой его длительностью из-за необходимости последовательного проведения периодической и апериодической синхронизации, а также применения фазоразностной модуляции для последовательности S1, в-третьих, большое время синхронизации из-за необходимости отработки следящими системами синхронизации частотной неопределенности (установки частоты), в-четвертых, низкая помехоустойчивость, следящих систем синхронизации из-за необходимости работы их дискриминанторов во всем диапазоне частотной неопределенности, что уменьшает отношение сигнал-помеха на их входе.

Целью изобретения является повышение помехоустойчивости, скрытности канала синхронизации и обеспечение быстрой синхронизации и ее поддержание в подвижных системах связи с "прерывистым" режимом передачи. Для этого в способе быстрой синхронизации в системах связи с шумоподобными сигналами, использующими "длинные" псевдослучайные последовательности, применяющем специальный сигнал синхронизации (СС), предлагается манипулировать СС по фазе последовательностью, образованной суммированием по модулю 2 несущей (внутренней) последовательности (НП) и модулирующей (внешней) последовательности (МП), причем длительности НП и элемента МП выбираются одинаковыми и так, чтобы обеспечить обнаружение НП во всем диапазоне частотной неопределенности, постоянно передавать с некоторым периодом между информационными символами независимо от передачи информации, параметры СС (например, период следования, несущая частота, НП и МП) менять по известному на приемной стороне псевдослучайному закону, поиск и синхронизация по которому осуществляется в четыре этапа. На первом этапе ведется поиск НП последовательно по всем элементам временной неопределенности (ЭВН) во всем диапазоне частотной неопределенности и осуществляется периодическая синхронизация по НП посредством согласованной фильтрации части СС, манипулированной одним периодом НП, детектирования огибающих, некогерентного накопления МП (ННМП) на рециркуляторе со скользящим окном на всю длительность СС, сравнения с порогом обнаружения, запоминания номеров ЭВН, при анализе которых происходит превышение порога обнаружения. На втором этапе ведется многоканальный по частоте поиск МП в ЭВН, номера которых зафиксированы на первом этапе, во всем диапазоне частотной неопределенности и осуществляется апериодическая синхронизация по МП посредством задержи на длительность СС и более принимаемого сигнала, многоканальной по частоте согласованной фильтрации задержанного СС с когерентным накопителем МП (КНМП), детектирования огибающей, сравнения с порогом в каждом канале, запоминания номеров ЭВН, при анализе которых происходит превышение порога в одном из частотных каналов. На третьем этапе выполняется проверка правильности апериодической синхронизации, а также измерение частоты и задержки СС в ЭВН, номера которых зафиксированы на втором этапе, во всем диапазоне частотной неопределенности посредством многоканальной по частоте согласованной фильтрации последующих СС с КНМП, детектирования огибающей и некогерентного накопления в каждом частотном канале в течение некоторого числа периодов СС, обеспечивающего его быстрое, надежное обнаружение, а также измерение задержки и частоты, окончательное принятие решения о наличии СС, а также оценка его задержки и частоты. На четвертом этапе выполняется подстройка параметров приемника по измеренным на третьем этапе значениям, замыкаются следящие системы по несущей и задержке, осуществляется и поддерживается с помощью следящих систем точная синхронизация по СС в течение всего сеанса связи.

В устройство для быстрой синхронизации в системах связи с шумоподобными сигналами, использующими "длинные" псевдослучайные последовательности, содержащее два квадратурных перемножителя, входы которых соединены с сигнальным входом устройства, а вторые входы являются входами опорных квадратурных сигналов, блок следящих систем по несущей и задержке (ССН и ССЗ), сигнальный вход которого соединен с сигнальным входом устройства, два перестраиваемых согласованных фильтра на часть СС, манипулированную одним периодом НП, причем входы обоих согласованных фильтров соединены с выходами соответствующих квадратурных перемножителей, введены два аналого-цифровых преобразователя (АЦП), вход которых соединены с выходами согласованных фильтров, два первых буферных запоминающих устройства (БЗУ), информационные входы которых соединены с выходами АЦП, два умножителя, первые выходы которые соединены с информационными выходами первых БЗУ, регистр сдвига МП, информационный выход старшего разряда которого соединен с его информационным входом младшего разряда и вторыми входами умножителей, два вторых БЗУ, информационные входы которых соединены с выходами умножителей, процессор прямого комплексного быстрого преобразования Фурье (ПКБПФ), информационные входы которого соединены с информационными выходами вторых БЗУ, блоки межканальной и межпериодной обработок (МКО и МПО), информационные входы которых соединены с информационными выходами процессора ПКБПФ, некогерентный накопитель на рециркуляторе со скользящим окном на всю длительность СС, информационные входы которого соединены с выходами АЦП, пороговое устройство, сигнальный вход которого соединен с выходом некогерентного накопителя, устройство управления, выходы сигналов обнаружения в одноканальном с ННМП и многоканальном с КНМП обнаружителях соединены с выходами порогового устройства и блока МКО соответственно, а выходы управления адресом и режимом чтения/записи первых, а также вторых БЗУ, сдвигом МП, вводом информации в процессор ПКБПФ, накоплением и принятием решения в блоке МПО и выдачи номера сигнального элемента временной неопределенности соединены с одноименными входами первых и вторых ВЗУ, регистра сдвига МП, процессора ПКБПФ, блоков МПО, а также блока ССН и ССЗ, выходы управления диапазоном поиска по частоте блоков МКО и МПО объединены и являются входом устройства, выходы блока МПО обнаружение СС и выдачи номера сигнального частотного канала соединены с блоком ССН и ССЗ, выходы выдачи оценок частоты и задержки СС блока ССП и ССЗ являются выходом устройства.

Применение СС, постоянно передаваемого с некоторым периодом между информационными символами независимо от передачи полезной информации с изменяющимися в каждом периоде параметрами, обеспечивает поддержание синхронизма между приемником и передатчиком в подвижных системах связи с "прерывистым" режимом передачи информации при перерывах в ее передаче.

Применение СС, манипулированного по фазе последовательностью, образованной суммированием по модулю 2 НП и МП, обработка в многоканальном по частоте обнаружителе с КНМП задержанного (следующего) СС позволяет повысить его энергетическую скрытность путем уменьшения длительности СС.

Применение многоканальной по частоте когерентной обработки МП повышает разрешение по частоте при поиске сигнала, это позволяет уменьшить время синхронизации за счет уменьшения времени отработки следящими системами синхронизации частотной неопределенности (времени установки частоты), а также повышает помехоустойчивость следящих систем синхронизации посредством улучшения отношения сигнал-помеха на входе дискриминаторов (частотного и временного) за счет уменьшения полосы пропускания полосовых фильтров, стоящих перед дискриминаторами. Повышение отношения сигнал-помеха на входе дискриминатора приводит к повышению стабильности крутизны его дискриминационной характеристики. Таким образом, применение предлагаемого способа синхронизации обеспечивает быструю синхронизацию и ее поддержание в подвижных системах связи с "прерывистым" режимом передачи информации, повышает скрытность и помехоустойчивость канала синхронизации.

Введение в устройство двух аналого-цифровых преобразователей, четырех БЗУ, двух умножителей, регистра сдвига МП, процессора ПКБПФ, некогерентного накопителя, порогового устройства, блоков МПО и МКО и устройства управления позволяет реализовать предлагаемый способ с использованием научно-технических достижений как в области временной (согласованные фильтры на ПЗС, ПАВ и др.), так и спектральной (процессоры БПФ) обработок, что значительно улучшает его технические характеристики.

Например, по сравнению с известным устройством быстрого поиска по частоте /коду /7/, содержащим перестраиваемый в диапазоне частотной неопределенности приемник, имеющим два квадратурных канала, перестраиваемые согласованные фильтры в каждом квадратурном канале, схемы выделения огибающей и поиска максимального значения огибающей, регистры информационного символа и управления частотой, память модулирующих псевдослучайных последовательностей с различными доплеровскими сдвигами частоты из диапазона частотной неопределенности, а также схему синхронизации, предлагаемое может обрабатывать сигналы с длительностью элемента сигнала порядка 100 нс. Обработка таких сигналов устройством /7/ технически затруднена из-за высоких требований к динамическим характеристикам перестраиваемых согласованных фильтров. В /7/ длительность элемента сигнала равна ~100 мкс. Отметим, что массогабаритные характеристики предлагаемого устройства будут незначительно уступать известному /7/ из-за того, что в нем используется процессор ПКБПФ.

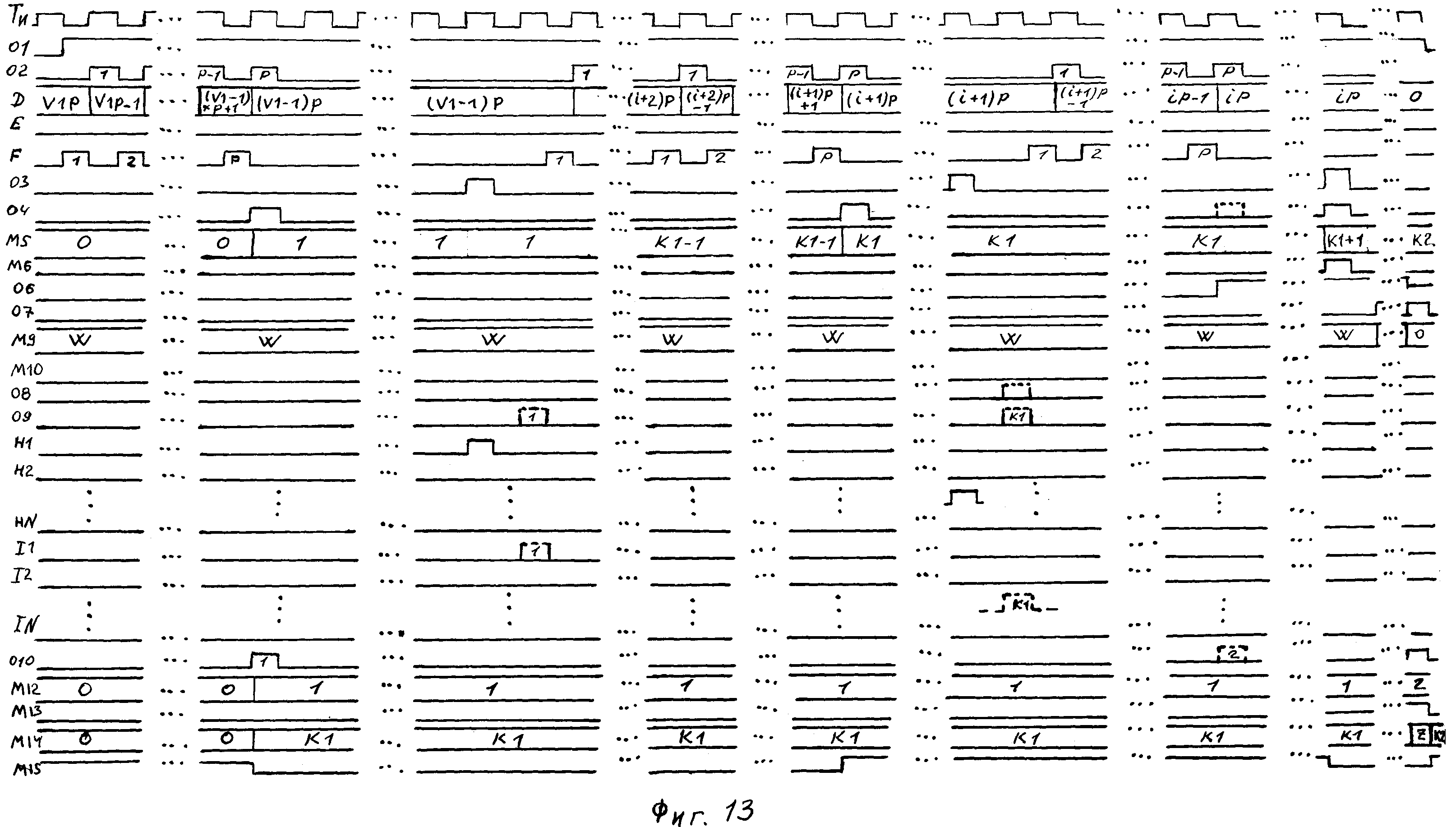

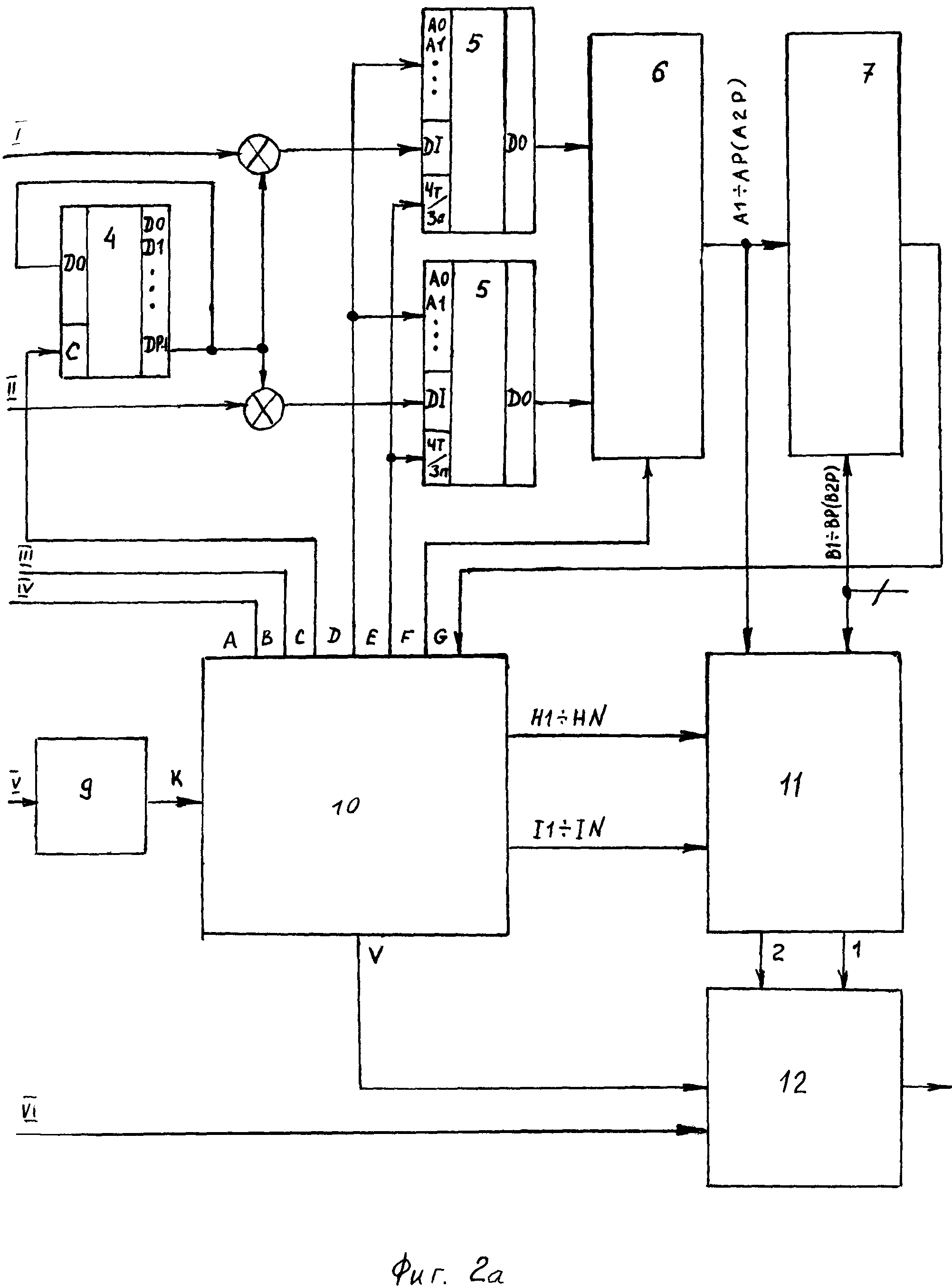

На фиг. 2 представлена структурная электрическая схема устройства для быстрой синхронизации в системах связи с ШПС, использующими "длинные" псевдослучайные последовательности.

Устройство содержит два квадратурных перемножителя, два перестраиваемых согласованных фильтра 1 на часть СС, манипулированную одним периодом НП, два АЦП2, два первых БЗУ 3, два умножителя, регистр сдвига МП 4, два вторых БЗУ 5, процессор ПКБПФ 6, некогерентный накопитель 8 на рециркуляторе со скользящим окном на всю длительность СС, пороговое устройство 9, блоки МКО 7 и МПО 11, устройство управления 10 и блок следящих систем по несущей и задержке 12 (ССН и ССЗ).

Квадратурные перемножители могут быть реализованы на аналоговых перемножителях 526ПС1, согласованные фильтры 1 - на дискретно-аналоговых процессорах свертки 528ХК1, Н1146ХК1, АЦП2 - на ИС 1107ПВ2, 1107ПВ3, умножители на ±1 (элемент МП) на ИС серии 533, 530.

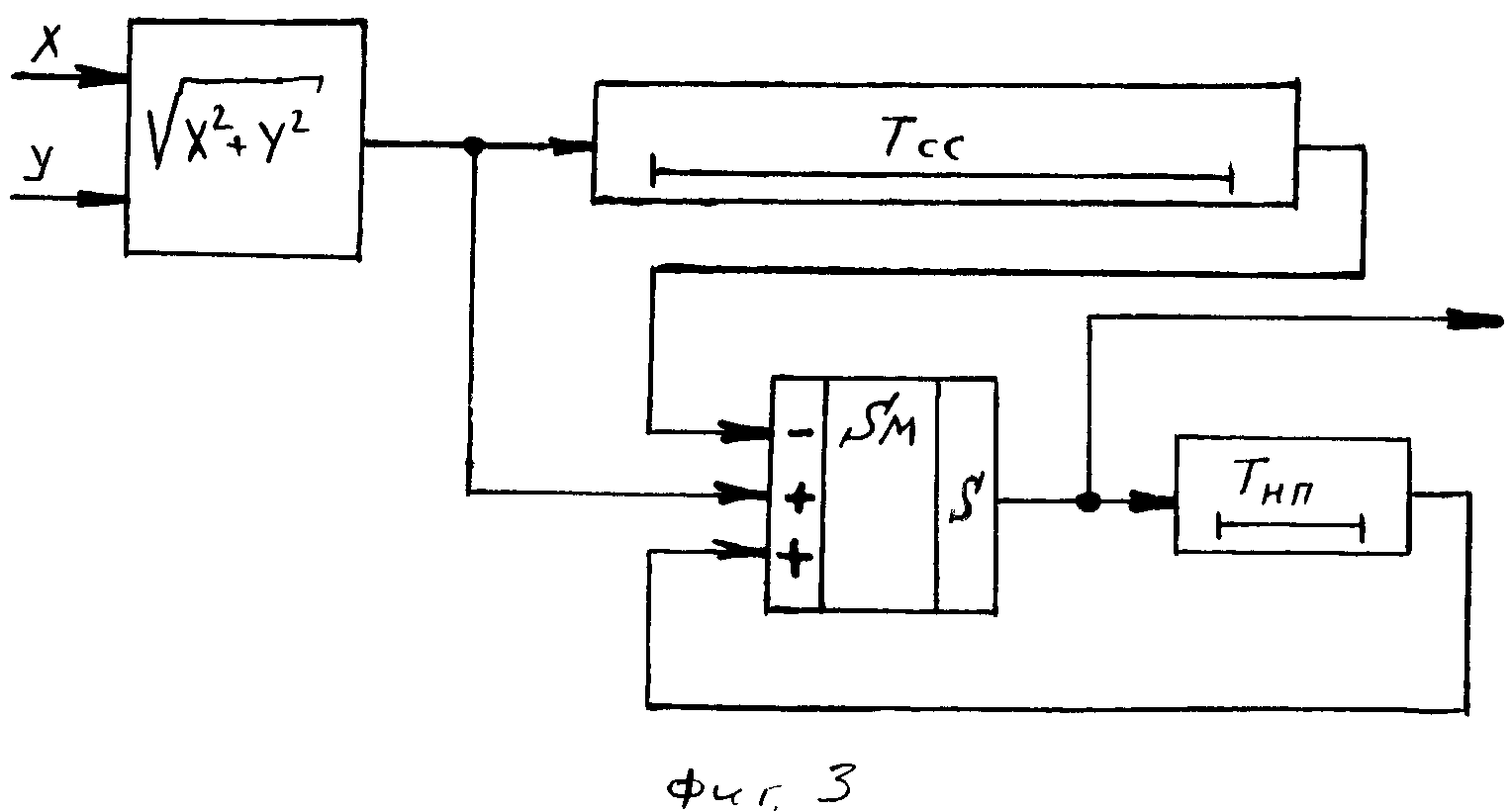

Некогерентный обнаружитель 8 на рециркуляторе со скользящим окном на всю длительность СС может быть реализован по структурной электрической схеме, показанной на фиг. 3 и содержит блок вычисления огибающей, реализующий операцию  , две линии задержки (ЛЗ), одна из которых задерживает сигнал на длительность одного периода НП ТНП, а вторая - на длительность всего сигнала синхронизации ТСС, и трехвходовый сумматор. Линии задержки могут быть реализованы на регистрах сдвига или БИС ОЗУ. Выполнение операции вида

, две линии задержки (ЛЗ), одна из которых задерживает сигнал на длительность одного периода НП ТНП, а вторая - на длительность всего сигнала синхронизации ТСС, и трехвходовый сумматор. Линии задержки могут быть реализованы на регистрах сдвига или БИС ОЗУ. Выполнение операции вида  может быть реализовано на БИС ПЗУ.

может быть реализовано на БИС ПЗУ.

Все элементы некогерентного накопителя 8 работают с тактовой частотой, равной частоте дискретизации. На каждом такте на его выходе будет формироваться код, равный сумме Р отсчетов огибающих СС, следующих с периодом НП ТНП, во временном окне, равном длительности СС ТСС. Такая работа обеспечивается наличием в схеме рециркулятора (сумматор и ЛЗ с задержкой на один период НП) и ЛЗ на длительность СС. В рециркуляторе происходит накопление отсчетов сигнала, следующих с периодом, равным периоду НП, ЛЗ на длительность СС обеспечивает вычитание из результата накопления тех отсчетов сигнала, которые выходят за пределы временного окна, равного длительности СС (эти отсчеты появляются на ее выходе).

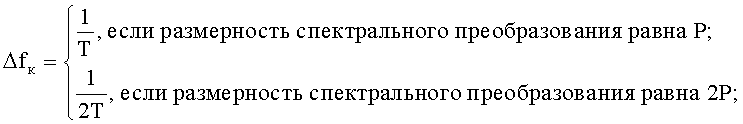

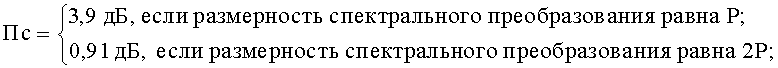

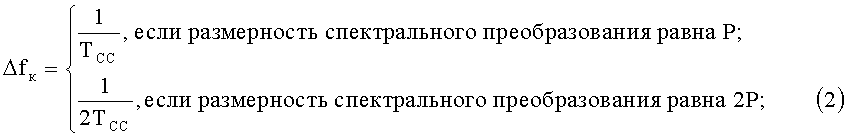

Процессор ПКБПФ 6 используется как многоканальный по частоте согласованный фильтр СС с детектором огибающей на выходе каждого канала. Размерность спектрального преобразования (число частотных каналов) может быть равно числу элементов модулирующей последовательности Р или в два раза больше (2Р). В зависимости от выбранной размерности спектрального преобразования ширина полосы одного частотного канала Δfк и величина подавления полезного сигнала на границе двух соседних частотных каналов (потери сигнала) Пс равны

При использовании 2Р-точечного спектрального преобразования каждая серия из Р синфазных и квадратурных отсчетов сигнала должны дополняться Р нулями. Процессор ПКБПФ 6 может быть реализован по хорошо известным и достаточно изученным алгоритмам /3, 4/ на БИС сумматоров и умножителей серий 1802, К1815ВФ3, 1832, 1838 и др. Для упрощения понимания работы устройства предположим, что процессор ПКБПФ 6 функционирует следующим образом. Вначале из вторых БЗУ 5 в процессор ПКБПФ 6 последовательно считывается серия из Р синфазных и квадратурных временных отсчетов СС. После окончания процесса считывания одной серии временных отсчетов начинается их спектральное преобразование. После завершения спектрального преобразования на выход A1-AP (A2P) процессора ПКБПФ 6 в параллельном двоичном коде одновременно выдаются Р (2Р) модулей спектральных компонент (огибающих сигналов частотных каналов).

Отметим, что при необходимости работа процессора ПКБПФ 6 может быть организована и по-другому. Например, вначале осуществляется спектральное преобразование всех серий временных отсчетов, хранимых во вторых БЗУ 5, результаты спектрального преобразования загружаются в отдельное буферное ОЗУ процессора ПКБПФ 6 или считывание серии временных отсчетов из вторых БЗУ 5 осуществляется по одной серии, как описывалось выше, а выдача модулей спектральных компонент может осуществляться последовательно по мере их вычисления в процессоре ПКБПФ 6. Другая работа процессора ПКБПФ 6 приведет к необходимости некоторого изменения структуры устройства управления 10, блоков МКО 7 и МПО 11. Однако это никак не отражается на общей структуре и алгоритме работы устройства.

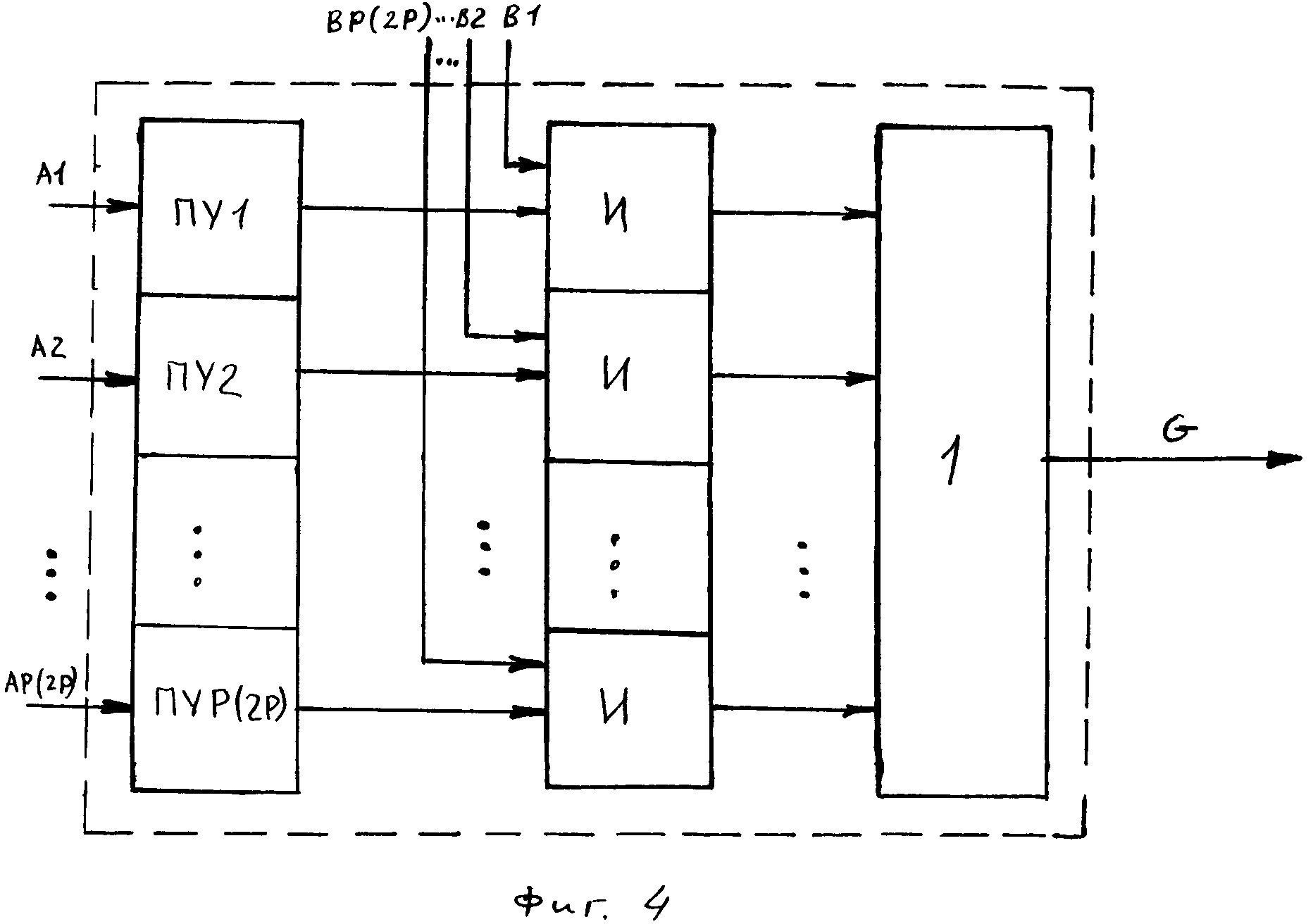

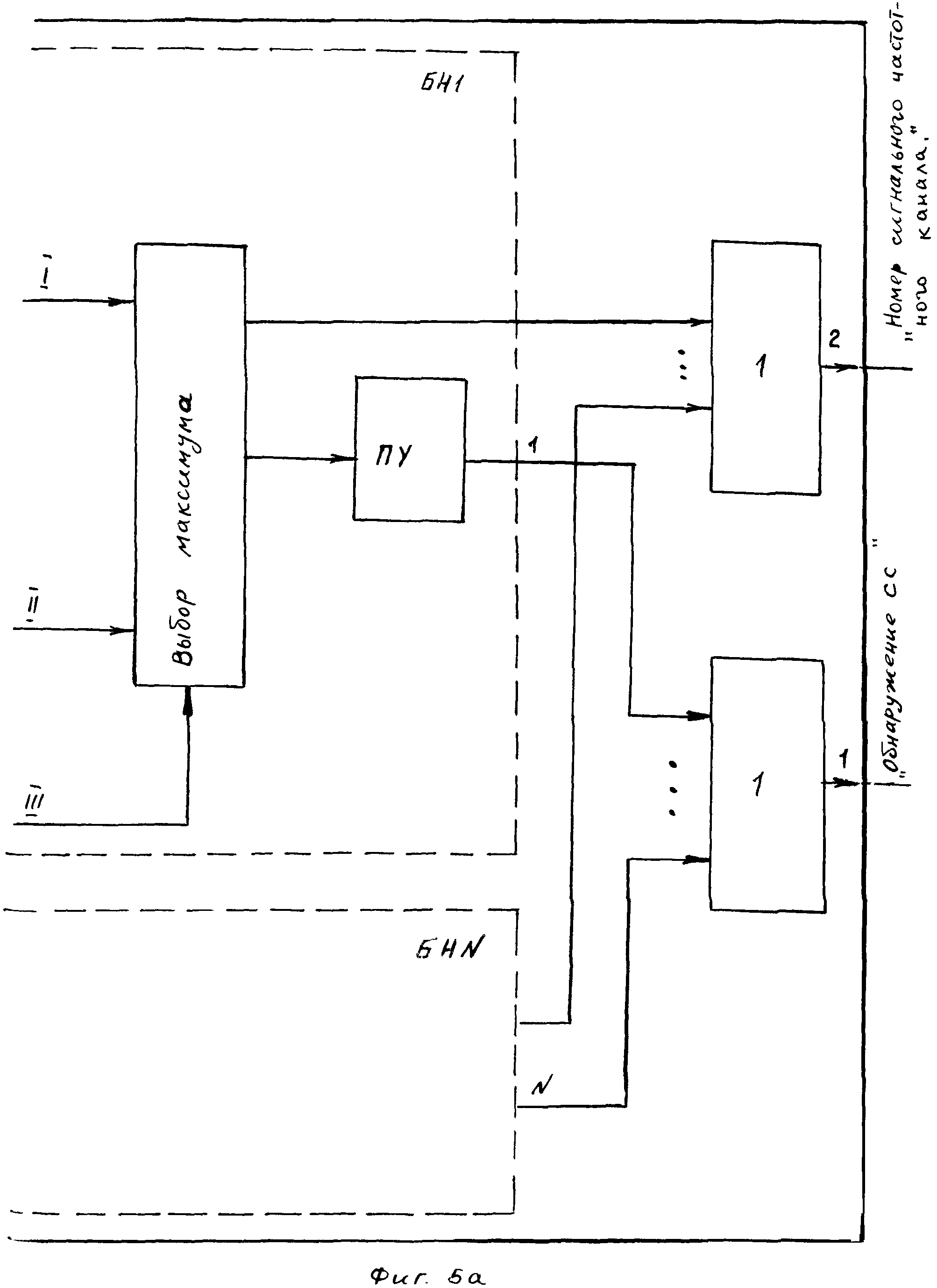

Блок МКО 7 может быть реализован, например, по структурной электрической схеме, показанной на фиг. 4 и содержит Р (2Р) каналов. В пороговом устройстве ПУ входной сигнал сравнивается с порогом обнаружения, выставленным в соответствии с требуемыми вероятностями правильного обнаружения и ложной тревоги. С помощью логических элементов "И" сигналами управления диапазоном поиска на частоте B1-BP (B2P) осуществляется блокировка тех частотных каналов, в которых по априорным оценкам сигнала нет. Если один из входных сигналов блока МКО 7 (один из сигналов частотных каналов) превышает порог обнаружения, то на его выходе формируется сигнал G "Обнаружение в многоканальном обнаружителе (МО)" при условии, что сигнал (частотный канал) находится в заданном диапазоне частотной неопределенности.

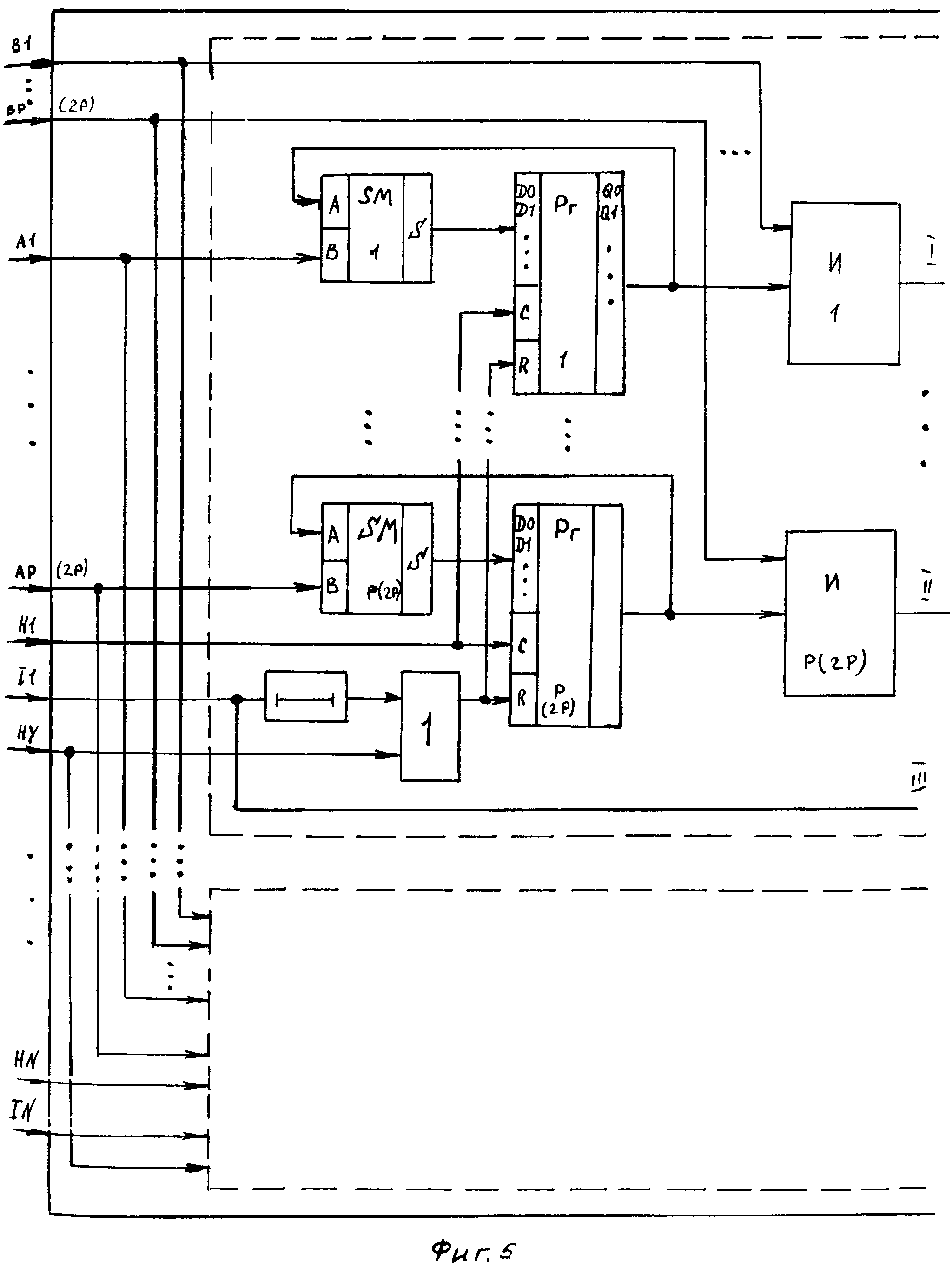

Блок МПО 11 может быть реализован, например, по структурной электрической схеме, показанной на фиг. 5, и содержит N блоков накопления БН1-БНN, где N равно числу ЭВН, анализируемых на этапе проверки и измерения параметров СС, которое не превышает числа спектральных преобразований, выполняемых процессором ПКБПФ 6 за один период СС. В каждом блоке содержится Р (2Р) накапливающих сумматоров, в которых производится накопление сигналов Р (2Р) - частных каналов А1-АР (2Р) на i-м проверяемом ЭВН. По окончании спектрального преобразования в процессоре ПКБПФ устройством управления 10 вырабатывается сигнал Hi "Накопление в i-м БН", по которому сумма текущего значения сигнала каждого частотного канала и накопленное ранее значение записываются в регистры Рг1÷РгР (2P). Выходы регистров через элементы И1-ИР (2P) поступают на выходы схемы выбора максимума, если сигнал управления диапазоном поиска по частоте В1-ВР (2Р) не блокирует его. Т.е. на вход схемы выбора максимума проходят сигналы тех частотных каналов, которые находятся в диапазоне частотной неопределенности. После окончания накопления устройством управления 10 формируется сигнал Ii "Принятие решения в i-м БН". Этот сигнал разрешает работу схемы выбора максимума, которая выдает номер частотного канала с максимальным уровнем сигнала (номер сигнального частотного канала) через элемент "ИЛИ" на выход 2 блока МПО и максимальный сигнал на вход порогового устройства ПУ с порогом обнаружения, выставленным в соответствии с требуемыми вероятностями правильного обнаружения и ложной тревоги. Если порог превышается, то на выходе 1 блока МПО формируется сигнал "Обнаружение СС", а по номеру частотного канала с максимальным уровнем сигнала, выдающегося на выход 2, определяется частота СС.

Заметим, что решающая схема блока МПО может быть построена другим образом. Например, решение может приниматься после окончания накопления во всех ЭВН, выделенных за один цикл анализа всего диапазона временной неопределенности (в одном стробе диапазона временной неопределенности), путем выбора максимального из всех частотных каналов, накопленных во всех ЭВН и сравнения его с порогом. При превышении порога по номеру частотного канала может быть определена частота СС.

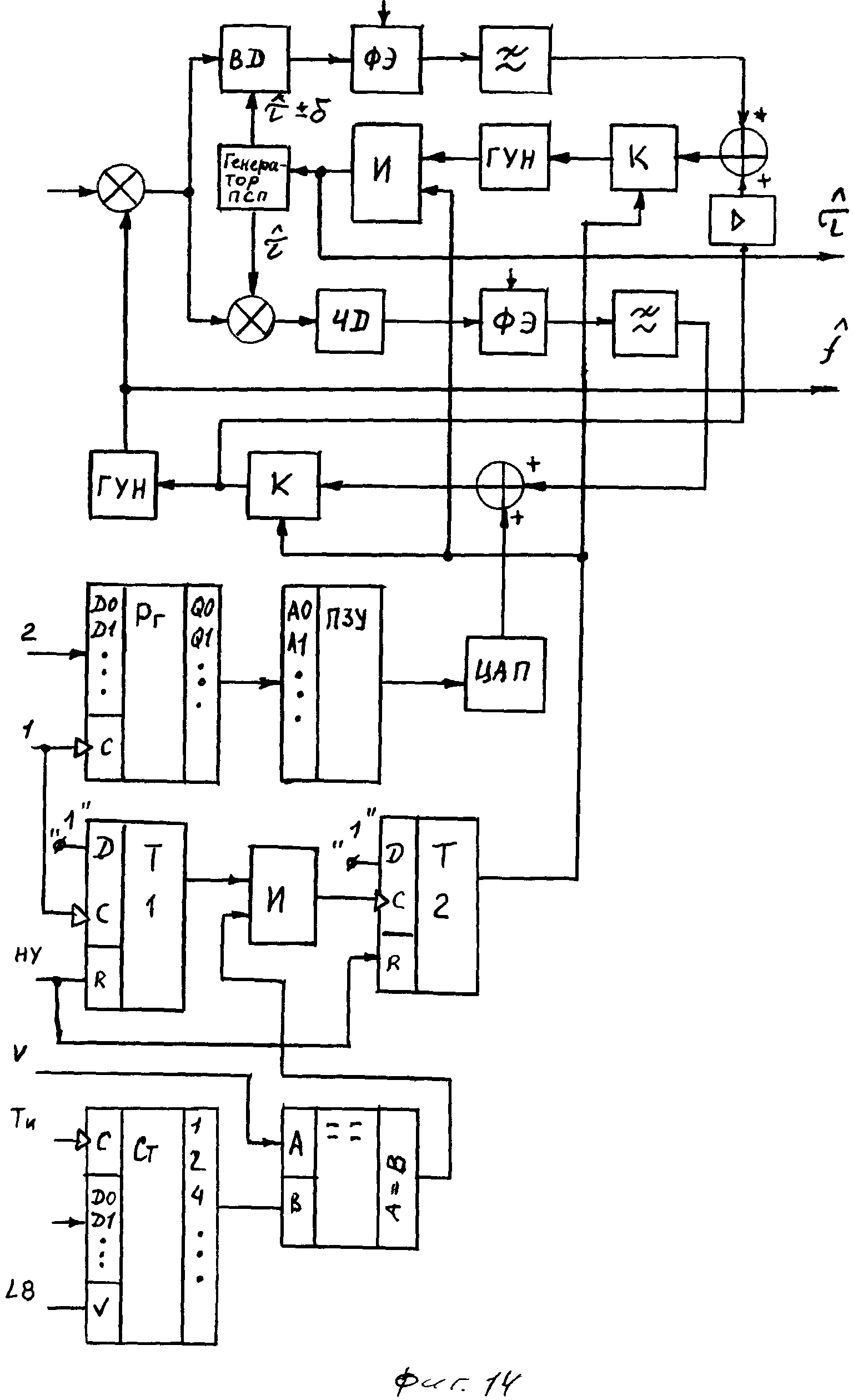

Возможный вариант блока 12 ССН и ССЗ показан на фиг. 14 и содержит следящие системы по несущей (частотный (фазовый) дискриминатор 4Д, фиксирующий элемент ФЭ, петлевой фильтр, сумматор, ключ К, и генератор, управляемый напряжением ГУН), задержке (временной дискриминатор ВД, фиксирующий элемент ФЭ, петлевой фильтр, сумматор, ключ К, ГУН, элемент И, а также генератор псевдослучайной последовательности ПСП сигнала сихронизации) /5/ и группу известных цифровых схем. При поступлении на вход блока сигнала 1 "Обнаружение СС" с блока МПО 11 триггер Т1 устанавливается в "1", а в регистр записывается номер частотного капала, при анализе которого принимается гипотеза о наличии сигнала. По этому номеру с помощью постоянного запоминающего устройства (ПЗУ) и цифроаналогового преобразователя (ЦАП) на вход сумматора ССН поступает напряжение, обеспечивающее установку ГУН-а петли в соответствии с измеренным значением. При поступлении на вход блока сигнала L8 "Строб СС" в счетчик (Ст) записывается код числа, равного количеству ЗВН в СС, и начинается счет тактовых импульсов. Такая начальная установка счетчика обеспечивает срабатывание схемы сравнения в момент начала поступления СС, так как номер ЭВН, поступающий на вход V блока, соответствует моменту окончания СС. При срабатывании схемы сравнения триггер Т2 устанавливается в "1", что приводит к замыканию следящих систем синхронизации и поступлению тактовых импульсов на вход генератора ПСП. Фиксирующий элемент осуществляет запоминание выходных сигналов ВД и ЧД в паузах между СС. Это обеспечивается подачей на их управляющие входы управляющих импульсов в момент окончания СС. С помощью масштабирующего усилителя и сумматора производится ввод доплеровского сдвига частоты в ССЗ. С помощью блока 12 ССН и ССЗ осуществляется слежение за СС в течение всего сеанса связи. Если захвата сигнала не происходит, поиск продолжается. Пороговые устройства и схемы выбора максимума могут быть реализованы на ИС сравнения, как показано в /6/ на рис. 7, 23.

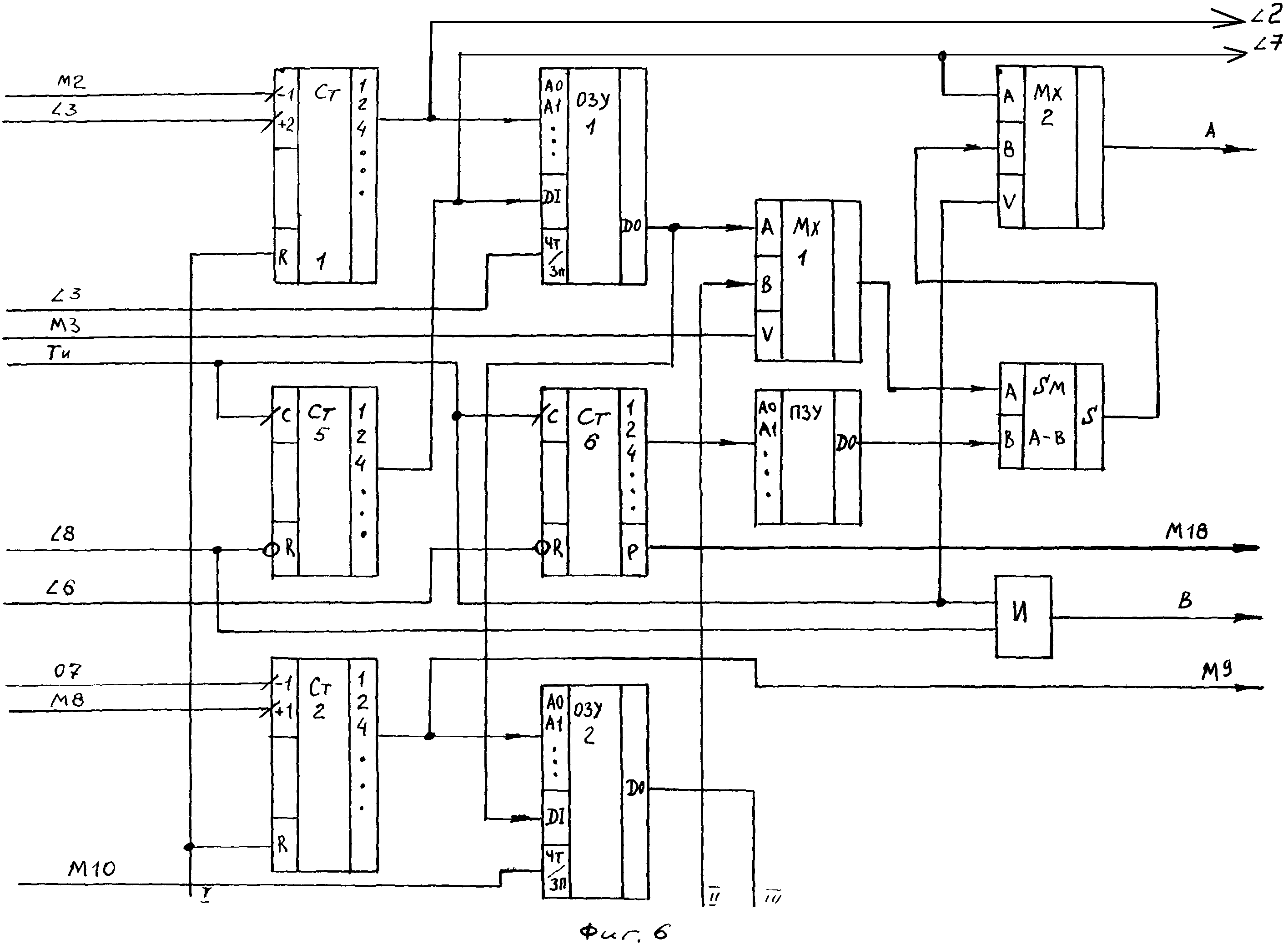

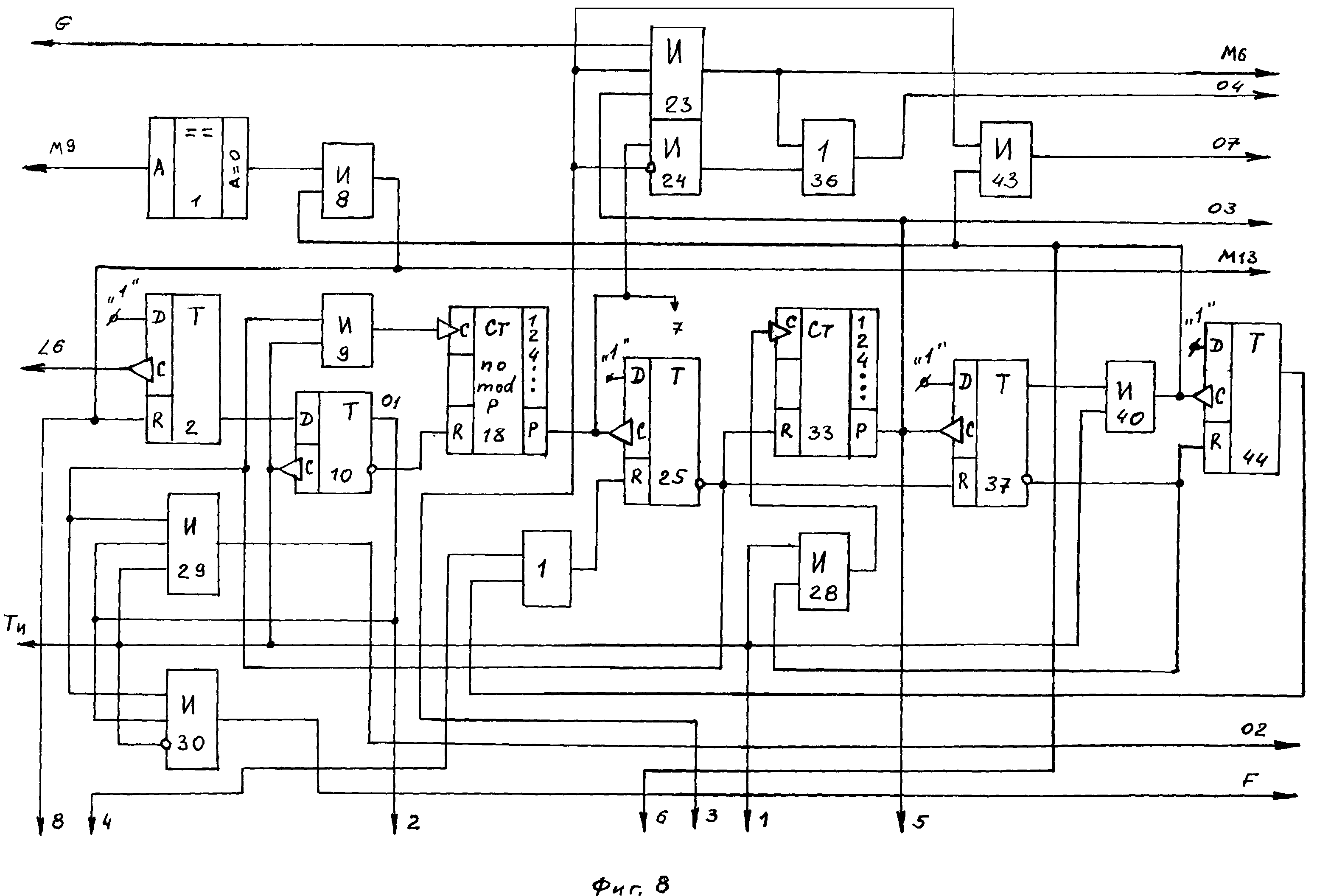

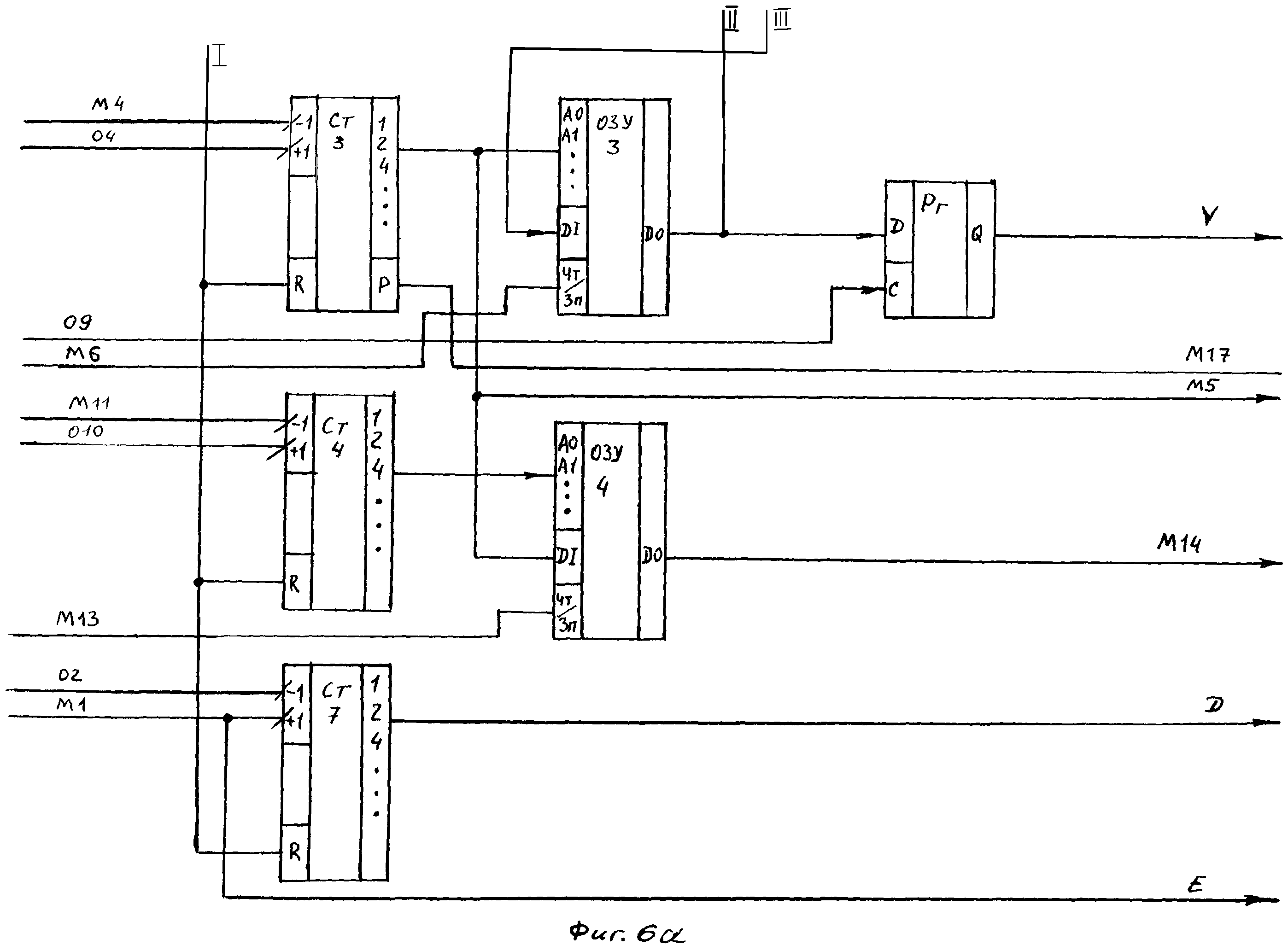

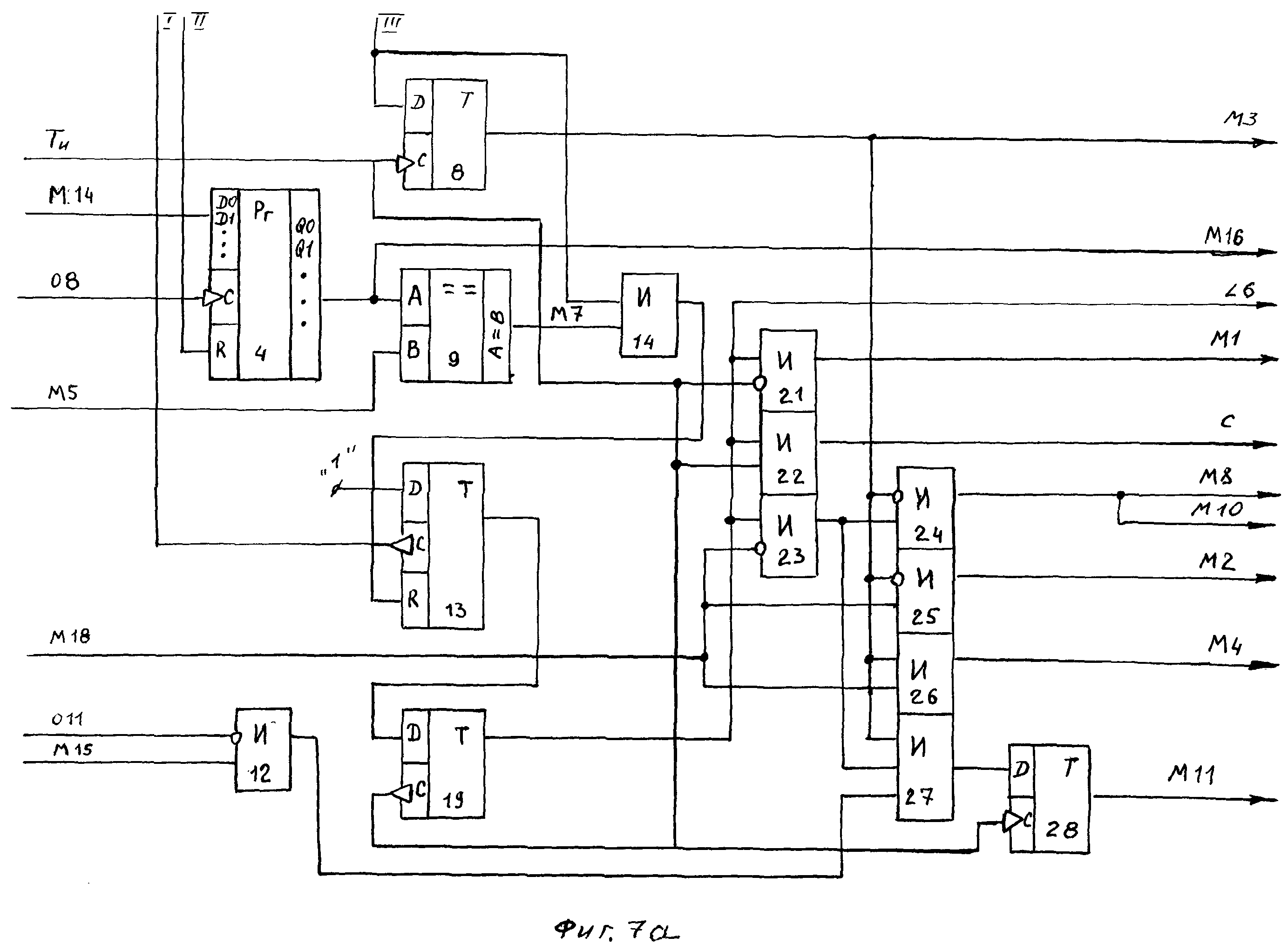

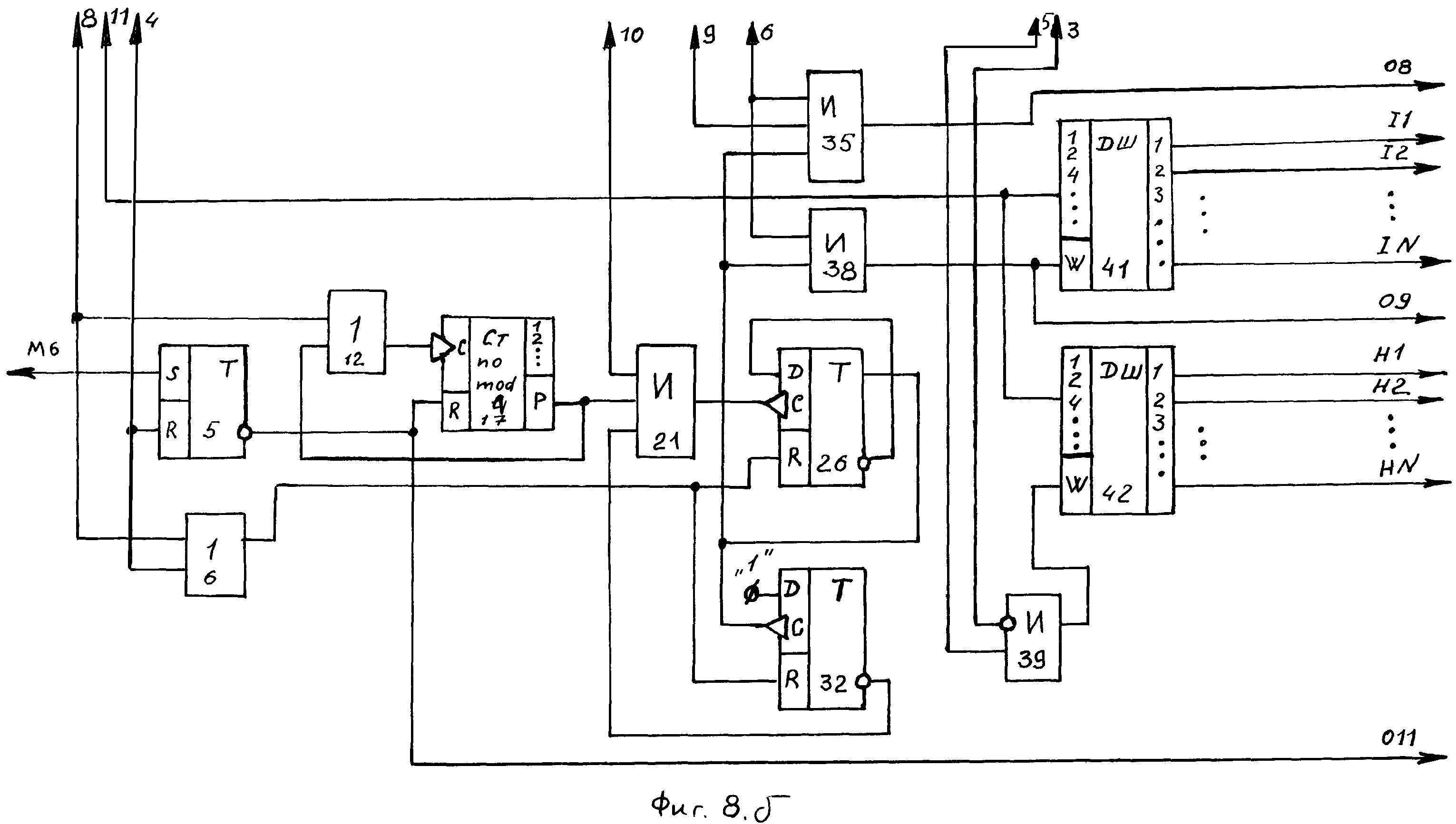

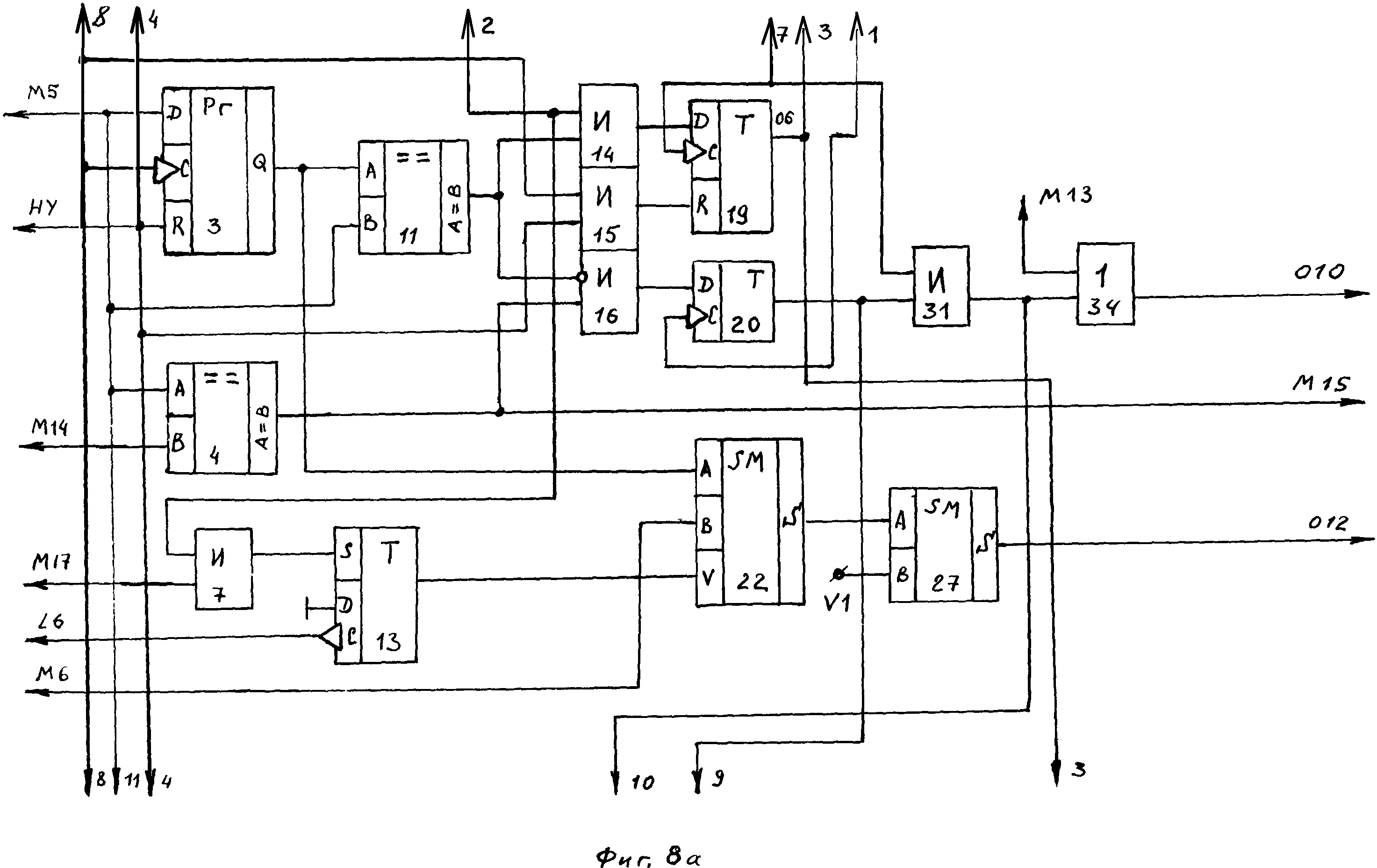

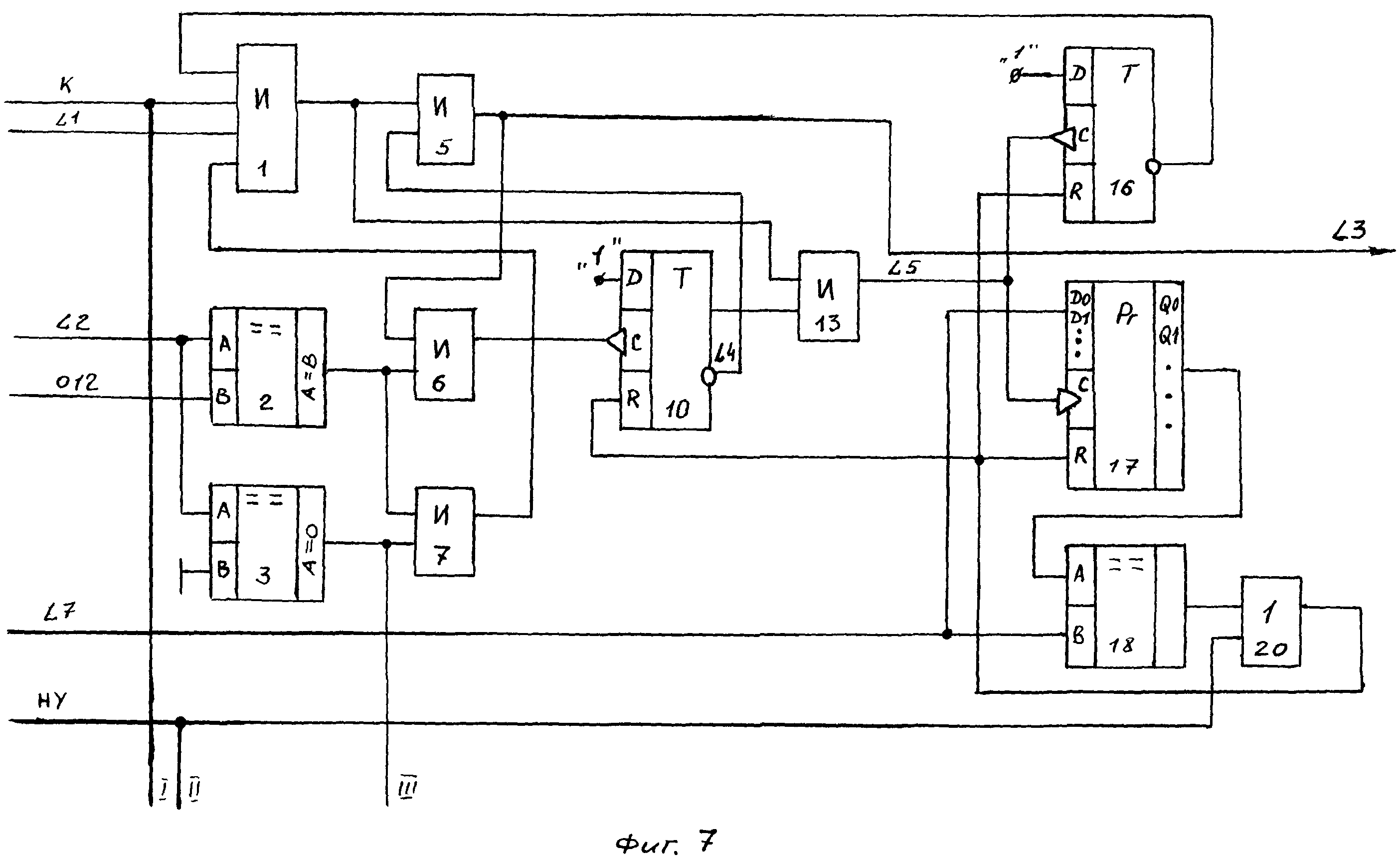

Устройство управления 10 может быть реализовано, например, из блоков формирования адреса (ФА), управления в режиме записи и перезаписи (УРЗ и П), а также управления в режиме обработки (УРО), возможные схемы которых показаны на фиг. 6, 7 и 8 соответственно.

В блоке ФА количество ячеек памяти в ОЗУ 1-ОЗУ 2 выбирается одинаковым и равным числу спектральных преобразований, выполняемых процессором ПК БПФ за один период СС. Количество ячеек памяти ОЗУ 3 и ОЗУ 4 равно числу ЭВН, анализируемых на этапе проверки и измерения параметров СС (равно количеству блоков накопления в блоке МРО 11). Разрядность ОЗУ 1-ОЗУ 4 равна log2t, где t - число ЭВН.

Работу устройства управления 10 целесообразно рассматривать совместно с работой устройства в целом. Поэтому рассмотрим работу устройства.

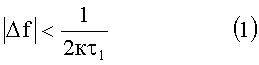

Рассмотрим систему связи, в которой для формирования шумоподобных сигналов используются "длинные" псевдослучайные последовательности. Например, в системах связи с фазоманипулированными шумоподобными сигналами (ФМ ШПС) "длинная" псевдослучайная последовательность (ПСП) определяет закон ФМ сигнала, в системах связи с псевдослучайной перестройкой рабочей частоты (ППРЧ) "длинная" ПСП определяет закон переключения рабочей частоты. В таких системах связи для приема информации необходимо выполнить апериодическую синхронизацию. Пусть для быстрой синхронизации приемника и передатчика используется специальный сигнал синхронизации (СС), представляющий собой ФМ ШПС, закон ФМ которого определяется последовательностью, образованной суммированием по mod2 несущей (внутренней) последовательности (НП) и модулирующей (внешней) последовательности (МП). Причем длительность НП равна длительности элемента МП. Такие сложные сигналы называются составными ФМ ШПС с противоположными сложными элементами. СС передается с некоторым периодом в течение всего сеанса связи между информационными символами независимо от передачи полезной информации. Параметры СС (например, период следования, несущая частота, НП и МП) меняются по известному как на приемной, так и передающей сторонах закону. Параметры СС (длительность элемента НП, число элементов несущей К и модулирующей Р последовательностей, период следования) выбираются таким образом, чтобы при заданных отношениях сигнал-помеха, диапазонах частотной Δf и временной Δt неопределенностей обеспечить быстрое и надежное его обнаружение. Длительность элемента τ1 и число элементов К НП выбираются так, чтобы перекрыть весь диапазон частотной неопределенности Δf, т.е.

Число элементов Р выбирается таким образом, чтобы при заданном входном отношении сигнал-помеха обеспечить требуемые вероятности ложной тревоги, правильного обнаружения и разрешения по частоте. Ширина одного частотного канала Δfк обнаружителя равна

где ТСС=КР - длительность СС.

Устройство для быстрой синхронизации содержит два обнаружителя: одноканальный обнаружитель с некогерентным накопителем МП (ННМП) и многоканальный по частоте обнаружитель с когерентным накопителем МП (КНМП), блок межпериодной обработки 11 (МПО 11) и устройство управления 10.

Многоканальный по частоте обнаружитель с КНМП состоит из двух квадратурных каналов, в каждом из которых содержится перемножитель, согласованный фильтр 1 (СФ 1) сложного элемента СС (согласованный фильтр на часть СС, манипулированную одним периодом НП), аналого-цифровой преобразователь 2 (АЦП 2), первое буферное запоминающее устройство 3 (БЗУ3), умножитель, второе БЗУ 5, процессора прямого комплексного быстрого преобразования Фурье 6 (ПК БПФ 6), а также блока межканальной обработки 7 (МКО 7). Одноканальный обнаружитель с ННМП содержит некогерентный накопитель 8 (НН8) на рециркуляторе со "скользящим окном" на всю длительность СС и пороговое устройство 9 (ПУ 9).

При выполнении условия (I) диапазон частотой неопределенности будет перекрываться обоими обнаружителями.

Синхронизация осуществляется следующим образом. Вначале с помощью одноканального обнаружителя с ННМП выполняется периодическая синхронизация по НП путем последовательного анализа элементов временной неопределенности (ЭВН) во всем диапазоне частотной неопределенности в реальном времени и запоминания номеров тех ЭВН, при анализе которых в обнаружителе принимается гипотеза о наличии сигнала. Назовем эти ЭВН "сигнальными". Затем с помощью многоканального по частоте обнаружителя с КНМП выполняется апериодическая синхронизация. Для снижения требований к быстродействию многоканального обнаружителя с КНМП (производительности процессора ПКБПФ 6) в нем обрабатывается задержанный на длительность СС и более (следующий) сигнал только в "сигнальных" ЭВН. Задержка сигнала в многоканальном обнаружителе с КНМП осуществляется с помощью первых БЗУ 3, в которые вначале последовательно записываются квадратурные отсчеты выходных сигналов СФ1, а затеи с задержкой, равной или более длительности СС, производится последовательное считывание серий квадратурных отсчетов выходных сигналов СФ1 (каждая серия состоит из Р квадратурных отсчетов, следующих с периодом, равным длительности сложного элемента), соответствующих "сигнальным" ЭВН. Назовем эти серии отсчетов "сигнальными".

В многоканальном по частоте обнаружителе с КНМП обработка осуществляется следующим образом. При последовательном считывании "сигнальных" серий квадратурных отсчетов с первых БЗУ 3 производится демодуляция МП путем умножения каждого комплексного отсчета на элемент МП. Результаты умножения записываются во вторые БЗУ 5. После перезаписи с умножением по МП всех "сигнальных" серий комплексных отсчетов во вторые БЗУ 5 начинается их обработка в процессоре ПКБПФ 6. Процессор ПКБПФ 6 используется как многоканальный (Р (2Р)-канальный) по частоте согласованный фильтр.

Номера ЭВН, при анализе которых в блоке МКО 7 принимается гипотеза о наличии сигнала, запоминаются для проведения проверки и измерения параметров СС. Проверка и измерение производятся блоком МПО 7 путем накопления результатов спектрального преобразования в течение некоторого количества СС, достаточного для его надежного обнаружения и измерения параметров. Если и блоке МПО 11 принимается гипотеза о наличии сигнала, то по номеру частотного канала и ЭВН, в которых произошло его обнаружение, определяют частоту и задержку СС. По оценкам частоты и задержи СС осуществляется наведение следящих систем по частоте и задержке, их замыкание и слежение за СС в течение всего сеанса связи.

Пороги обнаружения в блоках МКО 7 и МПО 11 устанавливаются таким образом, чтобы при заданной вероятности успешного завершения поиска минимизировать среднее время обнаружения СС.

Порог обнаружения в одноканальном обнаружителе с ННМП устанавливается так, чтобы, во-первых, вероятность правильного обнаружения были не хуже, чем в многоканальном обнаружителе с КНМП (в блоке МКО 7). Так как при некогерентном накоплении МП возникают потери, особенно при низких отношениях сигнал-помеха на выходе СФ1, то для обеспечения такой же вероятности правильного обнаружения порог в одноканальном обнаружителе с ННМП устанавливается ниже, чем в многоканальном обнаружителе с КНМП. Во-вторых, уровень ложных тревог должен быть таким, чтобы производительности процессора ПКБПФ хватило для обработки "сигнальных" серий отсчетов. Если в одноканальном обнаружителе с ННМП порог установлен в соответствии с приведенными выше двумя условиями, то вероятности ложной тревоги и правильного обнаружения на этапе апериодической синхронизации будут определяться только многоканальным обнаружителем с КНМП. Если производительность процессора ПКБПФ 6 не обеспечивает обработку всех "сигнальных" серий отсчетов, то в одноканальной обнаружителе с ННМП порог необходимо поднять, чтобы уменьшить число обрабатываемых в процессоре "сигнальных" серий отсчетов (уменьшить вероятность ложной тревоги. Однако это вызовет соответствующее уменьшение вероятности правильного обнаружения на этапе периодической синхронизации, а значит и апериодической.

Использование многоканального по частоте обнаружителя с когерентной обработкой МП позволяет исключить (частично исключить при нарушении первого условия) потери в одноканальном обнаружителе с ННМП вызывание некогерентным накопителем сложных элементов СС, увеличить точность измерения частоты несущей СС и выполнить апериодическую синхронизацию по МП. Увеличение точности измерения частоты несущей СС позволяет уменьшить время втягивания следящих систем синхронизации (ССН и ССЗ) за счет уменьшения времени установления частоты, а также повышает помехоустойчивость следящих систем синхронизации за счет улучшения отношения сигнал-помеха на входе дискриминаторов путем уменьшения полосы пропускания фильтров, стоящих перед дискриминаторами.

Следует отметить, что при достаточно хорошем отношении сигнал/помеха синхронизация может быть выполнена в три этапа. В этом случае на втором этапе должны осуществляться не только многоканальный поиск МП в ЭВН, номера которых зафиксированы на первом этапе, во всем диапазоне частотной неопределенности, апериодическая синхронизация по МП, но и измерение частоты и задержки СС посредством задержки на длительность СС и более принимаемого сигнала, многоканальной по частоте согласованной фильтрации задержанного СС с КНМП, детектирования огибающих, принятии решения о наличии сигнала, оценки его задержки и частоты СС. Затем может быть выполнен четвертый этап синхронизации. В этом случае в устройстве для синхронизации может быть исключен блок МКО 7, а в блоке МПО 11 решение должно приниматься по одному СС без его накопления в течение нескольких периодов.

Кроме того, на втором этапе может производиться обработка не задержанного СС, а следующего, что упрощает устройство для синхронизации. (Объем памяти первых БЗУ может быть значительно уменьшен, так как не требуется выполнять задержку СС, а необходимо только запоминать отсчеты СС в "сигнальных" ЭВН).

Рассмотрим более подробно работу устройства с описанием работы устройства управления 10.

В исходном состоянии ОЗУ 1-ОЗУ 4 устройства управления (УУ) 10 (блока ФА) обнулены, на вход устройства управления 10 и блока МПО 11 поступает сигнал начальной установки НУ, устанавливающий элементы схемы и начальное состояние. На входы управления диапазонов поиска по частоте В1-ВР (2P) поступают управляющие сигналы, определяющие число частотных каналов, подлежащих анализу в блоках МКО 7 и МПО 11. Эти сигналы формируются по результатам априорной оценки несущей частоты СС.

В квадратурных перемножителях формируются квадратурные составляющие принимаемого сигнала и осуществляется перенос спектра сигнала на частоту, удобную для обработки в СФ1, например, на видеочастоту. В СФ1 производится обработка (сжатие) части СС, манипулированной одним периодам НП. При приеме СС на выходах СФ1 будет наблюдаться периодические последовательности импульсов основных лепестков АКФ НП, манипулированных по фазе в соответствии с МП и модулированных доплеровским сдвигом частоты. Период следования импульсов АКФ равен длительности сложного элемента СС (периоду НП). Ширина основного лепестка АКФ равна τ1 по уровню 0,5 от максимального значения. В АЦП2 с частотой Fт (по l выборок на один элемент НП, обычно l=2) производится квантование сигналов СФ1 по времени и уровню. Разрядность n АЦП выбирается из заданных отношения сигнал-помеха и требуемого динамического диапазона сигнала. Отсчеты квадратурных составляющих выходных сигналов СФ1 поступают на информационные входы первых БЗУ 3 и некогерентный накопитель 8 на рециркуляторе со "скользящим" окном на всю длительность СС. В некогерентном накопителе 8 на каждом такте осуществляется некогерентное сложение Р отсчетов огибающих выходных сигналов СФ1, следующих с периодом равным периоду НП. При прохождении СС через некогерентный накопитель 8, на его выходе появится пачка из 2Р-1 импульсов нарастающей и спадающей по линейному закону амплитудой, период следования которых равен периоду НП. Любой из этих импульсов, особенно находящихся вблизи центрального, может превышать порог обнаружения в пороговом устройстве 9 (ПУ 9). При превышении порога в ПУ9 формируется сигнал К "Обнаружение в одноканальном обнаружителе (ОО)", поступающий на вход устройства управления 10. Полный цикл работы устройства состоит из трех циклов: цикла "записи", цикла "перезаписи" и цикла "обработки".

Первый полный цикл работа устройства начинается с первого цикла "Записи", когда на вход блока ФА устройства управления поступает первый импульс сигнала L8 "Строб СС", обозначающий возможные моменты начала и окончания поступления квадратурных отсчетов СС с выхода СФ1 на выходы первых БЗУ3. Сигнал L8 "Строб СС" формируется по результатам априорной оценки задержи СС. В первом цикле "Записи" в первые БЗУ 3 записываются все квадратурные отсчеты выходных сигналов СФ1, а в устройстве управления 10 (в ОЗУ 1 блока ФА) записываются адреса последних (p-x) квадратурных отсчетов выходных сигналов СФ1 из "сигнальных" серии (адрес "сигнальной" серии). По адресу "сигнальной" серии в первых БЗУ 3 однозначно определяется номер "сигнального" ЭВН, соответствующий этой серии. Это обеспечивается синхронизацией работы счетчика Ст5 блока ФА устройства управления 10 сигналом "Строб СС", который привязан к временной сетке приемника.

При поступлении сигнала "Строб СС" в блоке ФА устройства управления 10 начинает работать счетчик Ст5, мультиплексор МХ2 включается на передачу канала А (выход счетчика Ст5 выдается на выход А устройства управления 10) открывается элемент И, чем обеспечивается выдача сигнала записи В (высокий уровень) в первые БЗУ3. Это обеспечивает последовательную запись квадратурных отсчетов выходных сигналов СФ1 в ячейки первых БЗУ 3.

До поступления на вход блока ФА устройства управления 10 сигнала L1 "Строб ДВН" появление сигнала К с ПУ9 "Обнаружение в ОО" высокий уровень не приводит к каким-либо изменениям в работе устройства. Сигнал L1 "Строб ДВН" обозначает возможные моменты появления СС на входе некогерентного накопителя 8 (возможные моменты появления сигнала "Обнаружение в ОО") и формируется по результатам априорной оценки задержки СС. Сигнал L1 "Строб ДВН" появляется с задержкой на длительность СС Тсс после поступления сигнала L8 "Строб СС".

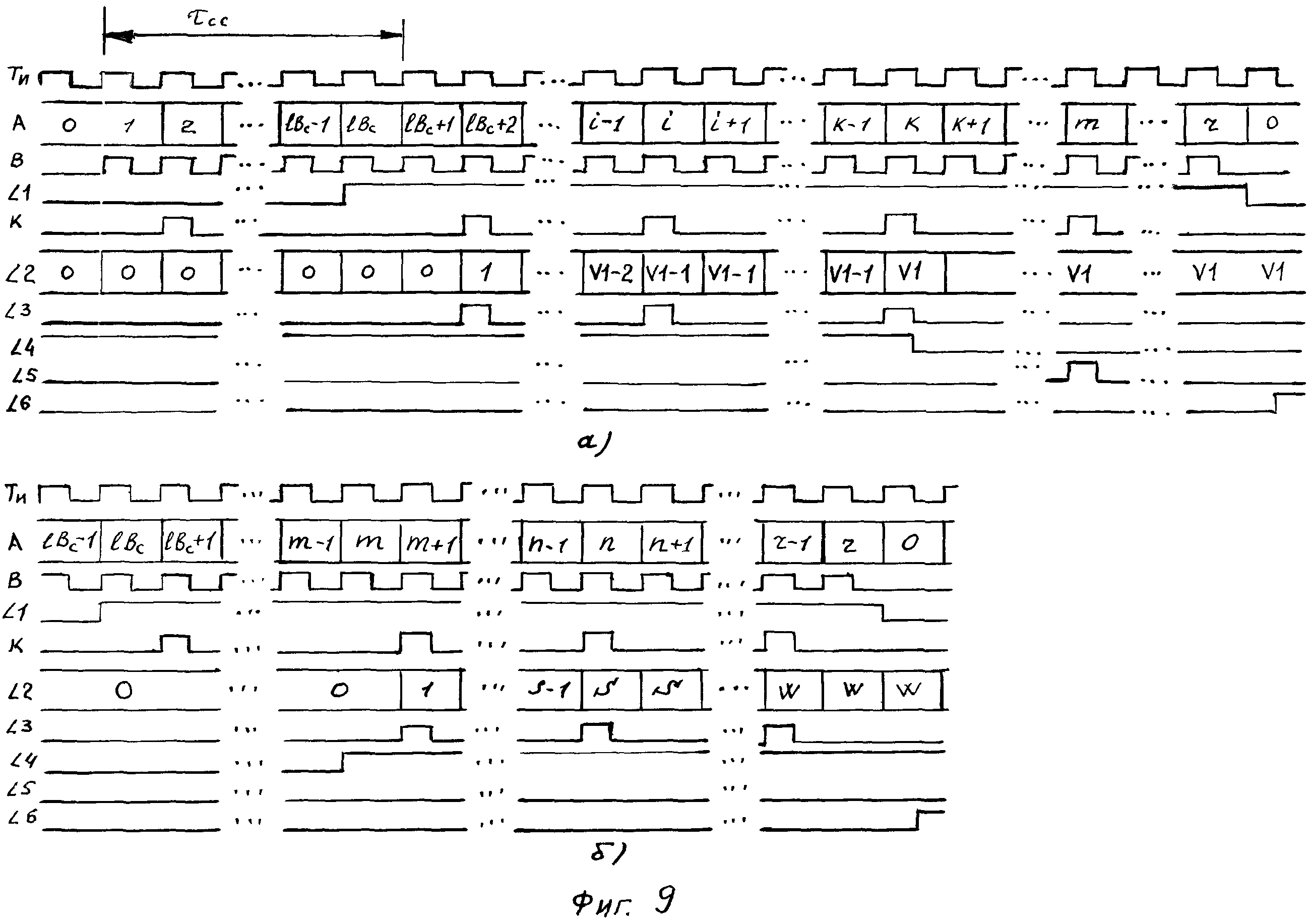

При поступлении сигнала L1 "Строб ДВН" в блоке УРЗ и II устройства управления 10 снимается блокировка с элемента И1. Поэтому при поступлении с ПУ9 сигнала К "Обнаружение в ОО" в УУ10 на вход блока УРЗ и II блок формирует сигналы L 3" + 1 адр ОЗУ 1" и L 3 записи "ЧГ/ЗП ОЗУ 1". Эти сигналы поступают на счетный вход счетчика Ст1 и вход управления режимов чтения/записи ОЗУ1 соответственно блока ФА устройства управления 10. Счетчик Ст1 формирует адрес, по которому в ОЗУ 1 записывается состояние счетчика Ст1 (адрес в первых БЗУ3 последних (р-х) квадратурных отсчетов выходных сигналов СФ1 из серии отсчетов, сумма которых вызвала превышение порога обнаружения в ПУ9 и инициировала команду К "Обнаружение в ОО", т.е. адрес "сигнальной" серии). На временной диаграмме (фиг. 9а) при появлении первого импульса сигнала К "Обнаружение в ОО" никаких изменений в схеме не происходит, так как нет сигнала L1 "Строб ДВН". При появлении второго импульса сигнала К "Обнаружение в ОО" в первую ячейку ОЗУ 1 записывается адрес lBc+2. Начиная с этого адреса в первых БЗУ 3 через lK ячеек (через период НП) в сторону уменьшения адреса располагаются Р квадратурных отсчетов выходных сигналов СФ1, некогерентное суммирование которых вызвало появление второго импульса сигнала К "Обнаружение в ОО".

В ОЗУ 1 записывается V1 таких адресов ("Сигнальных" ЭВН), где V1 равно числу спектральных преобразований, выполняемых процессором ПКБПФ 6 за один период СС с учетом времени на перезапись "сигнальных" серий отсчетов. При записи V1-го адреса на выходе схемы сравнения 2 блока УРЗ и II устройство управления формируется сигнал, разрешающий прохождение сигнала К "Обнаружение в ОО" па вход с Д-триггера Т10. По его заднему фронту триггер Т10 устанавливается в "1", чем разрешается прохождение сигнала L1 "Обнаружение в ОО" через элемент И13 (L5) и запрещается его прохождение через элемент И5 (L4). Поэтому при поступлении следующего V1+2 импульса сигнала К "Обнаружение в ОО" в регистр Рг17 запишется адрес первых БЗУ 3 (на диаграмме m), с которого будет продолжена запись адресов "сигнальных" серий отсчетов в ОЗУ 1 при обработке следующего (второго) СС ("Строба ДВН"), а триггер Т16 устанавливается в "1", блокируй прохождение сигнала К "Обнаружение в ОО" через элемент И1.

В таком состоянии устройство находится до момента окончания действия сигналов "Строб СС" и "Строб ДВН" (эти сигналы снимаются одновременно). После снятия сигнала "Строб СС" прекращается запись информации в первые БЗУ 3 и они устанавливаются в режим чтения сигналом В "ЧТ/ЗП БЗУ 3" в блоке ФА устройства управления 10. Мультиплексор МХ2 включается на передачу канала В (выхода сумматора SM на выход А устройства управления 10), счетчик Ст5 устанавливается в ноль. По заднему фронту сигнала L1 "Строб ДВН" в блоке УР3 и II устройства управления 10 Д-триггер Т15 устанавливается в "1" и в следующем такте на выходе Д-триггера Т19 формируется сигнал L6 "Перезапись". На этом первый цикл "Запись" заканчивается. Отметим, что циклы "Запись" и "Перезапись" могут быть закончены и начаты соответственно раньше, чем заканчивается действие сигнала L1 "Строб ДВН" сразу де после появления сигнала L5 на выходе элемента И13 блока УРЗ и II устройства управления 10. Для этого схема устройства управления 10 должна быть несколько изменена.

Так как в некогерентном накопителе 8 осуществляется некогерентное накопление отсчетов огибающих выходных сигналов СФ1, то в некогерентном обнаружителе решение о наличии сигнала может быть принято при задержках СС кратных периоду НП. Т.е. по сигналу К "Обнаружение в ОО" может быть получена периодическая синхронизация. Для осуществления апериодической синхронизации в устройстве производится многоканальная по частоте когерентная обработка МП в "сигнальных" сериях отсчетов.

Многоканальная по частоте когерентная обработка МП в "Сигнальных" сериях отсчетов выполняется за два цикла: цикл "Перезаписи" и цикл "Обработки".

В первом цикле "Перезаписи" производится перезапись "сигнальных" серий квадратурных отсчетов входных сигналов СФ1 из первых БЗУ 3 во вторые БЗУ 5 и их адресов из ОЗУ 1 и ОЗУ 2 блока ФА устройства управления 10. Причем при перезаписи "сигнальных" серий отсчетов производится умножение отсчета на соответствующий элемент МП: р-е отсчеты умножаются на р-й элементы Xp-1 МП, (р-1)-е отсчеты умножаются на (р-1)-й элемент Xp-2 МП, …, 1-е отсчеты умножаются на 1-й элемент Хо МП. При таком перемножении "сигнальных" серий отсчетов на элементы МП правильно будет демодулирована МП в той "сигнальной" серии отсчетов, в которой принятая МП совпадает с опорной, записанной в регистре сдвига 4. В этой "сигнальной" серии отсчетов (назовем эту "сигнальную" серию "синхронной") после правильной демодуляции МП отсчеты будут модулированы только доплеровским сдвигом частоты. В остальных "сигнальных" сериях отсчетов МП будет демодулирована неправильно.

В первом цикле "Обработки" "сигнальные" серии квадратурных отсчетов выходных сигналов СФ1, умноженные на МП последовательно считываются из вторых БЗУ 5 в процессор ПКБПФ 6. В процессоре ПК БПФ6 выполняется Р(2Р)-точечное спектральное преобразование (Р(2Р)-канальная по частоте согласованная фильтрация СС). При обработке "синхронной сигнальной" серии отсчетов в зависимости от величины доплеровского сдвига частоты сигнал появится в одном из частотных каналов. При обработке остальных "сигнальных" серий отсчетов с неправильно демодулированными МП, на выходе частотных каналов появятся сигналы, величина которых будет определяться боковыми лепестками функции неопределенности СС. Сигналы всех Р (2Р) частотных каналов (модули спектральных составляющих) поступают в блок МКО7, в котором принимается решение о наличии сигнала в обрабатываемой "сигнальной" серии отсчетов (ЭВН), если в каком-либо частотном канале сигнал превышает порог обнаружения. При этом на выходе блока формируется сигнал G "Обнаружение в многоканальном обнаружителе (МО)". Адреса этих серий (р-х квадратурных отсчетов) в первых БЗУ 3 переписываются из ОЗУ 2 в ОЗУ 3 блока ФА устройства управления 10 по сигналу G "Обнаружение в МО" блока МКО 7. После обработки в процессоре ПКБПФ 6 всех V1 записанных во вторые БЗУ 5 "сигнальных" серий отсчетов и анализа результатов спектрального преобразования в блоке МКО 7 первый цикл "Обработки" заканчивается. При этом в ОЗУ 3 блока ФА устройства управления 10 запишется К1 адресов "Сигнальных" серий отсчетов (K1<V1), которые будут анализироваться на этапе проверки и измерения параметров СС.

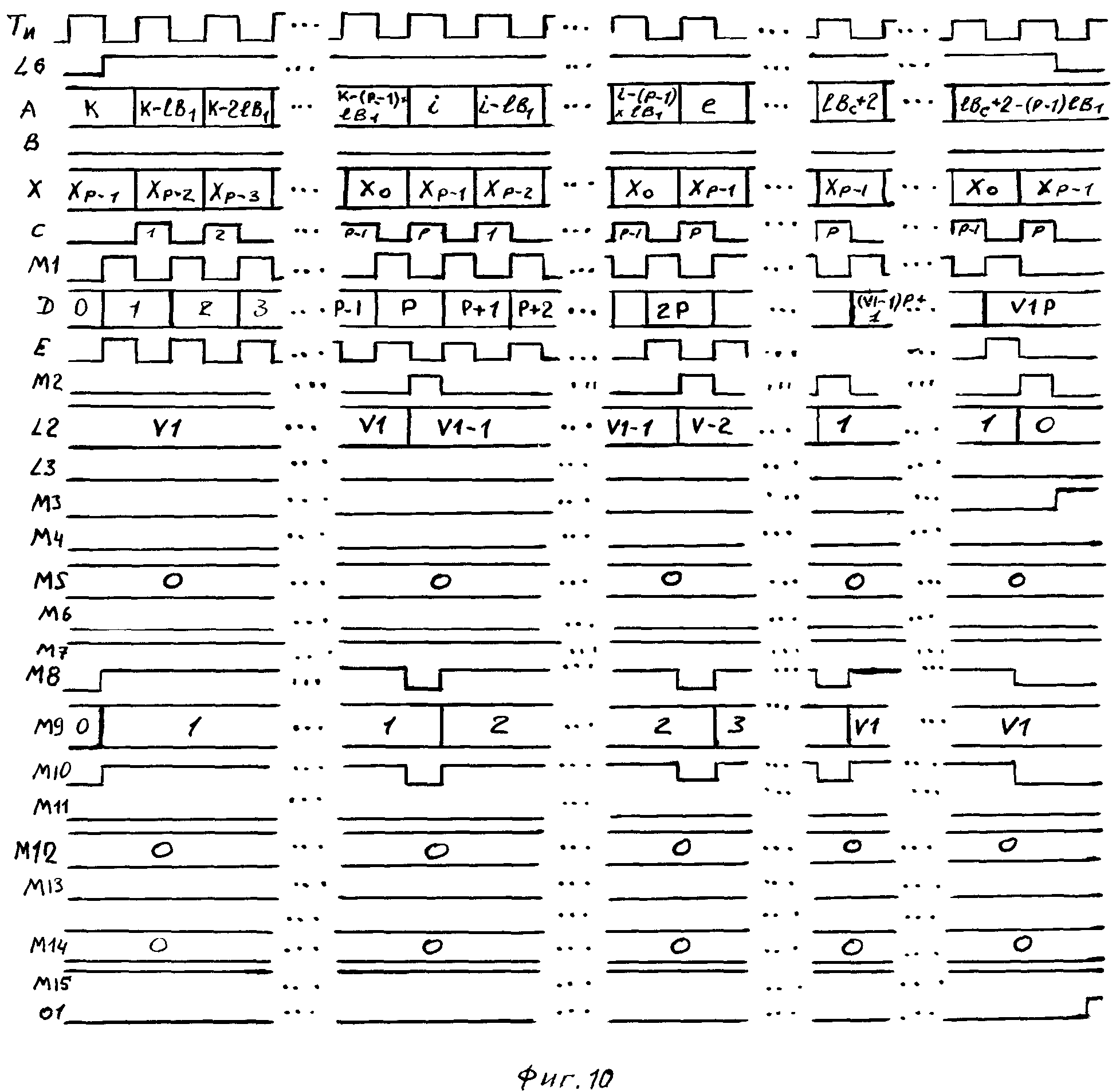

Временная диаграмма работы устройства в первом цикле "Перезаписи" показана на фиг. 10. Цикл "Перезаписи" начинается при появлении сигнала L6 "Перезапись" на выходе триггера Т19 блока УРЗ и II устройства управления 10. Этим сигналом снимается блокировка с элементов И21-И23 в блоке УРЗ и II устройства управления 10, а также разрешается работа счетчика Ст6 в блоке ФА устройства управления 10. Счетчик Ст6 ведет счет по модулю числа P и соединен с ПЗУ. В первые P ячеек ПЗУ записана последовательность величин 0, lВ1, 2lB1, …, (P-1)lB1, где В1 - база сложного элемента СС (число элементов НП, В1=К). С помощью сумматора и ПЗУ блока ФА устройства управления 10 по адресу р-го отсчета серии в первых БЗУ 3 в каждом такте определяются адреса остальных отсчетов путем вычитания из адреса p-го отсчета считываемого из ОЗУ 1 через мультиплексор МХ1, величин, записанных в ПЗУ. Так как в первом цикле "Записи" в ОЗУ1 последним был записан адрес V1-й "сигнальной" серии отсчетов К, то в начале цикла "Перезаписи" из ОЗУ 1 в течение Р тактов будет считываться число К. В первом такте с первых БЗУ 3 будет считываться р-е квадратурные отсчеты, имеющие адрес К, во втором такте - (р-1) отсчеты, имеющие адрес K-lB1, в третьем такте - (р-2) отсчеты, имеющие адрес К-2lВ1, …, в р-м такте - 1-е отсчеты, имеющие адрес К-(р-1)lB1. В умножителях р-е отсчеты умножаются на р-й элемент Xp-1 МП, (р-1)-е отсчеты умножаются на (р-1)-й элемент Xp-2 МП, …, 1-е отсчеты умножаются на 1-й элемент Хо МП. Запись результатов умножения во вторые БЗУ 5 обеспечивается тем, что в каждом такте на выходе элемента И21 УРЗ и II устройства управления 10 формируется сигнал M1′′+1 адр. БЗУ 5", который поступает на счетный вход счетчика Ст7 блока ФА устройства управления 10, чем обеспечивается последовательное изменение в каждом такте адреса Д вторых БЗУ5, и вход управления Е режимами чтения/записи вторых БЗУ5. Циклический сдвиг МП в регистре сдвига 4 обеспечивается формированием в каждом такте на выходе элемента И22 блока УРЗ и II устройства управления 10 сигнала С "Сдвиг МП". В блоке ФА устройства управления 10 адрес V1-й "сигнальной" серии отсчетов К, считываемый из ОЗУ1, одновременно поступает на информационный вход ОЗУ2 и записывается в него под управлением сигналов М8 "+1 адр. ОЗУ2" и М10 "ЧТ/ЗП ОЗУ2", вырабатываемых элементом И24 блока УР3 и II устройства управления 10.

Через Р тактов после записи во вторые БЗУ5 произведения 1-х квадратурных отсчетов V1-й "сигнальной" серии на 1-й элемент Хо МП на выходе переноса счетчика Ст6 блока ФА устройства управления 10 формируется сигнал М18 "-1 адр.", который поступает в блок УРЗ и II и обеспечивает появление на выходе элемента И25 сигнала М2 "-1 адр. ОЗУ 1". Этот сигнал поступает на счетный вход счетчика Ст1 блока ФА устройства управления 10, что обеспечивает считывание из ОЗУ1 адреса p-го отсчета следующей V1-1 "сигнальной" серии (адрес равен i). Далее описанный выше процесс повторяется. После перезаписи первой "сигнальной" серии отсчетов сигналом М2 "-1 адр. ОЗУ 1" счетчик Ст1 блока ФА устанавливается в "нулевое" состояние, что приводит к срабатыванию схемы сравнения 3, элемента И14 и сбросу триггера Т15 в блоке УРЗ и II устройства управления 10. Поэтому по заднему фронту тактового импульса в триггере Т19 происходит сброс сигнала L 6 "Перезапись". На этом первый цикл "Перезаписи" заканчивается.

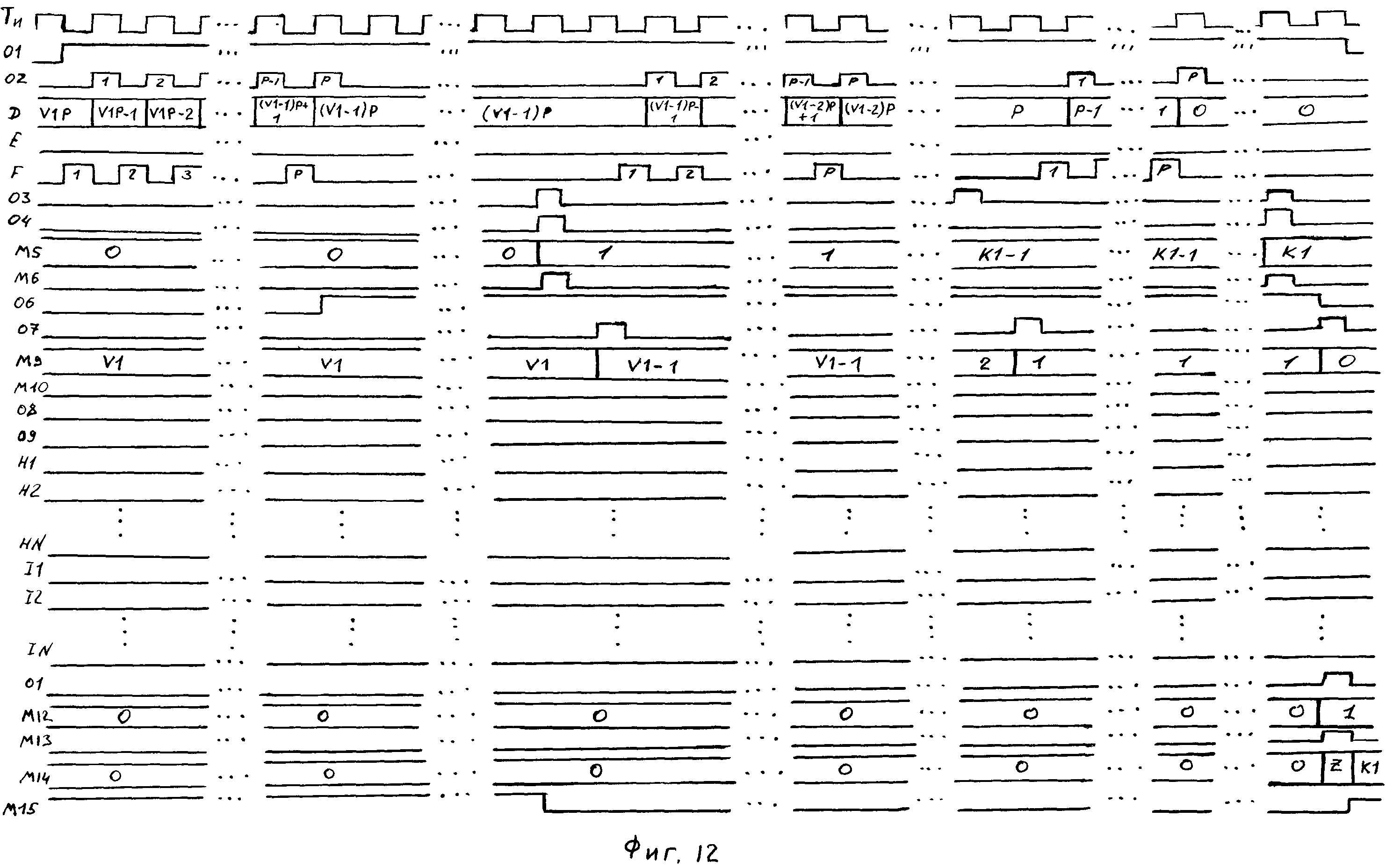

Временная диаграмма первого цикла "Обработки" показана на фиг. 12. По заднему фронту сигнала L6 "Перезапись" в блоке УРО устройства управления 10 триггер Т2 устанавливается в единицу. Затем по заднему фронту тактового импульса триггер T10 устанавливается в "единицу". После переключения триггера Т10 начинает работать счетчик Ст18, снижается блокировка с элементов И7, И14, И23, И30. Счетчик Ст18 ведет счет тактовых импульсов по модулю числа Р. На выходе элемента ИЗО формируется сигнал F "Управление вводом информации в процессор ПКБПФ 6", который обеспечивает последовательный ввод отсчетов первой "сигнальной" серии, считываемых из вторых БЗУ 5, в процессор ПКБПФ 6. Отсчеты считываются, начиная с первого адреса, адреса первой "сигнальной" серии во вторых ВЗУ 5 равны от V1P до (V1-1)Р. На выходе элемента И29 формируется сигнал 02 "-1 адр. БЗУ 2", который поступает на счетный вход Ст7 блока ФА устройства управления 10 и обеспечивает последовательное уменьшение в каждом такте адреса Д вторых БЗУ5. На выходе элемента И14 формируется сигнал, указывающий на начало обработки "сигнальных" серий, адреса которых записаны в ОЗУ2 (выделенных на этапе периодической синхронизации одноканальным обнаружителем с НН МП). После ввода в процессор ПКБПФ 6 p-го отсчета первой "сигнальной" серии (после p тактовых импульсов) в процессоре начинается спектральное преобразование введенных временных отсчетов, а в блоке УРО устройства управления 10 на выходе переноса счетчика Ст18 формируется сигнал, по переднему фронту которого на выходе триггера Т19 формируется сигнал 06 "Обработка" ЭВН из ОЗУ 2, а по заднему фронту триггер Тг5 устанавливается в "единицу", что блокирует прохождение тактовых импульсов через элемент И9 на счетный вход счетчика Ст18, управляющих сигналов через элементы И29, И30, а также разрешает работу счетчика Ст33. Объем счетчика Ст33 выбран таким образом, чтобы обеспечить выполнение спектрального преобразования в процессоре ПКБПФ 6 и принятия решения в блоке МКО7 до появления импульса переноса на его выходе. После выполнения спектрального преобразования и анализа результатов обработки в блоке МКО 7 на выходе переноса счетчика Ст33 формируется сигнал О3 "Конец преобразование". Этот сигнал разрешает прохождение сигнала G "Обнаружение в МО" с блока МКО 7 через элемент И23 и запускает формирователь одиночного импульса на триггерах Т37, Т44 и элементе И40. При поступлении с блока МКО 7 сигнала G "Обнаружение в МО" в блоке УРО на выходе триггера Т5 формируется сигнал О11 "Начало проверки и измерения" (активный уровень "нулевой"), а на выходе блика формируются сигналы М6 "ЗП. ОЗУ 3" и 04 "+1 адр. ОЗУ3 ".

Сигналы М6 "ЗП. ОЗУ 3" и 04 "+1 адр. ОЗУ 3" поступают в блок ФА устройства управления 10 на вход управления режимом чтения/записи ОЗУ 3, а также счетный вход счетчика Ст3 соответственно, и обеспечивают перезапись адреса (номера ЗВН) обработанной "сигнальной" серии из V1-й ячейки ОЗУ 2 в 1-ю ячейку ОЗУ 3. Сигнал О11 "Начало проверки и измерения" разрешает работу счетчика Ст17, ведущего подсчет числа накопленных в блоке МПО 7 импульсов СС по модулю числа q, где q - требуемое число накапливаемых импульсов СС, а также поступает в блок УРЗ и II устройства управления 10 на вход элемента И 12 и обеспечивает прохождение сигнала М14 "Ki=Адр. ОЗУ 3" со схемы сравнения 4 блока УРО устройства управления 10.

В блоке УРО устройства управления 10 формирователь одиночного импульса на триггерах Т37, Т44 и элементе И40 обеспечивает формирование сигнала О7 "-1 адр. ОЗУ 2" и сброс триггера Т25 в "ноль". Сигнал О7 "-1 адр. ОЗУ 2" поступает в блок ФА устройства управления 10 на счетный вход счетчика Ст2 и обеспечивает чтению адреса второй "сигнальной" серии отсчетов с (V1-1)-й ячейки ОЗУ 2. Далее, как было описано ранее, начинается последовательный ввод квадратурных отсчетов второй "сигнальной" серии из вторых БЗУ 5 в процессор ПКБПФ 6 и их обработка.

Описанный выше процесс продолжается до тех пор, пока не будет обработана последняя V1 "сигнальная" серия отсчетов, адрес которой считывается с первой ячейки ОЗУ 2. При принятии решения о наличии сигнала в блоке МКО 7 и появлении на выходе переноса счетчика Ст33 сигнала О3 "Конец преобразования" на выходе блока УРО устройства управления 10 формируются сигналы О4 "+1 адр. ОЗУ 4" и М6 "ЗП. ОЗУ 3", что обеспечивает записи в К 1-ю ячейку ОЗУ 3 адреса обработанной "сигнальной" серии (адрес V1-й "сигнальной" серии). В следующем такте по сигналу О7 "-1 адр. ОЗУ 2" в блоке ФА устройства управления 10 счетчик Ст2 устанавливается в "ноль". Это приводит к срабатыванию в блоке УРО схемы сравнения 1 и появлению на выходе элемента И8 сигнала М13 "ЗП.ОЗУ 4". По этому сигналу в блоке УРО устройства управления 10 сбрасывается в ноль триггера Т2, Т19, в регистр Рг3 записывается конечный адрес ОЗУ 3 К1 (число ЭВН, серий отсчетов, выделенных при многоканальной когерентной обработке МП для последующей проверки), счетчик Ст17 переходит в "единичное" состояние, а в блоке ФА устройства управления 10 в ОЗУ 4 записывается конечный адрес ОЗУ 3 К1. В блоке УРО после сброса триггера Т2 по заднему фронту тактового импульса на выходе Т10 сбрасывается команда 01 "Обработка". На этом первый цикл "Обработки" и первый полный цикл работы устройства заканчиваются.

Второй полный цикл работы устройства начинается со второго цикла "Записи", когда на вход блока ФА устройства управления 10 поступает второй импульс сигнала L 8 "Строб СС". В отличие от первого цикла "Записи" во втором цикле "Записи" запоминание адресов "сигнальных" серий отсчетов в ОЗУ 1 блока ФА устройства управления 10 (см. временную диаграмму на фиг. 9б) начинается с адреса, записанного в первом цикле в регистр Рг17 блока УРЗ и II устройства управления 10 (на диаграмме равен m).

Это обеспечивается тем, что, когда состояние шины А "Адр. БЗУ 3" станет равно числу, записанному в предыдущем цикле в Рг17, (числу m) в блоке УРЗ и II устройства управления 10 сработает схема сравнения 18. Срабатывание схемы сравнения 18 приведет к сбросу триггеров Т10 и Т16, а также регистра Рг17. Это приведет к началу записи адресов "сигнальных" серий отсчетов в ОЗУ 1.

В отличие от первого цикла "Записи" во втором цикле "Записи" в ОЗУ 1 записывается не более V1-К1 адресов "сигнальных" серий отсчетов. Это делается для того, чтобы процессор ПКБПФ 6 успел обработать "сигнальные" серии, записанные в этом цикле в ОЗУ 1 и хранимые в ОЗУ 3 (ЭВН подлежащие анализу на этапе проверки и измерения). Число записанных в ОЗУ 1 "сигнальных" серий отсчетов контролируется схемой сравнения 2 блока УРЗ и II устройства управления 10, на вход B которой поступает код, равный разнице между V1 и числом адресов "сигнальных" серий отсчетов (числом ЭВН), записанных в ОЗУ 3. Код разности формируется в блоке УРО устройства управления 10 с помощью сумматоров SM22 и SM27. В сумматоре SM22 число записанных в ОЗУ 3 "сигнальных" серий отсчетов (число ЭВН), выделенных для анализа на этапе проверки и измерения, определяется путем вычитания из конечного адреса массива "сигнальных" серий начального адреса массива, если конечный адрес больше начального и наоборот, если начальный адрес больше конечного. Начальный адрес может быть больше конечного, так как в ОЗУ 3 запись адресов "сигнальных" серий отсчетов осуществляется по "кругу", т.е. после заполнения последней ячейки ОЗУ 3 запись продолжается, начиная с нулевой. В этом случае конечный адрес становится меньше начального адреса массива "сигнальных" серий отсчетов. Для управления видом операции в сумматоре SM22 (А-В или В-А) используется триггер Т13. Если формируется импульс переноса "РСт3" со счетчика Ст3 блока ФА устройства управления 10, то триггер Т13 блока УРО устанавливается в "единицу" и в сумматоре SM22 выполняется операция вычитания из начального адреса, записанного в Рг4; блока УРЗ и II, конечного адреса, записанного в Рг3 блока УРО (В-А). Если переноса нет, то триггер Т13 остается в "нулевом" состоянии (устанавливается в "ноль" по заднему фронту сигнала "Перезапись") и в сумматоре SM22 выполняется операция вычитания из конечного адреса начального (А-В).

В сумматоре SM27 из V1 вычитается число записанных в ОЗУ3 "Сигнальных" серий отсчетов.

Число ЭВН, которое может быть записано в ОЗУ1 в следующем цикле "Записи", с выхода сумматора SM27 блока УРО устройства управления 10 (О12 "Число ЭВН ОЗУ 1") поступают на вход В схемы сравнения блока УРЗ и II устройства управления 10.

Если количество "сигнальных" серий отсчетов в этом цикле будет больше, чем V1-K1, то второй цикл "Записи" заканчивается так же, как и первый. При этом в регистре Рг17 блока УРЗ и II устройства управления 10 будет зафиксирован новый адрес первых БЗУ, с которого будет продолжена записи адресов "Сигнальных" серий обсчетов в ОЗУ 1 при обработке следующего (третьего) СС ("Строба ДВН").

Если количество "сигнальных" серий отсчетов в этом цикле будет меньше или равно V1-K1 (W≤V1-K1), то ДВН будет проанализирован до конца без запоминания в регистр Рг17 блока УРЗ и II устройства управления 10 адреса продолжения записи адресов "сигнальных" серий отсчетов в ОЗУ 1 (так как не срабатывает схема сравнения 2 блока УРЗ и II). Регистр Рг17 останется в "нулевом" состоянии, поэтому в следующем цикле "Записи" запись адресов "сигнальных" серий отсчетов начинается с первого ЭВН (с начала ДВН).

Второй цикл "Записи", как и первый, заканчивается формированием сигнала "Перезапись" на выходе блока УРЗ и II устройства управления 10. Во втором полном цикле работы устройства многоканальная по частоте когерентная обработка МП производится над "сигнальными" сериями отсчетов, которые были обнаружены во втором цикле "Записи" (их адреса записаны в ОЗУ 1 блока ФА устройства управления 10) и теми, которые были выделены в первом цикле "Обработки" для проведения проверки и измерения параметров СС из "сигнальных" серий, обнаруженных в первом цикле "Записи" (их адреса хранятся в ОЗУ 3 блока ФА устройства управления 10). Как и в первом полном цикле многоканальная по частоте когерентная обработка МП выполняется за два цикла: цикл "Перезаписи" и цикл "Обработки".

Во втором цикле "Перезаписи" производится перезапись "сигнальных" серии квадратурных отсчетов выходных сигналов СФ1 из первых БЗУ 3 во вторые БЗУ 5. Причем вначале перезаписываются "сигнальные" серии, адреса которых хранятся в ОЗУ 1 блока ФА устройства управления 10, а затем "сигнальные" серии, адреса которых хранятся в ОЗУ 3 блока ФА устройства управления 10. Одновременно с перезаписью первых "сигнальных" серий в блоке ФА устройства управления 10 производиться перезапись их адресов из ОЗУ 1 в ОЗУ 2. При перезаписи "сигнальных" серий отсчетов, как и в предыдущем цикле, производится умножение каждого отсчета на соответствующий элемент МП. Всего во вторые БЗУ 5 будет записано, как и в предыдущем случае, V1 "сигнальных" серий отсчетов.

Во втором цикле "Обработки" сигнальные серии квадратурных отсчетов выходных сигналов СФ1, умноженные на МП и записанные во вторые БЗУ5, обрабатываются в процессоре ПК БПФ6 в два этапа. Вначале обрабатываются "сигнальные" серии отсчетов выделенные для проведения проверки и измерения параметров СО. Результаты обработки этих "сигнальных" серий отсчетов накапливаются в блоке МПО 11 для каждой серии (для каждого ЭВН) и в каждом частотном канале. Затем обрабатываются "сигнальные" серии отсчетов, которые были выделены в предыдущем (втором) цикле "Записи". Результаты обработки каждой сигнальной серии анализируются в блоке МКО 7. Если в блоке МКО 7 принимается решение о наличии сигнала в обработанном ЭВН, то номер этого ЭВН (адрес обработанной "сигнальной" серии отсчетов в первых БЗУ 3) переписывается из ОЗУ 2 в ОЗУ 3 блока ФА устройства управления 10 по сигналу G "Обнаружение в МО".

После выполнения второго цикла "Обработки" в блоке МПО 11 начнется накопление во всех частотных каналах и в каждом из K1 ЭВН результатов спектрального преобразования, в ОЗУ 3 блока ФА устройства управления 10 запишется еще К2-К1 адресов "сигнальных" серий отсчетов, которые будут анализироваться на этапе проверки и измерения параметров СС.

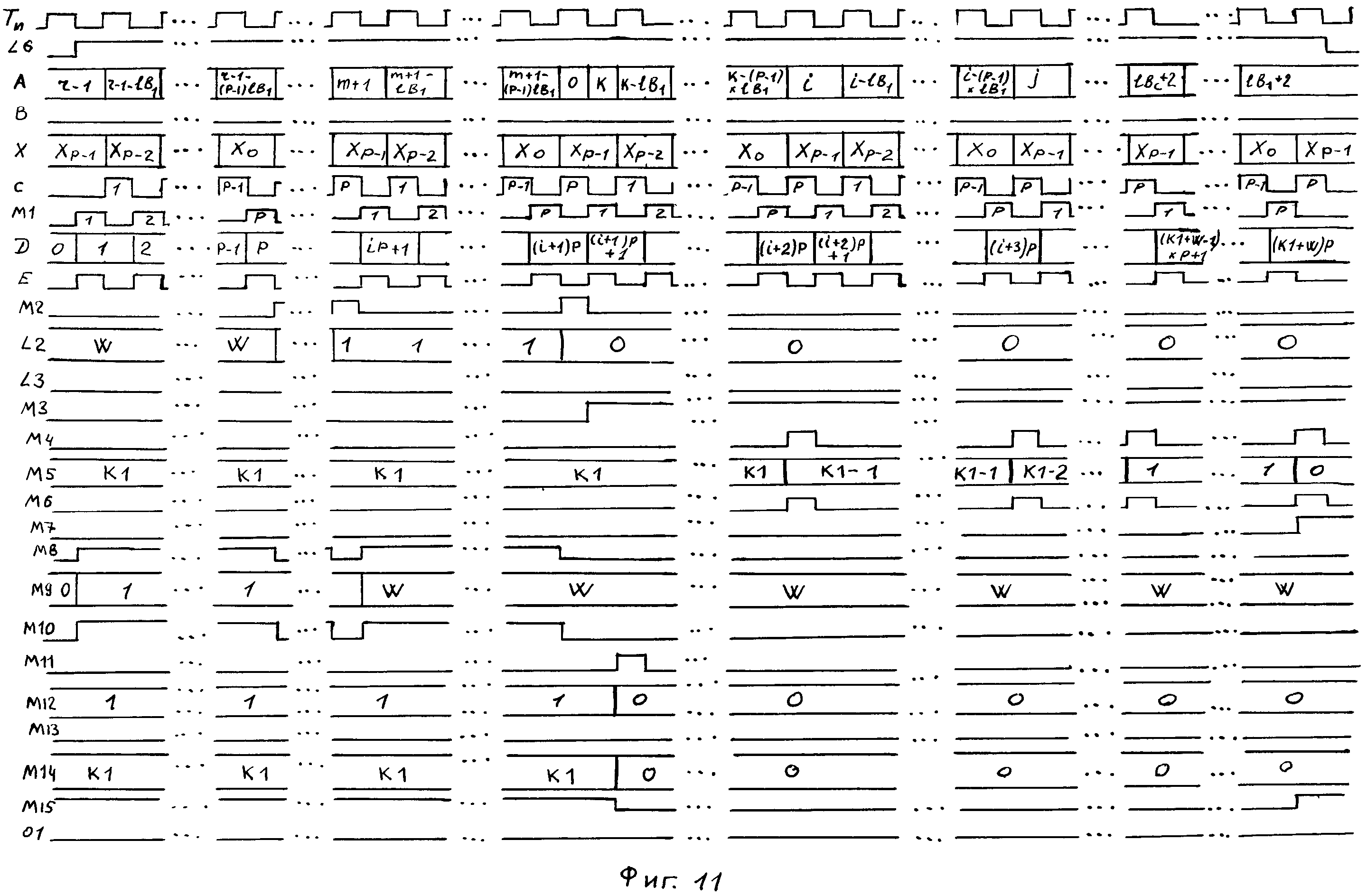

Временная диаграмма работы устройства во втором цикле "Перезаписи" показана на фиг. 11. Второй цикл "Перезаписи", как и первый, начинается при появлении сигнала L6 "Перезапись" на выходе триггера Т19 блока УРЗ и II устройства управления 10 и протекает аналогично до момента установки счетчика Ст1 блока ФА устройства управления 10 в "нулевое" состояние. Во втором цикле "Перезаписи" в блоке УРЗ и II устройства управления 10 установка счетчика Ст1 в "нулевое" состояние не приводит к сбросу триггера Т19, так как на выходе схемы сравнения 9 нет сигнала М7 "Конец перезаписи из ОЗУ 3". Этот сигнал не формируется схемой сравнения 9, так как в первом цикле "Обработки" в ОЗУ 3 блока ФА устройства управления 10 блока записано K1 адресов "сигнальных" серий отсчетов для проведения проверки и измерения параметров СС и поэтому на вход В схемы сравнения 9 поступает код числа К1, а на второй вход А поступает "ноль" с регистра Рг4.

Во втором цикле "Перезаписи" в блоке УРЗ и II устройства управления 10 установка счетчика Ст1 в "ноль" приводит к последовательному срабатыванию схемы сравнения 3 и триггера Т8. Срабатывание триггера Т8 приводит к появлению сигнала М3 "Конец перезаписи из ОЗУ 1", который блокирует прохождение сигналов управления чтением/записью ОЗУ 1 и ОЗУ 2 блока ФА устройства управления 10 через элементы И24, И25, разрешает прохождение сигналов управления ОЗУ 3 и ОЗУ 4 блока ФА через элементы И26, И27 и мультиплексором МХ1 в блоке ФА устройства управления 10 подключает выход ОЗУ 3 вместо выхода ОЗУ 1 к входу А сумматора SM. Это приводит к тому, что прекращается перезапись адресов "сигнальных" серий из ОЗУ 1 в ОЗУ 2, адреса "сигнальных" серий отсчетов, перезаписываемых из первых БЗУ 3 во вторые БЗУ 5, считываются из ОЗУ 3. Первым за командой М3 "Конец перезаписи из ОЗУ 1" тактовым импульсом на выходе триггера Тг8 блока УРЗ и II устройства, управления 10 формируется сигнал M11 "-1 адр. ОЗУ 4", поступающий на счетчик Ст4 блока ФА и устанавливающий его в "ноль". Это обеспечивает чтение "нулевой" ячейки ОЗУ 4 блока ФА устройства управления 10. В остальном цикл "Перезаписи" протекает аналогично первому циклу. В блоке УРЗ и II устройства управления 10 на выходе элементов И22, И21 и И26 формируются сигналы С "Сдвиг МП" на вход управления сдвигом МП в регистр Рг4, M1 "+1 адр. БЗУ 5" и М4 "-1 адр. ОЗУ 3", поступающие в блок ФА устройства управления 10 на счетчики Ст7, Ст3 и обеспечивающие перезапись с умножением на элементы МП "сигнальных" серий отсчетов, выделенных в первом цикле «Обработки" для проведения проверки и измерения параметров СС, из первых БЗУ 3 во вторые БЗУ 5.

После перезаписи с умножением на элементы МП последней "сигнальной" серии отсчетов (lBc+2) во вторые БЗУ 5 по адресу (К1+W-1)р+1 в блоке ФА устройства управления 10 счетчик Ст3 устанавливается в ноль. Поэтому в блоке УРЗ и II срабатывает схема сравнения 9 и на ее выходе формируется сигнал М7 "Конец перезаписи из ОЗУ 3". Появление сигнала М7 "Конец перезаписи из ОЗУ 3" приводит к последовательному срабатыванию триггеров Т15 и Т19. При срабатывании триггера Т19 снижается команда L6 "Перезапись". На этом второй цикл "Перезаписи" заканчивается.

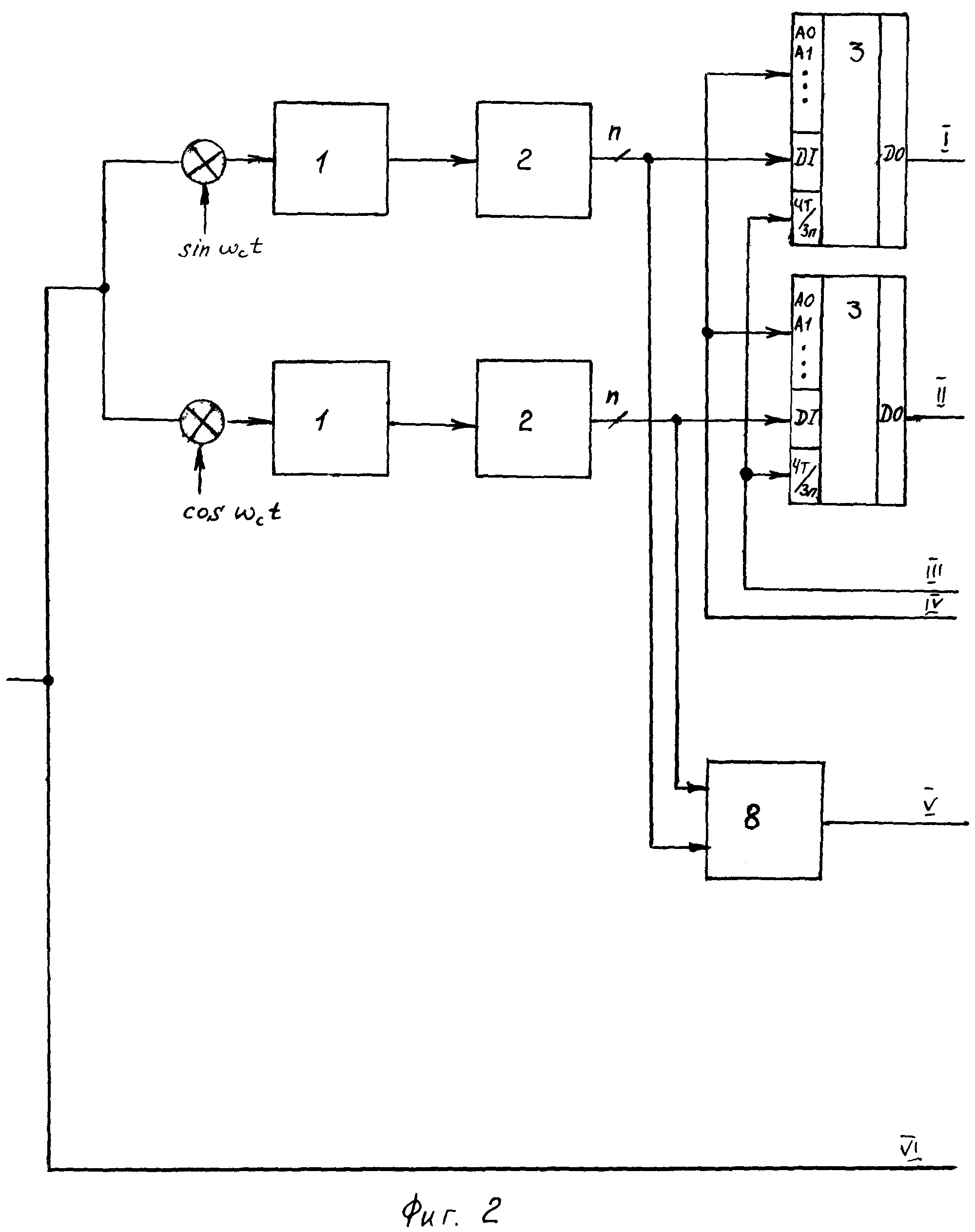

Временная диаграмма работы устройства во втором цикле "Обработки" показана на фиг. 13. В отличие от первого цикла "Обработки" во втором цикле в блоке УРО устройства управления 10 на выходе триггера Т19 не формируется сигнал O6 "Обработка ЭВН из ОЗУ 2" после ввода в процессор ПК БПФ6 р-го отсчета первой "сигнальной" серии (через р тактовых импульсов после начала действия сигнала О1 "Обработка"). Так как в блоки УРО устройства управления 10 на вход А схемы сравнения 11 поступает код числа К1 с регистра Рг3, который был записан в него в конце первого цикла "Обработки", а на вход В схемы сравнения 11 поступает "ноль".

Отсутствие сигнала О6 "Обработка ЭВН из ОЗУ 2" приводит к тому, что на выходе блока УРО устройства управления 10 при появлении импульса переноса на выходах счетчиков СТ18 и Ст33 формируются сигналы 04 "+1 адр. ОЗУ 3" и Hi "Накопление в i-м блоке накопления (БН)" соответственно, а при срабатывании схемы сравнения 4 и появлении импульса переноса на выходе счетчика Ст18 формируется сигнал О10 "+1 адр. ОЗУ 4". Сигнал 04 "+1 адр. ОЗУ 3" поступает в блок ФА устройства управления 10 на вход счетчика Ст3 и обеспечивает последовательное считывание с ячеек ОЗУ 3 адресов "сигнальных" серий отсчетов (номеров ЭВН), обрабатываемых и анализируемых в блоке МПО 11, на вход регистра. Сигнал Hi (i=1, 2…K1) "Накопление в i-м БН" поступает в блок МПО 11 на вход управления записью накапливающего регистра Рг1-РгР (2P) и обеспечивает накопление результатов спектрального преобразования А1-АР(А2Р) во всех частотных каналах и в каждом из К1 ЭВН. Сигнал О10 "+1 адр. ОЗУ 4" поступает в блок ФА устройства управления 10 на вход счетчика Ст4 и обеспечивает последовательное считывание с ячеек ОЗУ4 конечных адресов ОЗУ 3 (во втором цикле "Обработки" адрес К1).

После ввода в процессор ПКПБФ 6 (К+1) "сигнальной" серии отсчетов в блоке УРО устройства управления 10 по переднему фронту импульса переноса счетчика Ст18 на выходе триггера Т19 формируется сигнал О6 "Обработка ЭВН из ОЗУ 2", так как на выходе схемы сравнения 11 формируется сигнал совпадения кода, записанного в регистр Рг3, и кода на шине "Адр. ОЗУ 3" (код числа К1). После появления сигнала О6 "Обработка ЭВН из ОЗУ 2" устройство начинает работать так же, как и в первом цикле "Обработки". При этом в блоке ФА устройства управления 10 в ОЗУ 3 дополнительно будет записано К2-К1 адресов "сигнальных" серий отсчетов (номеров ЭВН), которые будут анализироваться вместе с К1 серией отсчетов на этапе проверки и измерения параметров СС, а в ОЗУ 4 записывается конечный адрес ОЗУ 3 К2 (число ЭВН "сигнальных" серий отсчетов, выделенных при когерентной обработке МП на первом и втором цикле "Обработки" для проведения проверки и измерения параметров СС).

При поступлении на вход блока ФА устройства управления 10 последующих импульсов сигнала "Строб СС" и "Строб ДВН" описанный выше второй полный цикл работы устройства повторяется до конца q-го цикла "Обработки". В конце q-го цикла "Обработки" в блоке УРО устройства управления 10 при появлении на выходе элемента И8 сигнала М3 "ЗП ОЗУ 4" на выходе переноса счетчика Ст17 появится сигнал переноса, блокирующий его дальнейшую работу. Поэтому на выходе переноса счетчика Ст17 установится потенциал, который снимет блокировку с элемента И21. В начале следующего (q+1)-го и последующих циклов "Обработки" первым импульсом сигнала с выхода элемента ИЗ1 "+1 адр. ОЗУ 4" (О10) триггер Т26 установится в "единицу". Установка триггера Т26 в "единицу" приведет к тому, что на выходе дешифратора ДШ41 и элемента И38 при появлении импульсов на выходе элемента И40 будут формироваться сигналы Ii "Принятие решения в i-м БН" (i=1, 2…К1) и 09 "ЗП номера ЭВН в Рг" соответственно. Сигнал О9 "ЗП номера ЭВН в Рг" (на временной диаграмме фиг. 13 показаны пунктиром) поступает в блок ФА устройства управления 10 на вход управления записью информации (адреса "сигнальной" серии отсчетов в первых БЗУ3, анализируемого в блоке МПО 11) регистра и обеспечивает запись адреса "сигнальной" серии отсчетов, считываемых с ОЗУ3. Сигнал Ii, "Принятие решения в i-м БН" (на временной диаграмме фиг. 13 показаны пунктиром) поступает в блок МПО 11 и разрешает работу схемы выбора максимума i-го БН, которая выбирает частотный канал с максимальным уровнем сигнала и выдает его на пороговое устройство, а также выдает номер "сигнального" частотного канала на выход 2. После принятия решения в i-м БН задержанным сигналом Ii "Принятие решения в i-м БН", накапливающие регистры Рг1-РгР(2Р) блока МПО 11 сбрасываются в "ноль" и могут быть снова использованы для накопления сигнала в следующем ЭВН. Если максимальный сигнал превышает порог обнаружения, то сигнал считывается обнаруженным и устройство прекращает поиск сигнала, например путем блокировки тактовых импульсов. В блоке 12 ССН и ССЗ по номеру частотного канала с максимальным уровнем сигнала определяется частота принимаемого СС, а по содержимому регистра Рг блока ФА устройства управления 10 определяется номер ЭВН, в котором находится сигнал (определяется задержка СС), осуществляется наведение следящих по несущей и задержке, их замыкание и слежение за СС в течение всего сеанса связи.

При обработке К1-й "сигнальной" серии отсчетов при появлении K1-го импульса на выходе элемента И40 на выходе элемента И35 появляется сигнал О8 "Зп. нач. адр. в Рг" (на временной диаграмме фиг. 13 показан пунктиром). Этот сигнал поступает в блок УРЗ и II устройства управления на вход управления записью информации регистра Рг4 и обеспечивает запись в регистр нового начального адреса ОЗУ 3 К1 вместо нулевого. На освободившееся место в следующих циклах обработки записываются новые адреса "сигнальных" серий отсчетов (новые номера ЭВН) для проведения проверки и измерения параметров СС. В каждом последующем цикле "Обработки" зона записи адресов "сигнальных" серий в ОЗУ 3 (соответственно и БН в блоке МПО 11) будет смещаться по "кругу" по мере окончания накопления и принятия решения в "сигнальных" сериях отсчетов, адреса которых записаны в ОЗУ 3. При вводе в процессор ПКБПФ 6 р-го комплексного отсчета (К1)-й "сигнальной" серии в блоке УРО устройства управления 10 на выходе элемента ИЗ1 формируется второй импульс сигнала О10 "+1 адр. ОЗУ 4". Этим сигналом триггер Т26 устанавливается в "ноль", что блокирует формирование сигналов Ii "Принятие решения в i-м БН" и вызывает установку триггера Т32 в "единицу".

Установка триггера Т32 в "единицу" блокирует прохождение последующих импульсов сигнала О10 "+1 адр. ОЗУ 4" через элемент И21.

Дальнейшая работа устройства аналогична работе устройства во втором цикле.

Отметим, что блоки МКО 7 и МПО 11 и некоторые функции устройства управления могут быть реализованы программно на микропроцессоре. При малых диапазонах временной неопределенности и высокой производительности процессора ПКБПФ 6, достаточной для обработки всех ЭВН, может сразу выполняться апериодическая синхронизация. В этом случае из устройства могут быть исключены некогерентный накопитель 8 и ПУ9.

Таким образом, предложенный способ синхронизации позволяет осуществить быструю апериодическую синхронизацию и обеспечивает поддержание синхронизма в течение всего сеанса связи в системах подвижной связи с "прерывистым" режимом передачи информации, а предложенное устройство дает возможность осуществить многоканальный по частоте с когерентным накопителем МП поиск сигнала синхронизации с использованием научно-технических достижений как в области временной (согласованные фильтры на ПЗС, ПАВ и др.), так и спектральной (процессоры БПФ) обработок, что значительно повышает его технические характеристики.

Технико-экономический эффект от использования заключается в обеспечении быстрой апериодической синхронизации приемной, передающей аппаратуры и поддержании синхронизма радиотехнических систем с шумоподобными сигналами при наличии априорной временной и частотной неопределенностей. Это повышает эффективность использования канала связи, сокращает время сеанса связи и повышает скрытность системы.

Источники информации

1. Патент № 4558453, 10.11.1985 г., F. Mimken, Способ синхронизации и система связи с псевдослучайной перестройкой рабочей частоты.

2. E. Olcayto and B Chreitan. Rapid synchronisation of long PN segvences using in Spread spectrum Sistem Dig. Process Signal commun. Int. Conf. 1985, p. 125-131 (вторичный источник: Реферат. Журнал, сер. Физика, 1986, №11, реф. 11Ж77).

3. Микропроцессор К1815ВФЗ для цифровой обработки сигналов /В.А. Бобков и др. Микропроцессорные средства и системы, 1986, № 2, с. 21-23, 85.

4. Л.Рабинер, Б.Гоулд, Теория и применение цифровой обработки сигналов. М.: Мир, 1978.

5. Журавлев В.И. Поиск и синхронизация в широкополосных системах, - М.: Радио и связь, 1986, с.240.

6. Макаров С.Б., Цикин И.А. Передача дискретных сообщений по радиоканалам с ограниченной полосой пропускания. М.: Сов. Радио, 1988, с. 304.

7. Патент № 4485477, от 27.11.1984. I.J. Nossen. Быстрый поиск по частоте/коду.

Устройство синхронизации составных шумоподобных сигналов, содержащее первую ступень корреляционной обработки (КО), в состав которой входят соединенные по входу два квадратурных канала, каждый из которых состоит из последовательно соединенных согласованного фильтра на часть сигнала, манипулированную одним периодом несущей последовательности, другой вход которого является входом опорного квадратурного сигнала, и аналого-цифровой преобразователь, выход которого является выходом первой ступени КО, вторую ступень КО, в состав которой входят два квадратурных канала, каждый из которых состоит из последовательно соединенных умножителя и буферного запоминающего блока, выход которого соединен с соответствующим сигнальным входом процессора прямого комплексного быстрого преобразования Фурье, выход которого является выходом второй ступени КО, и регистр циклического сдвига модулирующей последовательности, выход которого соединен со входами умножителей, выход второй ступени КО соединен с сигнальными входами блока межканальной обработки сигнала и блока межпериодной обработки сигнала, выходы которого соединены с первым и вторым входами блока следящих систем по несущей и задержке, третий вход которого соединен со входом первой ступени КО и является сигнальным входом устройства, а выход - выходом устройства, последовательно соединенные некогерентный накопитель, выполненный в виде рециркулятора со "скользящим" окном на всю длительность сигнала, входы которого соединены с выходами первой ступени КО, пороговый блок, блок управления, первый, второй, третий и четвертый выходы которого соединены соответственно с управляющим входом регистра циклического сдвига, адресными и управляющими входами буферных запоминающих блоков и управляющим входом процессора прямого комплексного быстрого преобразования Фурье второй ступени КО, отличающееся тем, что, с целью сокращения времени поиска и упрощения устройства, в него введены между первой и второй ступенями КО дополнительные буферные запоминающие блоки, первый и второй элементы И, последовательно соединенные первый, второй и третий блоки оперативной памяти и регистр, первый и второй мультиплексоры, счетчик, формирователь адреса серии, первый и второй дешифраторы, при этом первый и второй входы первого элемента И соединены соответственно с выходом блока межканальной обработки сигнала и соответствующим выходом блока управления, другие выходы которого соединены с соответствующими адресными входами первого, второго и третьего блоков оперативной памяти, управляющие входы которых соединены соответственно с соответствующими выходами блока управления и с выходом первого элемента И, четвертый вход блока следящих систем на несущей и задержке соединен с информационным выходом регистра, управляющий вход которого соединен соответствующий выход блока управления, выходы первого и третьего блоков оперативной памяти и соответствующий выход блока управления через первый мультиплексор соединены с первым входом формирователя адреса серии, второй вход которого соединен с соответствующим выходом блока управления, а выход - с первым входом второго мультиплексора, второй вход которого соединен с выходом счетчика, с информационным входом первого блока оперативной памяти и с соответствующим входом блока управления, а выход второго мультиплексора соединен с адресными входами дополнительных буферных запоминающих блоков, выходы первого и второго дешифраторов соединены с соответствующими входами блока межпериодной обработки, информационные входы первого и второго дешифраторов соединены между собой и с управляющим входом третьего блока оперативной памяти, а управляющие входы первого и второго дешифраторов соединены с соответствующим выходом блока управления и с управляющим входом регистра, входы тактовых импульсов аналого-цифровых преобразователей первой ступени КО, соответствующий вход блока управления, счетный вход счетчика, первый вход второго элемента И и тактовый вход формирователя адресов серии соединены между собой и являются входом тактовых импульсов устройства, управляющие входы счетчика и второго мультиплексора и второй вход второго элемента И соединены между собой и являются входом установки диапазона поиска по времени, а первый управляющий вход блока межканальной обработки и третий управляющий вход блока межканальной обработки соединены между собой и являются входом установки диапазона поиска по частоте.