Результат интеллектуальной деятельности: КОМПАРАТОР ТОКОВ С ГИСТЕРЕЗИСОМ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может использоваться в различных цифровых структурах, датчиковых системах, нейронных сетях, устройствах передачи информации и т.п.

В вычислительных и управляющих системах сегодня широко используются потенциальные логические элементы и компараторы, работающие по законам булевой алгебры и имеющие по входу и выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами [1-17].

Известны также компараторы двух входных токовых логических сигналов [18-29], которые имеют в основном потенциальные выходы.

Кроме этого, достаточно перспективны компараторы и цифровые элементы на их основе с входными и выходными токовыми логическими переменными, на базе которых могут быть реализованы различные спецвычислители и СФ-блоки ЭВМ (так называемые ускорители), работающие на принципах линейной (не булевой) алгебры [30-36].

В монографии [37], а также работах [38, 39] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство относится к этому типу цифровых устройств.

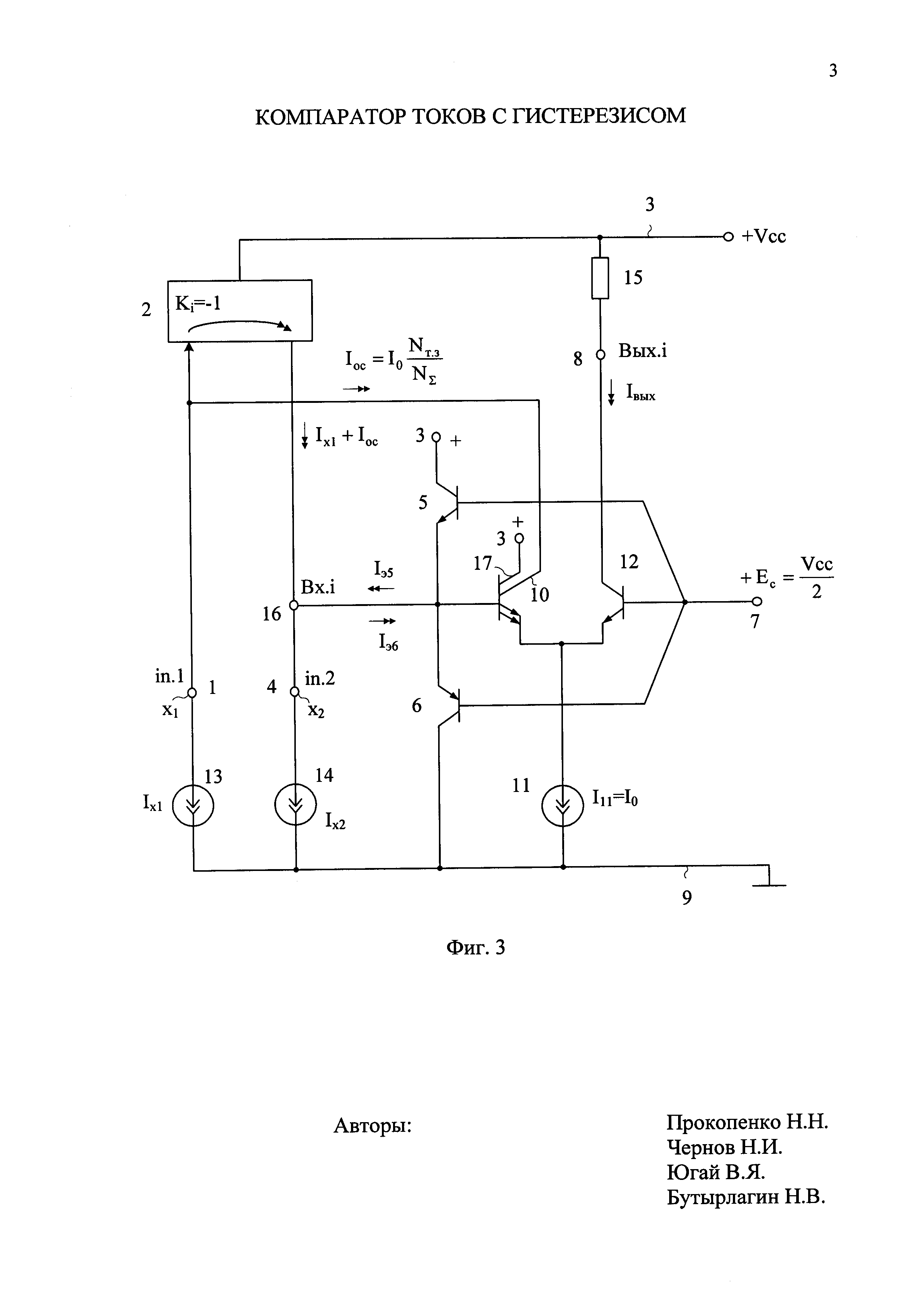

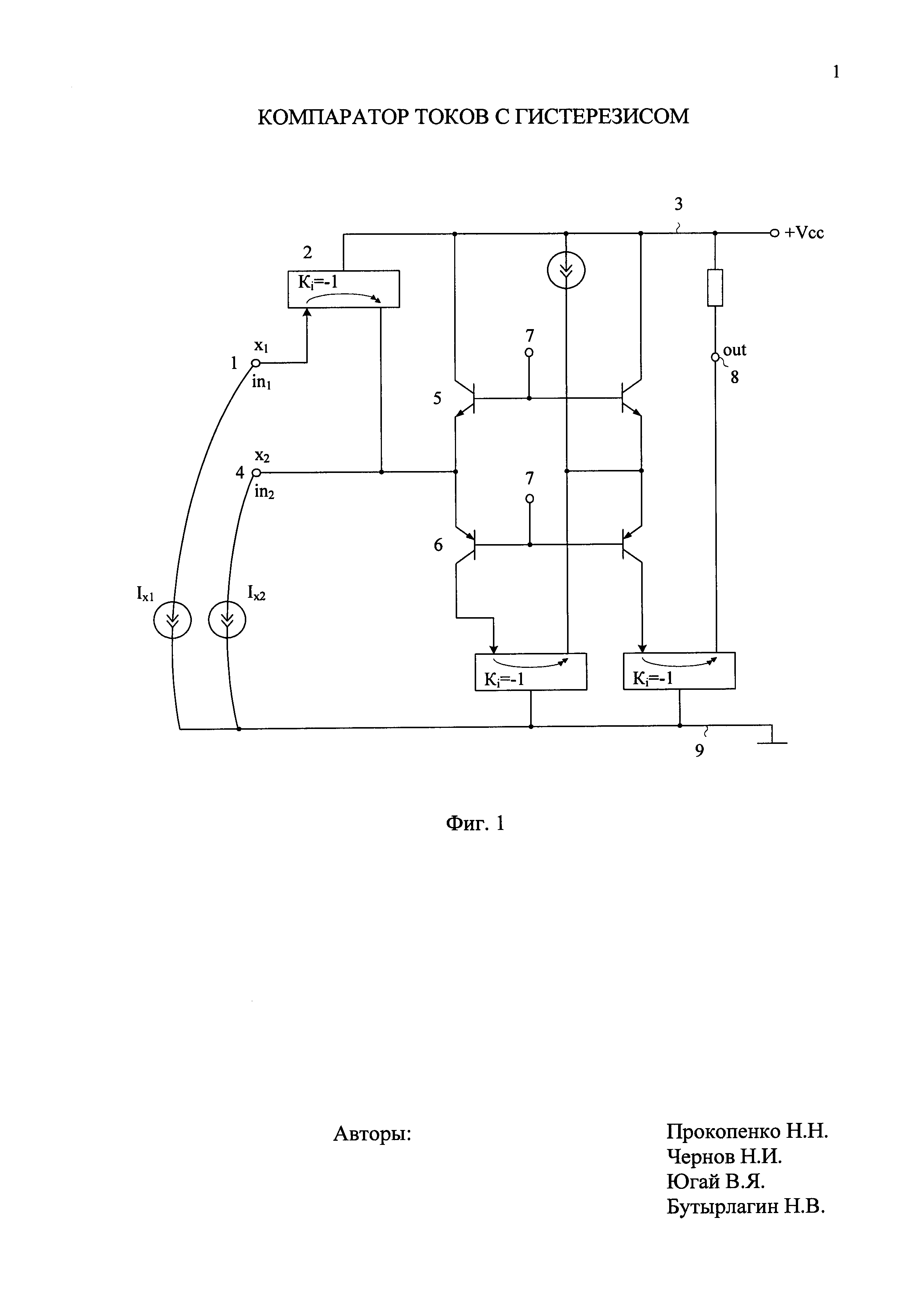

Ближайшим прототипом заявляемого устройства является компаратор двух входных токов с токовым выходом, представленный в патенте RU 2547233. Его назначение - обеспечить формирование выходного токового сигнала в результате сравнения на неравенство двух входных токов (Ix1, Ix2) в общем случае - многозначных. Компаратор-прототип фиг. 1 содержит первый 1 токовый логический вход, связанный со входом токового зеркала 2, согласованного с первой 3 шиной источника питания, второй 4 токовый логический вход, связанный с выходом токового зеркала 2 и объединенными эмиттерами первого 5 и второго 6 входных транзисторов, источник напряжения смещения 7, соединенный с базой первого 5 входного транзистора, коллектор которого подключен к первой 3 шине источника питания, токовый выход устройства 8, вторую 9 шину источника питания.

Существенный недостаток известного устройства состоит в том, что на его основе не реализуется компаратор входных токовых логических сигналов с гистерезисом. Наличие гистерезиса у компаратора имеет большое значение в случаях, когда величины двух сравниваемых токов (Ix1, Ix2) близки. В этом режиме возможны множественные переключения компаратора из-за шумов, помех, воздействий температуры или радиации, что недопустимо, т.к. приводит к сбоям в дальнейшей обработке сигналов.

Основная задача предлагаемого изобретения состоит в создании устройства, которое обеспечивает сравнение двух входных токовых сигналов Ix1, Ix2 и имеет гистерезис по входу Ix1, который может регулироваться по усмотрению разработчика. В конечном итоге это позволит создавать электронную компонентную базу для сенсоров с токовыми выходами, а также различных вычислительных устройств на основе искусственных нейронов.

Поставленная задача решается тем, что в компараторе токов (фиг. 1), содержащем первый 1 токовый логический вход, связанный со входом токового зеркала 2, согласованного с первой 3 шиной источника питания, второй 4 токовый логический вход, связанный с выходом токового зеркала 2 и объединенными эмиттерами первого 5 и второго 6 входных транзисторов, источник напряжения смещения 7, соединенный с базой первого 5 входного транзистора, коллектор которого подключен к первой 3 шине источника питания, токовый выход устройства 8, вторую 9 шину источника питания, предусмотрены новые элементы и связи - коллектор второго 6 входного транзистора подключен ко второй 9 шине источника питания, а его база связана с источником напряжения смещения 7, база первого 10 дополнительного транзистора соединена с объединенными эмиттерами первого 5 и второго 6 входных транзисторов, его коллектор подключен ко входу токового зеркала 2, а эмиттер через токостабилизирующий двухполюсник 11 связан со второй 9 шиной источника питания и подключен к эмиттеру второго 12 дополнительного транзистора, причем база второго 12 дополнительного транзистора связана с источником напряжения смещения 7, а его коллектор подключен к токовому выходу устройства 8.

На фиг. 1 представлена схема компаратора-прототипа.

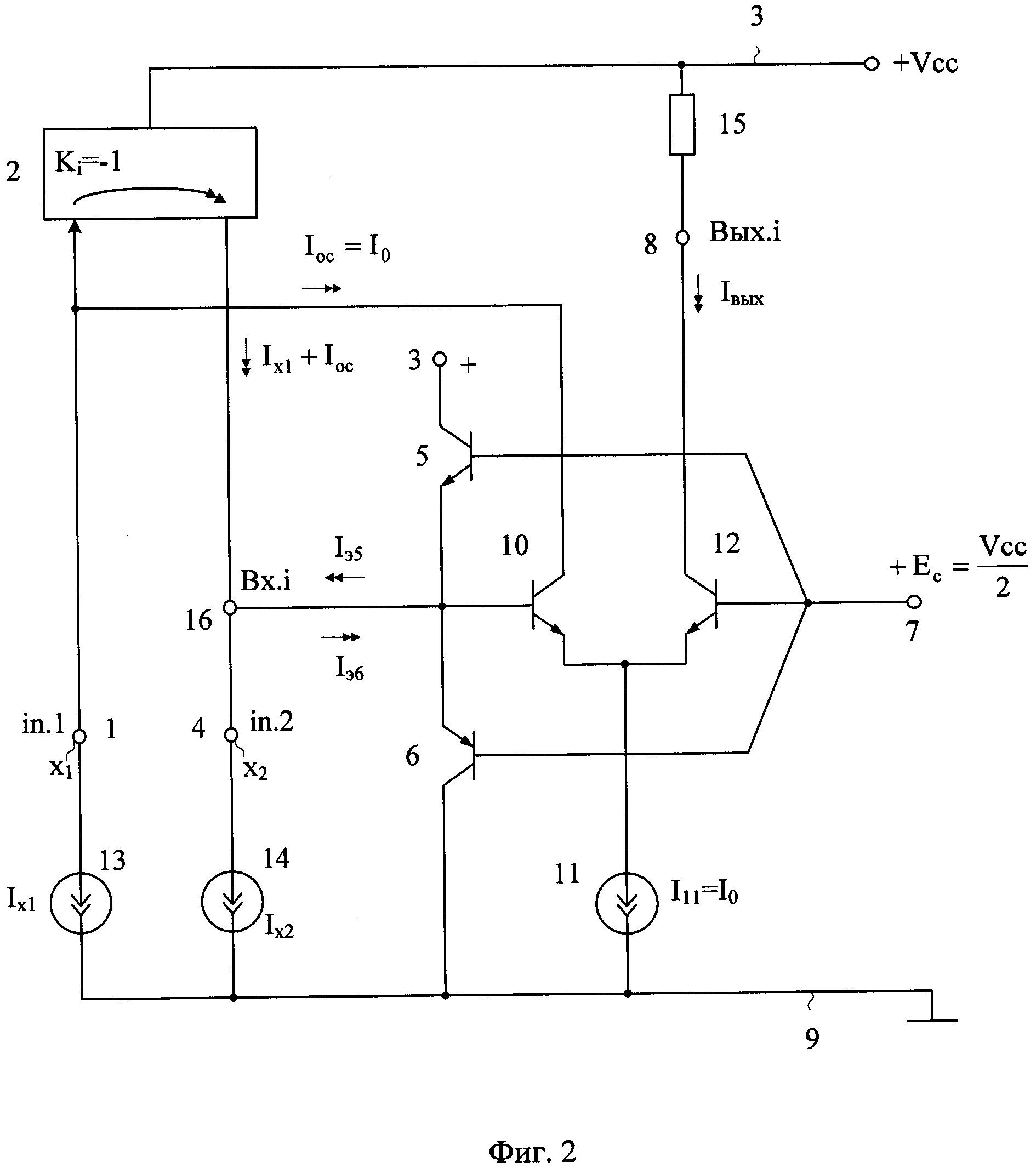

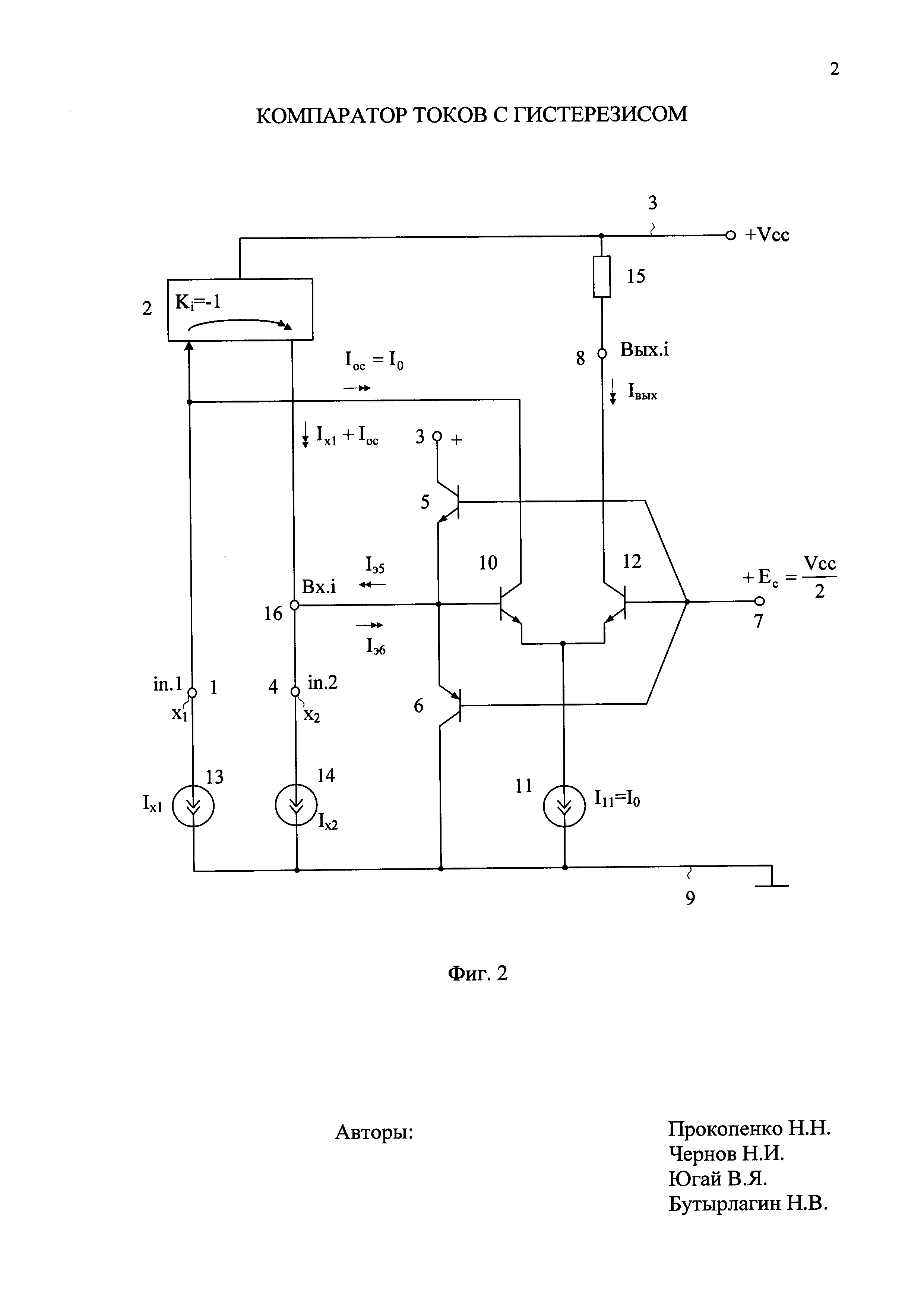

На фиг. 2 приведена схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

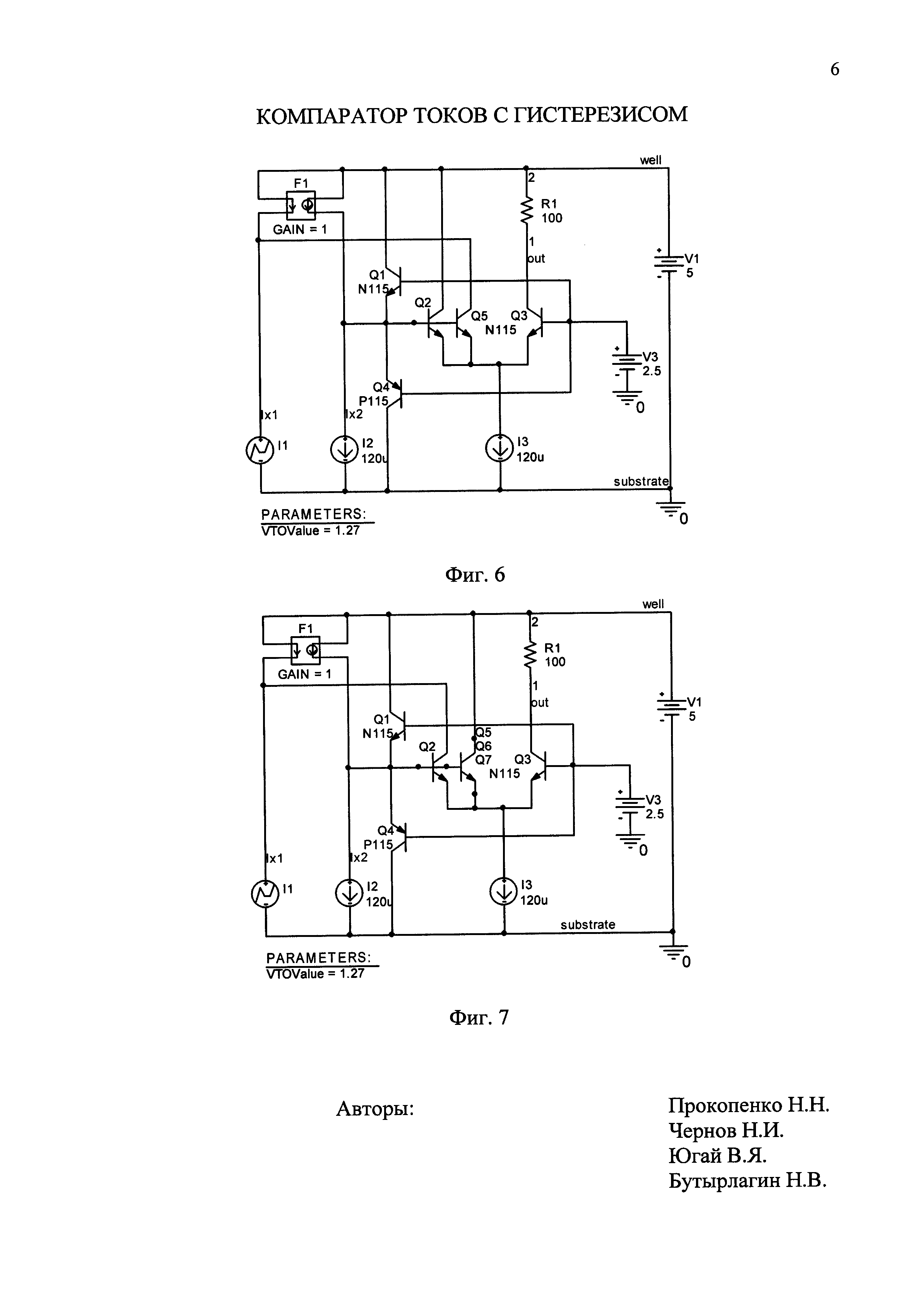

На фиг. 3 показана схема заявляемого компаратора в соответствии с п. 2 формулы изобретения.

На фиг. 4 представлена модификация схемы компаратора фиг. 3 в соответствии с пп. 3 и 4 формулы изобретения. Такие связи позволяют регулировать гистерезис заявляемого устройства.

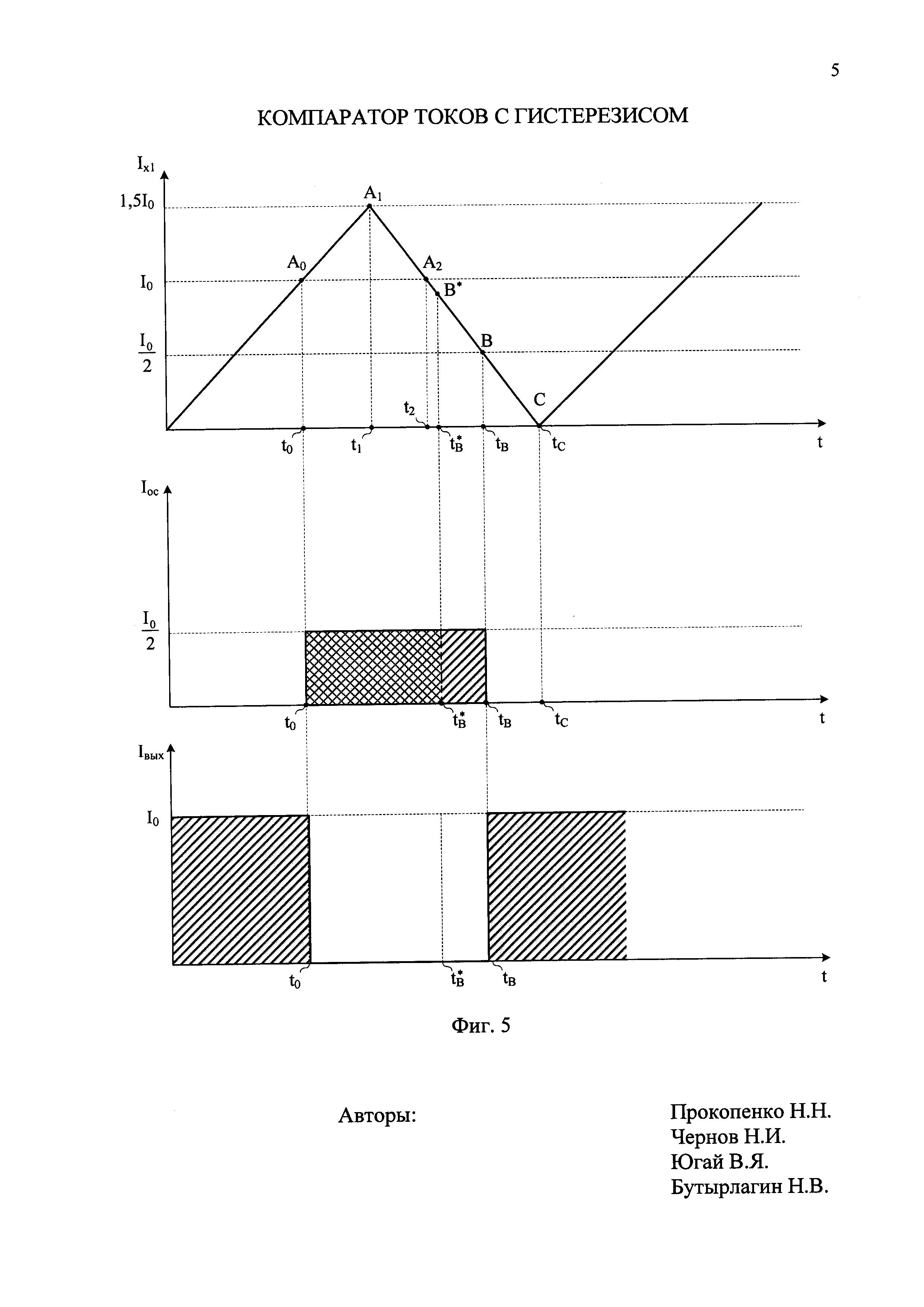

На фиг. 5 представлена теоретическая временная диаграмма работы компаратора токов фиг. 3.

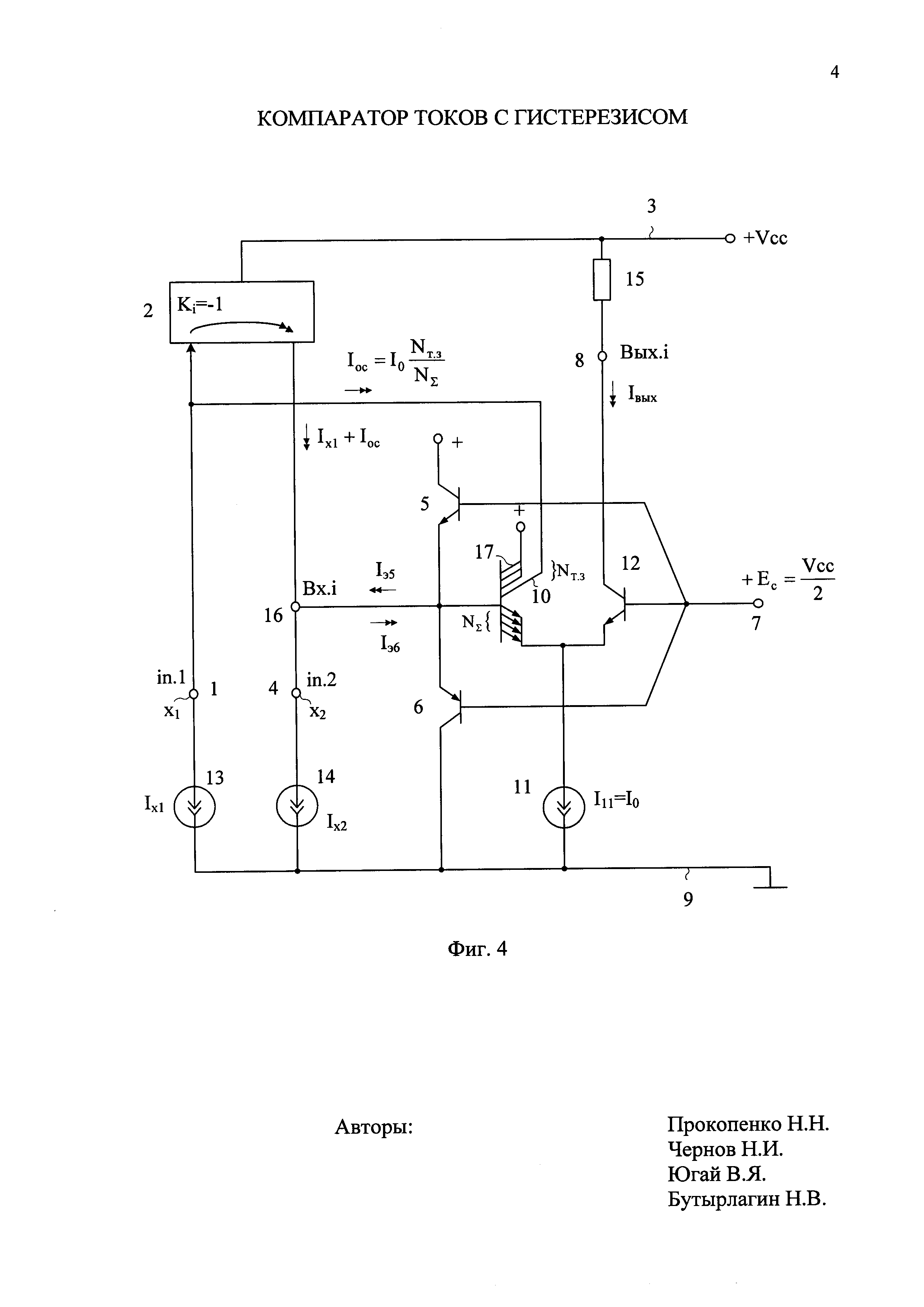

На фиг. 6 приведена схема заявляемого устройства фиг. 3 в среде компьютерного моделирования PSpice (для технологии аналогового базового матричного кристалла АБМК_2_1).

На фиг. 7 приведена схема заявляемого устройства фиг. 4 в среде PSpice (для технологии аналогового базового матричного кристалла АБМК_2_1).

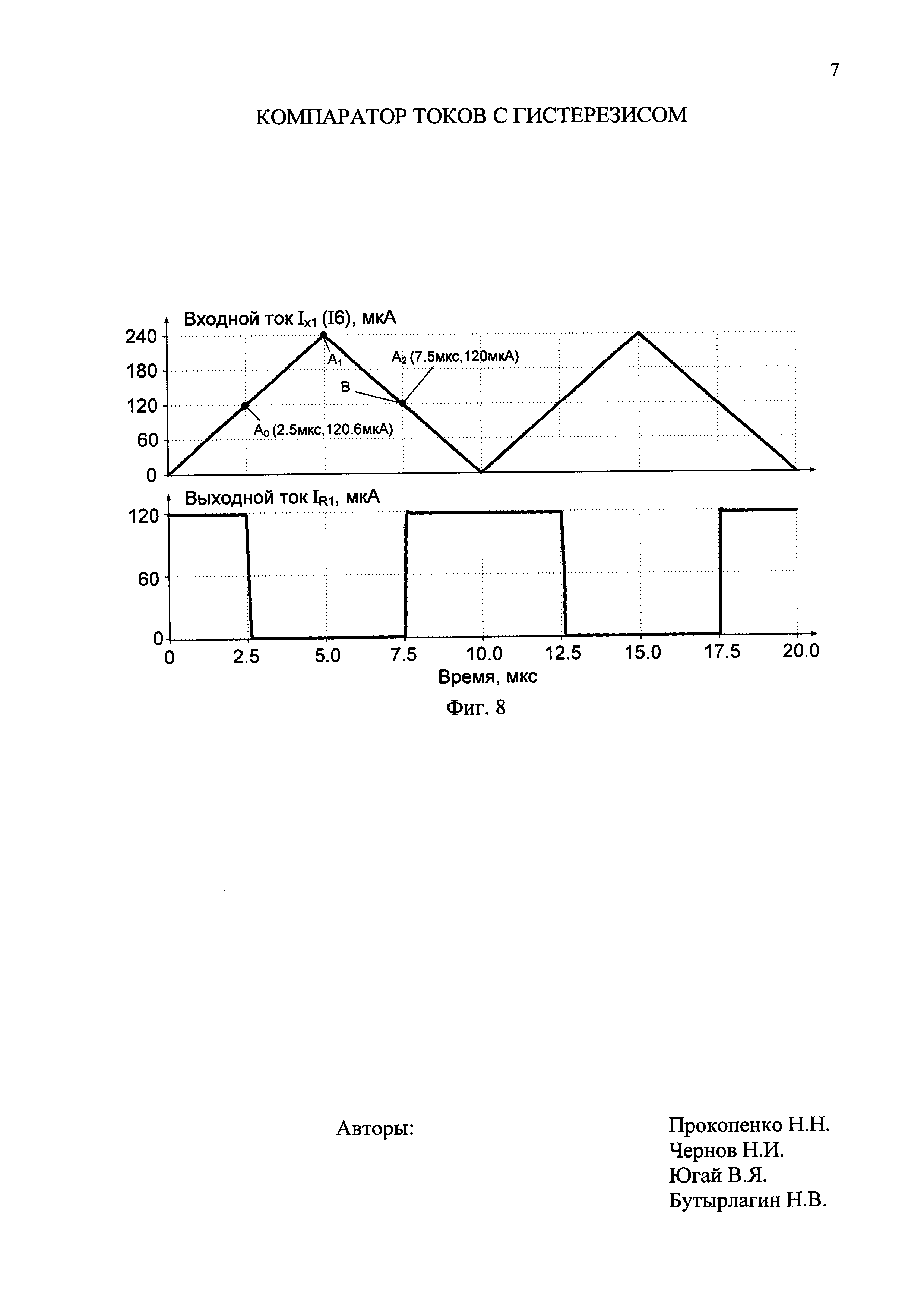

На фиг. 8 приведена временная диаграмма работы компаратора токов фиг. 6 (соответствует фиг. 3) без гистерезиса при фиксированном токе Ix2=120 мкА. Данный режим соответствует работе компаратора-прототипа и обеспечивается в схеме фиг. 6 (фиг. 3) подключением коллекторов первого 10 и третьего 17 дополнительных транзисторов к первой 3 шине источника питания.

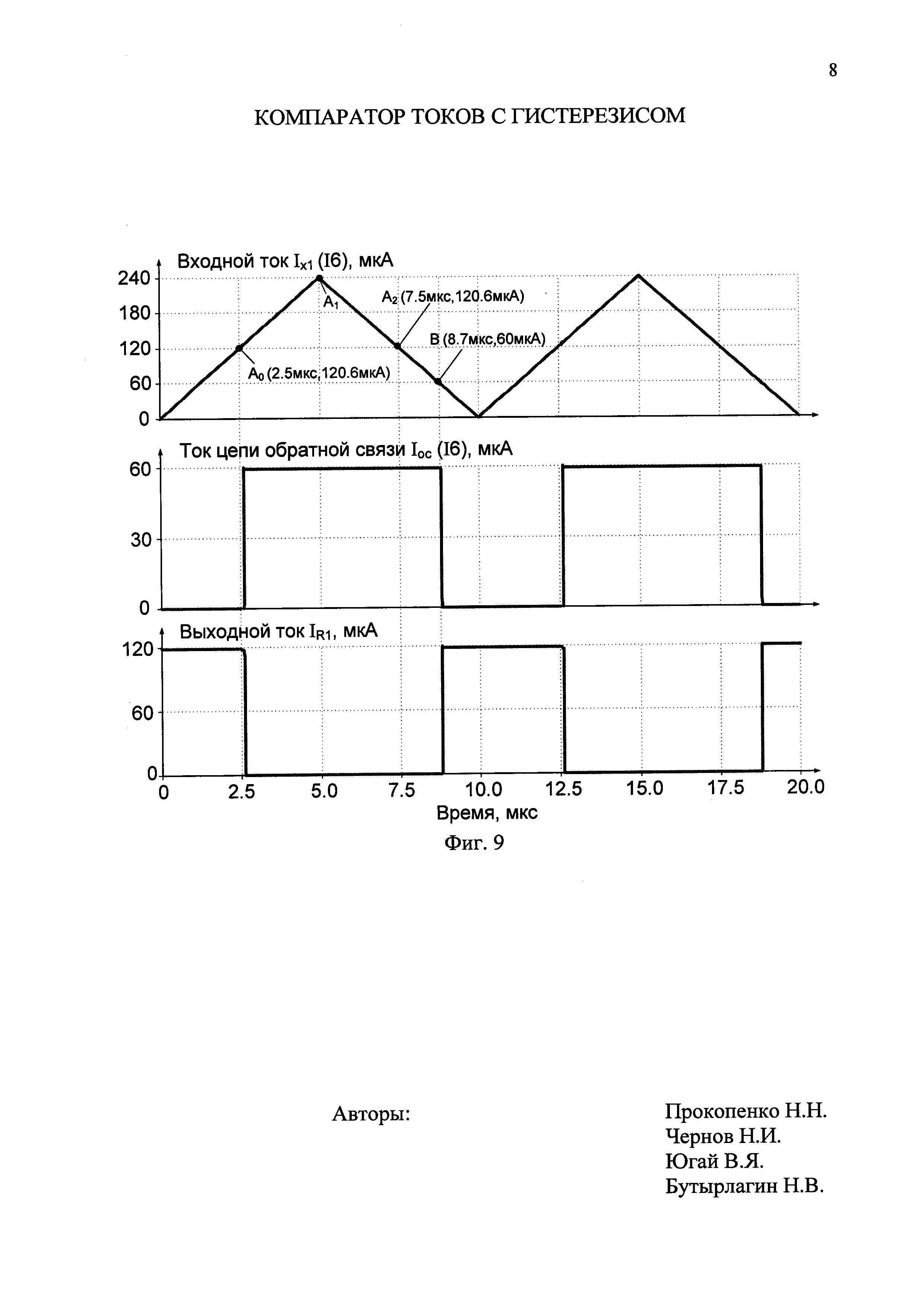

На фиг. 9 представлена временная диаграмма работы заявляемого компаратора токов фиг. 3.

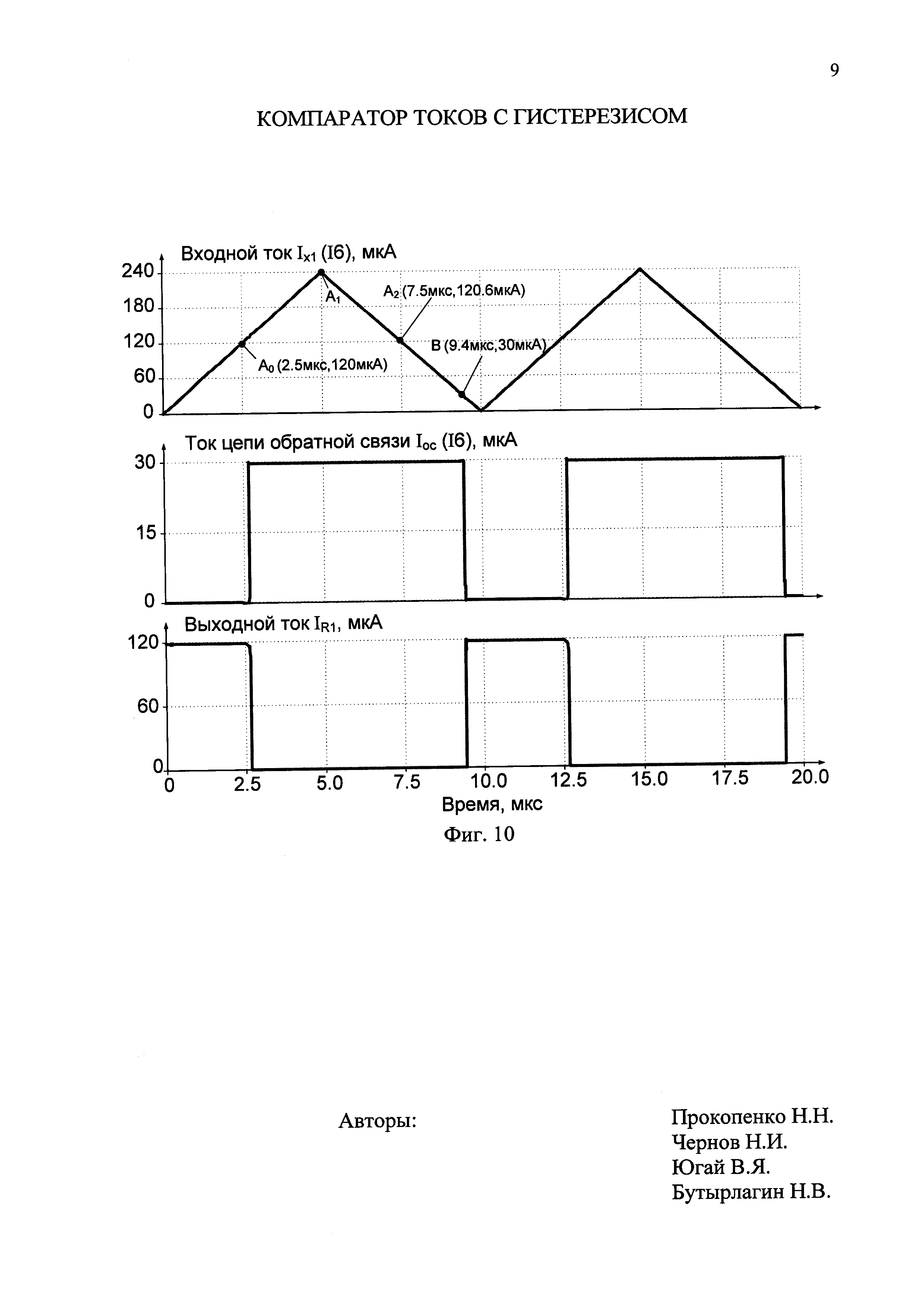

На фиг. 10 представлена временная диаграмма работы компаратора токов фиг. 7 (соответствует фиг. 4) с другими параметрами гистерезиса, которые определяются числом коллекторов элементарных транзисторов в третьем 17 (фиг. 4) (соответствует Q2 на чертеже фиг. 7) составном дополнительном транзисторе, подключенных ко входу токового зеркала 2 (F1).

Компаратор токов с гистерезисом фиг. 2 содержит первый 1 токовый логический вход, связанный со входом токового зеркала 2, согласованного с первой 3 шиной источника питания, второй 4 токовый логический вход, связанный с выходом токового зеркала 2 и объединенными эмиттерами первого 5 и второго 6 входных транзисторов, источник напряжения смещения 7, соединенный с базой первого 5 входного транзистора, коллектор которого подключен к первой 3 шине источника питания, токовый выход устройства 8, вторую 9 шину источника питания. Коллектор второго 6 входного транзистора подключен ко второй 9 шине источника питания, а его база связана с источником напряжения смещения 7, база первого 10 дополнительного транзистора соединена с объединенными эмиттерами первого 5 и второго 6 входных транзисторов, его коллектор подключен ко входу токового зеркала 2, а эмиттер через токостабилизирующий двухполюсник 11 связан со второй 9 шиной источника питания и подключен к эмиттеру второго 12 дополнительного транзистора, причем база второго 12 дополнительного транзистора связана с источником напряжения смещения 7, а его коллектор подключен к токовому выходу устройства 8.

В схеме фиг. 2 первая входная логическая переменная Ix1, подаваемая на первый 1 токовый логический вход, моделируется источником тока 13. Кроме этого, вторая входная логическая переменная Ix2, подаваемая на второй 2 токовый логический вход устройства, моделируется источником тока 14.

Двухполюсник 15 на фиг. 2 моделирует свойства нагрузки, которая подключается к токовому выходу 8 устройства.

Суммирующий узел 16 на фиг. 2 является токовым входом Bx.i, в котором обеспечивается сравнение токовых логических переменных.

На фиг. 3 в соответствии с п. 2 формулы изобретения в схему введен третий 17 дополнительный транзистор, база которого соединена с базой первого 10 дополнительного транзистора, эмиттер соединен с эмиттером первого 10 дополнительного транзистора, а коллектор подключен к первой 3 шине источника питания.

На фиг. 4 в соответствии с п. 3 формулы изобретения третий 17 дополнительный транзистор выполнен как составной транзистор, который содержит N17>1 параллельно включенных элементарных биполярных транзисторов.

Кроме этого, на фиг. 4 в соответствии с п. 4 формулы изобретения первый 10 дополнительный транзистор выполнен как составной транзистор, который содержит NT.3>l параллельно включенных элементарных биполярных транзисторов.

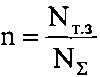

Данная схемотехника позволяет регулировать гистерезис заявляемого компаратора путем изменения коэффициентов N∑ и NT.З, где N∑ - общее количество параллельно включенных эмиттерно-базовых переходов элементарных транзисторов, входящих в структуру первого 10 и третьего 17 дополнительных транзисторов, NT.З - количество коллекторов элементарных транзисторов, входящих в структуру первого 10 составного дополнительного транзистора, связанного с токовым зеркалом 2.

Рассмотрим работу компаратора токов фиг. 3 на основе диаграммы фиг. 5.

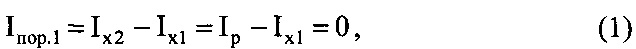

Если зафиксировать второй логический ток на уровне Ix2=Ip=I0/m, то первый уровень порогового тока Ix1, при котором переключается компаратор, можно найти из уравнения

где m=I0/Ip - отношение кванта тока I0 к заданному фиксированному значению логической переменной Ix2=Ip, Ip - заданный фиксированный уровень тока Ix2, причем Ip=0÷I0.

То есть компаратор в этом случае срабатывает при Ix1=Ip (точка «А0» на чертеже фиг. 5). После этого на вход токового зеркала 2 поступает не только ток Ix1, но и часть кванта тока I0 (тока коллектора первого 10 дополнительного транзистора). Поэтому компаратор переходит в другое состояние, когда

где

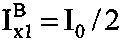

Из уравнения (2) можно найти входной пороговый ток  , при котором компаратор возвращается в исходное состояние (точка «В» на чертеже фиг. 5):

, при котором компаратор возвращается в исходное состояние (точка «В» на чертеже фиг. 5):

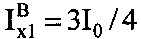

Если m=1, Nт.з=1, N∑=2, то  . При Nт.з=1, N∑=4, m=1, из (3) получаем, что

. При Nт.з=1, N∑=4, m=1, из (3) получаем, что  (фиг. 10). В пределе, когда коэффициенты m=1 и n=1, имеем

(фиг. 10). В пределе, когда коэффициенты m=1 и n=1, имеем  .

.

Таким образом, при изменении отношения n=Nт.з/N∑ в диапазоне 0÷1 и фиксированном значении Ix2=Ip=I0/m параметры гистерезиса для логической переменной Ix1 изменяются в диапазоне Ix1=I0÷0.

Аналогично можно определить параметры гистерезиса при других численных значениях коэффициента m (Ix2=Ip=I0/m).

Представленные на чертежах фиг. 8, фиг. 9, фиг. 10 временные работы компаратора подтверждают полученные выше результаты анализа.

Таким образом, заявляемое устройство имеет управляемые параметры гистерезиса, что обеспечивает ему существенные преимущества в сравнении с прототипом.

Источники информации

1. Патентная заявка WO 2004/112247

2. Патент US 6157693, fig. 5

3. Патентная заявка US 2009/0237163, fig. 2

4. Патентная заявка US 2006/0006910

5. Патентная заявка US 2008/0032656, fig. 6

6. Патентная заявка US 2010/0097141, fig. 7

7. Патент ФРГ №2551068

8. Патент ФРГ №2620999

9. Патентная заявка US 2007/0018694

10. Патент US 6414519

11. Патент US 6566912

12. Патент US 6700413

13. Патент US 6680625

14. Патент JP 10098374

15. Патент US 6573758

16. Патент РФ №2549142

17. Патент РФ №2553070

18. Патент US 5446397

19. Патент US 7583108

20. Патент US 6008673

21. Патент US 7170329

22. Патент US 6424183

23. Патент US 6275075

24. Патент US 6586972

25. Патент US 6320427

26. Патент US 5136184

27. Патент US 5077491

28. Патент US 4069460

29. Патент US 4.348.602

30. Патент РФ 2546085

31. Патент РФ 2547225

32. Патент РФ 2547233

33. Патент РФ 2549142

34. Патент РФ 2553070

35. Патент РФ 2503071

36. Патент РФ 2554557

37. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С. 84-93.

38. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

39. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.