Результат интеллектуальной деятельности: ТОКОВЫЙ ЭЛЕМЕНТ ОГРАНИЧЕНИЯ МНОГОЗНАЧНОЙ ВЫХОДНОЙ ЛОГИЧЕСКОЙ ПЕРЕМЕННОЙ

Вид РИД

Изобретение

Предполагаемое изобретение относится к области вычислительной техники, автоматики, связи и может использоваться в цифровых вычислительных структурах, системах автоматического управления, передачи и обработки цифровой информации и т.п.

Токовая логика, базирующаяся на принципах линейной (не булевой алгебры), относится к одному из новых направлений синтеза и практической реализации цифровых структур (ЦС) и постоянно развивается [1-15]. Преимущества таких ЦС - потенциальная возможность работы в жестких условиях эксплуатации (космороботы, беспилотные летательные аппараты, ядерные объекты и т.д.).

Одним из важных направлений синтеза и практической реализации цифровых структур является пороговая логика, теоретические основы которой заложены в работах [16-20]. Для ее практического использования в токовых устройствах автоматики и связи необходимо иметь специальные элементы ограничения выходных токовых логических переменных. Заявляемое устройство относится к этому типу логических элементов.

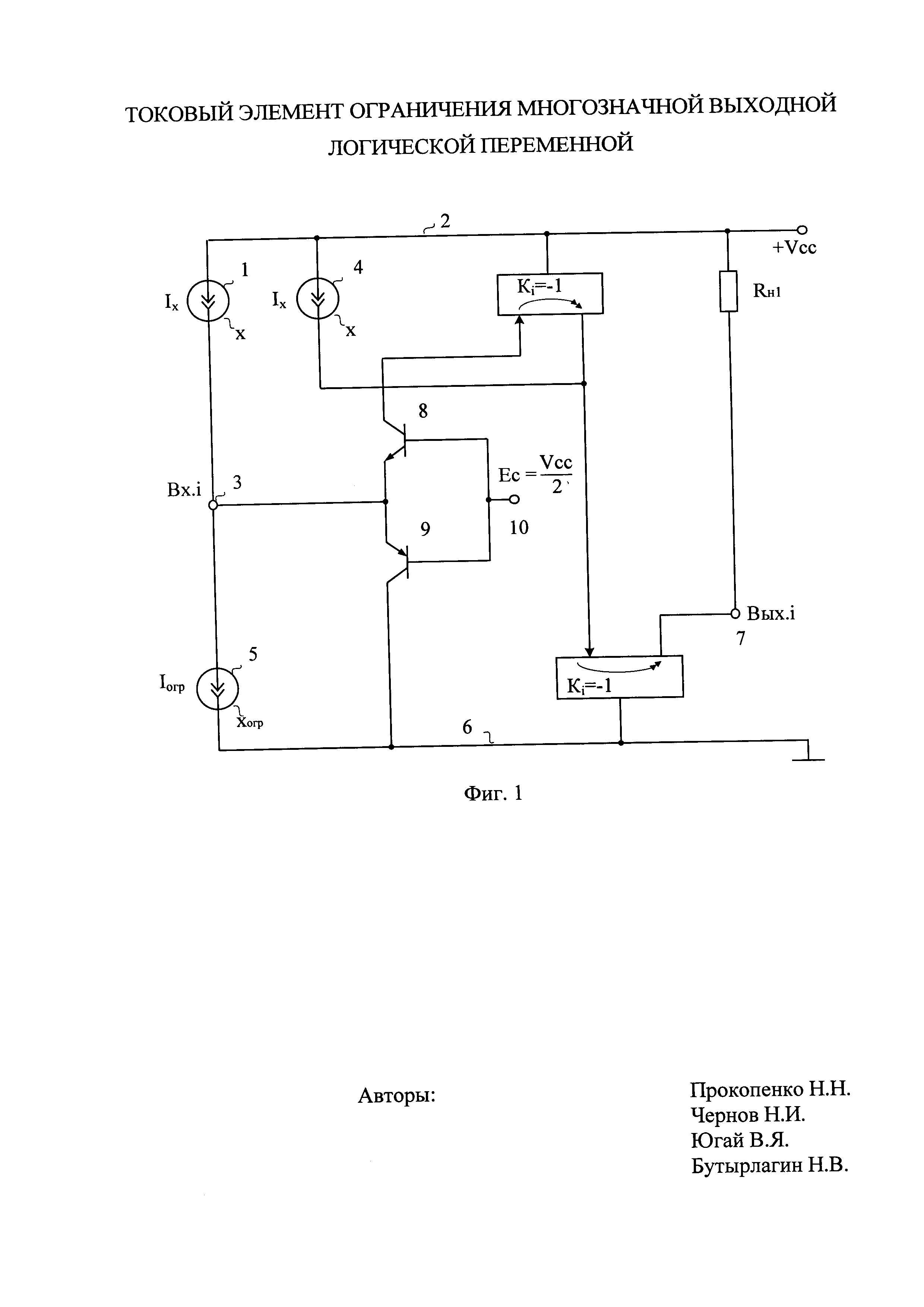

Ближайшим прототипом заявляемого устройства является логический элемент «максимум», представленный в патенте RU 2568385 (фиг.1). Он содержит первый 1 источник входного логического тока, соответствующий первой многозначной логической переменной "х", который включен между первой 2 шиной источника питания и токовым входом 3 устройства, второй 4 источник входного логического тока, соответствующий первой многозначной логической переменной "х", третий 5 источник входного логического тока, соответствующий второй логической переменной "хогр", устанавливающей уровень ограничения выходного тока устройства, который включен между токовым входом 3 устройства и второй 6 шиной источника питания, первый 7 токовый выход устройства, первый 8 и второй 9 входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу 3 устройства, причем коллектор первого 8 входного транзистора согласован с первой 2 шиной источника питания, а коллектор второго 9 входного транзистора подключен ко второй 6 шине источника питания, источник вспомогательного напряжения 10, связанный с базами первого 8 и второго 9 входных транзисторов.

Существенный недостаток известного устройства фиг.1 состоит в том, что оно реализует лишь одну токовую пороговую логическую функцию «Ограничение сверху» двух многозначных входных переменных ("х", "хогр"), соответствующих значениям входных токов Ix, Iогр. Это требует неоправданного расширения номенклатуры базовых токовых элементов для реализации второй токовой пороговой функции «Ограничение снизу» двух многозначных входных переменных ("х", "хогр"), соответствующих значениям входных токов Ix, Iогр, и не позволяет создать на его основе универсальный базис логических элементов для построения средств вычислительной техники, функционирующих на принципах пороговой логики.

Основная задача предлагаемого изобретения состоит в создании элемента ограничения, который в рамках одной и той же архитектуры может реализовывать две пороговые логические функции «Ограничение снизу» и «Ограничение сверху» двух многозначных входных переменных ("х", "хогр"). Это позволяет уменьшить номенклатуру базовых элементов токовой логики и повысить технологичность изготовления элементной базы многозначной пороговой логики, работающей на принципах линейной алгебры [21-23].

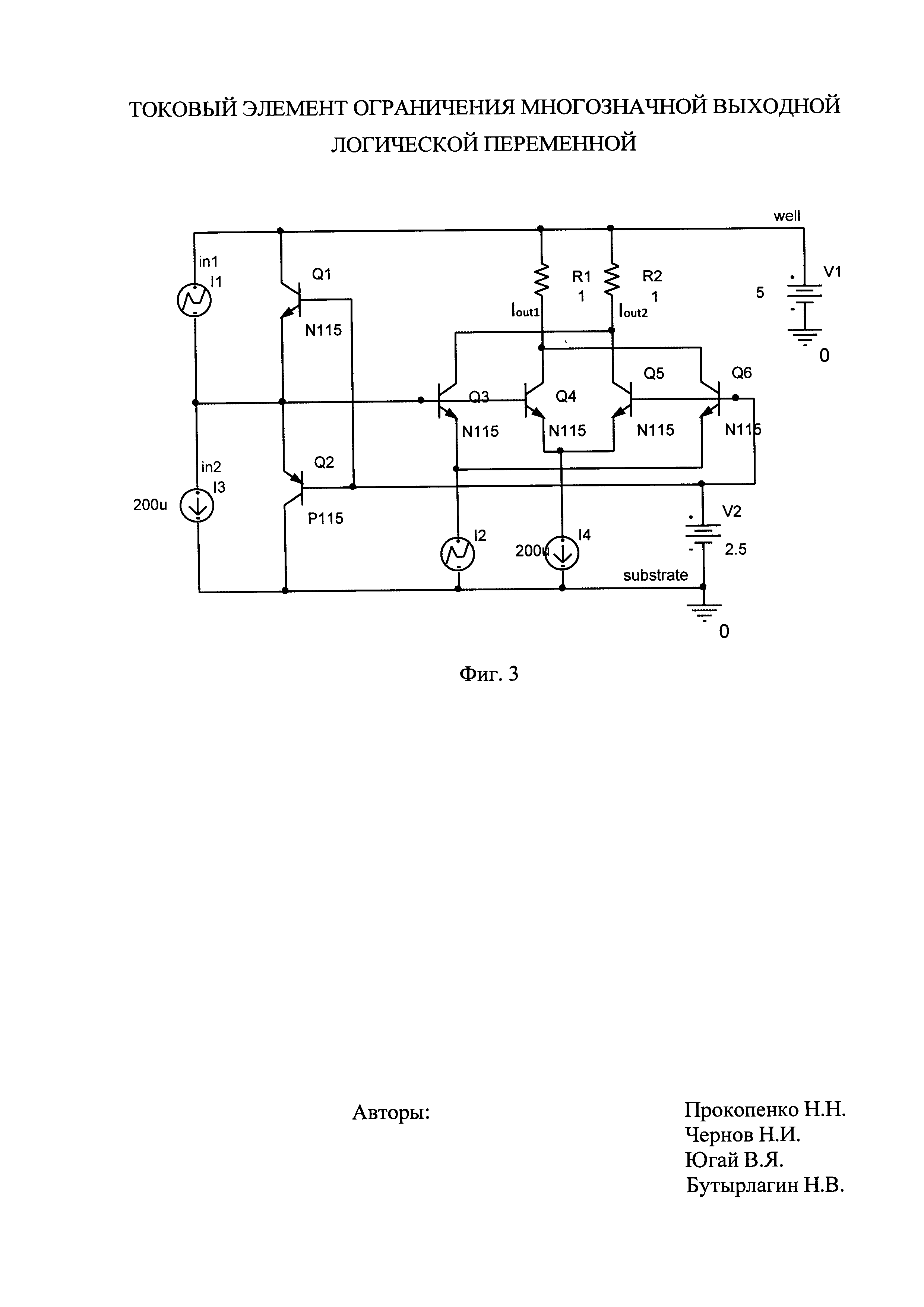

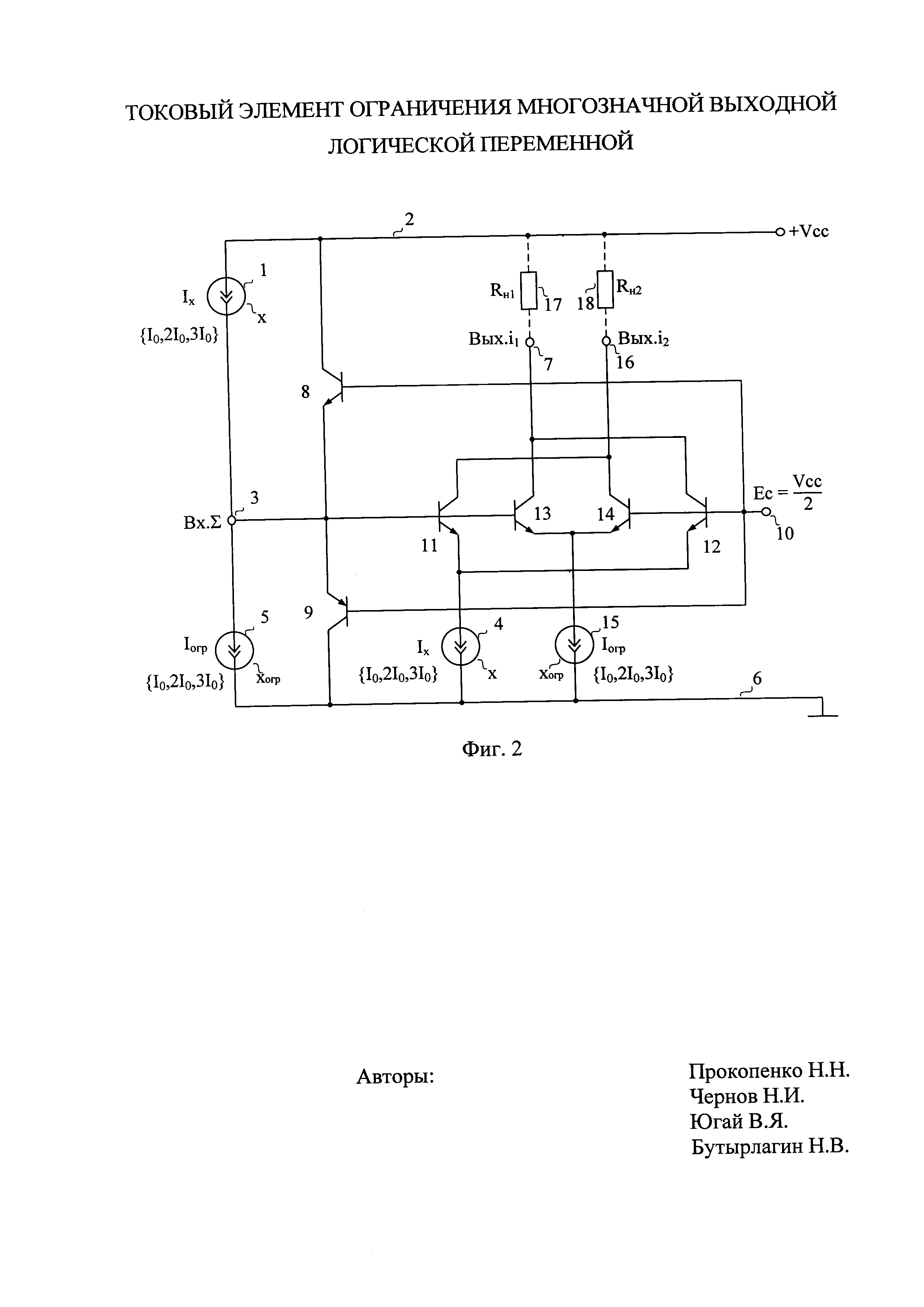

Поставленная задача решается тем, что в токовом логическом элементе (фиг. 1), содержащем первый 1 источник входного логического тока, соответствующий первой многозначной логической переменной "х", который включен между первой 2 шиной источника питания и токовым входом 3 устройства, второй 4 источник входного логического тока, соответствующий первой многозначной логической переменной "х", третий 5 источник входного логического тока, соответствующий второй логической переменной "хогр", устанавливающей уровень ограничения выходного тока устройства, который включен между токовым входом 3 устройства и второй 6 шиной источника питания, первый 7 токовый выход устройства, первый 8 и второй 9 входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу 3 устройства, причем коллектор первого 8 входного транзистора согласован с первой 2 шиной источника питания, а коллектор второго 9 входного транзистора подключен ко второй 6 шине источника питания, источник вспомогательного напряжения 10, связанный с базами первого 8 и второго 9 входных транзисторов, предусмотрены новые элементы и связи - в схему добавлены первый 11, второй 12, третий 13 и четвертый 14 дополнительные транзисторы, причем второй 4 источник входного логического тока включен между объединенными эмиттерами первого 11 и второго 12 дополнительных транзисторов и второй 6 шиной источника питания, первый 15 дополнительный источник входного логического тока, соответствующий второй логической переменной "хогр", устанавливающей уровень ограничения выходного тока устройства, включен между объединенными эмиттерами третьего 13 и четвертого 14 дополнительных транзисторов и второй 6 шиной источника питания, коллекторы второго 12 и третьего 13 дополнительных транзисторов объединены и связаны с первым 7 токовым выходом устройства, коллекторы первого 11 и четвертого 14 дополнительных транзисторов объединены и подключены ко второму 16 дополнительному токовому выходу устройства, базы первого 11 и третьего 13 дополнительных транзисторов объединены и подключены к токовому входу 3 устройства, базы второго 12 и четвертого 14 дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения 10.

Схема известного устройства показана на фиг. 1. На фиг. 2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

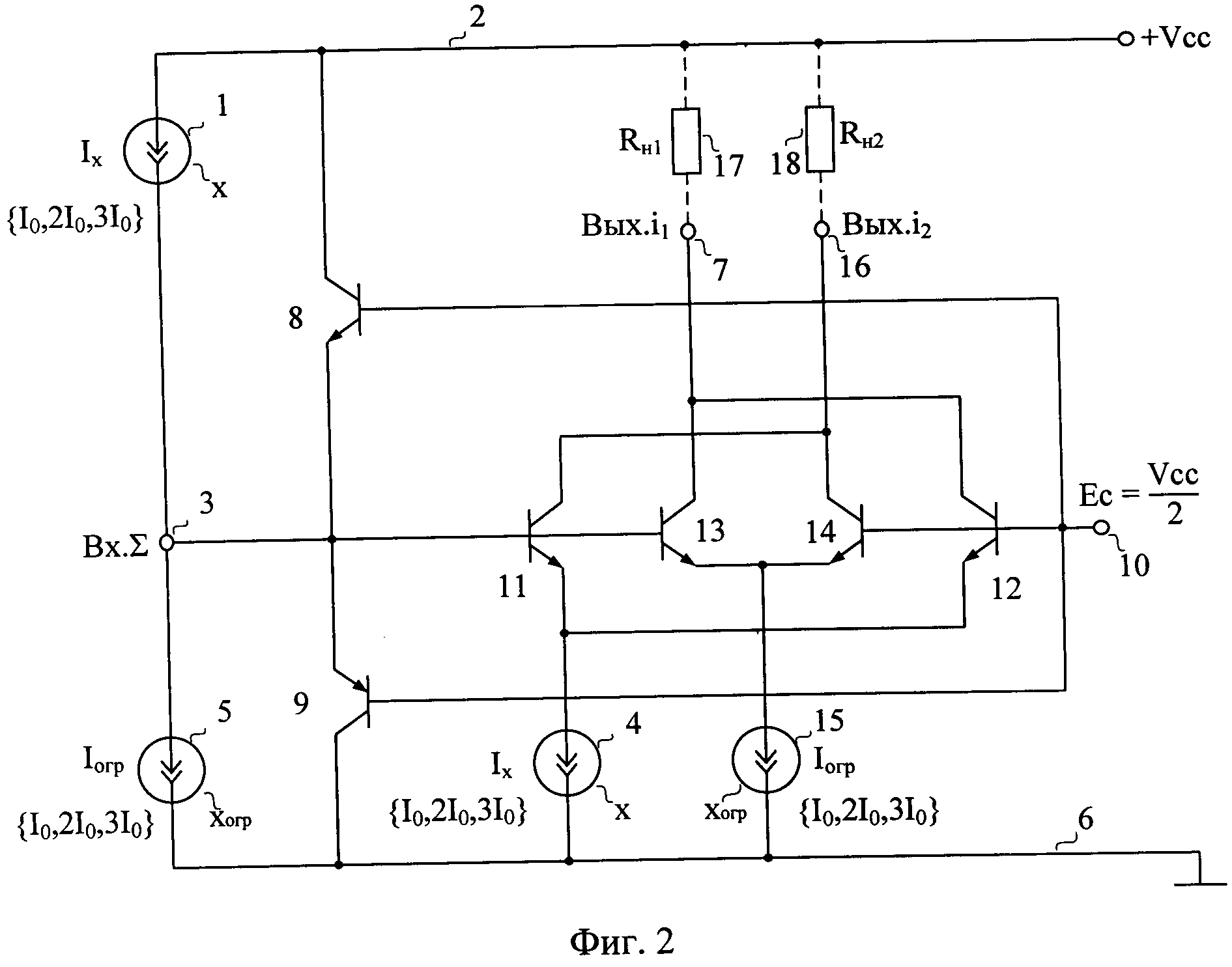

На фиг. 3 представлена принципиальная схема заявляемого устройства фиг. 2 в среде компьютерного моделирования PSpice.

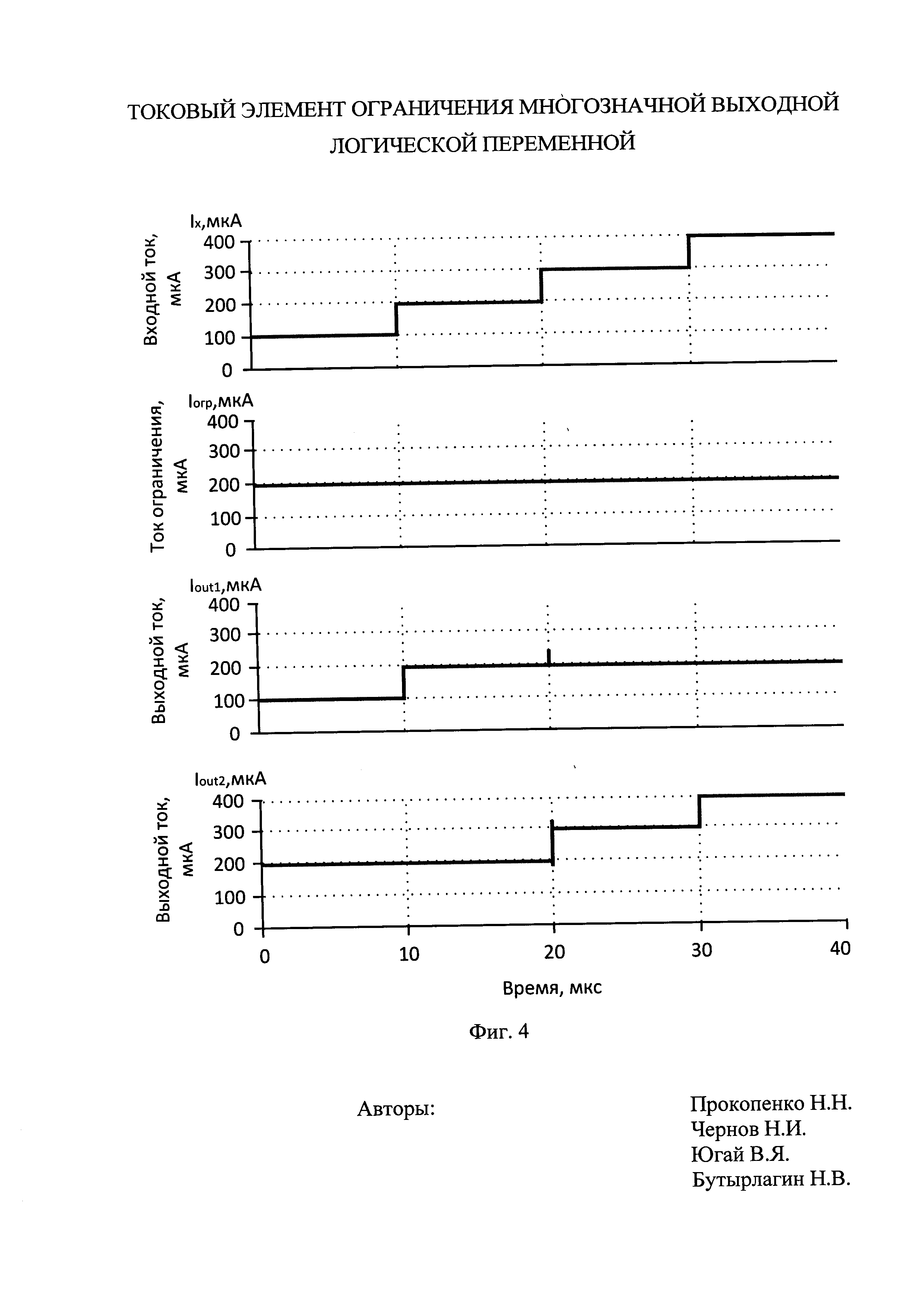

На фиг. 4 приведены временные диаграммы работы заявляемого устройства фиг. 3, где ток, соответствующий первой входной переменной "х", равен I1=I2≈Ix, а ток второй входной переменной "хогр" равен I3=I4≈Iогр.

Токовый элемент ограничения многозначной выходной логической переменной фиг. 2 содержит первый 1 источник входного логического тока, соответствующий первой многозначной логической переменной "х", который включен между первой 2 шиной источника питания и токовым входом 3 устройства, второй 4 источник входного логического тока, соответствующий первой многозначной логической переменной "х", третий 5 источник входного логического тока, соответствующий второй логической переменной "хогр", устанавливающей уровень ограничения выходного тока устройства, который включен между токовым входом 3 устройства и второй 6 шиной источника питания, первый 7 токовый выход устройства, первый 8 и второй 9 входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу 3 устройства, причем коллектор первого 8 входного транзистора согласован с первой 2 шиной источника питания, а коллектор второго 9 входного транзистора подключен ко второй 6 шине источника питания, источник вспомогательного напряжения 10, связанный с базами первого 8 и второго 9 входных транзисторов. В схему введены первый 11, второй 12, третий 13 и четвертый 14 дополнительные транзисторы, причем второй 4 источник входного логического тока включен между объединенными эмиттерами первого 11 и второго 12 дополнительных транзисторов и второй 6 шиной источника питания, первый 15 дополнительный источник входного логического тока, соответствующий второй логической переменной "хогр", устанавливающей уровень ограничения выходного тока устройства, включен между объединенными эмиттерами третьего 13 и четвертого 14 дополнительных транзисторов и второй 6 шиной источника питания, коллекторы второго 12 и третьего 13 дополнительных транзисторов объединены и связаны с первым 7 токовым выходом устройства, коллекторы первого 11 и четвертого 14 выходных транзисторов объединены и подключены ко второму 16 дополнительному токовому выходу устройства, базы первого 11 и третьего 13 дополнительных транзисторов объединены и подключены к токовому входу 3 устройства, базы второго 12 и четвертого 14 дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения 10, первый 17 и второй 18 двухполюсники моделируют свойства нагрузки.

Рассмотрим работу устройства фиг. 2. При подаче на токовый вход заданного уровня ограничения Iогр входной многозначный сигнал х на выходе у ограничивается «снизу» или «сверху» величиной Iогр. При этом направления выходных токов могут быть любыми, в зависимости от условий функционирования предыдущих и последующих элементов схемы.

Входные токовые сигналы первого 1 (Ix) и третьего 5 (Iогр) источников входного логического тока поступают на токовый вход 3 устройства. Так как ток Ix является втекающим, а ток Iогр - вытекающим, то в эмиттеры первого 8 и второго 9 входных транзисторов поступает разность этих входных токов. Токи второго 4 (Ix) и четвертого 15 (Iогр) источников входного логического тока являются вытекающими.

При выполнении неравенства Ix>Iогр в токовом входе 3 устройства формируется разностный втекающий ток, который будет «уходить» в эмиттер второго 9 входного транзистора, снижая напряжение на базах первого 11 и второго 13 дополнительных транзисторов до значения Ес-Uбэ9, где Uбэ9 - напряжение открытого эмиттерного перехода второго 9 входного транзистора. Первый дополнительный транзистор 11 будет открыт и его выходной вытекающий ток будет равен току Ix, который поступит на второй 16 токовый выход устройства (Вых.i2). Третий 13 дополнительный транзистор также будет открыт и его выходной ток будет равен току Iогр, который поступит на первый 7 токовый выход устройства (Вых.i1). При этом второй 12 и четвертый 14 дополнительные транзисторы будут закрыты.

При выполнении неравенства Ix<Iогр в токовом входе 3 устройства формируется разностный вытекающий ток, который будет протекать через эмиттер первого 8 входного n-p-n-транзистора, увеличивая напряжение на базах первого 11 и второго 13 дополнительных транзисторов до значения Ес+Uбэ8, где Uбэ8 - напряжение открытого эмиттерного перехода первого 8 входного транзистора. Второй 12 дополнительный транзистор будет открыт, и его вытекающий выходной ток будет равен току Ix, который поступит на первый 7 токовый выход устройства (Вых.i1), при этом четвертый 14 дополнительный транзистор также будет открыт и его выходной ток будет равен току Iогр, который поступит на второй 16 дополнительный токовый выход устройства (Вых.i2), а первый 11 и третий 13 дополнительные транзисторы будут закрыты.

Показанные на чертеже фиг. 4 результаты моделирования подтверждают указанные свойства заявляемой схемы логического элемента пороговой логики.

Таким образом, в схеме фиг. 2 по первому 7 токовому выходу предлагаемого устройства выходной сигнал принимает значение, соответствующее меньшему из двух входных сигналов ("х", "хогр"), а по второму 16 дополнительному токовому выходу - выходной сигнал принимает значение, соответствующее большему из двух входных сигналов ("х", "хогр").

Резисторы 17 и 18 являются вспомогательными и служат для определения наличия тока в выходных цепях. Они используются только в процессе экспериментальных исследований схемы.

Предлагаемое схемотехническое решение порогового элемента характеризуется многозначным состоянием внутренних сигналов и сигналов на его токовых выходах, что может быть положено в основу вычислительных и управляющих устройств, использующих многозначную пороговую логику.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №2514789.

2. Патент РФ №2520416.

3. Патент РФ №2546078.

4. Патент РФ №2546082.

5. Патент РФ №2546085.

6. Патент РФ №2547225.

7. Патент РФ №2547231.

8. Патент РФ №2547233.

9. Патент РФ №2549144.

10. Патент РФ №2549142.

11. Патент РФ №2553070.

12. Патент РФ №2553071.

13. Патент РФ №2554557.

14. Патент РФ №2559705.

15. Патент РФ №2568385.

16. Дертоузос М. Пороговая логика // М.: Мир, 1967. 344 с.

17. Зуев Ю.А. Пороговые функции и пороговые представления булевых функций // Матем. вопросы кибернетики. Вып. 5. - М.: Физматлит, 1994. - С. 5-61.

18. Никонов В.Г., Никонов Н.В. Особенности пороговых представлений k-значных функций. // «Труды по дискретной математике», 2008, Т. 11.

19. Волгин Л.И. Синтез и схемотехника аналоговых электронных средств в элементном базисе усилителей и повторителей тока: монография / Л.И. Волгин, А.И. Зарукин; под общ. ред. Л.И. Волгина; УлГТУ. - Ульяновск: УлГТУ, 2005. - 200 с.: ил.

20. Бурделев А.В., Никонов В.Г. О построении аналитического задания k-значной пороговой функции. «Computational nanotechnology», 2015, вып. 2.

21. Прокопенко Н.Н., Чернов Н.И., Югай В.Я., Бутырлагин Н.В. Линейный синтез k-значной цифровой элементной базы с токовыми логическими сигналами: принцип обобщения // Проблемы разработки перспективных микро- и наноэлектронных систем - 2016. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2016. Часть I. С. 70-77.

22. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

23. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.

Токовый элемент ограничения многозначной выходной логической переменной, содержащий первый (1) источник входного логического тока, соответствующий первой многозначной логической переменной "х", который включен между первой (2) шиной источника питания и токовым входом (3) устройства, второй (4) источник входного логического тока, соответствующий первой многозначной логической переменной "х", третий (5) источник входного логического тока, соответствующий второй логической переменной "х", устанавливающей уровень ограничения выходного тока устройства, который включен между токовым входом (3) устройства и второй (6) шиной источника питания, первый (7) токовый выход устройства, первый (8) и второй (9) входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу (3) устройства, причем коллектор первого (8) входного транзистора согласован с первой (2) шиной источника питания, а коллектор второго (9) входного транзистора подключен ко второй (6) шине источника питания, источник вспомогательного напряжения (10), связанный с базами первого (8) и второго (9) входных транзисторов, отличающийся тем, что в схему введены первый (11), второй (12), третий (13) и четвертый (14) дополнительные транзисторы, причем второй (4) источник входного логического тока включен между объединенными эмиттерами первого (11) и второго (12) дополнительных транзисторов и второй (6) шиной источника питания, первый (15) дополнительный источник входного логического тока, соответствующий второй логической переменной "х", устанавливающей уровень ограничения выходного тока устройства, включен между объединенными эмиттерами третьего (13) и четвертого (14) дополнительных транзисторов и второй (6) шиной источника питания, коллекторы второго (12) и третьего (13) дополнительных транзисторов объединены и связаны с первым (7) токовым выходом устройства, коллекторы первого (11) и четвертого (14) дополнительных транзисторов объединены и подключены ко второму (16) дополнительному токовому выходу устройства, базы первого (11) и третьего (13) дополнительных транзисторов объединены и подключены к токовому входу (3) устройства, базы второго (12) и четвертого (14) дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения (10).