Результат интеллектуальной деятельности: ОБЕСПЕЧЕНИЕ ОЧЕРЕДИ КОМАНД ВО ВСТРОЕННОЙ ПАМЯТИ

Вид РИД

Изобретение

ПРИТЯЗАНИЕ НА ПРИОРИТЕТ

[0001] Настоящая заявка испрашивает приоритет на основе предварительной заявки на патент США № 61/875,721, поданной 10 сентября 2013 и озаглавленной «SYSTEMS AND METHODS FOR PROVIDING COMMAND QUEUING IN THE EMBEDDED MULTI-MEDIA CONTROLLER (eMMC) STANDARD» («СИСТЕМЫ И СПОСОБЫ ДЛЯ ОБЕСПЕЧЕНИЯ ОЧЕРЕДИ КОМАНД В СТАНДАРТЕ «ВСТРОЕННЫЙ МУЛЬТИМЕДИЙНЫЙ КОНТРОЛЛЕР» (eMMC))», которая включена в настоящий документ по ссылке во всей своей полноте.

[0002] Настоящая заявка также испрашивает приоритет на основе заявки на патент США № 14/478,032, поданной 5 сентября 2014 и озаглавленной «PROVIDING COMMAND QUEUING IN EMBEDDED MEMORIES» («ОБЕСПЕЧЕНИЕ ОЧЕРЕДИ КОМАНД ВО ВСТРОЕННОЙ ПАМЯТИ»), которая включена в настоящий документ по ссылке во всей своей полноте.

УРОВЕНЬ ТЕХНИКИ

I. Область техники, к которой относится изобретение

[0003] Технология раскрытия относится, в целом, к встроенной памяти и, в частности, к обеспечению очереди команд для нее.

II. Уровень техники

[0004] Многие мобильные устройства полагаются на флэш-память для хранения данных и/или программного обеспечения для использования мобильным устройством. Флэш-память имеет две основные разновидности: фиксированная (встроенная) и съемная. Съемная флэш-память обычно имеет форму съемной карты памяти и обычно используется в таких устройствах, как цифровые камеры или аудиоустройства. Встроенная флэш-память, как правило, припаяна или иным образом постоянно крепится к плате или другому опорному носителю в мобильном устройстве.

[0005] Объединенный инженерный совет по электронным устройствам (JEDEC) отвечает за создание стандартов «Встроенная мультимедийная карта» (eMMC), относящихся к одному типу встроенной флэш-памяти. eMMC описывает архитектуру, состоящую из решения для встроенного накопителя с интерфейсом мультимедийной карты, флэш-памятью и контроллером, все это в небольшом корпусе с массивом шариковых выводов (BGA). eMMC является в настоящее время синхронным протоколом, в котором хост отправляет команду на чтение из устройства или запись в устройство. Устройство отправляет ответ, а затем происходит передача блока данных. По завершении передачи данных хост отправляет другую команду, принимает другой ответ, и происходит другая передача данных. Эта синхронная структура команд имеет место для каждой передачи данных в и из памяти eMMC. Как правило, программное обеспечение участвует в каждой команде и ответе. Такое программное обеспечение, как правило, является медленно реагирующим объектом, и участие программного обеспечения в каждой команде и ответе добавляет задержку при совершении передачи данных.

[0006] В отличие от синхронной структуры команд eMMC другой стандарт памяти, универсальная флеш-память (UFS), использует хорошо известные модель архитектуры и протоколы команд интерфейса малых компьютерных систем (SCSI), поддерживающие несколько команд с функциями очереди команд и позволяющие использовать парадигму многопоточного программирования. На практике очередь команд позволяет хосту отправлять множество задач устройству до выполнения этих задач устройством. Эти задачи сохраняются в очереди в устройстве. Устройство затем выбирает задачу из множества задач, которые оно приняло, исполняет выбранную задачу и сообщает хосту о завершении.

[0007] Очередь команд позволяет более эффективно использовать шину, по которой происходит передача данных, потому что программное обеспечение в хосте и устройстве может работать одновременно, а не ждать друг друга. eMMC мог бы извлечь пользу из очереди команд и улучшения эффективности использования шины данных. Однако, учитывая, что в eMMC исторически не предусмотрена очередь команд, существует потребность определить, как хост может узнать о статусе задач в очереди в устройстве.

Сущность изобретения

[0008] Аспекты, раскрытые в подробном описании, включают в себя обеспечение очереди команд во встроенной памяти. В частности, аспекты, раскрытые в настоящем документе, относятся к процессу, посредством которого статус очереди передается хосту от устройства. Аспекты настоящего раскрытия используют структуру команд стандарта «Встроенная мультимедийная карта» (eMMC), так что хост может определить состояние очереди в устройстве вблизи от известного конца выполняющейся передачи данных. Таким образом, хост может выбрать задачу для начала после завершения текущей передачи данных, пока текущая передача данных все еще продолжается.

[0009] С связи с этим в одном аспекте раскрывается хост. Хост содержит приемопередатчик, выполненный с возможностью передачи сигналов и приема сигналов от устройства, совместимого со стандартом eMMC. Хост также содержит систему управления, функционально связанную с приемопередатчиком. Система управления выполнена с возможностью давать команду устройству определить состояние регистра статуса очереди (QSR) в устройстве. Система управления также выполнена с возможностью приема ответа от устройства с информацией о QSR устройства.

[0010] В другом аспекте раскрывается устройство. Устройство содержит приемопередатчик, выполненный с возможностью передачи сигналов и приема сигналов от хоста, совместимого со стандартом eMMC. Устройство также содержит систему управления, функционально связанную с приемопередатчиком. Система управления выполнена с возможностью приема команды от хоста определить состояние QSR в устройстве. Система управления дополнительно выполнена с возможностью передачи ответа хосту с информацией о QSR устройства.

[0011] В другом аспекте раскрывается способ функционирования хоста eMMC. Способ содержит этап, на котором передают сигналы от хоста eMMC устройству, включающие в себя команду определить состояние QSR в устройстве. Способ также содержит этап, на котором принимают ответ от устройства с информацией о QSR устройства.

Краткое описание чертежей

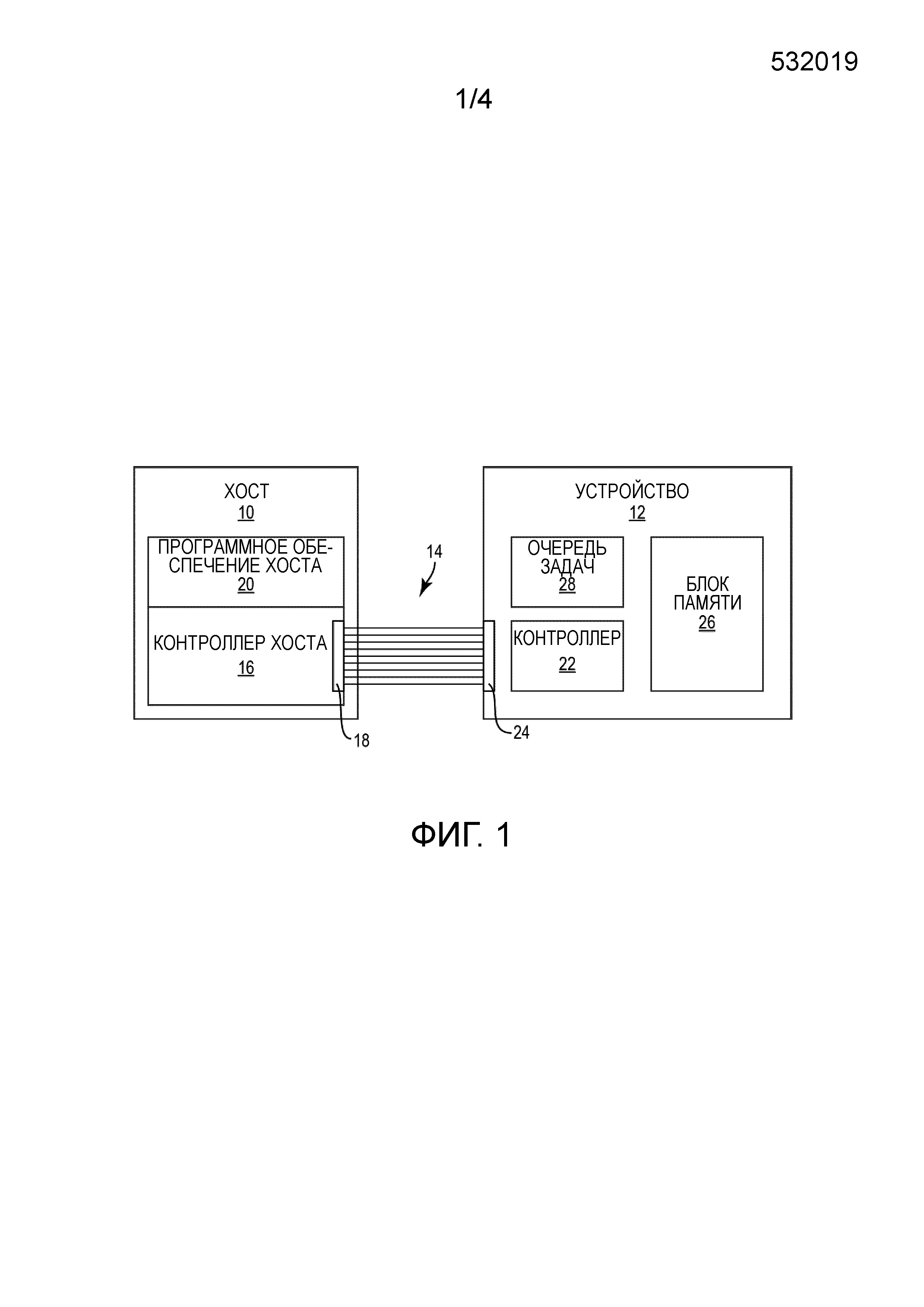

[0012] Фигура 1 является блок-схемой иллюстративного соединения между хостом и устройством с использованием стандарта «Встроенная мультимедийная карта» (eMMC);

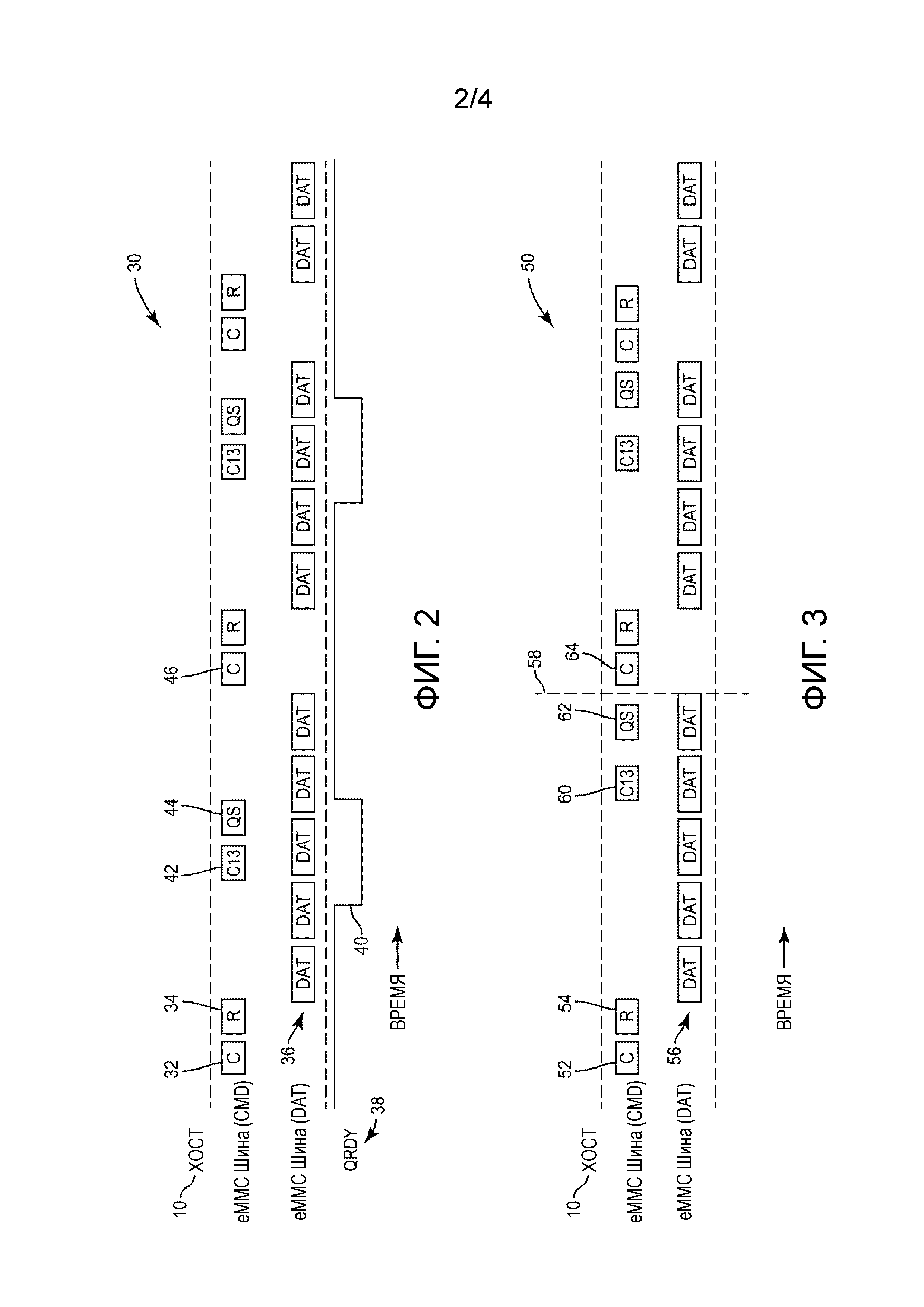

[0013] фигура 2 является временной диаграммой сигналов между хостом и устройством с использованием контакта прерывания;

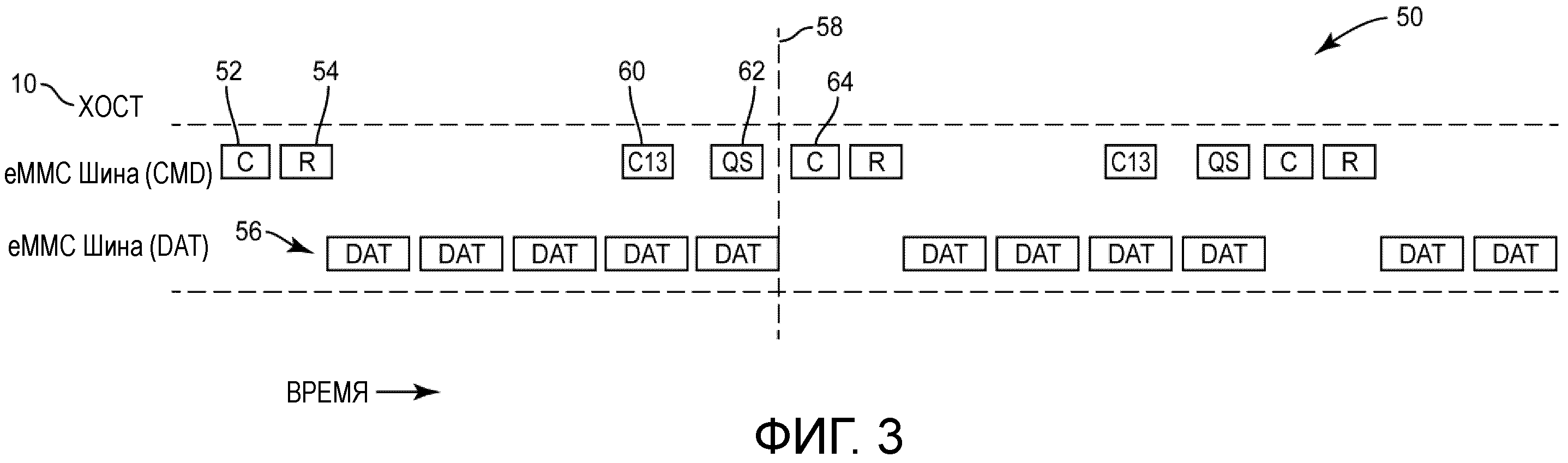

[0014] фигура 3 является временной диаграммой сигналов между хостом и устройством с использованием структуры команды в соответствии с иллюстративными аспектами настоящего раскрытия;

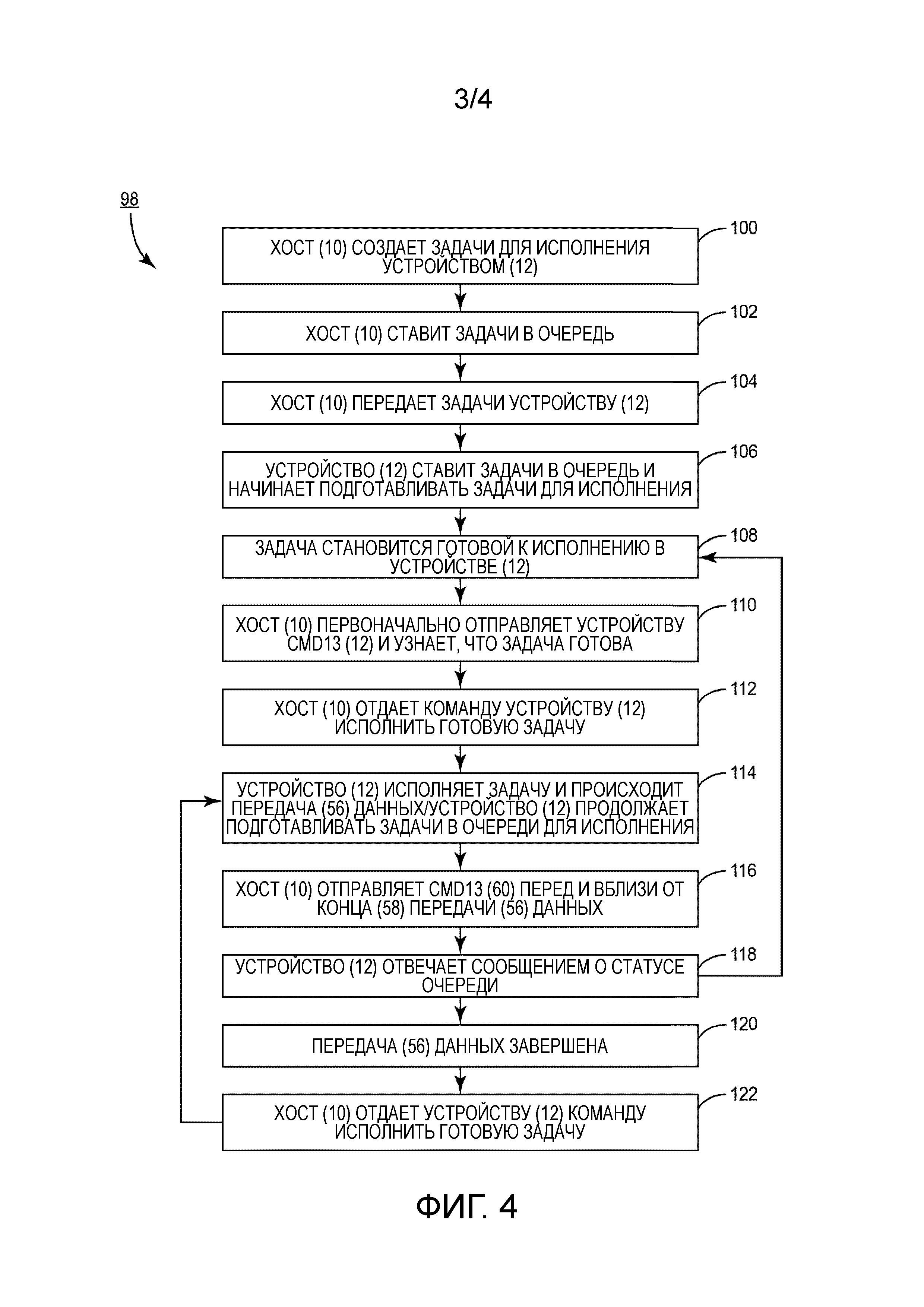

[0015] фигура 4 является блок-схемой последовательности операций иллюстративного процесса настоящего раскрытия и

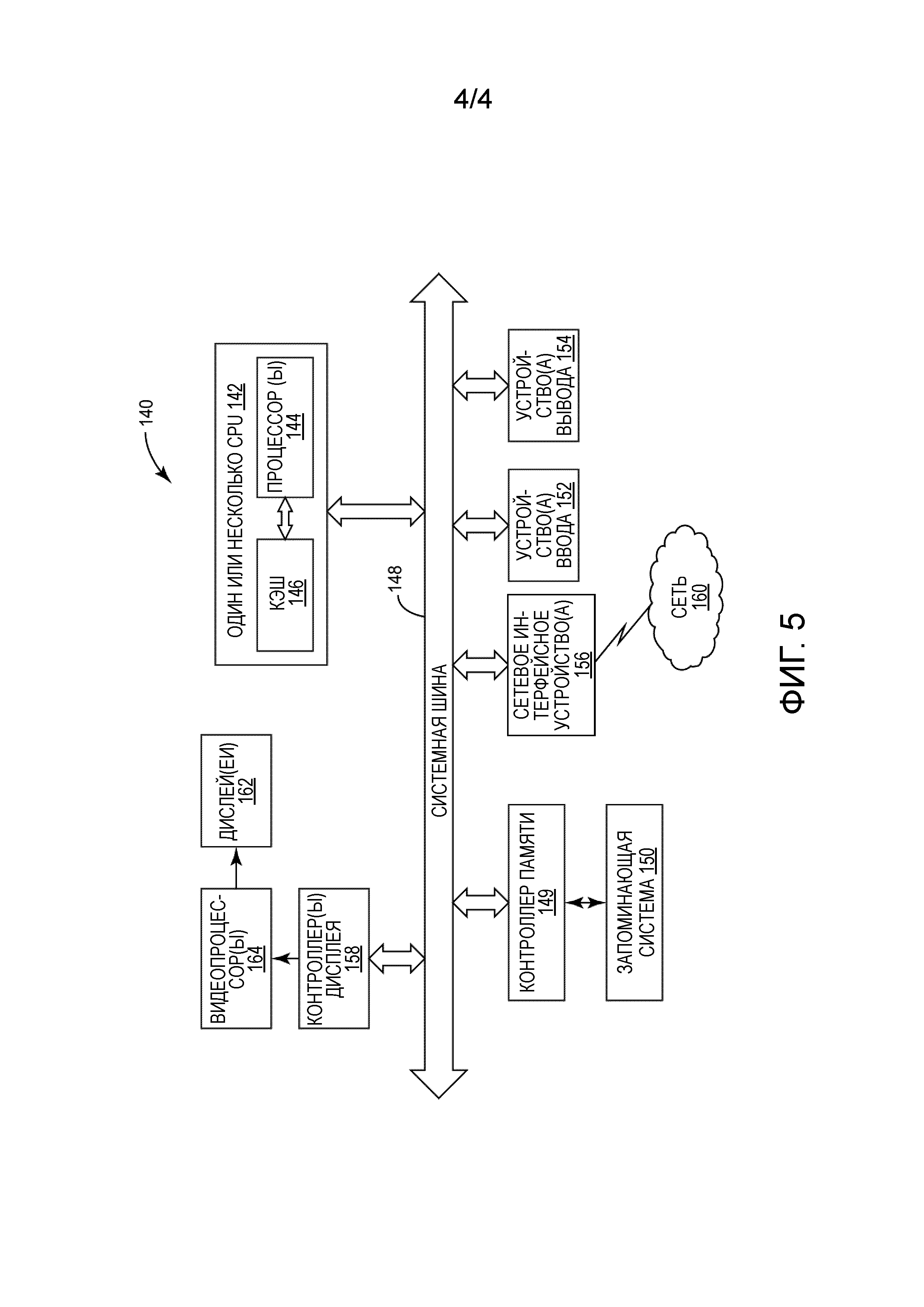

[0016] фигура 5 является блок-схемой иллюстративной системы на основе процессора, которая может включать в себя хост и устройство фигуры 1, функционирующие в соответствии с аспектами настоящего раскрытия.

Подробное описание

[0017] Теперь со ссылкой на чертежи будут описаны несколько иллюстративных аспектов настоящего раскрытия. Слово «иллюстративный» в настоящем документе означает «служащий в качестве примера, образца или иллюстрации». Любой аспект, описанный в настоящем документе как «иллюстративный», не обязательно должен толковаться как предпочтительный или полезный по сравнению с другими аспектами.

[0018] Аспекты, раскрытые в подробном описании, включают в себя обеспечение организации очередей команд во встроенных запоминающих устройствах. В частности, аспекты, раскрытые в настоящем документе, относятся к процессу, посредством которого статус очереди передается хосту от устройства. Аспекты настоящего раскрытия используют структуру команд стандарта «Встроенная мультимедийная карта» (eMMC), так что хост может определить состояние очереди в устройстве вблизи от известного конца выполняющейся передачи данных. Таким образом, хост может выбрать задачу для начала после завершения текущей передачи данных, пока текущая передача данных все еще продолжается.

[0019] Когда хост создает задачу, он априорно знает, сколько данных будет передано. Учитывая, что хост также инструктирует устройство, когда начать передачу данных, хост может определить, когда передача данных, ассоциированная с конкретной задачей, будет близка к завершению. Соответственно хост может запланировать опрашивающий запрос в некоторый момент до завершения передачи данных. В иллюстративном аспекте опрашивающий запрос имеет вид сигнала команды SEND_QUEUE_STATUS (CMD13) от хоста устройству. Устройство отвечает информацией о статусе очереди. Хост затем имеет достаточно информации относительно того, какие задачи в очереди готовы к выполнению. В конце текущей передачи данных хост может дать команду на исполнение новой задачи. Такая конструкция позволяет избежать необходимости в дополнительном контакте. Избегание дополнительных контактов экономит место и стоимость. Аналогично, эта конструкция сокращает число опрашивающих запросов путем привязки события опроса к близкому концу передачи данных вместо того, чтобы полагаться на периодический опрос. То есть если опрос делается периодически, хост может совершить опрос дважды (или более) во время одной передачи данных. В противоположность этому настоящее раскрытие имеет только одно событие опроса в течение одной передачи данных (вблизи от конца передачи данных). Устранение дополнительного опроса обеспечивает более эффективное использование шины данных.

[0020] Добавление очереди команд в системе eMMC позволяет устройству оптимизировать порядок выполнения. Такая оптимизация может увеличить время работы от батареи и/или устранить задержку при выполнении задач. Очередь команд обеспечивает уведомление хоста устройством о текущем статусе очереди и улучшает обработку ошибок. Кроме того, очередь команд улучшает аспекты синхронизации для команд.

[0021] В связи с этим фигура 1 является блок-схемой хоста 10, соединенного с устройством 12 через проводники 14. Связи между хостом 10 и устройством 12 соответствуют стандарту eMMC, такому как электрический стандарт 5.0 eMMC, опубликованный объединенным инженерным советом по электронным устройствам (JEDEC) в июне 2012. Версия 5.01 была опубликована в июле 2014. В настоящее время ведется работа по завершению версии 5.1 с ориентировочной публикацией в декабре 2014. Копии этого стандарта доступны в JEDEC по адресу 3103 North 10th Street, Suite 240 South, Arlington VA 22201-2107. Хост 10 включает в себя контроллер 16 хоста, который является основанной на аппаратном обеспечении системой с соответствующим интерфейсом 18 связи. Контроллер 16 хоста взаимодействует с программным обеспечением 20 хоста. В совокупности контроллер 16 хоста и программное обеспечение 20 хоста являются системой управления.

[0022] С дальнейшей ссылкой на фигуру 1 устройство 12 включает в себя контроллер 22, который является основанной на аппаратном обеспечении системой с соответствующим интерфейсом 24 связи. Устройство 12 дополнительно включает в себя блок 26 памяти (например, устройство флэш-памяти типа ОТРИЦАНИЕ И или НЕ И (NAND)). Устройство 12 дополнительно включает в себя очередь 28 задач. В совокупности контроллер 22 и любое программное обеспечение и микропрограммное обеспечение, ассоциированное с работой контроллера 22, являются системой управления.

[0023] Имело место совместное предложение Samsung, SanDisk и Qualcomm для JEDEC включить постановку команд в очередь посредством контакта QRDY. Использование такого контакта QRDY может позволить постановку команд в очередь, но может увеличить затраты и/или ухудшить пространственные характеристики. Тем не менее, для помощи в сравнении аспектов настоящего раскрытия аспекты контакта QRDY приведены на фигуре 2. В частности, фигура 2 обеспечивает прогрессирование сигнала как функцию времени 30 для контакта QRDY.

[0024] В связи с этим фигура 2 изображает временную диаграмму. В частности, хост 10 отправляет команду 32 (C) и принимает ответ (R) 34. Команда 32 инструктирует устройство 12 начать выполнение задачи в очереди в устройстве 12. После ответа 34 начинается передача 36 данных. Пока происходит передача 36 данных, устройство 12 завершает подготовку задачи в очереди 28 задач для выполнения. Контакт 38 QRDY переводится из состояния высокого уровня в состояние низкого уровня (см. переход 40). Изменение уровня контакта 38 QRDY заставляет хост 10 отправить команду 42 устройству 12. В иллюстративном аспекте команда 42 является CMD13. Устройство 12 отправляет обратно ответ 44, который может включать в себя состояние очереди (QS), включающее в себя вновь подготовленную задачу. В конце передачи 36 данных хост отправляет новую команду 46, инструктирующую устройство 12 начать выполнение одной из подготовленных задач в очереди 28 задач. Использование контакта 38 QRDY позволяет хосту 10 знать, когда задачи готовы к выполнению. Хост 10 может дать соответствующие команды на выполнение в конце существующей передачи данных вместо того, чтобы ожидать конца передачи данных, запросить состояние очереди в конце потока данных и затем дать команду выполнения задания после запроса.

[0025] Хотя добавление контакта 38 QRDY обеспечивает очередь команд и соответствующую экономию времени и эффективное использование шины данных, добавление контакта увеличивает расходы на производство и ухудшает конструктивные характеристики, поскольку к новому контакту должен быть проведен дополнительный проводник. Кроме того, добавление контакта увеличивает габариты устройства и хоста с контактом относительно аналогичного устройства (и хоста) без дополнительного контакта. Таким образом, добавление контакта 38 QRDY является, в целом, нежелательным.

[0026] Аспекты настоящего раскрытия позволяют избежать использования контакта 38 QRDY путем использования знания, которое имеет хост 10 относительно активной в настоящий момент передачи данных, в связке с CMD13, чтобы обеспечить своевременное обновление статуса очереди в устройстве 12. Дополнительные регистры могут быть добавлены в предназначенном для производителя диапазоне карты регистров интерфейса хост-контроллера (HCI), чтобы помочь обеспечить процессы настоящего раскрытия. Перед рассмотрением добавленных регистров представлено общее описание процесса.

[0027] В связи с этим фигура 3 изображает прогрессирование сигнала как функцию времени 50. Сигналы начинаются с того, что хост 10 отправляет команду 52 устройству 12 и принимает ответ 54. Команда 52 инструктирует устройство 12 исполнить готовую задачу. Устройство 12 исполняет готовую задачу, и начинается передача 56 данных. Хост 10 априорно знает, сколько данных будет передано как часть передачи 56 данных, и, таким образом, знает (или может вычислить), когда наступит конец 58 передачи 56 данных. Таким образом, учитывая, что система управления хоста 10 может знать, когда наступит конец 58 передачи 56 данных, система управления хоста 10 может выбрать время до, но вблизи от конца 58. Система управления хоста 10 отправляет CMD13 60 устройству 12 в это выбранное время. CMD13 60 включает в себя запрос относительно состояния очереди 28 задач. Устройство 12 отвечает сигналом 62 QS, который имеет информацию о состоянии очереди 28 задач, включающую в себя информацию обо всех задачах, которые готовы к выполнению. На основании готовых задач хост 10 затем дает команду 64 исполнить задачу, и процесс повторяется.

[0028] Более ясная блок-схема последовательности операций процесса 98, стоящего за прогрессированием сигнала как функцией времени 50, представлена со ссылкой на фигуру 4. Процесс 98 начинается с того, что хост 10 создает одну или несколько задач для исполнения устройством 12 (блок 100). Хост 10 ставит задачи в очередь (блок 102) и передает одну или несколько задач устройству 12 (блок 104) с командой для постановки одной или нескольких задач в очередь. Устройство 12 ставит задачи в очередь и начинает подготавливать задачи для выполнения (блок 106). В некоторый момент устройство 12 завершает подготовку одной или нескольких задач для выполнения (блок 108), и устройство 12 обновляет очередь 28 задач.

[0029] Первоначально хост 10 отправляет CMD13 устройству 12 и узнает, что задача готова (блок 110). Хост 10 отдает команду устройству 12 исполнить готовую задачу (блок 112). Устройство 12 исполняет задачу, и происходит передача 56 данных. В то же время устройство 12 продолжает подготавливать задачи в очереди для исполнения (блок 114). Одна или несколько дополнительных задач могут быть подготовлены таким образом.

[0030] Хост 10 на основании его априорного знания того, когда наступит конец 58 передачи 56 данных, отправляет CMD13 60 до, но вблизи от конца 58 передачи 56 данных (блок 116). Устройство 12 отвечает сообщением о статусе очереди (блок 118), включающим в себя любые задачи, которые стали готовыми к исполнению со времени последнего обновления, предоставленного хосту 10. Если задачи, готовые к исполнению в блоке 118, отсутствуют, система возвращается к блоку 108 и выполняет периодический опрос до тех пор, пока задача не станет готова. Однако если имеется задача, готовая к исполнению, передача 56 данных завершается (блок 120), и хост 10 отправляет команду (CMD46 или CMD47) 64 устройству 12 для исполнения готовой задачи (блок 122). Процесс 98 затем повторяется, как отмечалось, с выполнением устройством 12 задачи.

[0031] Как отмечалось выше, ряд регистров может быть включен в качестве организации очереди команд HCI. Эти регистры приведены в Таблице 1 ниже.

|

[0032] Хотя эти регистры описываются подробно в первичной предварительной заявке, особенный интерес представляет поле «Таймер простоя команды отправки статуса» регистра «Конфигурация 1 отправки статуса», которое позволяет контроллеру 16 хоста знать период времени, через который необходимо опросить устройство 12 с использованием команды STATUS, чтобы проверить статус очереди команд. Периодический опрос используется, когда задачи ожидают обработки в устройстве 12, но не происходит никакой передачи данных. Дополнительно следует отметить, что в различных реализациях различные регистры могут иметь различные названиями (например, «Конфигурация 1 отправки статуса очереди команд»), не отступая от объема настоящего раскрытия.

[0033] Также особенный интерес представляет поле «Счетчик блока команды отправки статуса» регистра «Конфигурация 1 отправки статуса», которое указывает контроллеру 16 хоста, в каком блоке отправлять команду STATUS, чтобы проверить статус очереди команд. Хост 10 отправит команду статуса BLOCK_CNT-1 блоков перед концом передачи.

[0034] Хотя это не показано, система управления может выдать запрос управления очередью, который может включать в себя команду удалить задачу.

[0035] Системы и способы для обеспечения очереди команд в стандарте eMMC в соответствии с аспектами, раскрытыми в настоящем документе, могут быть обеспечены или интегрированы в любое устройство на основе процессора. Примеры, без ограничения, включают в себя телеприставку, развлекательный блок, навигационное устройство, устройство связи, блок данных с фиксированным местоположением, блок данных с мобильным местоположением, мобильный телефон, сотовый телефон, компьютер, портативный компьютер, настольный компьютер, карманный персональный компьютер (PDA), монитор, компьютерный монитор, телевизор, тюнер, радио, спутниковое радио, аудиоплеер, цифровой аудиоплеер, портативный аудиоплеер, цифровой видеоплеер, видеоплеер, проигрыватель цифровых видеодисков (DVD) и портативный цифровой видеоплеер.

[0036] С связи с этим фигура 5 изображает пример системы 140 на основе процессора, которая может использовать хост 10 и устройство 12, изображенные на фигуре 1. В этом примере система 140 на основе процессора включает в себя один или несколько центральных блоков обработки (CPU) 142, каждый из которых включает в себя один или несколько процессоров 144. Один или несколько CPU 142 могут быть ведущим устройством и выполнять программное обеспечение 20. Один или несколько CPU 142 могут иметь кэш-память 146, соединенную с процессором(ами) 144 для быстрого доступа к временно сохраненным данным. Один или несколько CPU 142 соединены с системной шиной 148 и могут соединять между собой устройства, входящие в состав системы 140 на основе процессора. Как известно, один или несколько CPU 142 осуществляют связь с этими другими устройствами путем обмена информацией об адресах, управляющей информацией и информацией в виде данных по системной шине 148. Например, один или несколько CPU 142 могут посылать запросы транзакций шины запоминающей системе 150, которая может быть устройством 12. Запросы транзакций могут проходить через контроллер 149 памяти, который может быть контроллером 16 хоста. Хотя это не изображено на фигуре 5, может быть обеспечено несколько системных шин 148, при этом каждая системная шина 148 представляет собой различную структуру.

[0037] С системной шиной 148 могут быть соединены другие устройства. Как изображено на фигуре 5, эти устройства могут включать в себя запоминающую систему 150, одно или несколько устройств 152 ввода, одно или несколько устройств 154 вывода, одно или несколько сетевых интерфейсных устройств 156 и один или несколько контроллеров 158 дисплея в качестве примеров. Устройство(а) 152 ввода может включать в себя любой тип устройства ввода, в том числе, но не ограничиваясь только этим, клавиши ввода, переключатели, речевые процессоры и т.д. Устройство(а) 154 вывода может включать в себя любой тип устройства вывода, в том числе, но не ограничиваясь только этим, аудио, видео, другие визуальные индикаторы и т.д. Сетевое интерфейсное устройство(а) 156 может быть любыми устройствами, выполненными с возможностью осуществлять обмен данными с сетью 160. Сеть 160 может быть любым типом сети, в том числе, но не ограничиваясь только этим, проводной или беспроводной сетью, частной или общедоступной сетью, локальной сетью (LAN), глобальной LAN, беспроводной LAN и Интернетом. Сетевое интерфейсное устройство(а) 156 может быть выполнено с возможностью поддержки любого желаемого типа протокола связи.

[0038] Один или несколько CPU 142 также могут быть выполнены с возможностью осуществления доступа к контроллеру(ам) 158 дисплея по системной шине 148 для управления информацией, посылаемой одному или нескольким дисплеям 162. Контроллер(ы) 158 дисплея посылает информацию дисплею(ям) 162 для отображения с помощью одного или нескольких видеопроцессоров 164, которые преобразовывают информацию, которая должна быть отображена, в формат, подходящий для дисплея(ев) 162. Дисплей(и) 162 может включать в себя любой тип дисплея, в том числе, но не ограничиваясь только этим, электронно-лучевую трубку (CRT), дисплей на светодиодах (LED), жидкокристаллический дисплей (LCD), плазменный дисплей и т.д.

[0039] Специалистам в данной области техники также будет понятно, что различные иллюстративные логические блоки, модули, электрические схемы и алгоритмы, описанные применительно к аспектам, раскрытым в настоящем документе, могут быть реализованы как электронное аппаратное обеспечение, инструкции, сохраненные в памяти или в другом компьютерно-читаемом носителе и выполняемые процессором, другим устройством обработки или их комбинациями. Хосты и устройства, описанные в настоящем документе, могут использоваться, например, в любой электрической схеме, компоненте аппаратного обеспечения, интегральной схеме (IC) или кристалле IC. Память, раскрытая в настоящем документе, может быть памятью любого типа и размера, и она может быть выполнена с возможностью хранения любого типа желаемой информации. Чтобы ясно проиллюстрировать эту взаимозаменяемость, различные иллюстративные компоненты, блоки, модули, электрические схемы и этапы были описаны выше в целом с точки зрения их функциональности. То, как такая функциональность реализуется, зависит от конкретного применения, конструктивных решений и/или конструктивных ограничений, наложенных на систему в целом. Специалисты в данной области техники могут реализовать описанную функциональность различным образом для каждого конкретного применения, но такие решения по реализации не должны интерпретироваться как отклонения от объема настоящего раскрытия.

[0040] Различные иллюстративные логические блоки, модули и электрические схемы, описанные применительно к аспектам, раскрытым в настоящем документе, могут быть реализованы или выполнены с помощью процессора, цифрового сигнального процессора (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства, логического элемента на дискретных компонентах или транзисторных логических схемах, дискретных компонентах аппаратного обеспечения или любой их комбинации, предназначенной для выполнения функций, описанных в настоящем документе. Процессор может быть микропроцессором, но в альтернативном варианте процессор может быть любым традиционным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор может также быть реализован как комбинация вычислительных устройств, например комбинация DSP и микропроцессора, множества микропроцессоров, одного или нескольких микропроцессоров в сочетании с DSP-ядром или любая другая такая конфигурация.

[0041] Аспекты, раскрытые в настоящем документе, могут быть воплощены в аппаратном обеспечении и в инструкциях, которые сохранены в аппаратном обеспечении, и могут находиться, например, в оперативном запоминающее устройстве (RAM), флэш-памяти, постоянном запоминающем устройстве (ROM), электрически программируемом ROM (EPROM), электрически стираемом программируемом ROM (EEPROМ), регистрах, жестком диске, съемном диске, CD-ROM или любой другой форме компьютерно-читаемого носителя, известного в данной области техники. Иллюстративный накопитель данных соединен с процессором, так что процессор может считывать и записывать информацию в накопитель данных. В качестве альтернативы, накопитель данных может являться неотъемлемой частью процессора. Процессор и накопитель данных могут находиться в ASIC. ASIC может находиться в удаленной станции. В альтернативном варианте процессор и накопитель данных могут находиться как дискретные компоненты в удаленной станции, базовой станции или сервере.

[0042] Также следует отметить, что операционные этапы, описанные в любом из иллюстративных аспектов в настоящем документе, описываются для того, чтобы обеспечить примеры и обсуждение. Описанные операции могут выполняться в различных последовательностях, отличных от изображенных последовательностей. Кроме того, операции, описанные в одном операционном этапе, могут фактически выполняться в нескольких различных этапах. Дополнительно, один или несколько операционных этапов, обсуждаемых в иллюстративных аспектах, могут комбинироваться. Следует понимать, что операционные этапы, проиллюстрированные в схемах последовательности операций, могут быть подвергнуты многочисленным различным модификациям, как будет очевидно для специалиста в данной области техники. Специалистам в данной области техники также будет понятно, что информация и сигналы могут быть представлены с использованием любой из множества различных технологий и методик. Например, данные, инструкции, команды, информация, сигналы, биты, символы и элементарные сигналы, которые могут упоминаться на всем протяжении описания, могут быть представлены напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами или любой их комбинацией.

[0043] Предшествующее описание раскрытия обеспечено для того, чтобы позволить любому специалисту в данной области техники сделать или использовать раскрытие. Различные модификации раскрытия будут с легкостью очевидны для специалистов в данной области техники, а общие принципы, определенные в настоящем документе, могут быть применены к другим вариантам, не отступая от сущности или объема раскрытия. Таким образом, это раскрытие не должно ограничиваться примерами и конструкциями, описанными в настоящем документе, а должно соответствовать самому широкому объему, согласующемуся с принципами и новыми признаками, раскрытыми в настоящем документе.