Результат интеллектуальной деятельности: СТРУКТУРА МЕТАЛЛИЧЕСКИХ ДОРОЖЕК ПОДЛОЖКИ МАТРИЦЫ

Вид РИД

Изобретение

Область техники

Настоящее изобретение обносится к технической области жидкокристаллических дисплеев и, в частности, к структуре металлических дорожек подложки матрицы.

Предпосылки для создания изобретения

С развитием информационного общества спрос на дисплейное оборудование постоянно возрастает и, таким образом, способствует быстрому развитию производства жидкокристаллических панелей. Соответственно возрастает спрос на количество и качество дисплеев при повышающихся требованиях к конструкции и производительности.

Обычно структура металлических дорожек необходимо для линий отверждения при подготовке подложки матрицы для жидкокристаллического дисплея на тонкопленочных транзисторах (TFT LCD), выполняемой посредством метода вертикального выравнивания с полимерной стабилизацией (PSVA). С помощью такой структуры металлических дорожек площадка для проверки матрицы, которая используется для электрического контроля зондов в панели после завершения процесса изготовления подложки матрицы, может быть соединена с площадкой отверждения, которая используется для отверждения зондов жидкокристаллической панели. Обычно число линий шины для проверки матрицы равно числу линий шины отверждения при соответствии один к одному. В этом случае число периферических проводников в конструкции изделий должно быть увеличено из-за наличия дорожек отверждения, что приводит к рискам в отношении компоновки конструкции и объема выпуска.

Соответственно, в известном уровне техники предложена структура металлических дорожек для линий отверждения зондов, используемых при изготовлении подложки матрицы TFT LCD методом вертикального выравнивания с полимерной стабилизацией, в процессе изготовления жидкокристаллической панели с вертикальным выравниванием.

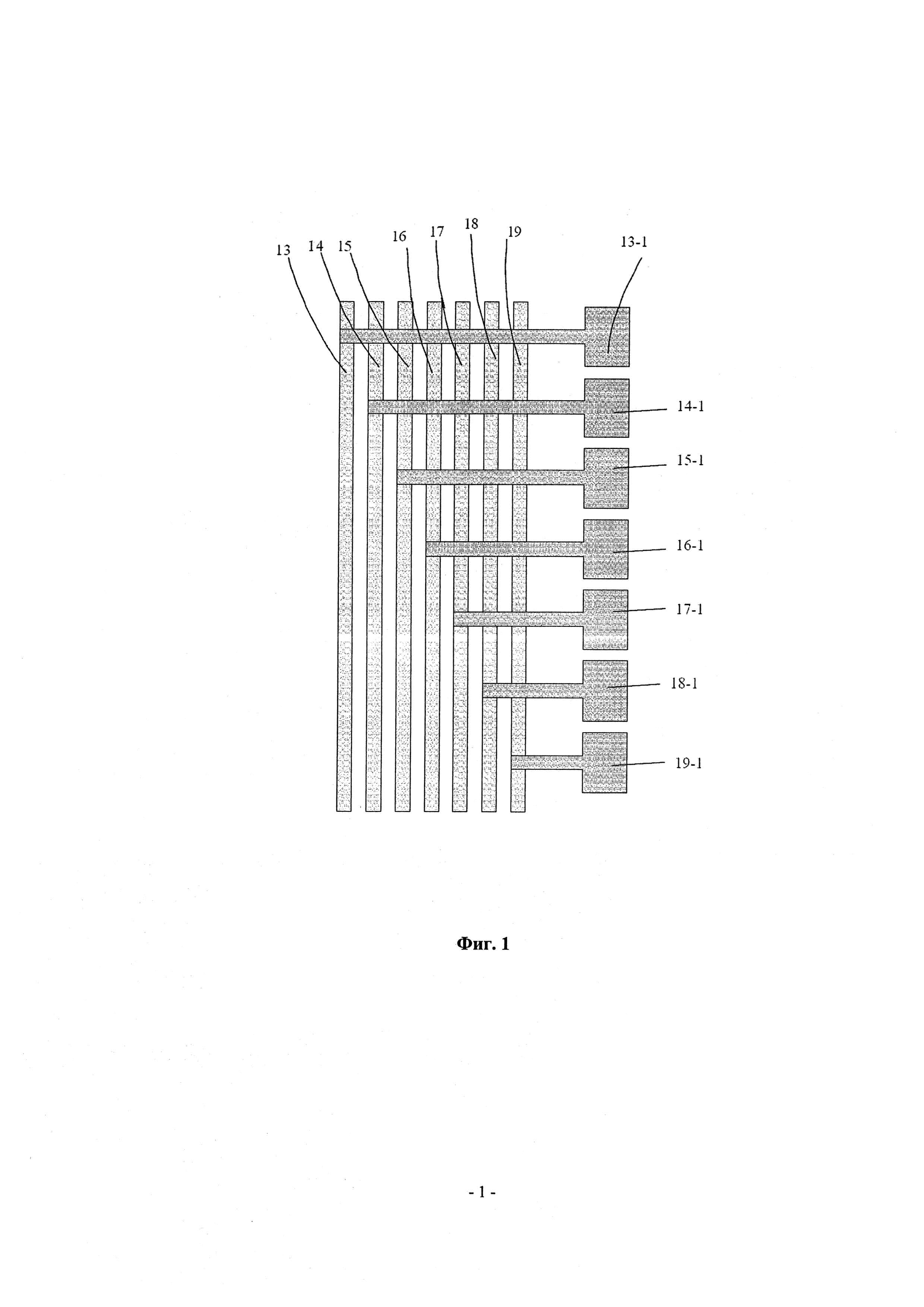

На Фиг. 1 показана структура металлических дорожек подложки матрицы из известного уровня техники. Со ссылкой на Фиг. 1, структура металлических дорожек подложки матрицы жидкокристаллической панели с вертикальным выравниванием из известного уровня техники включает линию красного 14, линю зеленого 15, линию синего 16, нечетную линию 17, четную линию 18, общую линию подложки матрицы 13 и общую линию подложки цветного фильтра 19, т.е. всего семь линий отверждения. При этом линия красного 14, линия зеленого 15 и линия синего 16 работают как линии данных во время процесса отверждения, а нечетная линия 17 и четная линия 18 работают как линии сканирования во время процесса отверждения. В известном уровне техники структура металлических дорожек жидкокристаллической панели с вертикальным выравниванием также включает семь соответствующих площадок отверждения и площадку для проверки подложки матрицы. Во время процесса отверждения, когда к площадке отверждения приложено напряжение, это напряжение затем подается на соответствующий конденсатор по соответствующей дорожке, а именно по одной из вышеуказанных семи линий, соединенных с упомянутой площадкой отверждения.

Таким образом, структура металлических дорожек жидкокристаллической панели с вертикальным выравниванием в известном уровне техники включает по меньшей мере семь дорожек для отверждения.

Обычно для того чтобы подать напряжение отверждения по общей линии 13 подложки матрицы на тонкопленочных транзисторах, требуется дополнительная площадка отверждения 13-1, которая должна быть электрически соединена с общей линией 13 каждого пикселя в области отображения пикселя подложки матрицы посредством дорожки. Таким образом, напряжение отверждения может быть подано на площадку отверждения 13-1, которая соединена с общей линией подложки матрицы 13 посредством этой дорожки. В конечном итоге напряжение передается на соответствующий запоминающий конденсатор каждого пикселя в области отображения пикселя.

Однако перед тем, как дорожка площадки отверждения 13-1 будет соединена с общей линией подложки матрицы 13, она может проходить через, над или вместе с другими дорожками. Например, дорожка площадки отверждения 13-1, которая показана на Фиг. 1, соединена с другими дорожками, чтобы сформировать область дорожек, что ведет к риску возникновения электронного статического разряда (ESD).

Можно видеть, что упомянутые семь дорожек занимают определенное пространство на подложке матрицы. Что касается стеклянной подложки фиксированного размера, то чем больше дорожек требуется, тем меньше места остается. Кроме того, если дорожек больше, то потребуется создать больше точек пересечения, что ведет к повышенному риску электронного статического разряда (ESD) в областях вокруг точек пересечения, а также к повышенному риску снижения объема выпуска изделий.

Будучи направленным на устранение вышеуказанных недостатков в известном уровне техники, настоящее изобретение улучшает структуру металлических дорожек подложки матрицы.

Раскрытие изобретения

Как сказано выше, в структуре металлических дорожек подложки матрицы в известном уровне техники семь дорожек будут занимать определенное место на подложке матрицы. Что касается стеклянной подложки фиксированного размера, то чем больше дорожек требуется, тем меньше места остается. Кроме того, если дорожек больше, то потребуется создать больше точек пересечения, что ведет к повышенному риску электронного статического разряда (ESD) в областях вокруг точек пересечения, а также ведет к повышенному риску снижения объема выпуска изделий.

Согласно настоящему изобретению на основе практического входного сигнала для зондов отверждения в жидкокристаллической панели с вертикальным выравниванием конструкция дорожек отверждения подложки матрицы жидкокристаллической панели с вертикальным выравниванием может быть улучшена и число дорожек отверждения может быть уменьшено, что поможет увеличить пространство для конструкции, снизить риск снижения объема выпуска и уменьшить число необходимых площадок отверждения. При этом число необходимых зондов отверждения в жидкокристаллической панели может быть уменьшено, таким образом снижая стоимость серийного производства.

Поэтому настоящее изобретение предлагает структуру металлических дорожек подложки матрицы.

Структура металлических дорожек подложки матрицы согласно настоящему изобретению включает объединенную линию RGB, служащую в качестве линий данных в процессе отверждения, объединенную линию ОЕ, служащую в качестве линий сканирования в процессе отверждения, общую линию подложки матрицы, общую линию подложки цветного фильтра, а также площадку отверждения RGB, площадку отверждения ОЕ, площадку отверждения подложки матрицы и площадку отверждения подложки цветного фильтра, которые соединены с объединенной линией RGB, объединенной линией ОЕ, общей линией подложки матрицы и общей линией подложки цветного фильтра соответственно и конфигурированы для получения соответствующих напряжений.

Таким образом, по сравнению с известным уровнем техники структура металлических дорожек согласно настоящему изобретению уменьшает число дорожек и площадок отверждения, что помогает уменьшить число периферических дорожек подложки матрицы, увеличить буферное пространство, увеличить буферное пространство для размещения конструкции и снизить риск возникновения производственных дефектов. При уменьшенном числе дорожек отверждения пространство для конструкции увеличивается, риск уменьшения объема выпуска снижается, число площадок отверждения уменьшается, и в то же время требуемое число зондов отверждения жидкокристаллической панели также снижается, что значительно снижает стоимость серийного производства.

Объединенная линия RGB предпочтительно включает линию красного, линию синего и линию зеленого, две соседние линии из линии красного, линии синего и линии зеленого соединены друг с другом посредством первого тонкопленочного транзистора, которые могут переключаться между включенным и отключенным состоянием под управлением затвора первого тонкопленочного транзистора, так что такие две соседние линии могут переключаться между короткозамкнутым и разъединенным состояниями. Соседние линии соединены посредством тонкопленочного транзистора, так что линией красного, линией синего и линией зеленого можно удобно, быстро и однообразно управлять, в результате чего снижается расход электроэнергии и повышается эффективность процесса отверждения.

Структура металлических дорожек предпочтительно также включает первую сигнальную линию, способную подавать сигнальное напряжение, при этом затвор первого тонкопленочного транзистора соединен с первой сигнальной линией. Первая сигнальная линия предназначена для управления первым тонкопленочным транзистором.

Линия красного и линия синего предпочтительно соединены друг с другом посредством первого тонкопленочного транзистора, и линия зеленого и линия синего соединены друг с другом посредством первого тонкопленочного транзистора.

Линия синего и линия красного предпочтительно соединены друг с другом посредством первого тонкопленочного транзистора, и линия зеленого и линия красного соединены друг с другом посредством первого тонкопленочного транзистора.

Линия синего и линия зеленого предпочтительно соединены друг с другом посредством первого тонкопленочного транзистора, и линия красного и линия зеленого соединены друг с другом посредством первого тонкопленочного транзистора.

Объединенная линия ОЕ предпочтительно включает нечетную линию и четную линию, соединенные друг с другом посредством второго тонкопленочного транзистора, и второй тонкопленочный транзистор может переключаться между включенным и отключенным состояниями под управлением затвора второго тонкопленочного транзистора, так что нечетная линия и четная линия могут переключаться между короткозамкнутым и разъединенным состояниями. Нечетная линия и четная линия соединены посредством тонкопленочного транзистора, так что нечетной линией и четной линией можно удобно, быстро и однообразно управлять, в результате чего снижается потребление электроэнергии и повышается эффективность процесса отверждения.

Структура металлических дорожек предпочтительно также включает вторую сигнальную линию, способную подавать сигнальное напряжение, и затвор второго тонкопленочного транзистора соединен с второй сигнальной линией. Вторая сигнальная линия предназначена для управления вторым тонкопленочным транзистором.

Структура металлических дорожек предпочтительно также включает по меньшей мере одну вспомогательную линию отверждения и одну вспомогательную площадку отверждения, соединенную с вспомогательной линией отверждения.

Предпочтительно, вспомогательная линия отверждения соединена с затворами первого тонкопленочного транзистора и второго тонкопленочного транзистора, и вспомогательная площадка отверждения предназначена для получения напряжений с затворов первого тонкопленочного транзистора и второго тонкопленочного транзистора. Посредством только одной вспомогательной линии отверждения линией красного, линией зеленого, линией синего, нечетной линией и четной линией можно удобно, быстро и однообразно управлять для их включения и отключения, в результате чего снижается потребление электроэнергии и повышается эффективность процесса отверждения.

При этом настоящее изобретение уменьшает число линий шины отверждения, улучшая известную конструкцию, что помогает уменьшить периферические дорожки подложки матрицы, увеличить буферное пространство для размещения конструкции и снизить риск возникновения производственных дефектов. С другой стороны, снижается число точек пересечения схем, и эффективно предотвращается риск возникновения электронного статического разряда (ESD) в точках пересечения.

Вышеописанные технические признаки могут быть объединены разным образом или заменены эквивалентными техническими признаками, если при этом достигается цель настоящего изобретения.

Краткое описание чертежей

Ниже настоящее изобретение будет описано более подробно на некоторых примерах со ссылками на прилагаемые чертежи. На чертежах:

Фиг. 1 - структура металлических дорожек подложки матрицы из известного уровня техники;

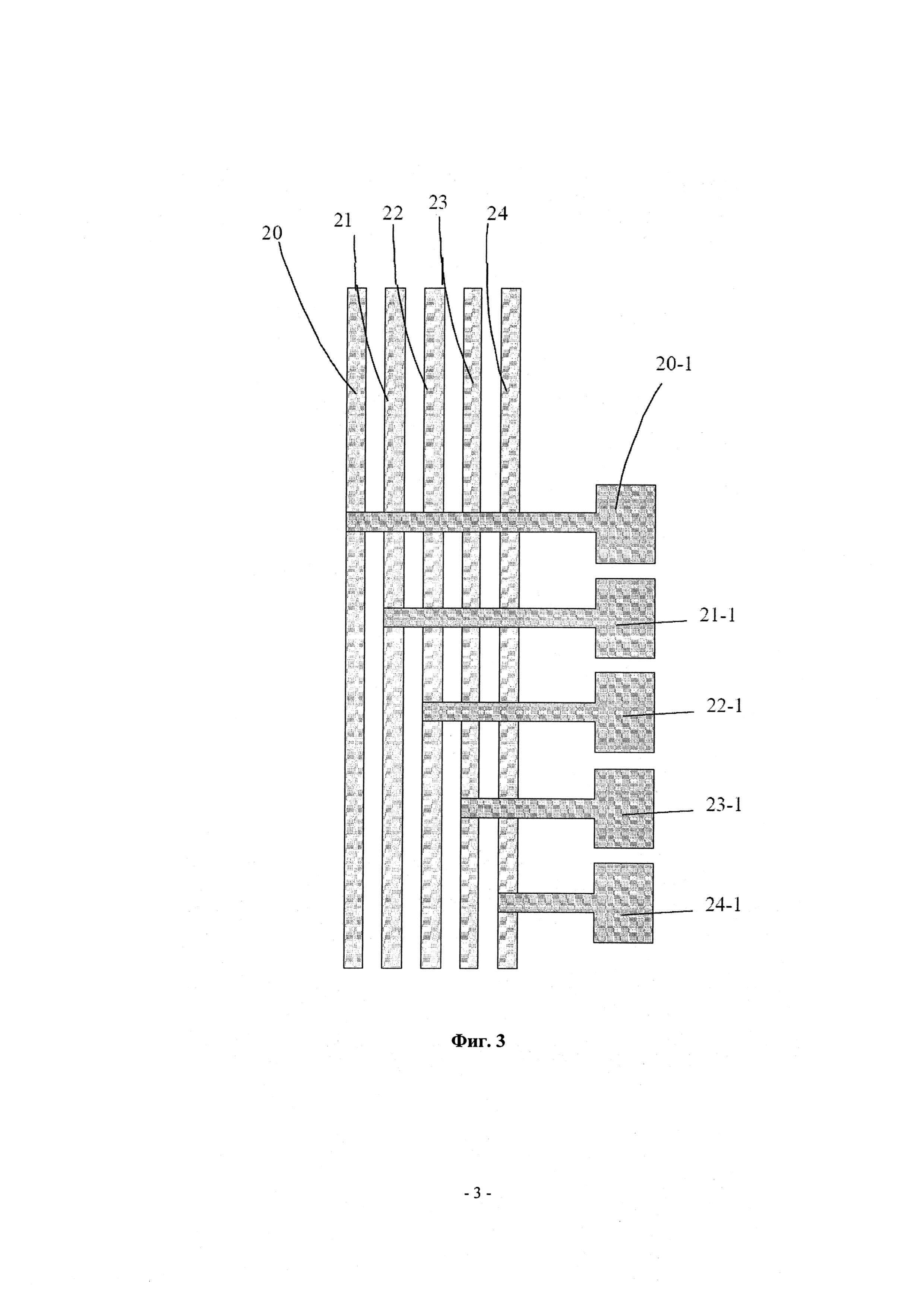

Фиг. 2 - расположение линии красного, линии зеленого, линии синего, нечетной линии и четной линии структуры металлических дорожек подложки матрицы из известного уровня техники;

Фиг. 3 - структура металлических дорожек подложки матрицы согласно настоящему изобретению;

Фиг. 4 - расположение объединенной линии RGB и объединенной линии ОЕ структуры металлических дорожек подложки матрицы согласно настоящему изобретению.

Одинаковые детали на чертежах обозначены одинаковыми ссылочными символами. Прилагаемые чертежи выполнены не по фактическому масштабу.

Подробное описание вариантов осуществления

Настоящее изобретение будет подробно описано ниже со ссылками на прилагаемые чертежи.

На Фиг. 2 показано расположение линии красного 14, линии зеленого 15, линии синего 16, нечетной линии 17 и четной линии 18 структуры металлических дорожек жидкокристаллической панели с вертикальным выравниванием, известной из уровня техники. Можно видеть, что в известном уровне техники линия красного 14, линия зеленого 15, линия синего 16, нечетная линия 17 и четная линия 18 получают соответствующие напряжения по отдельности как пять взаимно независимых линий.

Со ссылкой на Фиг. 2, в результате проведенного исследования заявитель полагает, что линия красного 14, линия зеленого 15 и линия синего 16 могут получать одинаковые напряжения в один и тот же момент времени в процессе отверждения. Подобно этому, нечетная линия 17 и четная линия 18 могут получать одинаковые напряжения в один и тот же момент времени. Соответственно, в процессе отверждения не нужно, чтобы линия красного 14, линия зеленого 15 и линия синего 16 получали напряжения по отдельности как три взаимно независимые дорожки, и также не нужно, чтобы нечетная линия 17 и четная линия 18 получали напряжения по отдельности как две взаимно независимые дорожки.

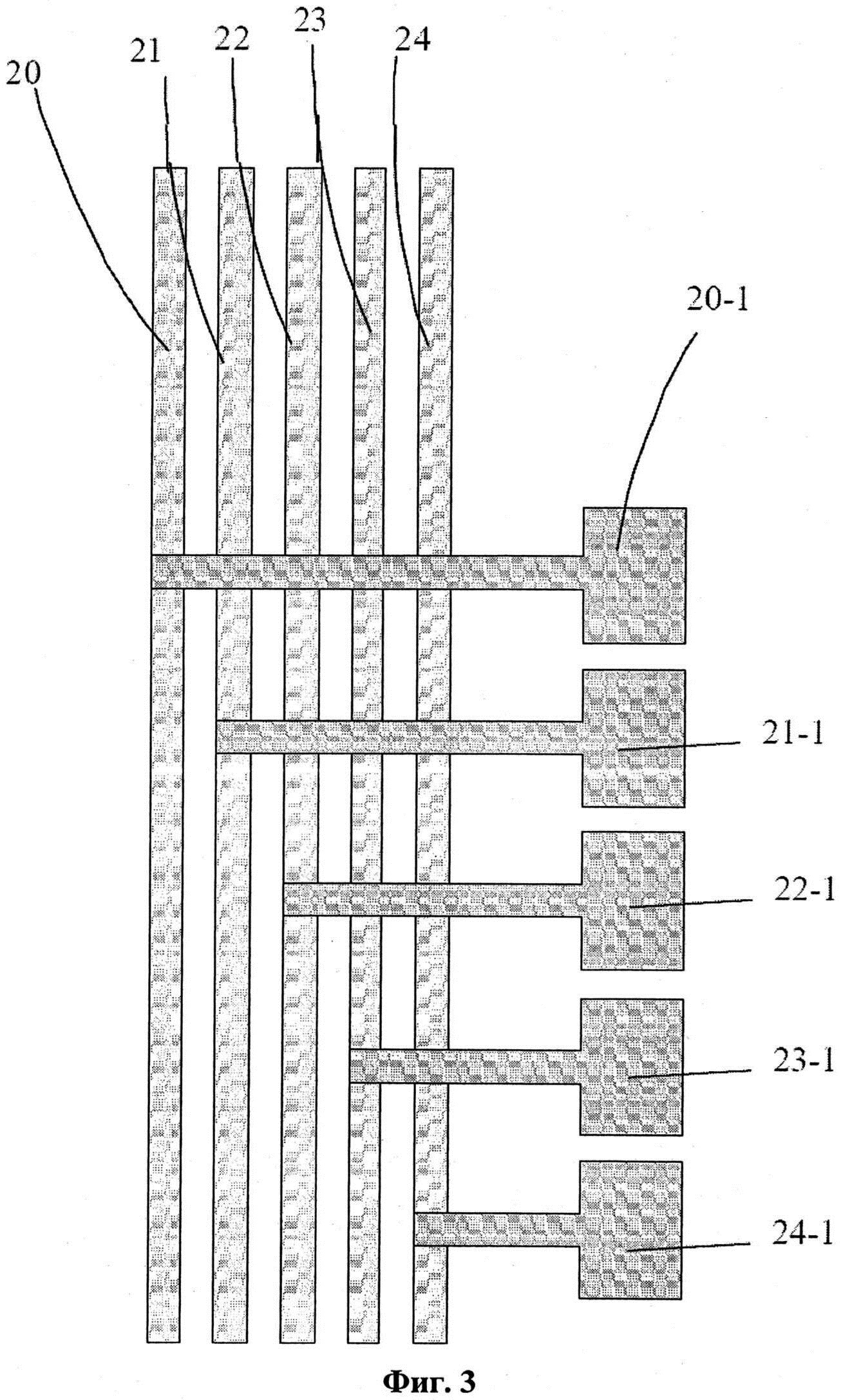

Таким образом, настоящее изобретение предлагает структуру металлических дорожек подложки матрицы. На Фиг. 3 показана структура металлических дорожек подложки матрицы жидкокристаллической панели с вертикальным выравниванием согласно настоящему изобретению.

Со ссылкой на Фиг. 3, структура металлических дорожек подложки матрицы согласно настоящему изобретению включает объединенную линию RGB (красного, зеленого и синего) 21, служащую в качестве линии данных в процессе отверждения, объединенную линию ОЕ (нечетную и четную) 22, служащую в качестве линии сканирования в процессе отверждения, общую линию подложки матрицы 20, общую линию подложки цветного фильтра 23, а также площадку отверждения RGB (красного, зеленого и синего) 21-1, площадку отверждения ОЕ (нечетной и четной линий) 22-1, площадку отверждения подложки матрицы 20-1 и площадку отверждения подложки цветного фильтра 23-1, которые соединены с объединенной линией RGB 21, объединенной линией ОЕ 22, общей линией подложки матрицы 20 и общей линией подложки цветного фильтра 23 соответственно и конфигурированы для получения соответствующих напряжений.

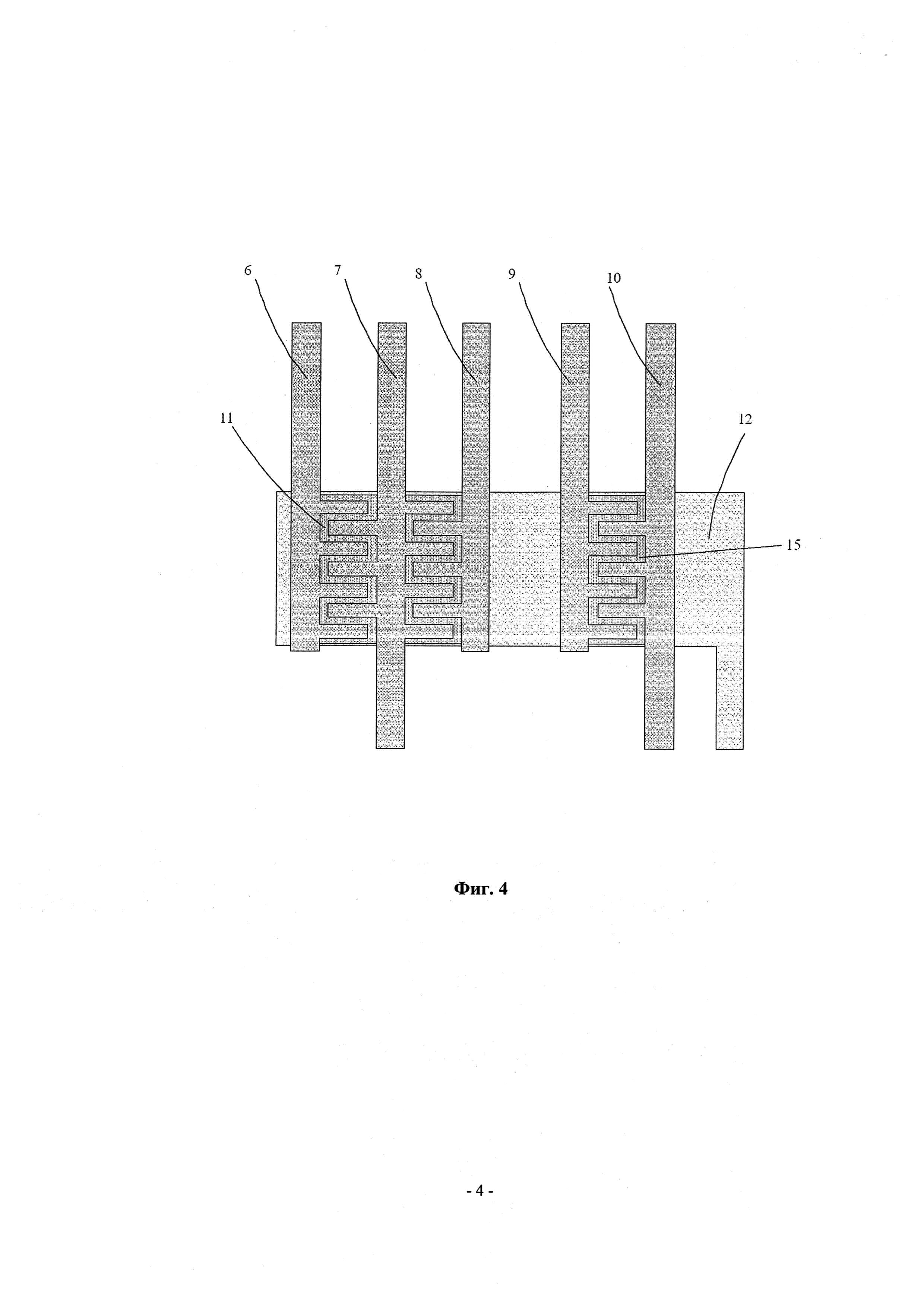

На Фиг. 4 показано расположение объединенной линии RGB и объединенной линии ОЕ структуры металлических дорожек подложки матрицы согласно настоящему изобретению.

Со ссылкой на Фиг. 4, объединенная линия RGB 21 включает линию красного 6, линию синего 8 и линию зеленого 7, причем две соседние линии из линии красного 6, линии синего 8 и линии зеленого 7 соединены посредством первого тонкопленочного транзистора 11. Первый тонкопленочный транзистор 11 может переключаться между включенным и отключенным состояниями затвором первого тонкопленочного транзистора 11, так что две линии, соединенные посредством первого тонкопленочного транзистора 11, могут переключаться между короткозамкнутым и разъединенным состояниями. Число первых тонкопленочных транзисторов 11 может составлять один или больше, исходя из конкретного требования к конструкции.

В примере, показанном на Фиг. 4, линия синего 8 и линия зеленого 7 соединены друг с другом посредством первого тонкопленочного транзистора 11, и линия зеленого 7 и линия красного 6 соединены друг с другом посредством первого тонкопленочного транзистора.

Альтернативно, также можно, чтобы линия красного 6 и линия синего 8 были соединены друг с другом посредством первого тонкопленочного транзистора 11, и линия зеленого 7 и линия синего 8 были соединены друг с другом посредством первого тонкопленочного транзистора 11.

Альтернативно, также можно, чтобы линия синего 8 и линия красного 6 были соединены друг с другом посредством первого тонкопленочного транзистора 11, и линия зеленого 7 и линия красного 6 были соединены друг с другом посредством первого тонкопленочного транзистора 11.

В одном примере структура металлических дорожек подложки матрицы согласно настоящему изобретению также включает первую сигнальную линию, способную подавать сигнальное напряжение, при этом затвор 12 первого тонкопленочного транзистора 11 соединен с первой сигнальной линией.

Со ссылкой на Фиг. 4, в одном предпочтительном примере объединенная линия ОЕ 22 включает нечетную линию 9 и четную линию 10, соединенные посредством второго тонкопленочного транзистора 15, и второй тонкопленочный транзистор 15 переключается между включенным и отключенным состояниями затвором второго тонкопленочного транзистора 15, так что нечетная линия 9 и четная линия 10 при этом становятся коротко замкнутыми или разъединенными. Число первых тонкопленочных транзисторов 11 может составлять один или больше, исходя из конкретного требования к конструкции.

В одном примере структура металлических дорожек также включает вторую сигнальную линию, способную подавать сигнальное напряжение, при этом затвор 12 второго тонкопленочного транзистора 15 соединен с второй сигнальной линией.

Снова со ссылкой на Фиг. 3, структура металлических дорожек подложки матрицы согласно настоящему изобретению также включает по меньшей мере одну вспомогательную линию отверждения 24 и одну вспомогательную площадку отверждения 24-1, соединенную с вспомогательной линией отверждения 24.

Вспомогательная линия отверждения 24 предпочтительно соединена с затворами первого тонкопленочного транзистора 11 и второго тонкопленочного транзистора 15, и вспомогательная площадка отверждения 24-1 предназначена для получения напряжений с затворов первого тонкопленочного транзистора 11 и второго тонкопленочного транзистора 15.

Посредством модификации структуры металлических дорожек из известного уровня техники настоящее изобретение может достигать цели уменьшения числа линий шины отверждения, что поможет уменьшить периферические дорожки подложки матрицы, увеличить буферное пространство для расположения схемы и снизить риск возникновения производственных дефектов. По сравнению с известным уровнем техники достигнут значительный прогресс.

Хотя настоящее изобретение описано выше со ссылками на предпочтительные примеры, в него могут быть внесены разные модификации, не нарушающие объем настоящего изобретения, и детали в настоящем изобретении могут быть заменены эквивалентными. Настоящее изобретение не ограничено конкретными примерами, раскрытыми в описании, а включает все технические решения, подпадающие под объем формулы изобретения.