Результат интеллектуальной деятельности: МНОГОКАНАЛЬНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных интерфейсах быстродействующих датчиковых систем.

Быстродействие операционных усилителей (ОУ) определяет динамические параметры многих аналоговых интерфейсов датчиков, буферных каскадов, АЦП, драйверов линий связи и т.п.

В современной измерительной технике и датчиковых системах находят применение ОУ, у которых в качестве промежуточного каскада применяется так называемый «перегнутый» каскод, выполненный на транзисторах по схеме с общей базой [1-6]. Для повышения симметрии схемы используется комплементарные «перегнутые» каскоды [7-15].

В работах [16-17] показано, что повышение максимальной скорости нарастания выходного напряжения ОУ (ϑвых) в режиме большого сигнала при однополюсной передаточной функции ОУ связано, прежде всего, с увеличением частоты единичного усиления ОУ (f1) и напряжения ограничения (Uгр) его входного дифференциального каскада (ДК). Данные параметры связаны формулой [16-17]:

На практике напряжение Uгр увеличивают за счет применения специальных ДК, работающих в режиме класса АВ [16-33]. В настоящее время можно считать, что проблема входных каскадов быстродействующих ОУ успешно решена - существуют сотни модификаций ДК [16-33] с напряжением ограничения Uгр=1-5 В.

Однако в ряде важных для практики случаев предельные значения ϑвых ОУ начинают определяться не входным, а промежуточным каскадом, ограничением его выходного тока, т.е. нелинейным режимом работы. Прежде всего, это относится к ОУ на основе так называемых «перегнутых» каскодов (ПК) [1-15], являющихся наиболее высокочастотными и поэтому, наиболее часто применяемыми архитектурами. Повышение быстродействия ОУ данного класса без ухудшения качества переходного процесса и существенного увеличения перерегулирования переходной характеристики - одна из проблем современной аналоговой микроэлектроники.

Известны схемотехнические решения ОУ [6, 3, 34, 14, 4, 2], в которых динамическая перегрузка ПК частично устраняется за счет введения параллельных RC-каналов [27], цепей положительной обратной связи [35, стр. 188, рис. 3.59] и др. Однако такая схемотехника далека от оптимальных решений и не всегда обеспечивает получение предельного быстродействия [16-17], например, по времени установления переходного процесса, запаса устойчивости в режиме большого сигнала и т.п.

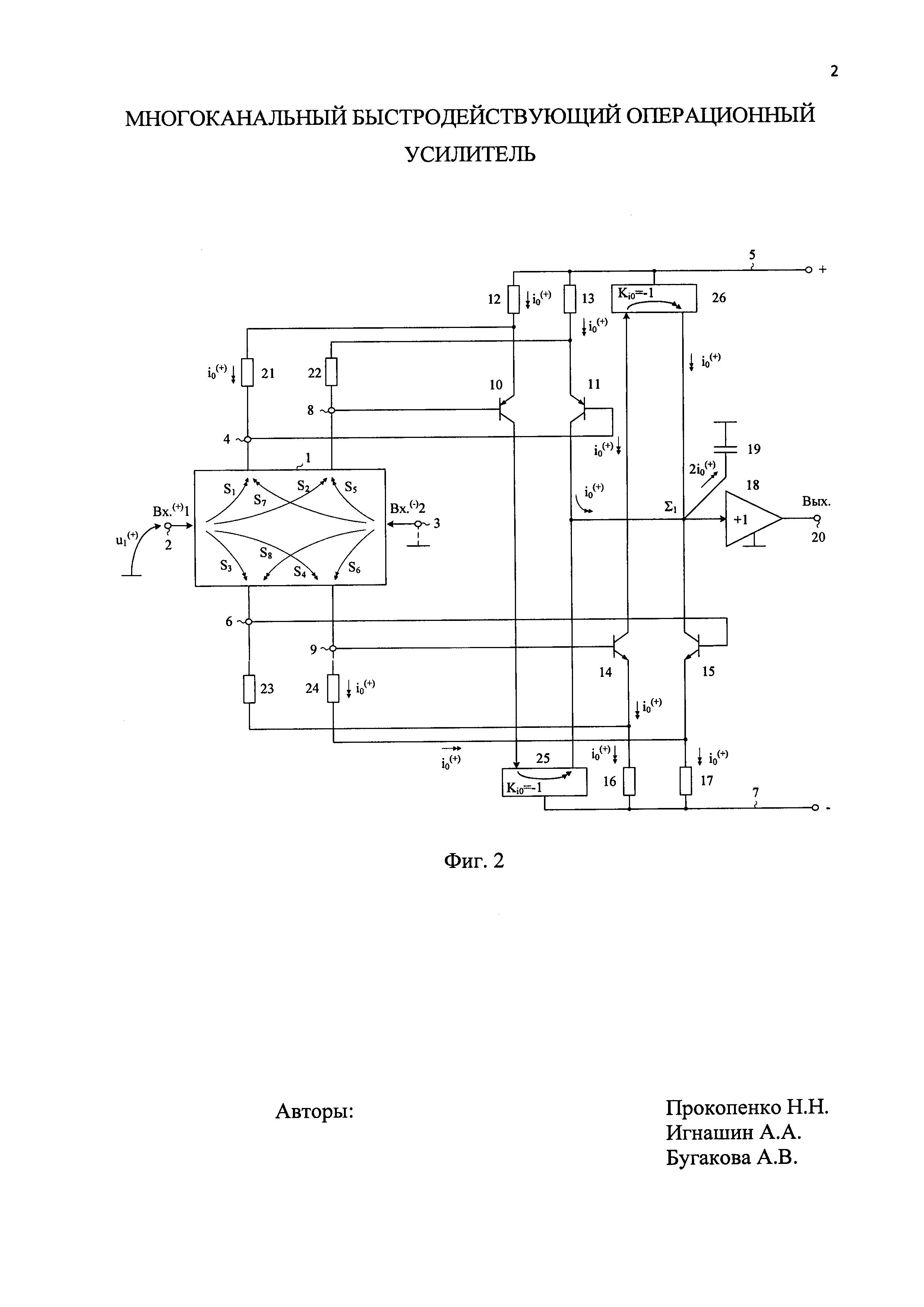

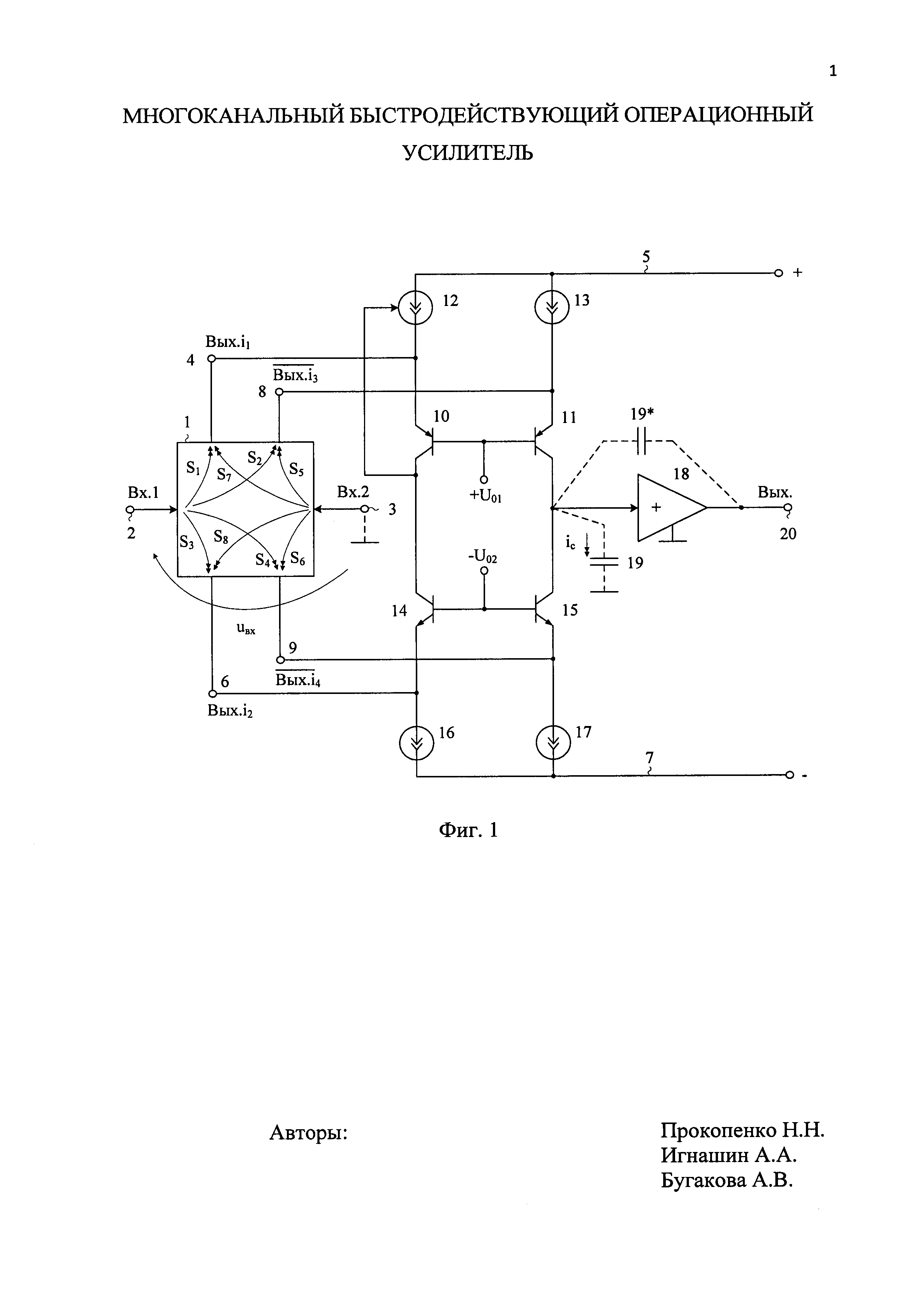

Ближайшим прототипом заявляемого устройства является операционный усилитель с промежуточным каскадом (фиг. 1), выполненным по архитектуре комплементарных «перегнутых» каскодов, представленный в справочнике - Эннс В.И., Кобзев Ю.М. «Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика» / М.: Горячая Линия - Телеком, 2005. - 454 с.; стр. 206, рис. 3.81. Он содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первый 4 токовый выход входного дифференциального каскада 1, согласованный с первой 5 шиной источника питания, второй 6 токовый выход входного дифференциального каскада 1, согласованный со второй 7 шиной источника питания, третий 8 токовый выход входного дифференциального каскада 1, согласованный с первой 5 шиной источника питания, четвертый 9 токовый выход входного дифференциального каскада 1, согласованный со второй 7 шиной источника питания, причем, первый 4 и второй 6 токовые выходы входного дифференциального каскада 1 синфазны, третий 8 и четвертый 9 токовые выходы входного дифференциального каскада 1 синфазны друг с другом и противофазны первому 4 и второму 6 токовым выходам входного дифференциального каскада 1, первый 10 и второй 11 выходные транзисторы, эмиттер первого 10 выходного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1 и через первый 12 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, эмиттер второго 11 выходного транзистора соединен с третьим 8 токовым выходом входного дифференциального каскада 1 и через второй 13 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, третий 14 и четвертый 15 выходные транзисторы, эмиттер третьего 14 выходного транзистора соединен со вторым 6 токовым выходом входного дифференциального каскада 1 и через третий 16 токостабилизирующий двухполюсник связан со второй 7 шиной источника питания, эмиттер четвертого 15 выходного транзистора соединен с четвертым 9 токовым выходом входного дифференциального каскада 1 и через четвертый 17 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, коллекторы второго 11 и четвертого 15 выходных транзисторов связаны со входом буферного усилителя 18 и корректирующим конденсатором 19, причем выход 20 буферного усилителя 18 является выходом устройства.

Существенный недостаток операционного усилителя-прототипа состоит в том, что он не обеспечивает предельное быстродействие для данной каскодной архитектуры, характеризующееся максимальной скоростью нарастания (ϑвых.) выходного напряжения в режиме большого сигнала. Это обусловлено нелинейным режимом работы той части схемы ОУ, которая включена между входами ОУ (2, 3) и корректирующим конденсатором 19 ОУ.

Основная задача предлагаемого изобретения состоит в повышении быстродействия ОУ в режиме большого сигнала до уровня 20000 В/мкс (при технологии Zarlink). Технически это обеспечивается за счет исключения (в соответствии с формулой изобретения) динамической перегрузки промежуточного каскада ОУ, выполненного в виде комплементарных «перегнутых» каскодов.

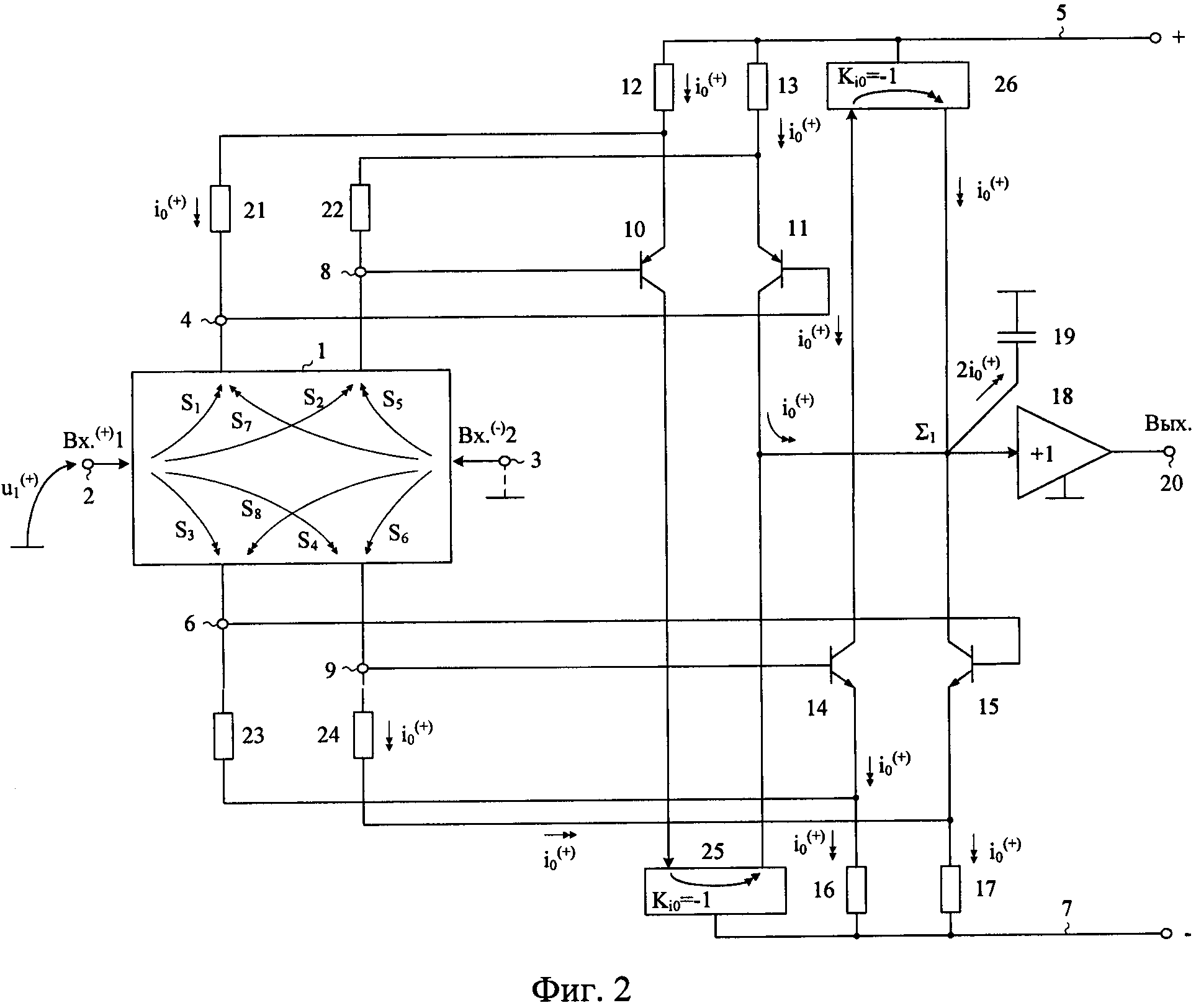

Поставленная задача достигается тем, что операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первый 4 токовый выход входного дифференциального каскада 1, согласованный с первой 5 шиной источника питания, второй 6 токовый выход входного дифференциального каскада 1, согласованный со второй 7 шиной источника питания, третий 8 токовый выход входного дифференциального каскада 1, согласованный с первой 5 шиной источника питания, четвертый 9 токовый выход входного дифференциального каскада 1, согласованный со второй 7 шиной источника питания, причем первый 4 и второй 6 токовые выходы входного дифференциального каскада 1 синфазны, третий 8 и четвертый 9 токовые выходы входного дифференциального каскада 1 синфазны друг с другом и противофазны первому 4 и второму 6 токовым выходам входного дифференциального каскада 1, первый 10 и второй 11 выходные транзисторы, эмиттер первого 10 выходного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1 и через первый 12 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, эмиттер второго 11 выходного транзистора соединен с третьим 8 токовым выходом входного дифференциального каскада 1 и через второй 13 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, третий 14 и четвертый 15 выходные транзисторы, эмиттер третьего 14 выходного транзистора соединен со вторым 6 токовым выходом входного дифференциального каскада 1 и через третий 16 токостабилизирующий двухполюсник связан со второй 7 шиной источника питания, эмиттер четвертого 15 выходного транзистора соединен с четвертым 9 токовым выходом входного дифференциального каскада 1 и через четвертый 17 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, коллекторы второго 11 и четвертого 15 выходных транзисторов связаны со входом буферного усилителя 18 и корректирующим конденсатором 19, причем выход 20 буферного усилителя 18 является выходом устройства, предусмотрены новые элементы и связи - база первого 10 выходного транзистора соединена с третьим 8 токовым выходом входного дифференциального каскада 1, база второго 11 выходного транзистора соединена с первым 4 токовым выходом входного дифференциального каскада 1, база третьего 14 выходного транзистора соединена с четвертым 9 токовым выходом входного дифференциального каскада 1, база четвертого 15 выходного транзистора соединена со вторым 6 токовым выходом входного дифференциального каскада 1, эмиттер первого 10 выходного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1 через первую цепь согласования потенциалов 21, эмиттер второго 11 выходного транзистора соединен с третьим 8 токовым выходом входного дифференциального каскада 1 через вторую цепь согласования потенциалов 22, эмиттер третьего 14 выходного транзистора соединен со вторым 6 токовым выходом входного дифференциального каскада 1 через третью 23 цепь согласования потенциалов, эмиттер четвертого 15 выходного транзистора соединен с четвертым 9 токовым выходом входного дифференциального каскада 1 через четвертую 24 цепь согласования потенциалов, коллектор первого 10 выходного транзистора соединен со входом первого 25 дополнительного токового зеркала, согласованного со второй 7 шиной источника питания, выход которого подключен ко входу буферного усилителя 18, коллектор третьего 14 выходного транзистора соединен со входом второго 26 дополнительного токового зеркала, согласованного с первой 5 шиной источника питания, выход которого подключен ко входу буферного усилителя 18, причем в качестве входного дифференциального каскада 1 используются каскады с широким диапазоном активной работы, а каждый первый 12, второй 13, третий 16 и четвертый 17 токостабилизирующие двухполюсники выполнены в виде соответствующих резисторов.

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

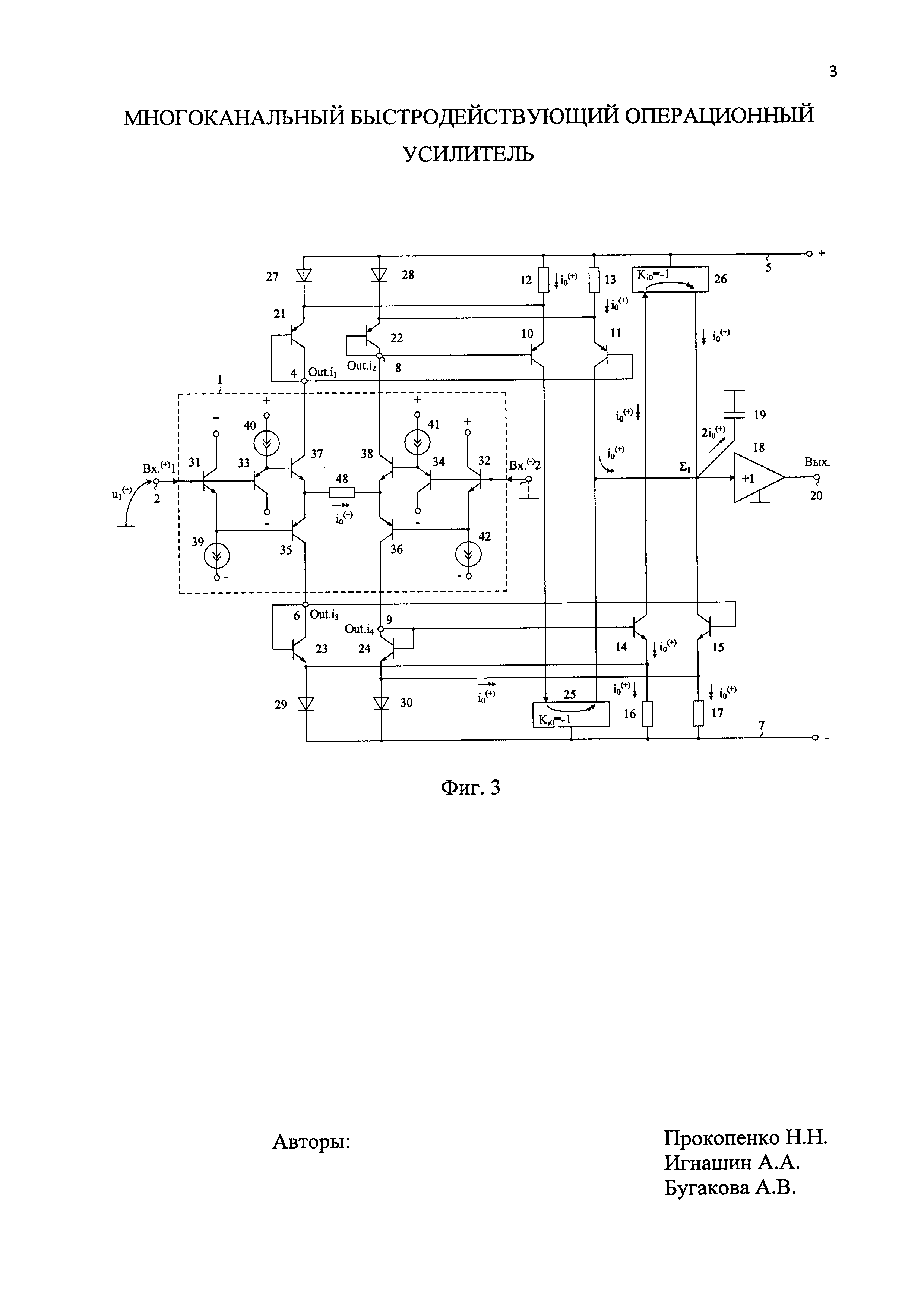

На чертеже фиг. 3 показана схема заявляемого ОУ в соответствии с пунктами 2, 3, 4 и 5 формулы изобретения. Кроме этого, на данном чертеже приведен пример конкретного построения входного дифференциального каскада 1, имеющего расширенный диапазон активной (линейной) работы, в пределах которого сохраняется пропорциональность между выходными токами входного ДК 1 и входным дифференциальным напряжением ОУ (uвх).

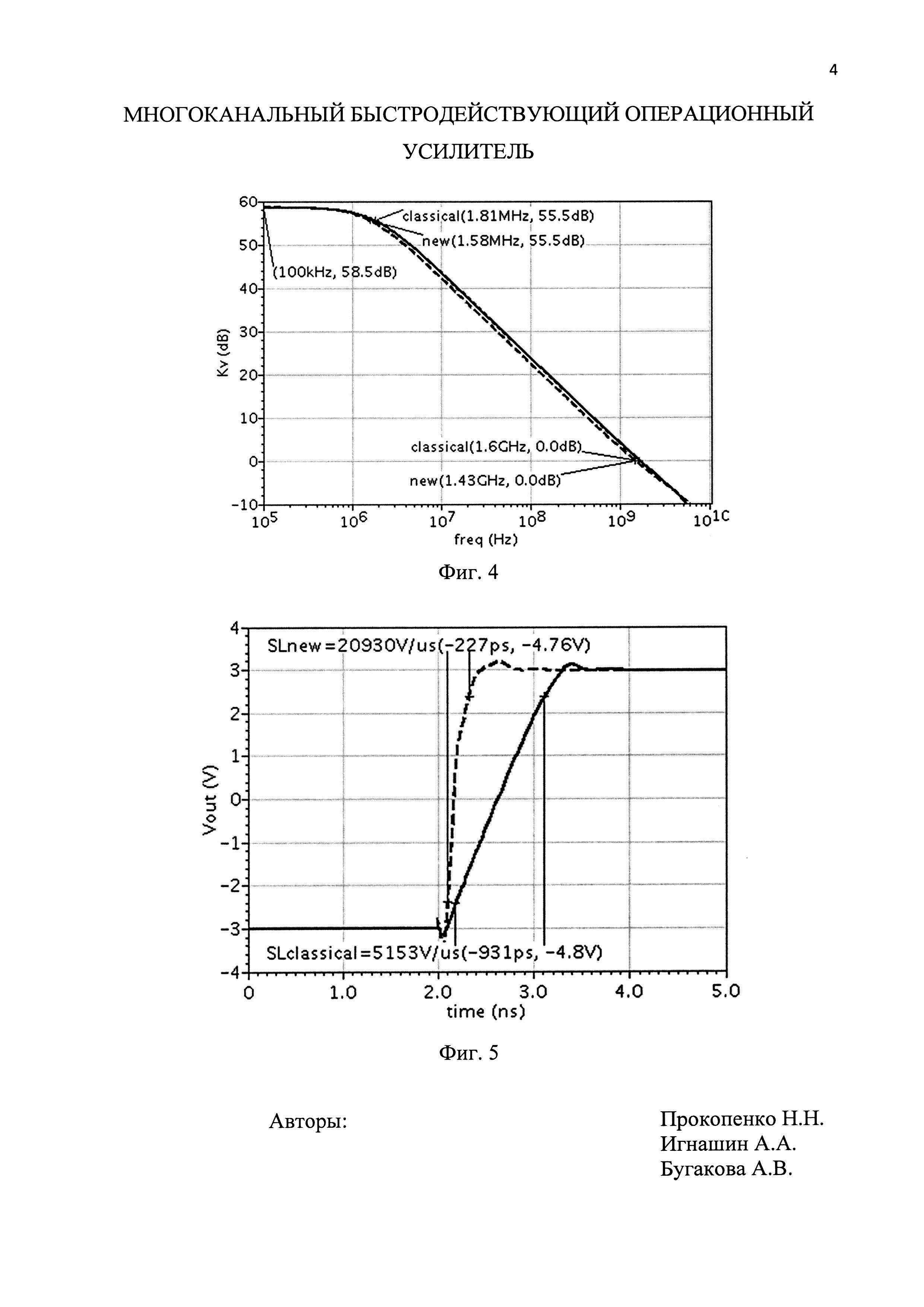

На чертеже фиг. 4 приведены амплитудно-частотные характеристики разомкнутого коэффициента усиления предлагаемого ОУ (фиг. 3) и ОУ-прототипа (фиг. 1) при одинаковом запасе устойчивости по фазе (для случая реализации ОУ на основе техпроцесса фирмы Zarlink).

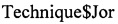

На чертеже фиг. 5 представлены графики переходных процессов заявляемого ОУ (фиг. 3) и ОУ-прототипа (фиг. 1) в режиме больших входных импульсных сигналов.

Многоканальный быстродействующий операционной усилитель фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первый 4 токовый выход входного дифференциального каскада 1, согласованный с первой 5 шиной источника питания, второй 6 токовый выход входного дифференциального каскада 1, согласованный со второй 7 шиной источника питания, третий 8 токовый выход входного дифференциального каскада 1, согласованный с первой 5 шиной источника питания, четвертый 9 токовый выход входного дифференциального каскада 1, согласованный со второй 7 шиной источника питания, причем, первый 4 и второй 6 токовые выходы входного дифференциального каскада 1 синфазны, третий 8 и четвертый 9 токовые выходы входного дифференциального каскада 1 синфазны друг с другом и противофазны первому 4 и второму 6 токовым выходам входного дифференциального каскада 1, первый 10 и второй 11 выходные транзисторы, эмиттер первого 10 выходного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1 и через первый 12 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, эмиттер второго 11 выходного транзистора соединен с третьим 8 токовым выходом входного дифференциального каскада 1 и через второй 13 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, третий 14 и четвертый 15 выходные транзисторы, эмиттер третьего 14 выходного транзистора соединен со вторым 6 токовым выходом входного дифференциального каскада 1 и через третий 16 токостабилизирующий двухполюсник связан со второй 7 шиной источника питания, эмиттер четвертого 15 выходного транзистора соединен с четвертым 9 токовым выходом входного дифференциального каскада 1 и через четвертый 17 токостабилизирующий двухполюсник связан с первой 5 шиной источника питания, коллекторы второго 11 и четвертого 15 выходных транзисторов связаны со входом буферного усилителя 18 и корректирующим конденсатором (19), причем выход 20 буферного усилителя 18 является выходом устройства. База первого 10 выходного транзистора соединена с третьим 8 токовым выходом входного дифференциального каскада 1, база второго 11 выходного транзистора соединена с первым 4 токовым выходом входного дифференциального каскада 1, база третьего 14 выходного транзистора соединена с четвертым 9 токовым выходом входного дифференциального каскада 1, база четвертого 15 выходного транзистора соединена со вторым 6 токовым выходом входного дифференциального каскада 1, эмиттер первого 10 выходного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1 через первую цепь согласования потенциалов 21, эмиттер второго 11 выходного транзистора соединен с третьим 8 токовым выходом входного дифференциального каскада 1 через вторую цепь согласования потенциалов 22, эмиттер третьего 14 выходного транзистора соединен со вторым 6 токовым выходом входного дифференциального каскада 1 через третью 23 цепь согласования потенциалов, эмиттер четвертого 15 выходного транзистора соединен с четвертым 9 токовым выходом входного дифференциального каскада 1 через четвертую 24 цепь согласования потенциалов, коллектор первого 10 выходного транзистора соединен со входом первого 25 дополнительного токового зеркала, согласованного со второй 7 шиной источника питания, выход которого подключен ко входу буферного усилителя 18, коллектор третьего 14 выходного транзистора соединен со входом второго 26 дополнительного токового зеркала, согласованного с первой 5 шиной источника питания, выход которого подключен ко входу буферного усилителя 18, причем в качестве входного дифференциального каскада 1 используются каскады с широким диапазоном активной работы, а каждый первый 12, второй 13, третий 16 и четвертый 17 токостабилизирующие двухполюсники выполнены в виде соответствующих резисторов.

В схеме фиг. 3 в соответствии с п. 2 формулы изобретения первый 21 и второй 22 согласующие двухполюсники выполнены на вспомогательных транзисторах, у которых база соединена с коллектором. Причем вспомогательные транзисторы идентичны первому 10 и второму 11 выходным транзисторам.

В схеме фиг. 3 в соответствии с п. 3 формулы изобретения третий 23 и четвертый 24 согласующие двухполюсники выполнены на вспомогательных транзисторах, у которых база соединена с коллектором. Причем вспомогательные транзисторы идентичны третьему 14 и четвертому 15 выходным транзисторам.

В схеме фиг. 3 в соответствии с п. 4 формулы изобретения параллельно каждому первому 12, второму 13, третьему 16 и четвертому 17 токостабилизирующим резисторам включены соответствующие первый 27, второй 28, третий 29 и четвертый 30 ограничители напряжения.

В схеме фиг. 3 в соответствии с п. 5 формулы изобретения в качестве каждого из ограничителей напряжения (27, 28, 29, 30) используется прямосмещенный pn-переход.

Кроме этого, на чертеже фиг. 3 входной дифференциальный каскад 1 с расширенным диапазоном активной (линейной) работы выполнен по классической схеме [35, стр. 143, рис. 3.13, стр. 144, рис. 3.13, стр. 205, рис. 3.78] на транзисторах 31, 32, 33, 34, 35, 36, 37, 38 и источниках опорного тока 39, 40, 41, 42. Данный ДК содержит также резистор 43, определяющий крутизну преобразования входного напряжения ДК в его выходные токи.

Рассмотрим работу операционного усилителя фиг. 3 в режиме большого входного импульсного сигнала.

Особенность предлагаемого ОУ состоит в том, что в нем обеспечивается пропорциональность тока в корректирующем конденсаторе 19 и входного дифференциального напряжения ОУ uвх. В ОУ-прототипе данное условие не выполняется, что является причиной его сравнительно низкого быстродействия. Об этом свидетельствуют результаты компьютерного моделирования сравниваемых ОУ фиг. 4, при одинаковом запасе устойчивости по фазе, показанные на чертеже фиг. 5. Из графиков фиг. 5 следует, что предлагаемый ОУ (в рамках техпроцесса Zarlink) имеет предельную скорость нарастания выходного напряжения 20930 В/мкс, что в 4 раза больше, чем в ОУ-прототипе.

Таким образом, предлагаемый операционный усилитель характеризуется более высокими значениями максимальной скорости нарастания выходного напряжения.

Источники информации

1. Патент US №6710654.

2. Патент US №7176760.

3. W. Redman-White, "A high bandwidth constant g/sub m/ and slew-rate rail-to-rail CMOS amplifier circuit for embedded low-voltage applications," 1996 Symposium on VLSI Circuits, Digest of Technical Papers., pp. 150-151, 13-15 June 1996. DOI: 10.1109/VLSIC. 1996.507750.

4. Патент US №8604878.

5. R.G. Carvajal, J. Galan, J. Ramirez-Angulo and A. Torralba, "Low-power low-voltage differential class-AB OTAs for SC circuits," in Electronics Letters, vol. 38, no. 22, pp.1304-1305, 24 Oct 2002. DOI: 10.1049/el:20020958.

6. Vadim V. Ivanov, and Igor M. Filanovsky, Operational Amplifier Speed and Accuracy Improvement, Kluwer Academic Peblishers, Boston, 2004. DOI 10.1007/bl05872.

7. Патент US №2321161.

8. Патент RU №2412530.

9. Патент RU №2384937.

10.Sen S. and Bosco Leung, "A class-AB high-speed low-power operational amplifier in BiMOS technology," IEEE Journal of Solid-State Circuits, Volume: 31, Issue: 9, pp. 1325-1330, September 1996. DOI: 10.1109/4.535418.

11. S.R. Zarabadi, F. Larsen, and M. Ismail, A reconfigurable CMOS op-amp/differential difference amplifier architecture, IEEE Trans. Circuits Syst. I, vol. 39, pp. 484-487, June 1992.

12. Патент US №6433637.

13. Патент US №6392485.

14. M. Rezaei, Е. Zhian-Tabasy and S.J. Ashtiani, "Slew rate enhancement method for folded-cascode amplifiers," Electronics Letters, vol. 44, No. 21, pp. 1226-1228, 9th October 2008. DOI: 10.1049/el:20082200.

15. Патент US №7639078.

16. Анисимов В.И., Прокопенко H.H., Капитонов М.В., Соколов Ю.М. Операционные усилители с непосредственной связью каскадов (монография) / Л.: «Энергия», 1979. - 148 с.

17. Прокопенко Н.Н., Будяков А.С. Архитектура и схемотехника быстродействующих операционных усилителей (монография) / Шахты: ЮРГУЭС, 2006. - 232 с.

18. Патент ЕР №191488719. 3аявка на патент US №2004/0027200.

20. Патент US №7339433.

21. Патент US №7646243.

22. Bin Huang and Degang Chen, "A Simple Slew Rate Enhancement Technique Wiflnmproved Linearity. And Preserved Small Signal Performance," IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 270-273, 3-6 Aug. 2014.

DOI: 10.1109/MWSCAS.2014.6908404.

23. Shouli Yan, Jingyu Hu, Tongyu Song and Sanchez-Sinencio E., "Constant-gm  Rail-to-Rail CMOS Amplifier Input Stages: A Comparative Study" IEEE International Symposium on Circuits and Systems (ISCAS 2005), Vol. 3, pp. 2571-2574, 23-26 May 2005.

Rail-to-Rail CMOS Amplifier Input Stages: A Comparative Study" IEEE International Symposium on Circuits and Systems (ISCAS 2005), Vol. 3, pp. 2571-2574, 23-26 May 2005.

DOI: 10.1109ASCAS.2005.1465151.

24. A. Thanachayanont and W. Chaloenlarp, "Low-voltage, rail-to-rail, Gm-enhanced pseudo-differential class-AB OTA" The 2004 47th Midwest Symposium on Circuits and Systems (MWSCAS '04), vol. 1, pp. 53-56, 25-28 July 2004. DOI: 10.1109/MWSCAS.2004.1353895.

25. R.G. Carvajal, J. Galan, J. Ramirez-Angulo and A. Torralba, "New low-power low-voltage differential class-AB OTA for SC circuits," Proceedings of the 2003 International Symposium on Circuits and Systems (ISCAS '03), vol. 1, pp. 589-592,25-28 May 2003. DOI: 10.1109/ISCAS.2003.1205632.

26. J. Ramirez-Angulo, R. Gonzalez-Carvajal, A. Torralba and C. Nieva, "A new class AB differential input stage for implementation of low-voltage high slew rate op amps and linear transconductors," The 2001 IEEE International Symposium on Circuits and Systems (ISCAS 2001), vol. 1, pp. 671-674, 06-09 May 2001. DOI: 10.1109/ISCAS.2001.921945.

27. R. Krithivasan, L. Yuan, L. Najafizadeh, Z. Chendong, J.D. Cressler, S. Chen, C. Ulaganathan and B.J. Blalock, "A High-Slew Rate SiGe BiCMOS Operational Amplifier for Operation Down to Deep Cryogenic Temperatmes," Bipolar/BiCMOS Circuits and Technology Meeting, pp. 1-4, 8-10 October 2006. DOI: 10.1109/BIPOL.2006.311170.

28. Sen S. and Bosco Leung, "A class-AB high-speed low-power operational amplifier in BiMOS technology," IEEE Journal of Solid-State Circuits, Volume: 31, Issue: 9, pp. 1325-1330, September 1996. DOI: 10.1109/4.535418.

29. Патент US №8207789.

30. A.J. Gano and J.E. Franca, "Fully differential variable gain instrumentation amplifier based on a fully differential DDA topology," The 6th IEEE International Conference on Electronics, Circuits and Systems, Proceedings of ICECS '99, vol. 2, pp. 781-784, 5-8 September 1999.

DOI: 10.1109/ICECS.1999.813225.

31. D.D. Shulman and Y. Jian, "An Analytical Model for the Transient Response of CMOS Class AB Operational Amplifiers," IEEE Transactions On Circuits And Systems-1: Fundamental Theory And Applications, vol. 4, No. 1, pp. 49-52, January 1994.

32. D. Smith, M. Koen and A.F. Witulski, "Evolution of high-speed operational amplifier architectures," in IEEE Journal of Solid-State Circuits, vol. 29, no. 10, pp. 1166-1179, Oct 1994. DOI: 10.1109/4.315199.

33. С. Binan Wang, J. Todsen and T. Kalthoff, "A dual channel 20 bit current-input A/D converter for photo-sensor applications," Mixed-Signal Design, 2000. SSMSD. 2000 Southwest Symposium on, San Diego, CA, 2000, pp. 57-60. DOI: 10.1109/SSMSD.2000.836446.

34. Патент US №7342450.

35. Эннс В.И., Кобзев Ю.М. «Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика» / М.: Горячая Линия - Телеком, 2005. - 454 с.