Результат интеллектуальной деятельности: Способ определения знака разности частот и устройство для его реализации

Вид РИД

Изобретение

Изобретение относится к радиотехнике и может быть также использовано в дискретных системах автоматики для получения информации о знаке разности частот двух импульсных колебаний, в том числе имеющих близкие по значению частоты. Наибольшее применение изобретение может найти в измерительных системах с частотными датчиками и системах фазовой автоподстройки частоты (ФАПЧ) в качестве определителя знака частотного рассогласования опорного и подстраиваемого колебаний.

Известны способы определения знака и величины разности частот, основанные на счете числа периодов анализируемых колебаний за известный калиброванный промежуток времени и их последующем сравнении, счете числа периодов одной частоты за один или несколько периодов другой частоты [1], компенсации одной частоты другой и накоплением их разности [1, 2]. В системах ФАПЧ с элементами дискретизации наибольшее применение нашли методы, базирующиеся на компенсационном способе определения разности частот [2] и анализе фазового рассогласования колебаний [3]. В последнем методе анализируется изменение разности фаз между колебаниями. Информация о знаке и величине частотного рассогласования вырабатывается на основе учета направления (оценивается область изменения разности фаз - положительная или отрицательная) и значения частоты перескока фазы (частоты фазовых переходов через уровень ±2π) [3, 4]. Последний способ выбран в качестве прототипа.

Способ учета моментов достижения разностью фаз Δϕ=ϕ1-ϕ2 сравниваемых частот ƒ1 и ƒ2 значений Δϕ=±2πn, где ϕ1=2πƒ1t, ϕ2=2πƒ2t, n=1, 2, …, хорошо работает в случае, когда ƒ1 и ƒ2 различаются значительно. При малом различии частот ƒ1 и ƒ2 (ƒ1≈ƒ2) частота перескоков фазы стремится к нулю, то есть время t, через которое будет получен результат о знаке разности частот, значительно возрастает. Последнее является существенным недостатком при определении знака разности частот, близких по величине.

В методе определения знака разности частот, базирующемся на оценке разности фаз, с помощью цифровых частотно-фазовых дискриминаторов (ЦЧФД) вычисляются знак и величина Δϕ. Когда величина Δϕ достигает значений ±2πn, ЦЧФД вырабатываются импульсы, частота следования которых определяется Δƒ=ƒ1-ƒ2, несущие информацию о модуле частотного рассогласования. При Δƒ>0 последовательность импульсов выдается на одном выходе ЦЧФД, а при Δƒ<0 - на другом его выходе [3]. Для реализации данного метода колебания сравниваемых частот преобразуются в последовательности импульсных сигналов с уровнями цифровой логики. Эту операцию легко выполнить, применяя компараторы с уровнем порога, равным нулю.

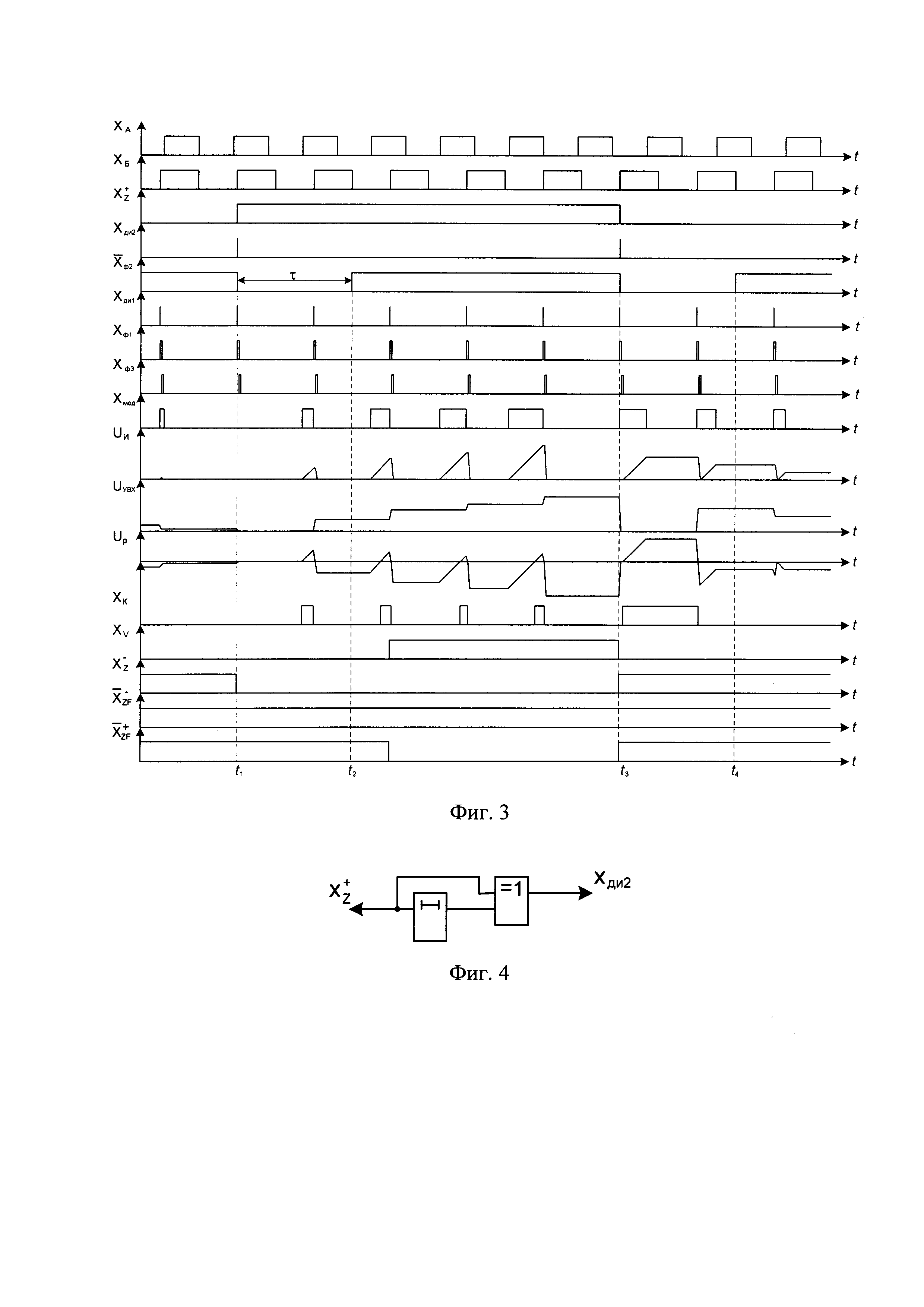

Для того чтобы получить информацию о знаке частотного рассогласования сравниваемых колебаний до момента достижения разностью фаз Δϕ величин ±2πn, необходимо постоянно отслеживать изменение Δϕ. В ЦЧФД узел, выполняющий оценку знака и величины Δϕ, представлен схемой цифрового фазового дискриминатора (ЦФД). Характер изменения напряжения U(Δϕ), несущего информацию о величине Δϕ, определяется формой дискриминационной характеристики (ДХ) фазового дискриминатора [2]. Оценка Δϕ представляется в виде мгновенного либо усредненного за период опорного колебания значения напряжения U(Δϕ) и имеет периодический характер с периодом 2π. Для ЦФД с ДХ релейного типа нормированное изменение (приращение оценки величины разности фаз) U(Δϕ) показано на фиг.1.

При Δƒ>0 (ƒ1>ƒ2) зависимость U(Δϕ) для ЦФД с релейной ДХ будет изменяться в соответствии с графиком, приведенным на фиг. 1, а. В случае Δƒ<0 график зависимости Δϕ(t) примет вид, показанный на фиг. 1, б. Стрелками на графиках показаны направления изменения разности фаз Δϕ во времени t. Из графиков видно, что для Δƒ>0 (фиг. 1, а) при знаке разности фаз Sign(Δϕ)=-1 значение  при изменении разности фаз от π[2π-1] до 2πn уменьшается, а при Sign(Δϕ)=1 на интервале от 2πn до π[2π+1] - возрастает. Для Δƒ<0 (фиг. 1, б) прослеживается обратная зависимость. При Sign(Δϕ)=-1 на интервале [-2πn, -π(2n+1)] значение

при изменении разности фаз от π[2π-1] до 2πn уменьшается, а при Sign(Δϕ)=1 на интервале от 2πn до π[2π+1] - возрастает. Для Δƒ<0 (фиг. 1, б) прослеживается обратная зависимость. При Sign(Δϕ)=-1 на интервале [-2πn, -π(2n+1)] значение  возрастает, а при Sign(Δϕ)=1 на интервале [-π(2n-1), -2πn] - уменьшается.

возрастает, а при Sign(Δϕ)=1 на интервале [-π(2n-1), -2πn] - уменьшается.

Если постоянно анализировать изменение  с учетом знака разности фаз Sign(Δϕ), то можно сделать вывод о знаке Δƒ, не дожидаясь момента, когда произойдет перескок фазы. На данном принципе базируется предлагаемый метод определения знака разности частот Sign(Δƒ). Знак Sign(Δƒ)=1, если при Sign(Δϕ)=-1 величина

с учетом знака разности фаз Sign(Δϕ), то можно сделать вывод о знаке Δƒ, не дожидаясь момента, когда произойдет перескок фазы. На данном принципе базируется предлагаемый метод определения знака разности частот Sign(Δƒ). Знак Sign(Δƒ)=1, если при Sign(Δϕ)=-1 величина  , изменяющаяся под действием ƒ1>ƒ2, уменьшается, а при Sign(Δϕ)=1 - увеличивается. Знак Sign(Δƒ)=-1, если при Sign(Δϕ)=-1 величина

, изменяющаяся под действием ƒ1>ƒ2, уменьшается, а при Sign(Δϕ)=1 - увеличивается. Знак Sign(Δƒ)=-1, если при Sign(Δϕ)=-1 величина  под действием ƒ1<ƒ2 увеличивается, а при Sign(Δϕ)=1 - уменьшается.

под действием ƒ1<ƒ2 увеличивается, а при Sign(Δϕ)=1 - уменьшается.

Целью изобретения является определение знака Sign(Δƒ) разности частот Δƒ=ƒ1-ƒ2 для близких по значению частот ƒ1 и ƒ2.

Способ определения Sign(Δƒ) заключается в сравнении модулей оценки разности фаз  во времени через интервал Тр, равный периоду колебаний опорной частоты ƒ2 (Tp=1/ƒ2). Колебание частотой ƒ1 рассматривается как исследуемое, то есть анализируется изменение его фазы относительно фазы опорного колебания. Величина Δϕ определяется как разность фаз между первыми гармониками импульсных колебаний с частотами ƒ1 и ƒ2. Для импульсных колебаний симметричной формы Δϕ можно определять также как разность фаз между одноименными фронтами (например, передними) колебаний.

во времени через интервал Тр, равный периоду колебаний опорной частоты ƒ2 (Tp=1/ƒ2). Колебание частотой ƒ1 рассматривается как исследуемое, то есть анализируется изменение его фазы относительно фазы опорного колебания. Величина Δϕ определяется как разность фаз между первыми гармониками импульсных колебаний с частотами ƒ1 и ƒ2. Для импульсных колебаний симметричной формы Δϕ можно определять также как разность фаз между одноименными фронтами (например, передними) колебаний.

Весь интервал времени анализа t можно представить состоящим из суммы подынтервалов Тр (t=kTp, где k=1, 2, 3, …). Определяя  в момент времени

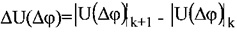

в момент времени  в момент времени t=(k+1)Tр и вычисляя их разность

в момент времени t=(k+1)Tр и вычисляя их разность  , можно с учетом значения Sign(Δϕ) определить Sign(Δƒ). Знак расстройки частот Sign(Δƒ)=1, если ΔU(Δϕ)>0 и Sign(Δϕ)=1 или ΔU(Δϕ)<0 и Sign(Δϕ)=-1. Знак расстройки частот Sign(Δƒ)=-1, если ΔU(Δϕ)<0 и Sign(Δϕ)=1 или ΔU(Δϕ)>0 и Sign(Δϕ)=-1.

, можно с учетом значения Sign(Δϕ) определить Sign(Δƒ). Знак расстройки частот Sign(Δƒ)=1, если ΔU(Δϕ)>0 и Sign(Δϕ)=1 или ΔU(Δϕ)<0 и Sign(Δϕ)=-1. Знак расстройки частот Sign(Δƒ)=-1, если ΔU(Δϕ)<0 и Sign(Δϕ)=1 или ΔU(Δϕ)>0 и Sign(Δϕ)=-1.

Предлагаемый способ определения знака разности частот можно реализовать, используя ЦФД, позволяющий получать информацию о знаке и величине фазового рассогласования импульсных колебаний. Наиболее подходят для использования в качестве ЦФД логические фазовые дискриминаторы (ЛФД) [5-7]. Они имеют два входа и четыре выхода, первые два из которых отражают информацию о знаке Sign(Δϕ), а другие два - информацию о величине (модуле)  . Среди указанных, в качестве прототипа выбрана схема [5], обеспечивающая необходимые свойства оценки Δϕ при меньшей сложности реализации.

. Среди указанных, в качестве прототипа выбрана схема [5], обеспечивающая необходимые свойства оценки Δϕ при меньшей сложности реализации.

Поскольку выбранный в качестве прототипа дискриминатор применяется в системах ФАПЧ для целей формирования сигналов управления подстраиваемым генератором, наиболее важным является определение Sign(Δƒ) для моментов, когда в системе обеспечивается управление, способствующее уменьшению частотной расстройки  опорного и формируемого колебаний. Такими моментами для Δƒ>0 являются моменты, когда выполняется увеличение

опорного и формируемого колебаний. Такими моментами для Δƒ>0 являются моменты, когда выполняется увеличение  при Sign(Δϕ)=1, а для Δƒ<0 - когда выполняется увеличение

при Sign(Δϕ)=1, а для Δƒ<0 - когда выполняется увеличение  при Sign(Δϕ)=-1. Моменты, когда в системе ФАПЧ обеспечивается увеличение

при Sign(Δϕ)=-1. Моменты, когда в системе ФАПЧ обеспечивается увеличение  , в данном случае можно не рассматривать. Эти моменты соответствуют для Δƒ>0 уменьшению

, в данном случае можно не рассматривать. Эти моменты соответствуют для Δƒ>0 уменьшению  при Sign(Δϕ)=1, а для Δƒ<0 - уменьшению

при Sign(Δϕ)=1, а для Δƒ<0 - уменьшению  при Sign(Δϕ)=-1, в принципе, можно рассмотреть все варианты изменения

при Sign(Δϕ)=-1, в принципе, можно рассмотреть все варианты изменения  , но в этом случае реализация ЦЧФД существенно усложнится. Поэтому рассмотрим построение ЦЧФД для первого случая, когда выполняется увеличение

, но в этом случае реализация ЦЧФД существенно усложнится. Поэтому рассмотрим построение ЦЧФД для первого случая, когда выполняется увеличение  как для случая Δƒ>0, так и для случая Δƒ<0.

как для случая Δƒ>0, так и для случая Δƒ<0.

Цель получения информации о знаке разности частот достигается усовершенствованием изобретения по авторскому свидетельству №1432724 [5] путем дополнения его схемы, состоящей из совокупности логических элементов И-НЕ, элементов задержки и RS-триггеров и связей, имеющих два входа и четыре выхода. Причем структура изобретения [5] не изменяется. В качестве заявляемого изобретения предлагается использовать схему [5] без изменений (то есть полностью), определив известную совокупность элементов и связей в виде узла, имеющего два входа, на один из которых подается опорное импульсное колебание, а на второй - сравниваемое (анализируемое) импульсное колебание. Выходы модуля определены также, как и в известном устройстве, и выполняют те же функции. Первый и второй входы являются знаковыми. На первом выходе формируется потенциал, отражающий положительный знак Δϕ, а на втором выходе формируется потенциал, отражающий отрицательный знак Δϕ. Третий и четвертый выходы модуля отражают информацию о величине (модуле) разности фаз: третий - величину положительной разности фаз, а четвертый - отрицательной. Информация на первом и втором выходах отображается уровнями логической единицы, а информация на третьем и четвертом выходах - импульсами с уровнями логического нуля соответствующей длительности.

Рассмотренный узел дополняется тремя элементами И-НЕ, двумя дифференцирующими устройствами, двумя формирователями импульсов, элементом задержки, интегратором со сбросом (обнуляемым интегратором), устройством выборки-хранения, вычитающим устройством, компаратором и D-триггером.

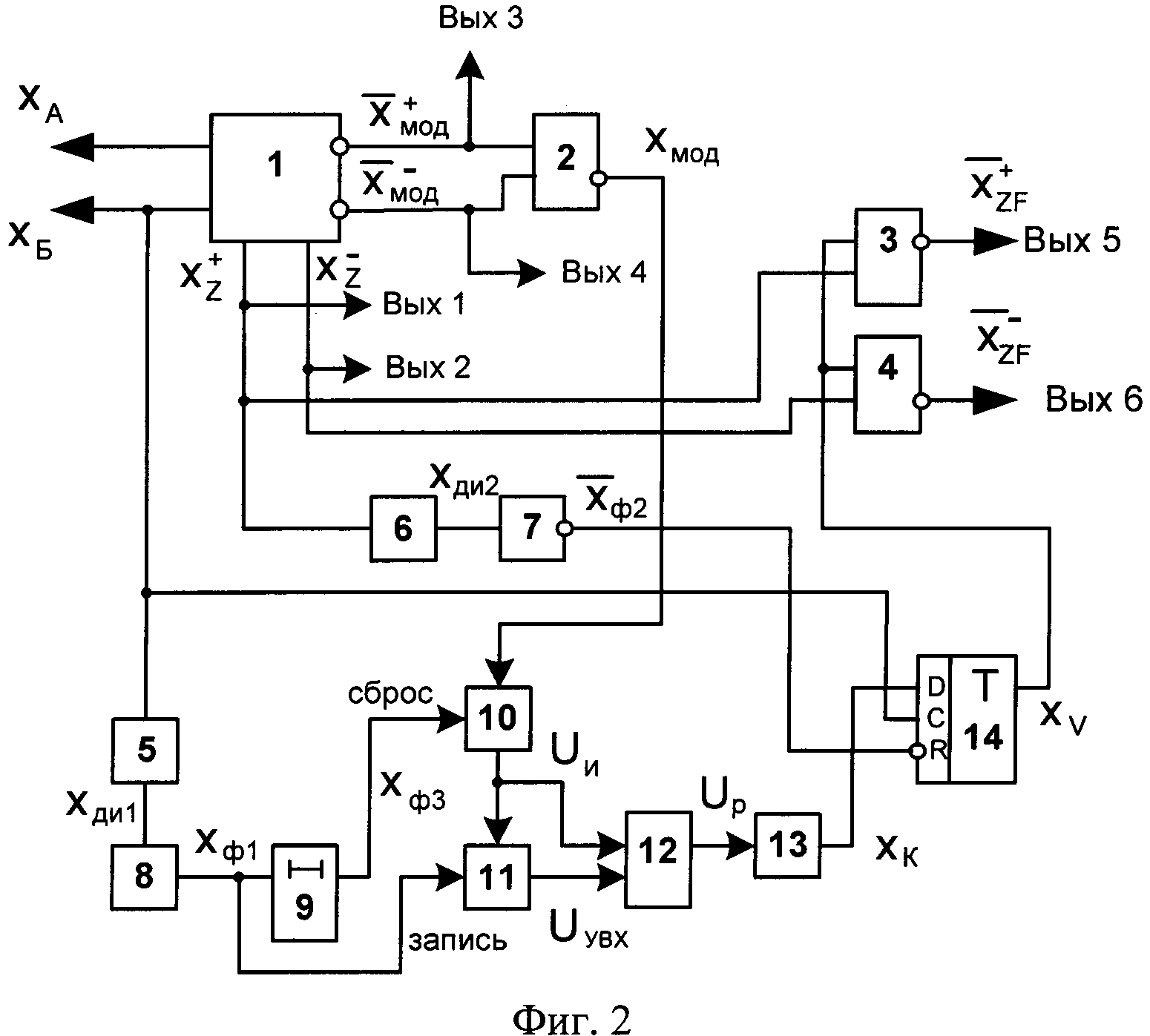

Рассмотрим структуру и принцип функционирования предлагаемого устройства. На фиг. 2 приведена схема заявляемого устройства, а на фиг. 3, 5 - временные диаграммы, поясняющие его функционирование.

Структура устройства, реализующего предлагаемый способ определения знака разности частот, показанная на фиг.2, содержит фазовый знако-модульный логический фазовый дискриминатор (ЗМЛФД) 1, первый 2, второй 3 и третий 4 элементы И-НЕ, первое дифференцирующее устройство 5, вырабатывающее импульсы в моменты переднего фронта импульсов, поступающих на его вход, второе дифференцирующее устройство 6, вырабатывающее импульсы при изменении каждого из уровней подаваемого на его вход импульсного колебания, первый 8 и второй 7 формирователи импульсов, элемент задержки 9, интегратор со сбросом 10, устройство выборки-хранения 11, вычитатель 12, компаратор напряжений 13, D-триггер 14 с записью сигнала по фронту колебания, подаваемого на его С-вход (динамический D-триггер).

Устройство определения знака разности частот работает следующим образом. На первый вход ЗМЛФД 1 поступает анализируемый импульсный сигнал хА (данный и последующие цитируемые сигналы показаны на фиг. 3, а) частотой ƒ1, а на его второй вход поступает второй импульсный сигнал хБ частотой ƒ2, используемый в качестве опорного сигнала. Оба этих сигнала имеют близкие частоты. На первом выходе ЗМЛФД 1 формируется сигнал  , отражающий положительный знак разности фаз, а на втором выходе формируется сигнал

, отражающий положительный знак разности фаз, а на втором выходе формируется сигнал  , отражающий отрицательный знак разности фаз. Третий и четвертый выходы ЗМЛФД, несут информацию о модуле положительной

, отражающий отрицательный знак разности фаз. Третий и четвертый выходы ЗМЛФД, несут информацию о модуле положительной  и отрицательной

и отрицательной  разностей фаз соответственно. Первый выход ЗМЛФД является первым выходом устройства, второй выход ЗМЛФД - вторым выходом устройства, третий выход ЗМЛФД - третьим выходом устройства, а четвертый выход ЗМЛФД - четвертым выходом устройства. Третий и четвертый выходы устройства подключены к входам первого элемента И-НЕ 2. На выходе элемента И-НЕ 2, выполняющего операцию ИЛИ над сигналами

разностей фаз соответственно. Первый выход ЗМЛФД является первым выходом устройства, второй выход ЗМЛФД - вторым выходом устройства, третий выход ЗМЛФД - третьим выходом устройства, а четвертый выход ЗМЛФД - четвертым выходом устройства. Третий и четвертый выходы устройства подключены к входам первого элемента И-НЕ 2. На выходе элемента И-НЕ 2, выполняющего операцию ИЛИ над сигналами  и

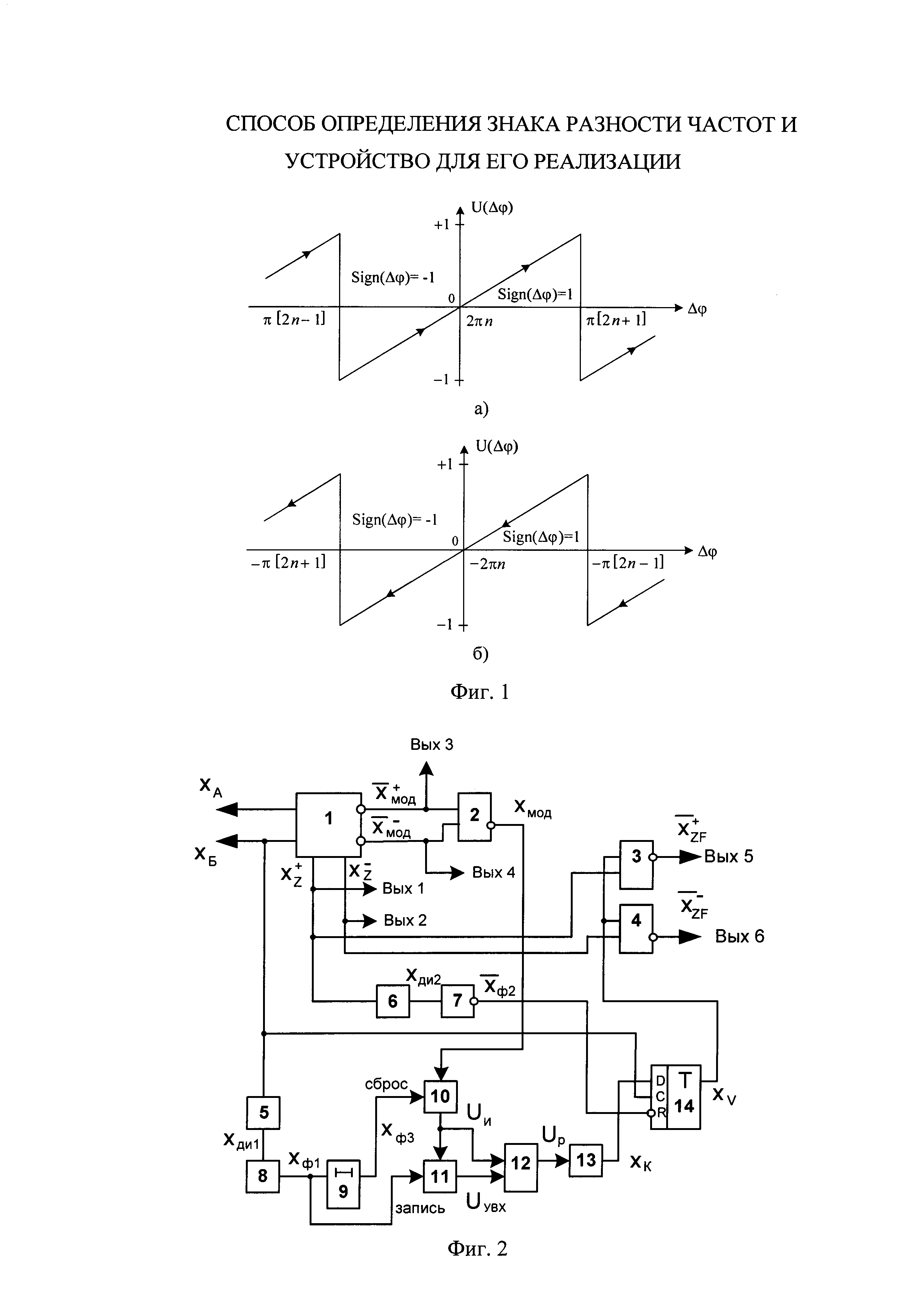

и  , формируется сигнал хмод. Выход элемента И-НЕ 2 подключен к информационному входу обнуляемого интегратора (ОИ) 10. Второй вход ЗМЛФД 1 связан с входами первого дифференцирующего устройства (ДУ) 5 и С-входом D-триггера 14. На выходе ДУ 5 вырабатывается последовательность импульсов хди1, которая подается на вход первого формирователя импульсов 8, выходной сигнал хф1 которого подается на вход линии задержки 9 и вход разрешения записи напряжения в устройство выборки-хранения (УВХ) 11. Выход линии задержки 9 соединен с входом сброса (обнуления) интегратора 10. Выход интегратора 10, подключен к положительному входу вычитателя 12, и информационному входу УВХ 11. Выход УВХ соединен с отрицательным входом вычитателя 12. Вычитатель формирует разность Up напряжений Uи с выхода интегратора 10 и Uyвх с выхода устройства выборки-хранения 11. Выход вычитателя 12 подключен к положительному входу компаратора 13, на отрицательный вход которого подается пороговое напряжение положительного уровня, близкого к нулю. Сигнал хк, формируемый на выходе компаратора, подается на D-вход триггера 14, вход R которого соединен с выходом второго формирователя импульсов 7. На R-вход D-триггера подается сигнал xф2. Вход второго формирующего устройства 7 подключен к выходу второго дифференцирующего устройства 6, вход которого соединен с первым выходом ЗМЛФД. На выходе второго дифференцирующего устройства 6 формируется сигнал хди2, состоящий из последовательности коротких импульсов, формируемых в момент изменения уровня подаваемого на его вход импульсного колебания. Схема такого дифференцирующего устройства может состоять из элемента задержки и сумматора по модулю 2 и иметь структуру, представленную на фиг. 4. Прямой выход D-триггера, формирующий сигнал xV, подключен к первым входам второго 3 и третьего 4 элементов И-НЕ, на вторые входы которых подаются сигналы

, формируется сигнал хмод. Выход элемента И-НЕ 2 подключен к информационному входу обнуляемого интегратора (ОИ) 10. Второй вход ЗМЛФД 1 связан с входами первого дифференцирующего устройства (ДУ) 5 и С-входом D-триггера 14. На выходе ДУ 5 вырабатывается последовательность импульсов хди1, которая подается на вход первого формирователя импульсов 8, выходной сигнал хф1 которого подается на вход линии задержки 9 и вход разрешения записи напряжения в устройство выборки-хранения (УВХ) 11. Выход линии задержки 9 соединен с входом сброса (обнуления) интегратора 10. Выход интегратора 10, подключен к положительному входу вычитателя 12, и информационному входу УВХ 11. Выход УВХ соединен с отрицательным входом вычитателя 12. Вычитатель формирует разность Up напряжений Uи с выхода интегратора 10 и Uyвх с выхода устройства выборки-хранения 11. Выход вычитателя 12 подключен к положительному входу компаратора 13, на отрицательный вход которого подается пороговое напряжение положительного уровня, близкого к нулю. Сигнал хк, формируемый на выходе компаратора, подается на D-вход триггера 14, вход R которого соединен с выходом второго формирователя импульсов 7. На R-вход D-триггера подается сигнал xф2. Вход второго формирующего устройства 7 подключен к выходу второго дифференцирующего устройства 6, вход которого соединен с первым выходом ЗМЛФД. На выходе второго дифференцирующего устройства 6 формируется сигнал хди2, состоящий из последовательности коротких импульсов, формируемых в момент изменения уровня подаваемого на его вход импульсного колебания. Схема такого дифференцирующего устройства может состоять из элемента задержки и сумматора по модулю 2 и иметь структуру, представленную на фиг. 4. Прямой выход D-триггера, формирующий сигнал xV, подключен к первым входам второго 3 и третьего 4 элементов И-НЕ, на вторые входы которых подаются сигналы  и

и  с первого и второго выходов ЗМЛФД соответственно. Выход второго элемента И-НЕ является пятым выходом устройства, а выход третьего элемента И-НЕ - шестым выходом устройства. Сигналы

с первого и второго выходов ЗМЛФД соответственно. Выход второго элемента И-НЕ является пятым выходом устройства, а выход третьего элемента И-НЕ - шестым выходом устройства. Сигналы  и

и  , формируемые на пятом и шестом выходах устройства несут информацию о знаке разности частот:

, формируемые на пятом и шестом выходах устройства несут информацию о знаке разности частот:  - положительном, а

- положительном, а  - отрицательном.

- отрицательном.

Предлагаемое устройство, реализующее способ определения знака разности частот, работает следующим образом. Временные диаграммы, поясняющие функционирование заявляемого устройства при положительном значении Δƒ=ƒ1-ƒ2, приведены на фиг. 3. Фаза колебаний хА частотой ƒ1, поступающих на первый вход ЗМЛФД 1, сравниваются с фазой колебаний хБ частотой ƒ2, поступающих на второй (опорный) вход дискриминатора. Значения знаков отклонения фазы колебания хА от фазы колебания хБ отображаются уровнями логической единицы на первом и втором выходах ЗМЛФД 1 в виде процессов  и

и  . Первое дифференцирующее устройство 5 формирует короткие импульсы xди1 в моменты перехода импульсов колебания хБ из уровня логического нуля в уровень логической единицы. Первым формирователем импульсов 8 на основе импульсов хди1 формируется последовательность импульсов хф1 с уровнем логической единицы. Импульсы xф1 поступают на вход разрешения перезаписи напряжения Uи, формируемого интегратором 10, в устройство выборки-хранения 11. Их длительность задается достаточной для выполнения перезаписи напряжения из интегратора в УВХ. Импульсы хф1, задерживаясь элементом задержки 11, на время длительности данных импульсов преобразуются в последовательность импульсов xф3, используемых для сброса (обнуления) интегратора. Импульсы хф3 с выхода элемента задержки 9 поступают на вход сброса (второй вход) интегратора 10. На первый (информационный) вход интегратора 10 подается сигнал xмод, формируемый с помощью первого элемента И-НЕ как операция ИЛИ над процессами

. Первое дифференцирующее устройство 5 формирует короткие импульсы xди1 в моменты перехода импульсов колебания хБ из уровня логического нуля в уровень логической единицы. Первым формирователем импульсов 8 на основе импульсов хди1 формируется последовательность импульсов хф1 с уровнем логической единицы. Импульсы xф1 поступают на вход разрешения перезаписи напряжения Uи, формируемого интегратором 10, в устройство выборки-хранения 11. Их длительность задается достаточной для выполнения перезаписи напряжения из интегратора в УВХ. Импульсы хф1, задерживаясь элементом задержки 11, на время длительности данных импульсов преобразуются в последовательность импульсов xф3, используемых для сброса (обнуления) интегратора. Импульсы хф3 с выхода элемента задержки 9 поступают на вход сброса (второй вход) интегратора 10. На первый (информационный) вход интегратора 10 подается сигнал xмод, формируемый с помощью первого элемента И-НЕ как операция ИЛИ над процессами  и

и  , формируемыми на третьем и четвертом (модульных) выходах ЗМЛФД 1.

, формируемыми на третьем и четвертом (модульных) выходах ЗМЛФД 1.

Для получения оценки приращений модулей разности фаз Δϕ напряжение Uи, формируемое интегратором 10 и запомненное значение напряжения Uи на предыдущем интервале анализа, выраженное как Uувх, подаются на положительный (+) и отрицательный (-) входы вычитателя 12 соответственно. Полученная на выходе вычитателя разность напряжений Up=Uи-Uувх поступает на положительный вход компаратора напряжения 13. На отрицательном входе компаратора устанавливается уровень порога в виде положительного постоянного напряжения, незначительно отличающегося от нуля. Порог устанавливается таким, чтобы в случае ƒ1=ƒ2, когда Uи≈Uувх и Up≈0, уровень сигнала xк на выходе компаратора поддерживался равным логическому нулю. Сигнал xк записывается в D-триггер 14 по переднему фронту колебаний сигнала xБ. Для этого С-вход триггера подключен к второму входу ЗМЛФД 1. Корректная работа предлагаемого устройства обеспечивается, когда запись информации в D-триггер запрещается сигналом обнуления xф2. Сигналы хф2 длительностью τ≈1.5Тр, (Tp=1/ƒ2) вырабатываются на основе импульсов хди2, формируемых при каждом изменении уровня сигнала  . Сигналы xф2 используются для удержания D-триггера в нулевом состоянии независимо от уровней сигналов, поступающих на его D- и С-входы.

. Сигналы xф2 используются для удержания D-триггера в нулевом состоянии независимо от уровней сигналов, поступающих на его D- и С-входы.

Запомненный D-триггером сигнал xк поступает на первые входы второго 3 и третьего 4 элементов И-НЕ, в которых осуществляется операция конъюнкции xк с  и

и  соответственно. На выходе элемента И-НЕ 3 уровнем логического нуля отображается положительный знак

соответственно. На выходе элемента И-НЕ 3 уровнем логического нуля отображается положительный знак  , а на выходе элемента И-НЕ 4 - уровнем логического нуля отображается отрицательный знак

, а на выходе элемента И-НЕ 4 - уровнем логического нуля отображается отрицательный знак  разности частот. Причем уровень логического нуля в определенный момент времени может принимать только один из сигналов

разности частот. Причем уровень логического нуля в определенный момент времени может принимать только один из сигналов  или

или  , другой в это время находится в состоянии логической единицы. Когда разность анализируемых частот равна нулю оба сигнала

, другой в это время находится в состоянии логической единицы. Когда разность анализируемых частот равна нулю оба сигнала  и

и  принимают уровень логической единицы.

принимают уровень логической единицы.

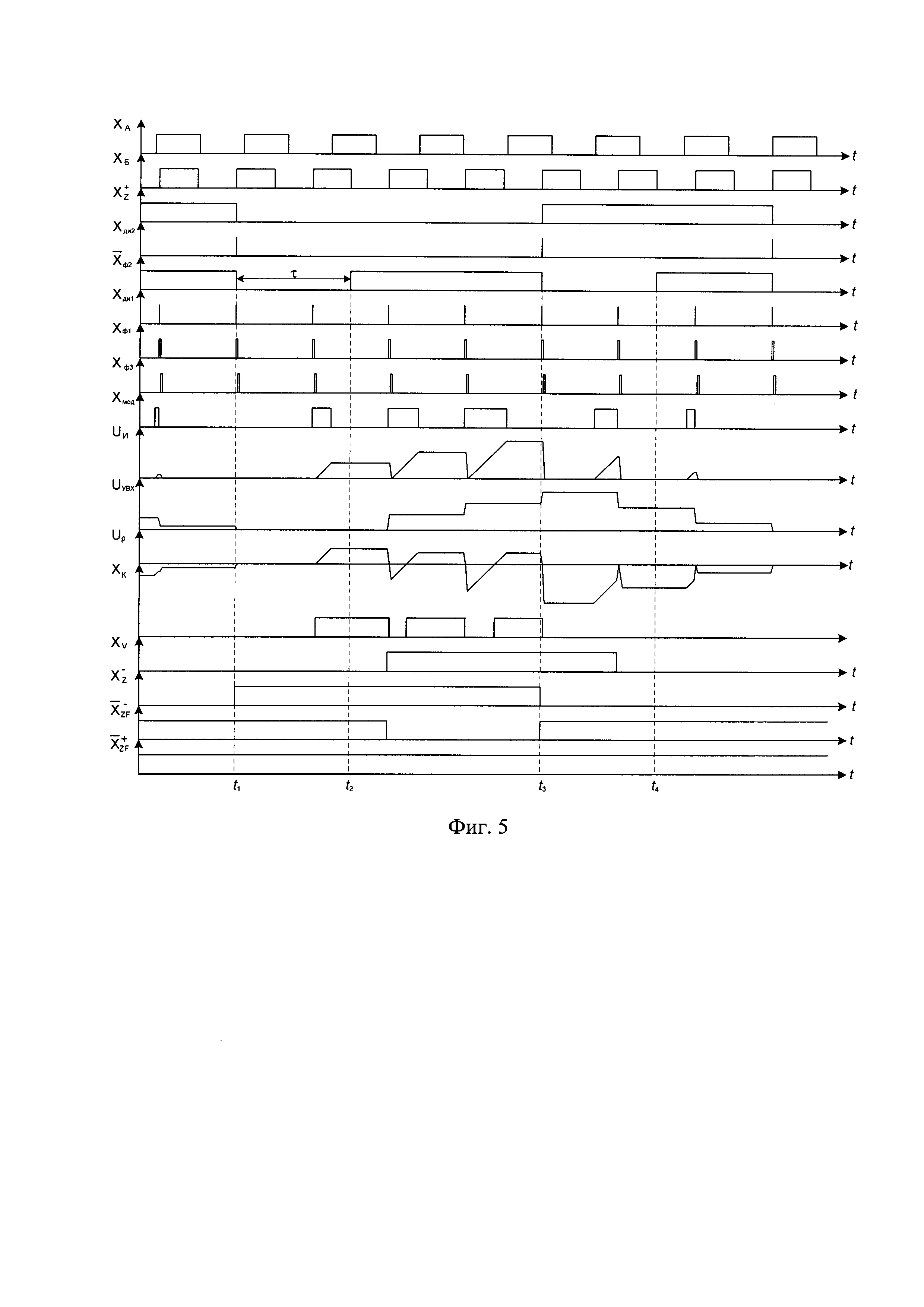

Временные диаграммы, поясняющие работу устройства определения знака разности частот при отрицательной разности частот (Δƒ<0), представлены на фиг. 5. Одноименные процессы на фиг. 3 и 5 обозначены одинаковыми символами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Прошин Е.М. Цифровые измерительные устройства: учебное пособие / Е.М. Прошин; Рязанский государственный радиотехнический университет. - Рязань: 2011, - 224 с.

2. Системы фазовой синхронизации с элементами дискретизации. 2-изд., доп. и перераб. / В.В. Шахгильдян, А.А. Ляховкин, В.Л. Карякин и др.; под ред. В.В. Шахгильдяна. М.: Радио и связь, 1989. - 320 с.

3. Одиноков В.Ф. Цифровой дискриминатор кратных частот // Радиотехника. 1986. №11. С. 30-34.

4. Цифровые системы фазовой синхронизации / М.И. Жодзишский, С.Ю. Сила-Новицкий, В.А. Прасолов и др., под ред. М.И. Жодзишского. - М.: Сов. Радио, 1980. - 208 с.

5. АС 1432724 СССР, МКИ H03D 13/00, G01R 25/00. Фазовый дискриминатор / В.Ф. Одиноков, С.И. Холопов. №4212180/24-09; заявлено 19.03.87; опубл. 23.10.88 в Б.И. №39.

6. АС 1568207 СССР, МКИ H03D 13/00. Фазовый дискриминатор / В.Ф. Одиноков, С.И. Холопов. №4374505; заявлено 05.02.88; опубл. 30.05.90 в БИ №20.

7. Патент РФ 2541899, МКП H03D 13/00. Фазовый дискриминатор / С.И. Холопов. №2013157154/08; заявлено 23.12.2013; опубл. 20.02.2015 в бюл. №5.