Результат интеллектуальной деятельности: ДИФФЕРЕНЦИАЛЬНЫЙ ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ

Вид РИД

Изобретение

Изобретение относится к области аналоговой усилительной техники и может быть использовано в качестве драйвера, обеспечивающего передачу дифференциальных сигналов по двухпроводным линиям связи, а также в виде усилителя выходных сигналов классических мостовых измерительных систем.

В современных устройствах передачи информации и датчиковых системах находят применение дифференциальные инструментальные усилители (ИУ) с парафазным выходом, обеспечивающие усиление аналоговых и цифровых дифференциальных сигналов [1-27].

Известны драйверы дифференциальных линий связи на основе классических операционных усилителей с парафазным выходом, коэффициент передачи которых выбирается исходя из затухания сигнала в линии связи и определяется резисторами двухканальной отрицательной обратной связи [1-12].

Известны ИУ для работы с дифференциальными линиями связи, реализуемые на основе серийных микросхем мультидифференциальных операционных усилителей (МОУ), в которых с помощью резисторов вводится двухканальная отрицательная обратная связь [13-17, 18 (fig. 4, fig. 8d), 19-20]. Данные ИУ могут обеспечить необходимое усиление входного сигнала (1,5-2 раза). Однако они требуют применения внешних (по отношению к микросхеме) резисторов, которые включаются между входами и парафазными выходами микросхемы МОУ. Следует заметить, что сегодня ведущими микроэлектронными фирмами мира выпускаются более 20 типов микросхем МОУ.

Известны инструментальные усилители (ИУ) и драйверы дифференциальных линий связи на их основе, реализуемые на базе МОУ, которые не содержат резисторов отрицательной обратной связи [21-22, 18 (fig. 8b), 23-26]. В устройствах данного подкласса парафазные выходы МОУ связаны с его парафазными входами непосредственно - без каких-либо пассивных элементов. Это положительно сказывается на ряде статических и динамических характеристик ИУ (диапазоне рабочих частот, напряжении смещения нуля, быстродействии, шумах и т.д.). Предлагаемый дифференциальный инструментальный усилитель относится к данному подклассу аналоговых преобразователей сигналов.

Ближайшим прототипом заявляемого устройства является дифференциальный инструментальный усилитель с парафазным выходом (фиг. 1), представленный в статье Duque-Carrillo J., Torelli G., Perez-Aloe R. Valverde J., Maloberti F. "Fully differential basic bulding blocks based on fully differential difference amplifiers with unity-gain difference feddback," IEEE Trans. Circuits Syst.-I, vol. 42, No. 3, March 1995, p. 191, fig. 1, fig. 2a. Кроме этого данное техническое решение описано в статье [27] (при введении 100% отрицательной обратной связи), а также в работах [21, 23-26]. Он содержит (фиг. 1) неинвертирующий вход 1 устройства и синфазный ему неинвертирующий выход 2 устройства, инвертирующий вход 3 устройства и синфазный ему инвертирующий выход 4 устройства, первый 5 входной дифференциальный каскад, инвертирующий вход 6 которого соединен с неинвертирующим выходом 2 устройства, а неинвертирующий вход 7 соединен с инвертирующим выходом 4 устройства, второй 8 входной дифференциальный каскад, неинвертирующий вход 9 которого подключен к неинвертирующему входу 1 устройства, а инвертирующий вход 10 соединен с инвертирующим входом 3 устройства, первый 11 токовый выход первого 5 входного дифференциального каскада соединен с первым 12 токовым выходом второго 8 входного дифференциального каскада и подключен к первому 13 входу выходного дифференциального каскада 14, второй 15 токовый выход первого 5 входного дифференциального каскада соединен со вторым 16 токовым выходом второго 8 входного дифференциального каскада и подключен ко второму 17 входу выходного дифференциального каскада 14, неинвертирующий выход 2 устройства и инвертирующий выход 4 устройства соединены с соответствующими первым 18 и вторым 19 выходами выходного дифференциального каскада 14, причем первый 11 токовый выход первого 5 входного дифференциального каскада и первый 12 токовый выход второго 8 входного дифференциального каскада синфазны относительно соответствующих неинвертирующих входов 7 и 9 первого 5 и второго 8 входных дифференциальных каскадов, первый 11 и второй 15 токовые выходы первого 5 входного дифференциального каскада противофазны, первый 12 и второй 16 токовые выходы второго 8 входного дифференциального каскада противофазны, неинвертирующий вход 7 первого 5 входного дифференциального каскада и неинвертирующий выход 2 устройства синфазны, неинвертирующий вход 9 второго 8 входного дифференциального каскада и неинвертирующий выход 2 устройства синфазны, инвертирующий вход 3 устройства и инвертирующий выход 4 устройства синфазны, неинвертирующий выход 2 устройства и инвертирующий выход 4 устройства противофазны, инвертирующий вход 6 первого 5 входного дифференциального каскада и неинвертирущий выход 2 устройства противофазны, инвертирующий вход 10 второго 8 входного дифференциального каскада и неинвертирующий выход 2 устройства противофазны.

Существенный недостаток дифференциального инструментального усилителя-прототипа состоит в том, что без резисторов обратной связи он обеспечивает дифференциальный коэффициент передачи по напряжению (Ку) не более единицы. Это не позволяет, например, компенсировать потери сигнала в двухпроводной линии связи. С другой стороны, введение внешних резисторов в микросхему серийно выпускаемого мультидифференциального операционного усилителя (МОУ) не всегда целесообразно (появляются дополнительные шумы и наводки, увеличивается нестабильность напряжения смещения нуля, подчеркивается влияние разброса параметров резисторов на симметрию выходных сигналов и их нелинейные искажения и т.д.).

Основная задача предлагаемого изобретения состоит в получении коэффициента передачи по напряжению на уровне двух единиц (Ку=2) дифференциального инструментального усилителя при 100% отрицательной обратной связи, т.е. при отсутствии соответствующих резисторов. Это позволит скомпенсировать потери аналогового или цифрового сигналов при их передаче по двухпроводным линиям связи и не потребует включения внешних элементов к микросхеме МОУ.

Поставленная задача достигается тем, что в дифференциальном инструментальном усилителе с парафазным выходом фиг. 1, содержащем неинвертирующий вход 1 устройства и синфазный ему неинвертирующий выход 2 устройства, инвертирующий вход 3 устройства и синфазный ему инвертирующий выход 4 устройства, первый 5 входной дифференциальный каскад, инвертирующий вход 6 которого соединен с неинвертирующим выходом 2 устройства, а неинвертирующий вход 7 соединен с инвертирующим выходом 4 устройства, второй 8 входной дифференциальный каскад, неинвертирующий вход 9 которого подключен к неинвертирующему входу 1 устройства, а инвертирующий вход 10 соединен с инвертирующим входом 3 устройства, первый 11 токовый выход первого 5 входного дифференциального каскада соединен с первым 12 токовым выходом второго 8 входного дифференциального каскада и подключен к первому 13 входу выходного дифференциального каскада 14, второй 15 токовый выход первого 5 входного дифференциального каскада соединен со вторым 16 токовым выходом второго 8 входного дифференциального каскада и подключен ко второму 17 входу выходного дифференциального каскада 14, неинвертирующий выход 2 устройства и инвертирующий выход 4 устройства соединены с соответствующими первым 18 и вторым 19 выходами выходного дифференциального каскада 14, причем первый 11 токовый выход первого 5 входного дифференциального каскада и первый 12 токовый выход второго 8 входного дифференциального каскада синфазны относительно соответствующих неинвертирующих входов 7 и 9 первого 5 и второго 8 входных дифференциальных каскадов, первый 11 и второй 15 токовые выходы первого 5 входного дифференциального каскада противофазны, первый 12 и второй 16 токовые выходы второго 8 входного дифференциального каскада противофазны, неинвертирующий вход 7 первого 5 входного дифференциального каскада и неинвертирующий выход 2 устройства синфазны, неинвертирующий вход 9 второго 8 входного дифференциального каскада и неинвертирующий выход 2 устройства синфазны, инвертирующий вход 3 устройства и инвертирующий выход 4 устройства синфазны, неинвертирующий выход 2 устройства и инвертирующий выход 4 устройства противофазны, инвертирующий вход 6 первого 5 входного дифференциального каскада и неинвертирущий выход 2 устройства противофазны, инвертирующий вход 10 второго 8 входного дифференциального каскада и неинвертирующий выход 2 устройства противофазны, предусмотрены новые элементы и связи - в схему введен дополнительный дифференциальный каскад 20, неинвертирующий вход 21 которого соединен с неинвертирующим 1 входом устройства, инвертирующий вход 22 дополнительного дифференциального каскада 20 подключен к инвертирующему 3 входу устройства, первый 23 токовый выход дополнительного дифференциального каскада 20 связан с первым 12 токовым выходом второго 8 входного дифференциального каскада, а второй 24 токовый выход дополнительного дифференциального каскада 20 связан со вторым 16 токовым выходом второго 8 входного дифференциального каскада, причем неинвертирующий вход 21 дополнительного дифференциального каскада 20 синфазен с неинвертирующим выходом 2 устройства, а инвертирующий вход 22 синфазен с инвертирующим выходом 4 устройства, первый 23 токовый выход дополнительного дифференциального каскада 20 синфазен с первым 12 токовым выходом второго 8 входного дифференциального каскада, а второй 24 токовый выход дополнительного дифференциального каскада 20 синфазен со вторым 16 токовым выходом второго 8 входного дифференциального каскада.

На фиг. 1 показана схема дифференциального инструментального усилителя - прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

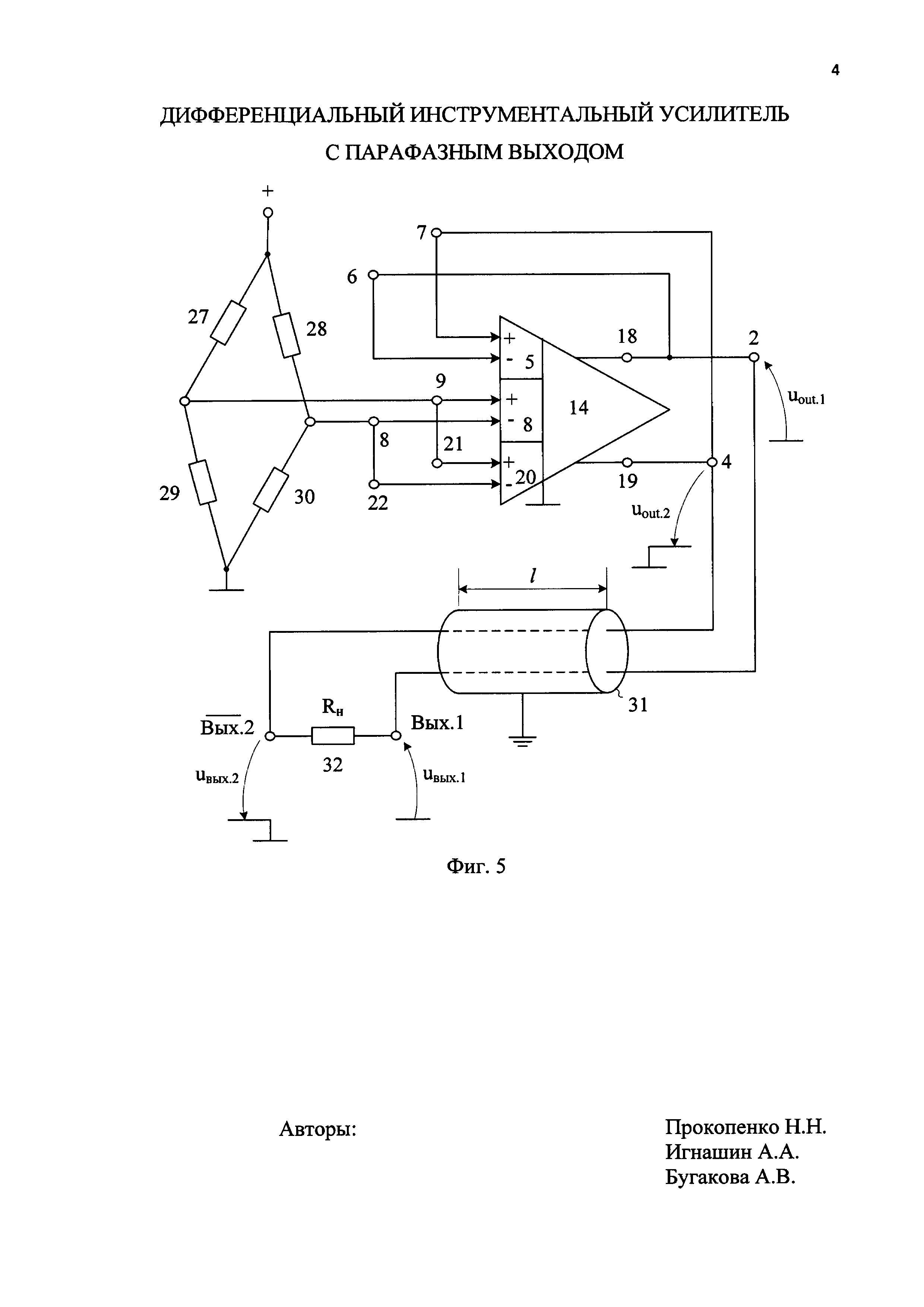

На фиг. 3 представлено условное обозначение дифференциального инструментального усилителя-прототипа, соответствующее схеме фиг. 1, которое широко применяется в технической литературе.

На фиг. 4 представлено условное обозначение заявляемого устройства, соответствующее фиг. 2.

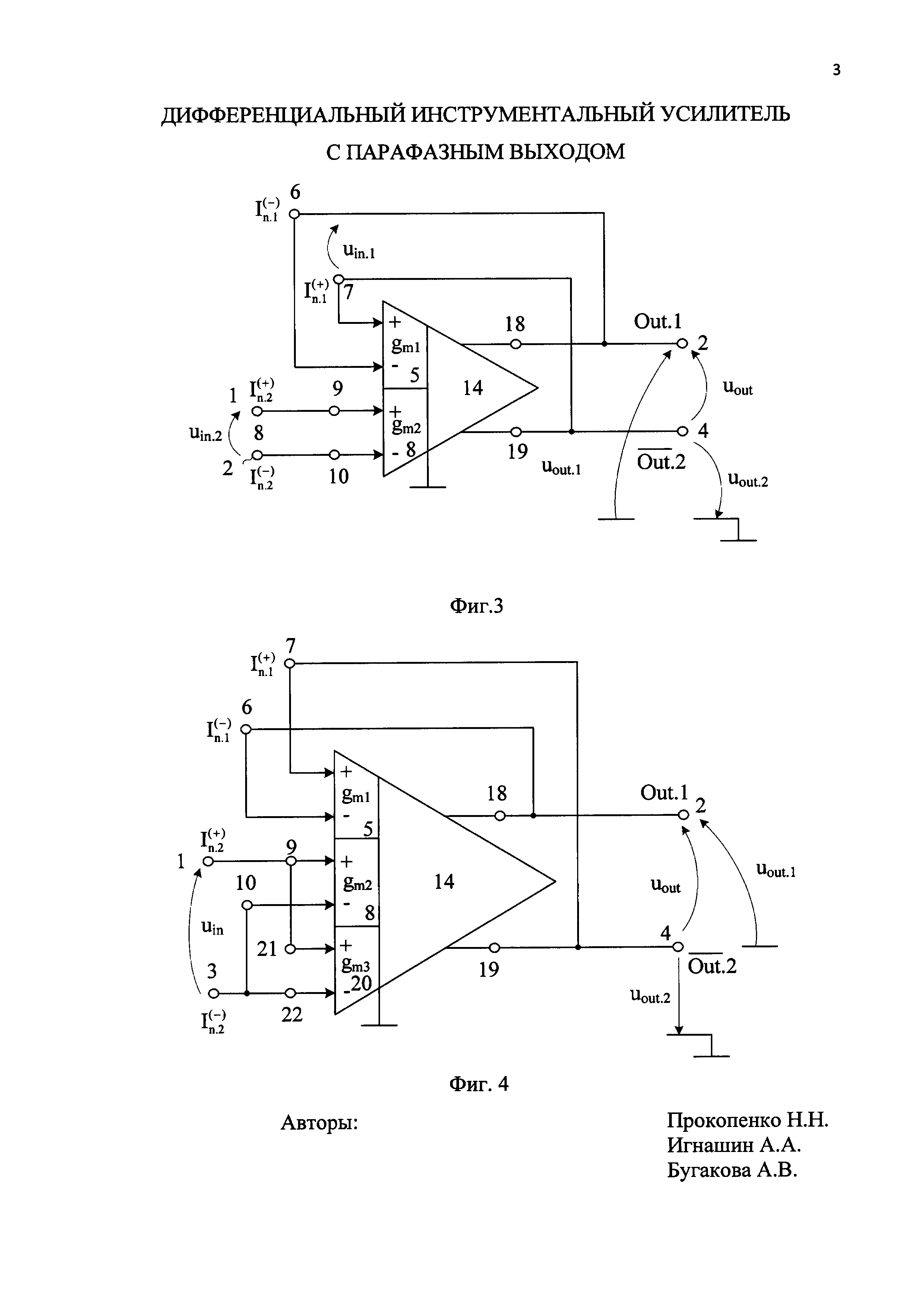

На фиг. 5 показан пример включения заявляемого дифференциального инструментального усилителя в классической мостовой измерительной схеме с дистанционным включением нагрузки по двухпроводной линии связи.

Дифференциальный инструментальный усилитель с парафазным выходом фиг. 2 содержит неинвертирующий вход 1 устройства и синфазный ему неинвертирующий выход 2 устройства, инвертирующий вход 3 устройства и синфазный ему инвертирующий выход 4 устройства, первый 5 входной дифференциальный каскад, инвертирующий вход 6 которого соединен с неинвертирующим выходом 2 устройства, а неинвертирующий вход 7 соединен с инвертирующим выходом 4 устройства, второй 8 входной дифференциальный каскад, неинвертирующий вход 9 которого подключен к неинвертирующему входу 1 устройства, а инвертирующий вход 10 соединен с инвертирующим входом 3 устройства, первый 11 токовый выход первого 5 входного дифференциального каскада соединен с первым 12 токовым выходом второго 8 входного дифференциального каскада и подключен к первому 13 входу выходного дифференциального каскада 14, второй 15 токовый выход первого 5 входного дифференциального каскада соединен со вторым 16 токовым выходом второго 8 входного дифференциального каскада и подключен ко второму 17 входу выходного дифференциального каскада 14, неинвертирующий выход 2 устройства и инвертирующий выход 4 устройства соединены с соответствующими первым 18 и вторым 19 выходами выходного дифференциального каскада 14, причем первый 11 токовый выход первого 5 входного дифференциального каскада и первый 12 токовый выход второго 8 входного дифференциального каскада синфазны относительно соответствующих неинвертирующих входов 7 и 9 первого 5 и второго 8 входных дифференциальных каскадов, первый 11 и второй 15 токовые выходы первого 5 входного дифференциального каскада противофазны, первый 12 и второй 16 токовые выходы второго 8 входного дифференциального каскада противофазны, неинвертирующий вход 7 первого 5 входного дифференциального каскада и неинвертирующий выход 2 устройства синфазны, неинвертирующий вход 9 второго 8 входного дифференциального каскада и неинвертирующий выход 2 устройства синфазны, инвертирующий вход 3 устройства и инвертирующий выход 4 устройства синфазны, неинвертирующий выход 2 устройства и инвертирующий выход 4 устройства противофазны, инвертирующий вход 6 первого 5 входного дифференциального каскада и неинвертирущий выход 2 устройства противофазны, инвертирующий вход 10 второго 8 входного дифференциального каскада и неинвертирующий выход 2 устройства противофазны. В схему введен дополнительный дифференциальный каскад 20, неинвертирующий вход 21 которого соединен с неинвертирующим 1 входом устройства, инвертирующий вход 22 дополнительного дифференциального каскада 20 подключен к инвертирующему 3 входу устройства, первый 23 токовый выход дополнительного дифференциального каскада 20 связан с первым 12 токовым выходом второго 8 входного дифференциального каскада, а второй 24 токовый выход дополнительного дифференциального каскада 20 связан со вторым 16 токовым выходом второго 8 входного дифференциального каскада, причем неинвертирующий вход 21 дополнительного дифференциального каскада 20 синфазен с неинвертирующим выходом 2 устройства, а инвертирующий вход 22 синфазен с инвертирующим выходом 4 устройства, первый 23 токовый выход дополнительного дифференциального каскада 20 синфазен с первым 12 токовым выходом второго 8 входного дифференциального каскада, а второй 24 токовый выход дополнительного дифференциального каскада 20 синфазен со вторым 16 токовым выходом второго 8 входного дифференциального каскада.

В схеме фиг. 2 выходной дифференциальный каскад 14 реализован на основе повторителей напряжения 25 и 26 с единичным коэффициентом усиления. В других случаях данный функциональный узел может быть реализован на основе известных каскадов усиления аналоговых сигналов, в т.ч. инвертирующих.

На фиг. 5 показан пример применения предлагаемого устройства в составе классического измерительного моста с сенсорными элементами 27, 28, 29, 30, в качестве которых могут применяться резистивные, магниторезистивные и другие датчики. В данной схеме первый 2 и второй 4 выходы заявляемого устройства соединены через двухпроводную линию связи 21 с цепью удаленной нагрузки 32.

Рассмотрим работу ИУ-прототипа фиг. 1.

На основе второго закона Кирхгофа можно составить следующие уравнения для схемы фиг. 1:

где KБУi - коэффициент передачи по напряжению i-го буферного усилителя БУ1 (БУ2), входящего в выходной дифференциальный каскад 14;

uΣ1, uΣ2 - напряжения в высокоимпедансных узлах Σ1, Σ2;

uout.1 - выходное напряжение для первого 2 выхода (Out.1) устройства;

uout.2 - выходное напряжение для второго 4 противофазного выхода (Out.2) устройства;

uout - дифференциальное выходное напряжение между выходами Out.1 (2) и Out.2 (4).

Для высокоимпедансных узлов Σ1, Σ2 можно определить, что

где RΣ1, RΣ2 - эквивалентные выходные сопротивления в высокоимпедансных узлах Σ1, Σ2,

gmi - проводимость передачи i-го (первого 5 и второго 8 входных дифференциальных каскадов).

После преобразований формулы (4) и (5) находим взаимосвязь uout и uin.2:

Таким образом, коэффициент передачи по напряжению рассматриваемой схемы ИУ-прототипа:

Если gm1=gm2=gm, KБУ1=KБУ2=KБУ, RΣ1=RΣ2=RΣ, то

где T=KБУRΣgm - петлевое усиление.

При Т>>1 коэффициенты передачи для дифференциального (Ку) и недифференциального (Ку1, Ку2) выходов:

Таким образом, для недифференциального сигнала известное устройство дает не усиление, а ослабление входного сигнала (Ky1=Ky2=0,5), а для дифференциального выхода его коэффициент передачи Kу не превышает единицы (9). Это не позволяет компенсировать потери сигналов в двухпроводной линии связи.

Выполним далее анализ схемы заявляемого устройства фиг. 2.

На основе закона Кирхгофа можно составить следующие основные уравнения для схемы фиг. 2:

где KБУi - коэффициент передачи по напряжению i-го буферного усилителя БУ1 (БУ2), входящего в выходной дифференциальный каскад 14.

uΣ1, uΣ2 - напряжения в высокоимпедансных узлах Σ1, Σ2;

uout.1 - выходное напряжение для первого 2 выхода (Out.1) устройства;

uout.2 - выходное напряжение для второго 4 противофазного выхода (Out.2) устройства;

uout - дифференциальное выходное напряжение между выходами Out.1 (2) и Out.2 (4).

Из (11)-(13) можно определить, что напряжения в высокоимпедансных узлах Σ1, Σ2

где RΣ1, RΣ2 - эквивалентные выходные сопротивления в высокоимпедансных узлах Σ1, Σ2,

gmi - проводимость передачи i-го входного дифференциального каскада (5, 8, 20).

После преобразований формул (14) и (15) находим взаимосвязь uout и uin.2:

Таким образом, коэффициент передачи по напряжению заявляемой схемы ИУ:

Если gm1=gm2=gm3=gm, KБУ1=KБУ2=KБУ, RΣ1=RΣ2=RΣ, то

где T=KБУRΣgm - петлевое усиление.

При Т>>1 коэффициенты передачи для дифференциального (Ку) и недифференциального (Ку1, Ку2) выходов заявляемого устройства:

Таким образом, дифференциальный коэффициент передачи по напряжению заявляемого устройства, которое не содержит резисторов отрицательной обратной связи, близок к двум единицам.

Кроме этого исключение внешних резисторов улучшает ряд статических и динамических параметров предлагаемого дифференциального инструментального усилителя - расширяет его диапазон рабочих частот, уменьшает напряжение смещения нуля и шумы, повышает быстродействие в режиме большого сигнала, исключает асимметрию выходных сигналов и их нелинейные искажения из-за разброса параметров резисторов обратной связи и т.д.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Design of Bipolar Differential OpAmps with Unity Gain Bandwidth up to 23 GHz / A. Budyakov, K. Schmalz, N. Prokopenko, C. Scheytt, P. Ostrovskyy, // Proceeding of the 4-th European Conference on Circuits and Systems for Communications - ECCSC'08 / Politehnica University, Bucharest, Romania: July 10-11, 2008. - pp. 50-53.

2. Патент US 6.323.734, fig. 2.

3. Патент US 5.166.635, fig. 1.

4. Патент US 6.329.876, fig. 4.

5. Патент US 6.566.946, fig. 4.

6. Патент US 6.975.171, fig. 3.

7. Патент US 6.919.768, fig. 3.

8. Патент US 6.876.256, fig. 3.

9. Патентная заявка US 2015/0236661, fig. 1.

10. Патент US 6.359.505, fig. 3.

11. Патентная заявка US 2009/0134940, fig. 1.

12. Патентная заявка US 2011/0150245, fig. 1.

13. Патент US 5.861.778.

14. Патент US 6.011.436 fig. 21, fig. 22.

15. Патент EP 1083655, fig. 8.

16. R. Wu, J.H. Huijsing and K.A.A. Makinwa, "A current-feedback instrumentation amplifier with a gain error reduction loop and 0.06% untrimmed gain error," Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011 IEEE International, San Francisco, CA, 2011, pp. 244-246. DOI: 10.1109/ISSCC. 2011. 5746303, fig. 1.

17. P. Bruschi, F. Del Cesta, A.N. Longhitano, M. Piotto and R. Simmarano, "A very compact CMOS instrumentation amplifier with nearly rail-to-rail input common mode range," European Solid State Circuits Conference (ESSCIRC), ESSCIRC 2014 - 40th, Venice Lido, 2014, pp. 323-326. DOI: 10.1109/ESSCIRC.2014.6942087 fig. 1.

18. H. Alzaher and M. Ismail, "A CMOS fully balanced differential difference amplifier and its applications," in IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 48, no. 6, pp. 614-620, Jun 2001. DOI: 10.1109/82.943332, fig. 4, fig. 8b, fig. 8d.

19. Патент US 6.781.464, fig. 3.

20. Патентная заявка US 2014/0145785, fig. 3b.

21. Заявка на патент US 2003/0137345 fig. 2.

22. J.F. Duque-Carrillo, G. Torelli, R. Perez-Aloe, J.M. Valverde and F. Maloberti, "Fully differential basic building blocks based on fully differential difference amplifiers with unity-gain difference feedback," in IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 42, no. 3, pp. 190-192, Mar 1995. DOI: 10.1109/81.376865, fig. 2.

23. Патент US 6.833.756, fig. 2.

24. Патент US 6.943.622, fig. 2.

25. Патент WO 03/063340, fig. 2.

26. Патентная заявка US 2005/0093623, fig. 2.

27. Rong Wu, Huijsing J.H., Makinwa K.A.A. A Current-Feedback Instrumentation Amplifier With a Gain Error Reduction Loop and 0.06% Untrimmed Gain Error // Solid-State Circuits, IEEE Journal of - Year: 2011, Volume: 46, Issue: 12, pp. 2794-2806, DOI: 10.1109/JSSC.2011.2162923, fig. 1.

Дифференциальный инструментальный усилитель с парафазным выходом, содержащий неинвертирующий вход (1) устройства и синфазный ему неинвертирующий выход (2) устройства, инвертирующий вход (3) устройства и синфазный ему инвертирующий выход (4) устройства, первый (5) входной дифференциальный каскад, инвертирующий вход (6) которого соединен с неинвертирующим выходом (2) устройства, а неинвертирующий вход (7) соединен с инвертирующим выходом (4) устройства, второй (8) входной дифференциальный каскад, неинвертирующий вход (9) которого подключен к неинвертирующему входу (1) устройства, а инвертирующий вход (10) соединен с инвертирующим входом (3) устройства, первый (11) токовый выход первого (5) входного дифференциального каскада соединен с первым (12) токовым выходом второго (8) входного дифференциального каскада и подключен к первому (13) входу выходного дифференциального каскада (14), второй (15) токовый выход первого (5) входного дифференциального каскада соединен со вторым (16) токовым выходом второго (8) входного дифференциального каскада и подключен ко второму (17) входу выходного дифференциального каскада (14), неинвертирующий выход (2) устройства и инвертирующий выход (4) устройства соединены с соответствующими первым (18) и вторым (19) выходами выходного дифференциального каскада (14), причем первый (11) токовый выход первого (5) входного дифференциального каскада и первый (12) токовый выход второго (8) входного дифференциального каскада синфазны относительно соответствующих неинвертирующих входов (7) и (9) первого (5) и второго (8) входных дифференциальных каскадов, первый (11) и второй (15) токовые выходы первого (5) входного дифференциального каскада противофазны, первый (12) и второй (16) токовые выходы второго (8) входного дифференциального каскада противофазны, неинвертирующий вход (7) первого (5) входного дифференциального каскада и неинвертирующий выход (2) устройства синфазны, неинвертирующий вход (9) второго (8) входного дифференциального каскада и неинвертирующий выход (2) устройства синфазны, инвертирующий вход (3) устройства и инвертирующий выход (4) устройства синфазны, неинвертирующий выход (2) устройства и инвертирующий выход (4) устройства противофазны, инвертирующий вход (6) первого (5) входного дифференциального каскада и неинвертирущий выход (2) устройства противофазны, инвертирующий вход (10) второго (8) входного дифференциального каскада и неинвертирующий выход (2) устройства противофазны, отличающийся тем, что в схему введен дополнительный дифференциальный каскад (20), неинвертирующий вход (21) которого соединен с неинвертирующим (1) входом устройства, инвертирующий вход (22) дополнительного дифференциального каскада (20) подключен к инвертирующему (3) входу устройства, первый (23) токовый выход дополнительного дифференциального каскада (20) связан с первым (12) токовым выходом второго (8) входного дифференциального каскада, а второй (24) токовый выход дополнительного дифференциального каскада (20) связан со вторым (16) токовым выходом второго (8) входного дифференциального каскада, причем неинвертирующий вход (21) дополнительного дифференциального каскада (20) синфазен с неинвертирующим выходом (2) устройства, а инвертирующий вход (22) синфазен с инвертирующим выходом (4) устройства, первый (23) токовый выход дополнительного дифференциального каскада (20) синфазен с первым (12) токовым выходом второго (8) входного дифференциального каскада, а второй (24) токовый выход дополнительного дифференциального каскада (20) синфазен со вторым (16) токовым выходом второго (8) входного дифференциального каскада.