Результат интеллектуальной деятельности: RS-ТРИГГЕР

Вид РИД

Изобретение

Предлагаемое изобретение относится к области вычислительной техники, автоматики, связи и может использоваться в специализированных цифровых структурах, системах автоматического управления и передачи цифровой информации.

В различных цифровых и аналого-цифровых вычислительных и управляющих устройствах широко используются классические RS-триггеры [1-34], входными и выходными логическими сигналами которых являются заданные уровни напряжений (высокий - соответствующий логической единице «1», низкий - логическому нулю «0»). На базе данных функциональных узлов сегодня реализуется 95-98% компьютеров различного назначения. Однако традиционные средства вычислительной техники, основой которых является булева алгебра, достигли сегодня предельных возможностей по быстродействию и способности обеспечить надежную работу в условиях дестабилизирующих факторов.

В работе [35], а также монографиях соавтора настоящей заявки [36, 37] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является не заданное напряжение, а заданный квант тока. Заявляемое устройство относится к этому типу устройств.

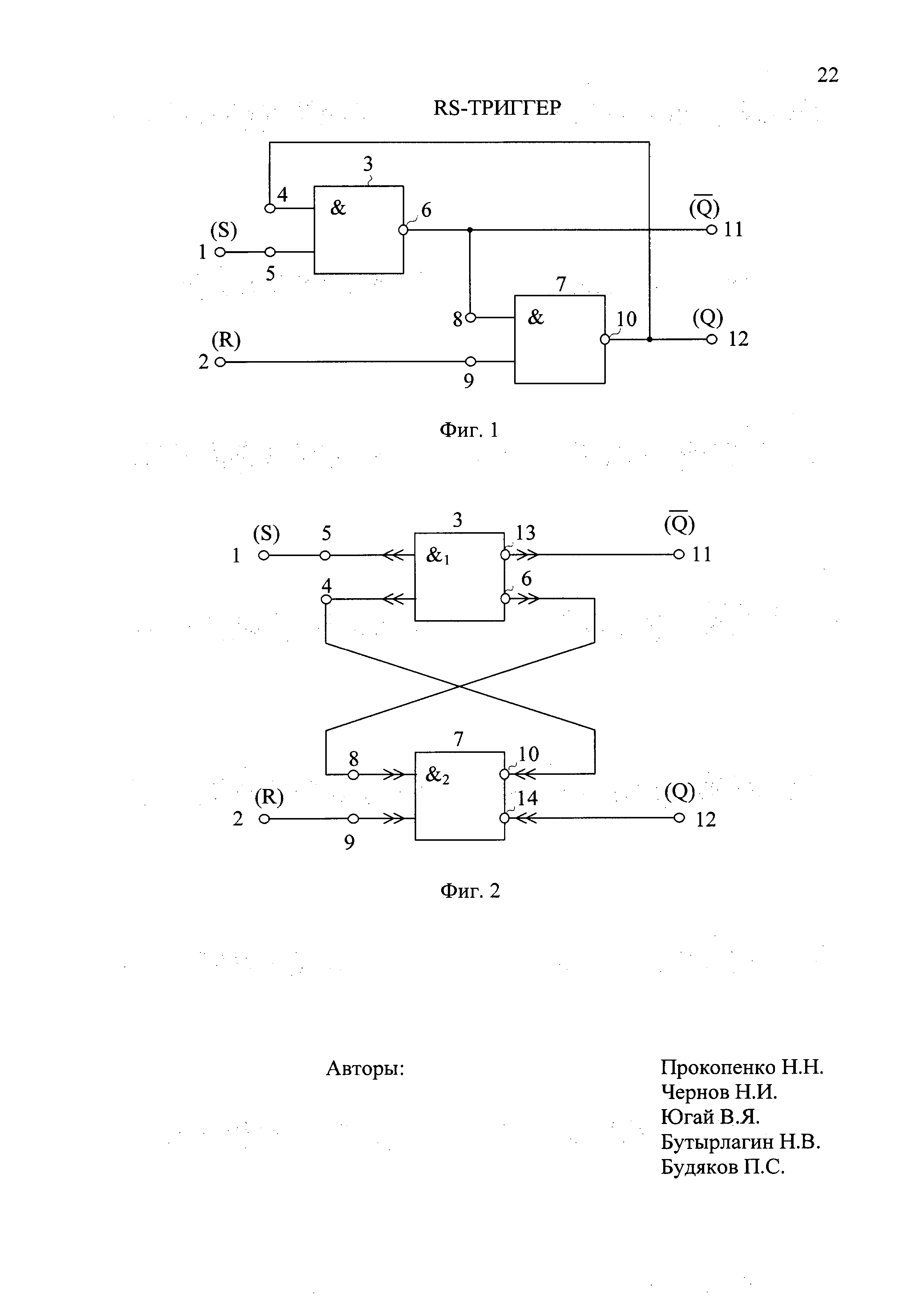

Ближайшим прототипом заявляемого устройства является классический RS-триггер, используемый в патенте US 8.232.825, fig. 9, структура которого присутствует во многих других патентах [1-34]. Он содержит первый 1 (S) и второй 2 (R) логические входы устройства, первый 3 инвертирующий логический элемент «И» с первым 4 и вторым 5 логическими входами первого 3 инвертирующего логического элемента «И», а также первым 6 выходом первого 3 инвертирующего логического элемента «И», второй 7 инвертирующий логический элемент «И» с первым 8 и вторым 9 логическими входами второго 7 инвертирующего логического элемента «И», а также вторым 10 выходом второго 7 инвертирующего логического элемента «И», причем первый 6 выход первого 3 инвертирующего логического элемента «И» связан с первым 8 логическим входом второго 7 инвертирующего логического элемента «И», первый 10 выход второго 7 инвертирующего логического элемента «И» соединен с первым 4 логическим входом первого 3 инвертирующего логического элемента «И», противофазные первый  и второй 12 (Q) логические выходы устройства, причем первый 1 (S) логический вход устройства соединен со вторым 5 логическим входом первого 3 инвертирующего логического элемента «И», второй 2 (R) логический вход устройства соединен со вторым 9 логическим входом второго 7 инвертирующего логического элемента «И».

и второй 12 (Q) логические выходы устройства, причем первый 1 (S) логический вход устройства соединен со вторым 5 логическим входом первого 3 инвертирующего логического элемента «И», второй 2 (R) логический вход устройства соединен со вторым 9 логическим входом второго 7 инвертирующего логического элемента «И».

Существенный недостаток известного устройства состоит в том, что он функционирует в базисе элементов потенциальной логики - его входными и выходными логическими сигналами является высокий (единица состояния) или низкий (ноль состояния) потенциал. Это не позволяет создать на его основе полный базис средств специальной вычислительной техники, функционирующих на принципах преобразования многозначных токовых сигналов.

Основная задача предлагаемого изобретения состоит в создании RS-триггера, в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов. В конечном итоге это позволяет повысить быстродействие специальных систем обработки информации и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [35-37].

Поставленная задача решается тем, что в RS-триггере (фиг. 1), содержащем первый 1 (S) и второй 2 (R) логические входы устройства, первый 3 инвертирующий логический элемент «И» с первым 4 и вторым 5 логическими входами первого 3 инвертирующего логического элемента «И», а также первым 6 выходом первого 3 инвертирующего логического элемента «И», второй 7 инвертирующий логический элемент «И» с первым 8 и вторым 9 логическими входами второго 7 инвертирующего логического элемента «И», а также вторым 10 выходом второго 7 инвертирующего логического элемента «И», причем первый 6 выход первого 3 инвертирующего логического элемента «И» связан с первым 8 логическим входом второго 7 инвертирующего логического элемента «И», первый 10 выход второго 7 инвертирующего логического элемента «И» соединен с первым 4 логическим входом первого 3 инвертирующего логического элемента «И», противофазные первый  и второй 12 (Q) логические выходы устройства, причем первый 1 (S) логический вход устройства соединен со вторым 5 логическим входом первого 3 инвертирующего логического элемента «И», второй 2 (R) логический вход устройства соединен со вторым 9 логическим входом второго 7 инвертирующего логического элемента «И», предусмотрены новые элементы и связи - в качестве первого 3 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 4 и второй 5 логические входы первого 3 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют вытекающие входные токи, которые соответствуют входным логическим переменным, причем первый 6 выход первого 3 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет вытекающий выходной ток, в качестве второго 7 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 8 и второй 9 логические входы второго 7 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют втекающие входные токи, которые соответствуют входным логическим переменным, причем первый 10 выход второго 7 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет втекающий выходной ток, первый 3 инвертирующий Логический элемент «И» имеет дополнительный токовый выход 13 первого 3 инвертирующего логического элемента «И», синфазный с первым 6 токовым выходом первого 3 инвертирующего логического элемента «И» и подключенный к первому

и второй 12 (Q) логические выходы устройства, причем первый 1 (S) логический вход устройства соединен со вторым 5 логическим входом первого 3 инвертирующего логического элемента «И», второй 2 (R) логический вход устройства соединен со вторым 9 логическим входом второго 7 инвертирующего логического элемента «И», предусмотрены новые элементы и связи - в качестве первого 3 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 4 и второй 5 логические входы первого 3 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют вытекающие входные токи, которые соответствуют входным логическим переменным, причем первый 6 выход первого 3 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет вытекающий выходной ток, в качестве второго 7 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 8 и второй 9 логические входы второго 7 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют втекающие входные токи, которые соответствуют входным логическим переменным, причем первый 10 выход второго 7 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет втекающий выходной ток, первый 3 инвертирующий Логический элемент «И» имеет дополнительный токовый выход 13 первого 3 инвертирующего логического элемента «И», синфазный с первым 6 токовым выходом первого 3 инвертирующего логического элемента «И» и подключенный к первому  логическому выходу устройства, второй 7 инвертирующий логический элемент «И» имеет дополнительный токовый выход 14 второго 7 инвертирующего логического элемента «И», синфазный с первым 10 токовым выходом второго 7 инвертирующего логического элемента «И» и подключенный ко второму 12 (Q) логическому выходу устройства.

логическому выходу устройства, второй 7 инвертирующий логический элемент «И» имеет дополнительный токовый выход 14 второго 7 инвертирующего логического элемента «И», синфазный с первым 10 токовым выходом второго 7 инвертирующего логического элемента «И» и подключенный ко второму 12 (Q) логическому выходу устройства.

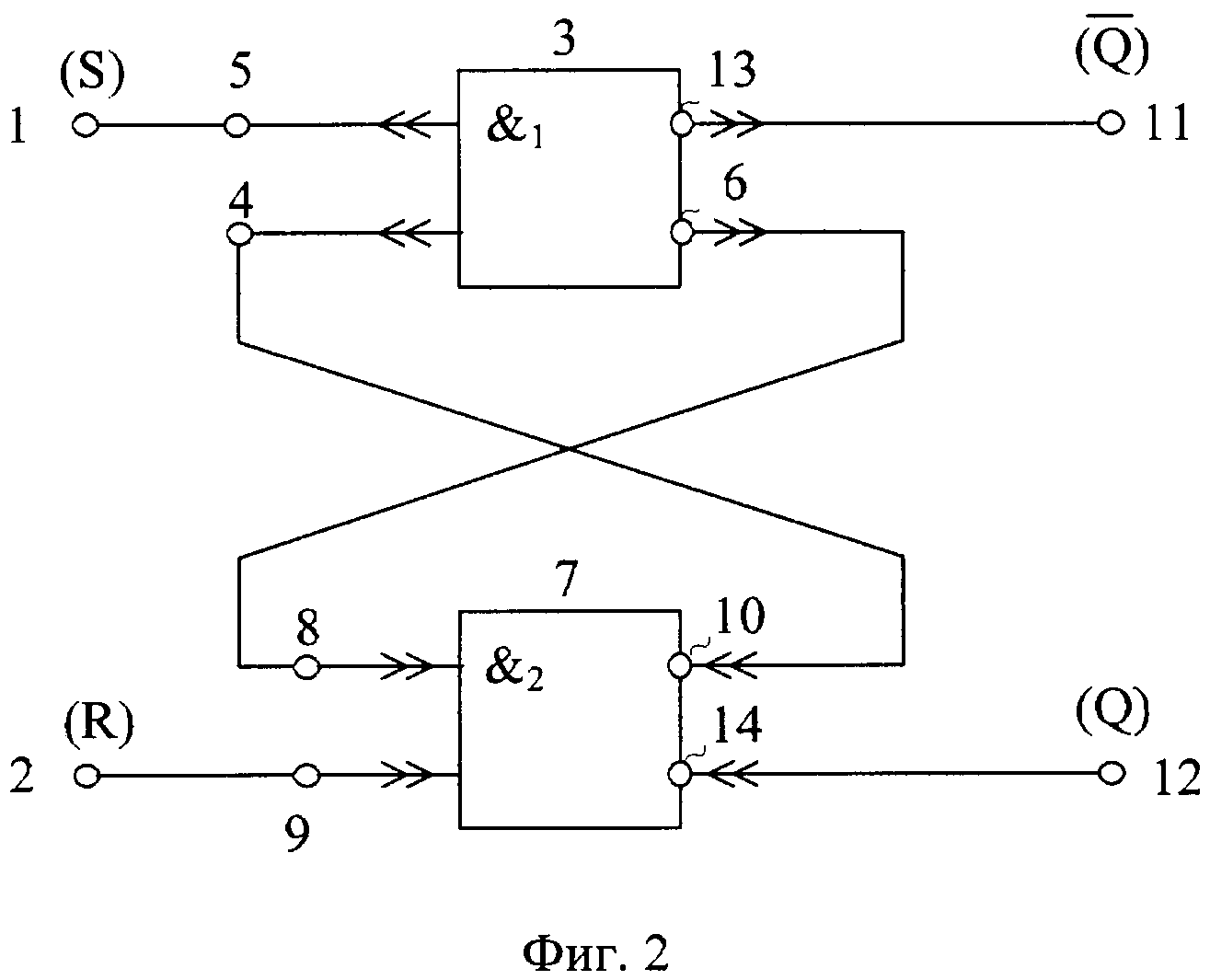

Схема RS-триггера-прототипа показана на чертеже фиг. 1. На чертеже фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

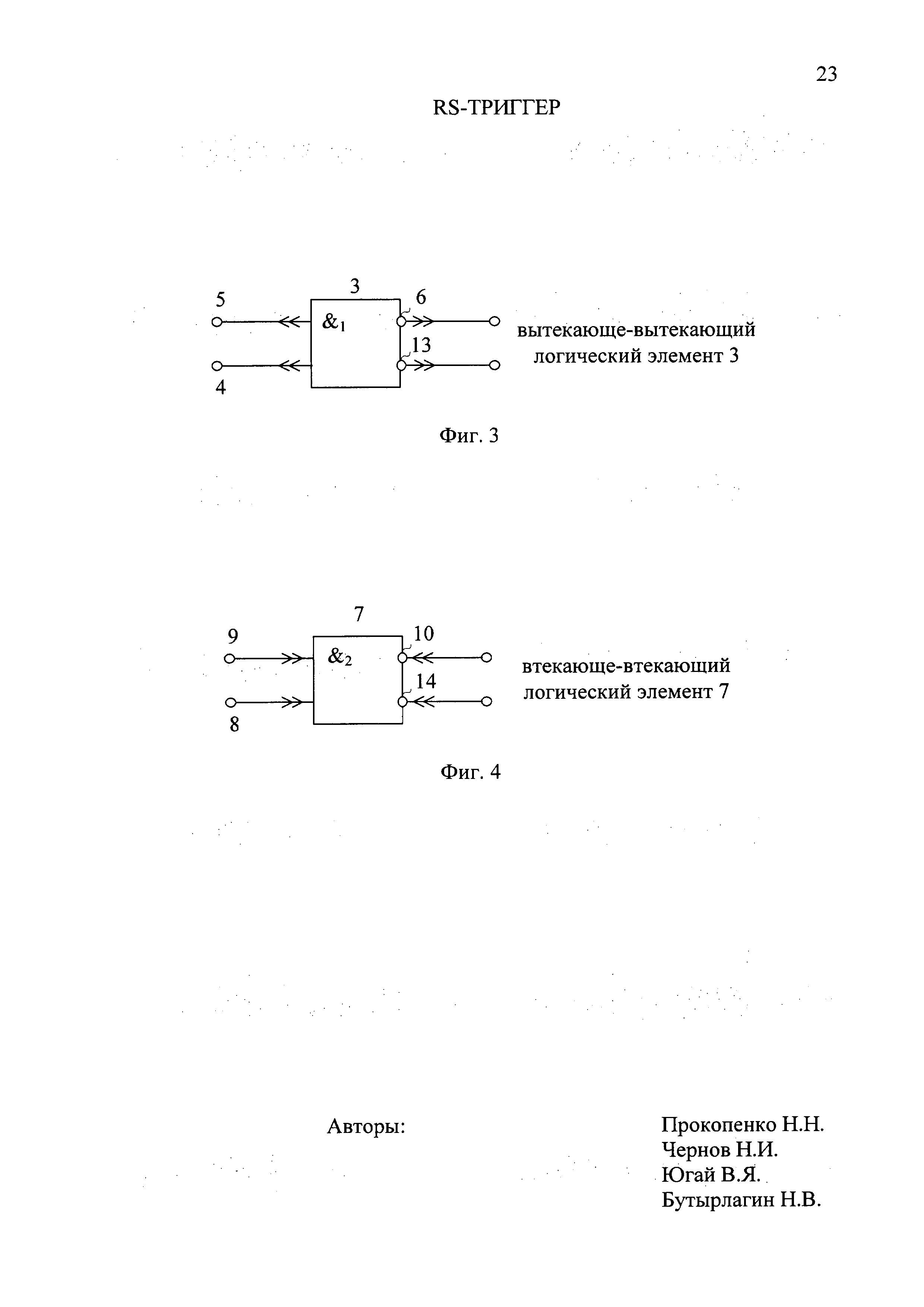

На чертеже фиг. 3 и фиг. 4 показаны обозначения первого 3 и второго 7 инвертирующих логических элементов «И», а также направления их входных и выходных токовых координат, которые обозначены стрелками.

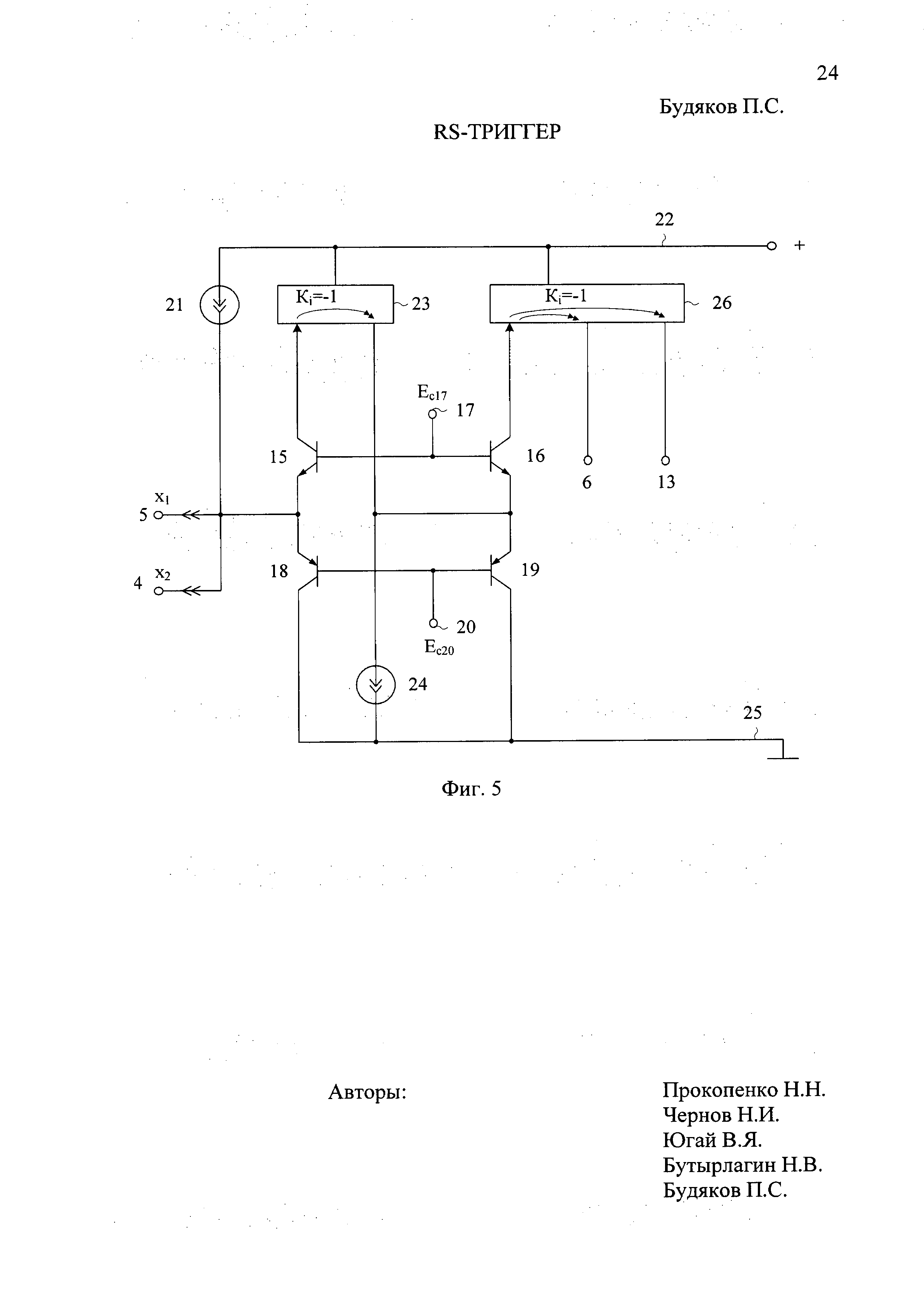

На чертеже фиг. 5 приведена схема первого 3 инвертирующего логического элемента «И», соответствующая п. 2 формулы изобретения.

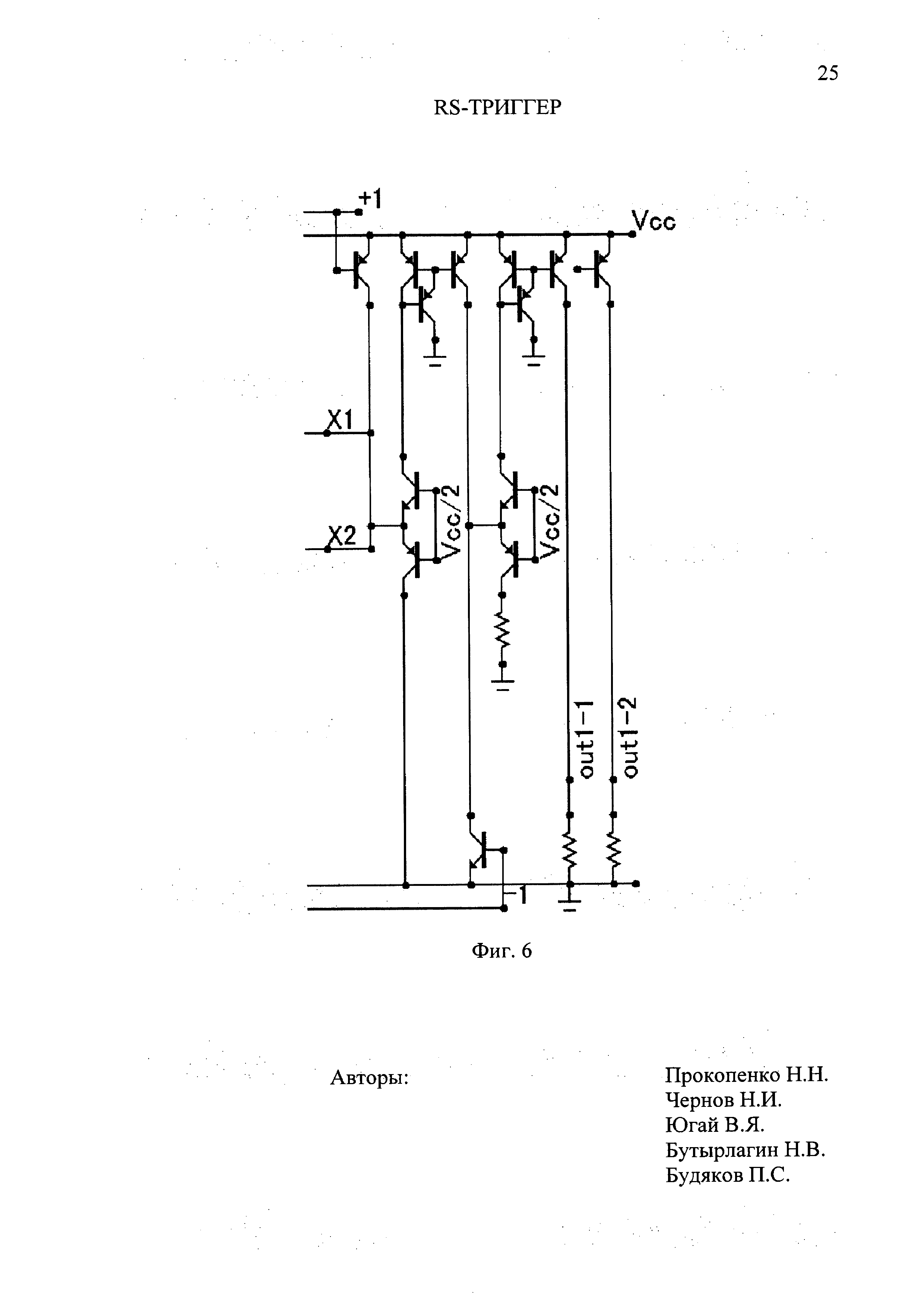

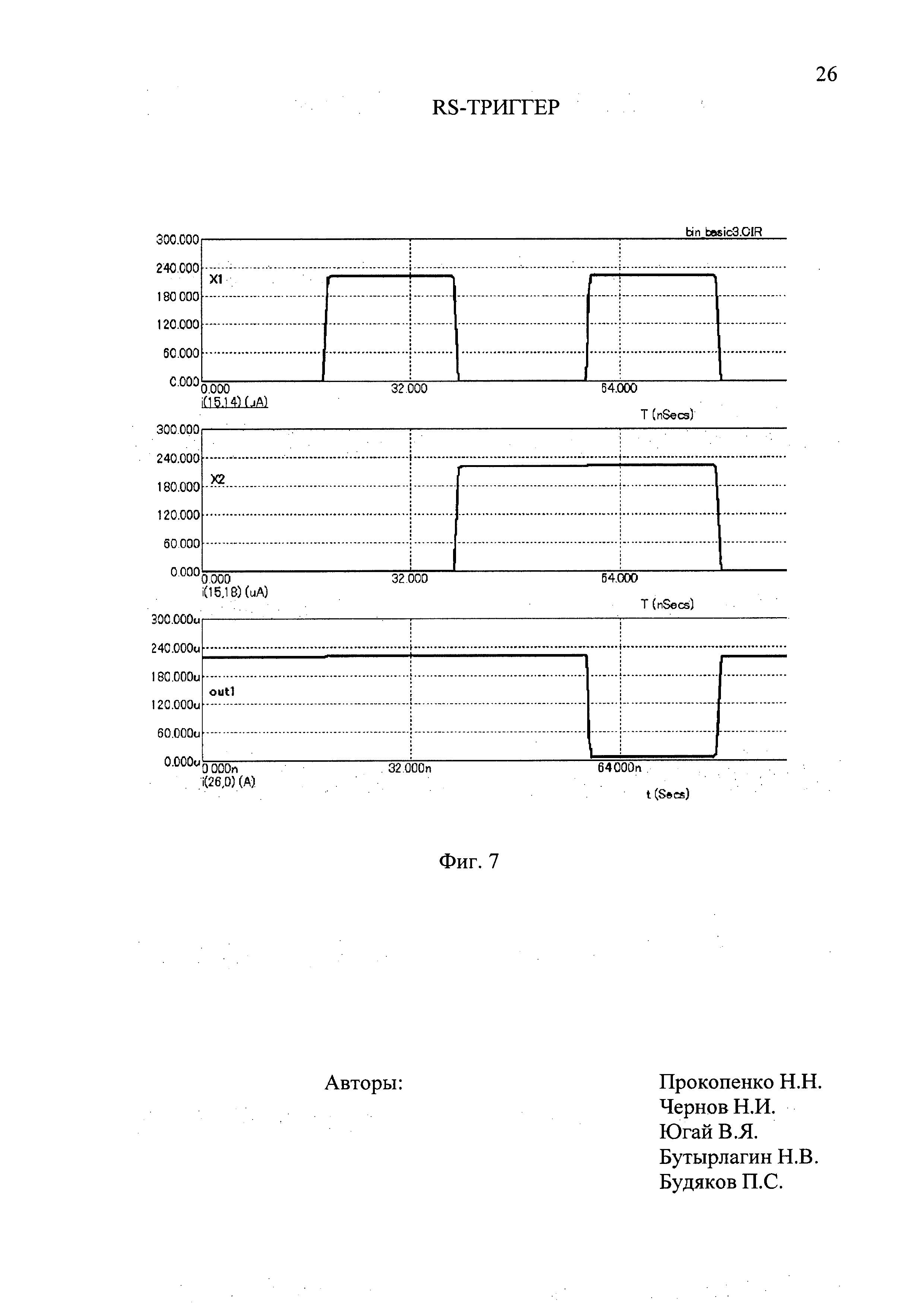

На чертеже фиг. 6 представлена схема фиг. 5 в среде компьютерного моделирования МС9.

На чертеже фиг. 7 приведены временные диаграммы работы схемы фиг. 6.

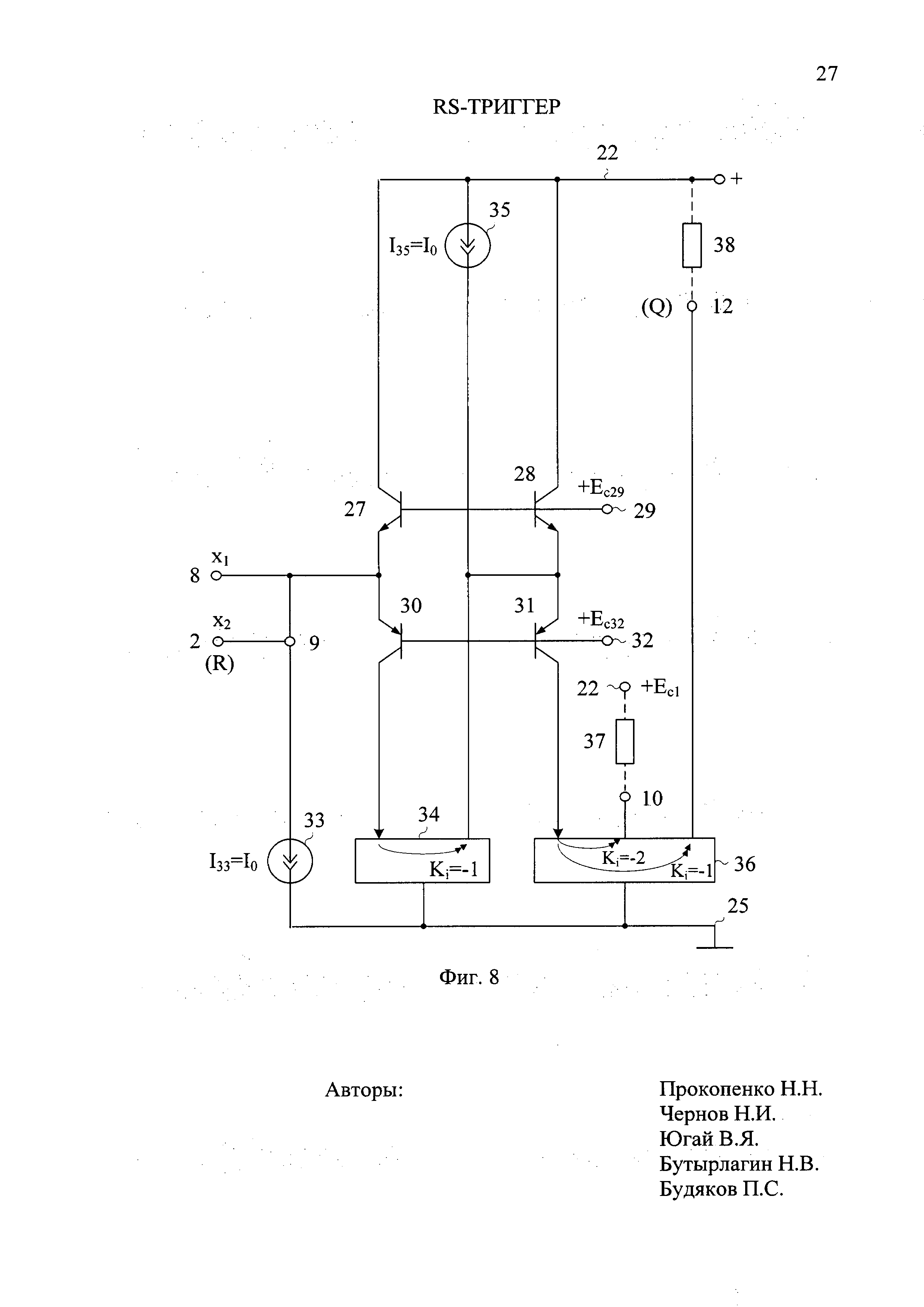

В соответствии с п. 3 формулы изобретения на чертеже фиг. 8 представлена схема второго 7 инвертирующего логического элемента «И».

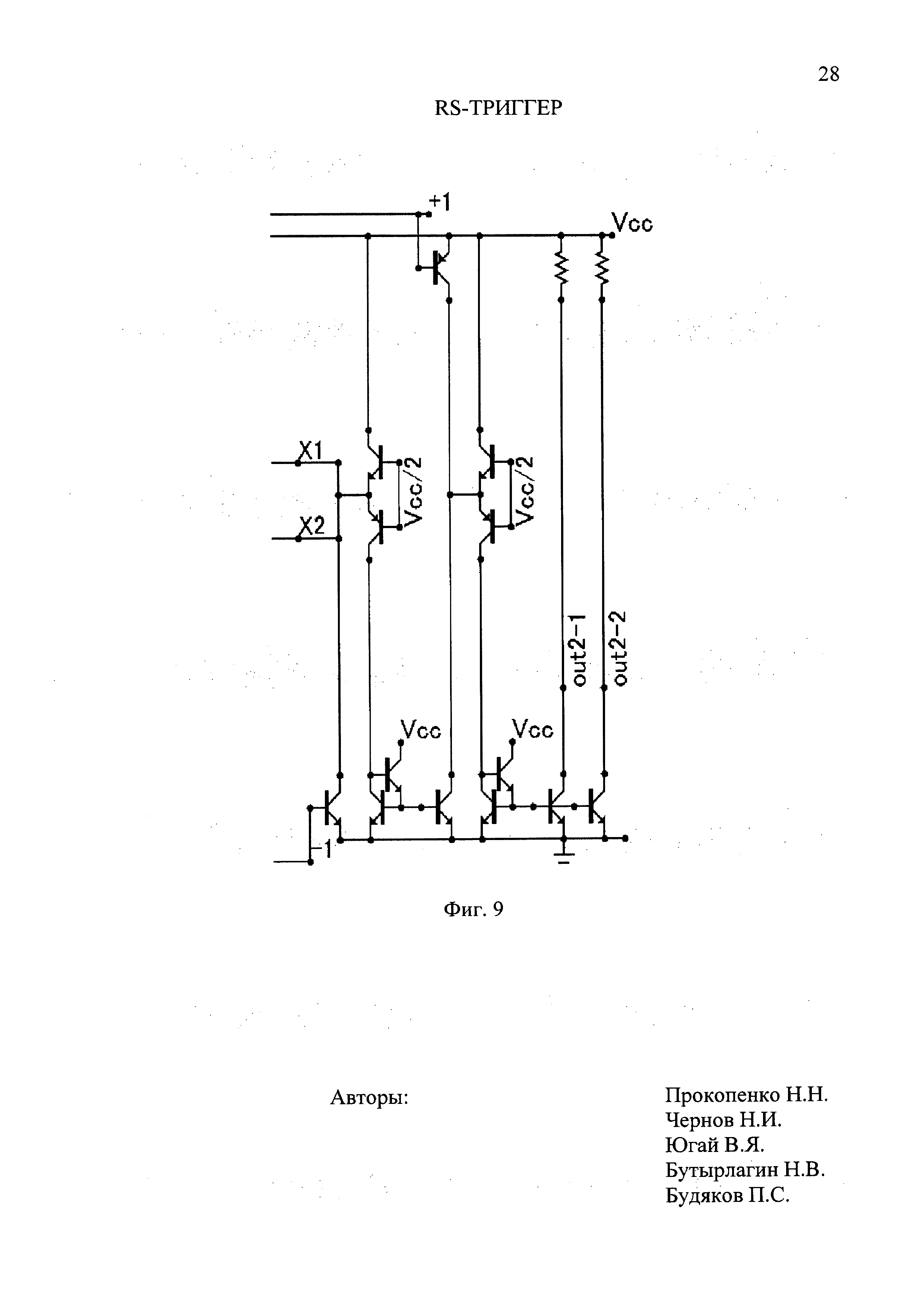

На чертеже фиг. 9 представлена схема фиг. 8 в среде компьютерного моделирования МС9.

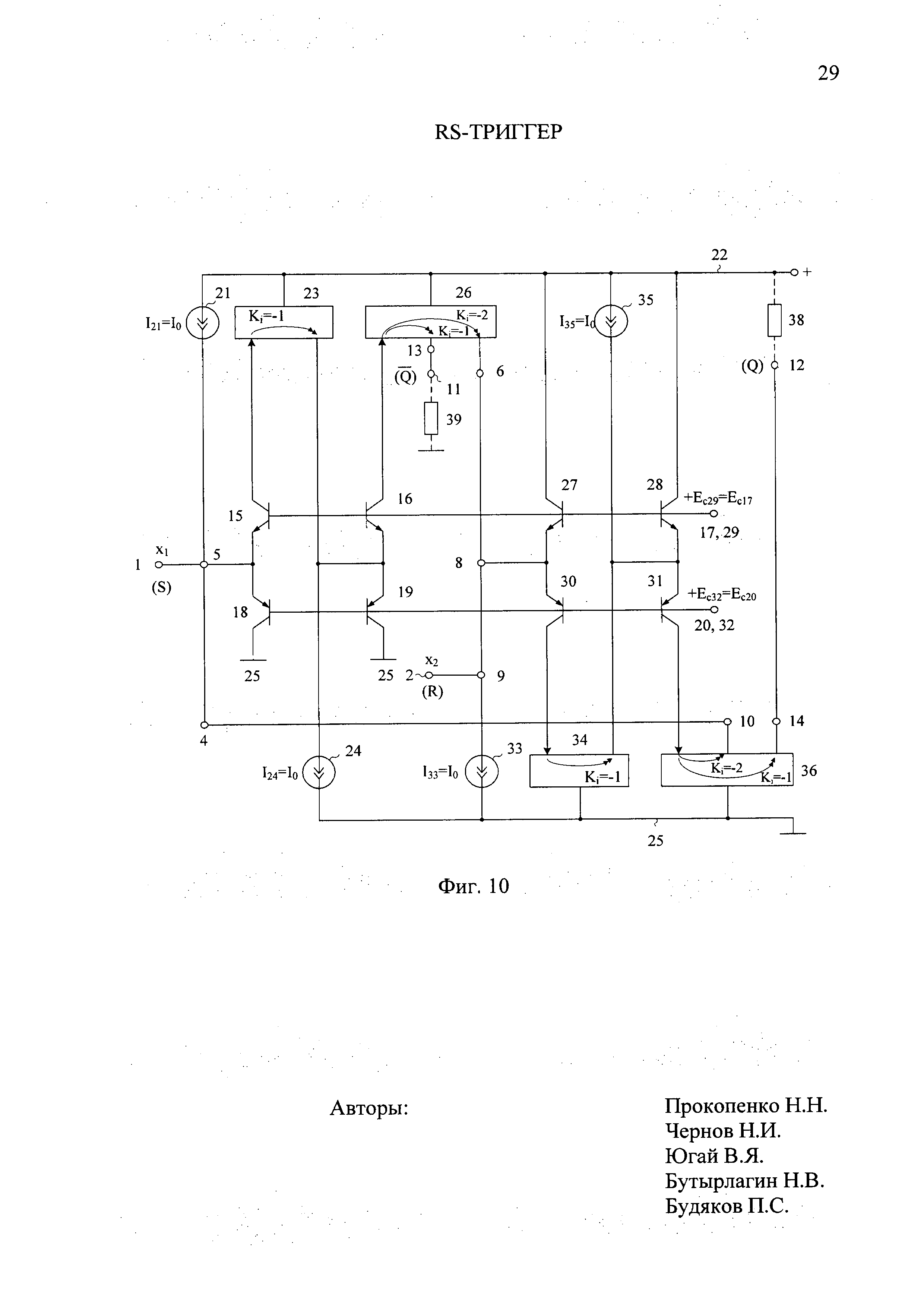

На чертеже фиг. 10 показана схема заявляемого RS-триггера, функциональная схема которого соответствует чертежу фиг. 2, а конкретное выполнение первого 3 и второго 7 инвертирующих логических элементов «И» соответствует чертежам фиг. 5 и фиг. 8.

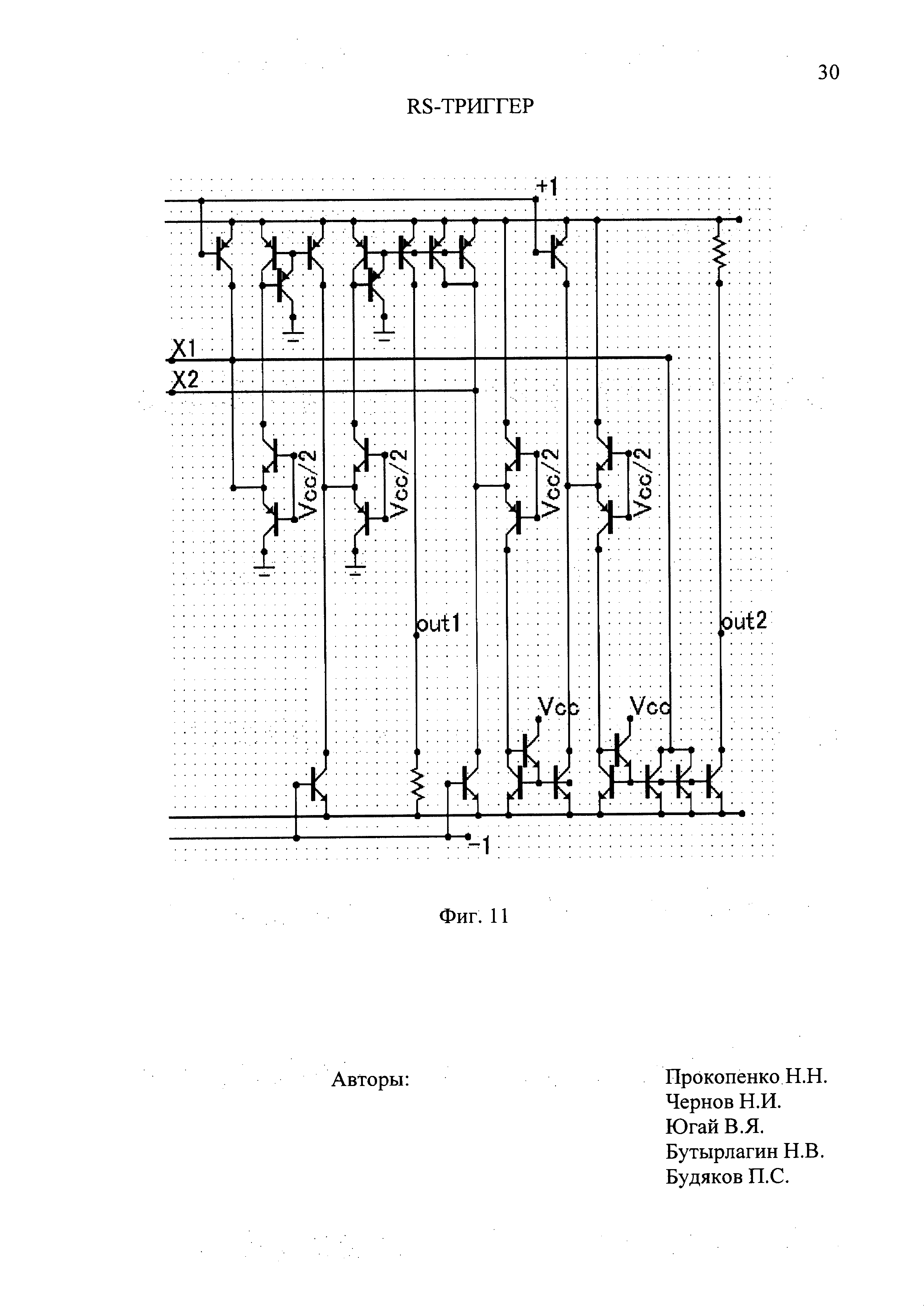

На чертеже фиг. 11 представлена схема фиг. 10 в среде компьютерного моделирования МС9.

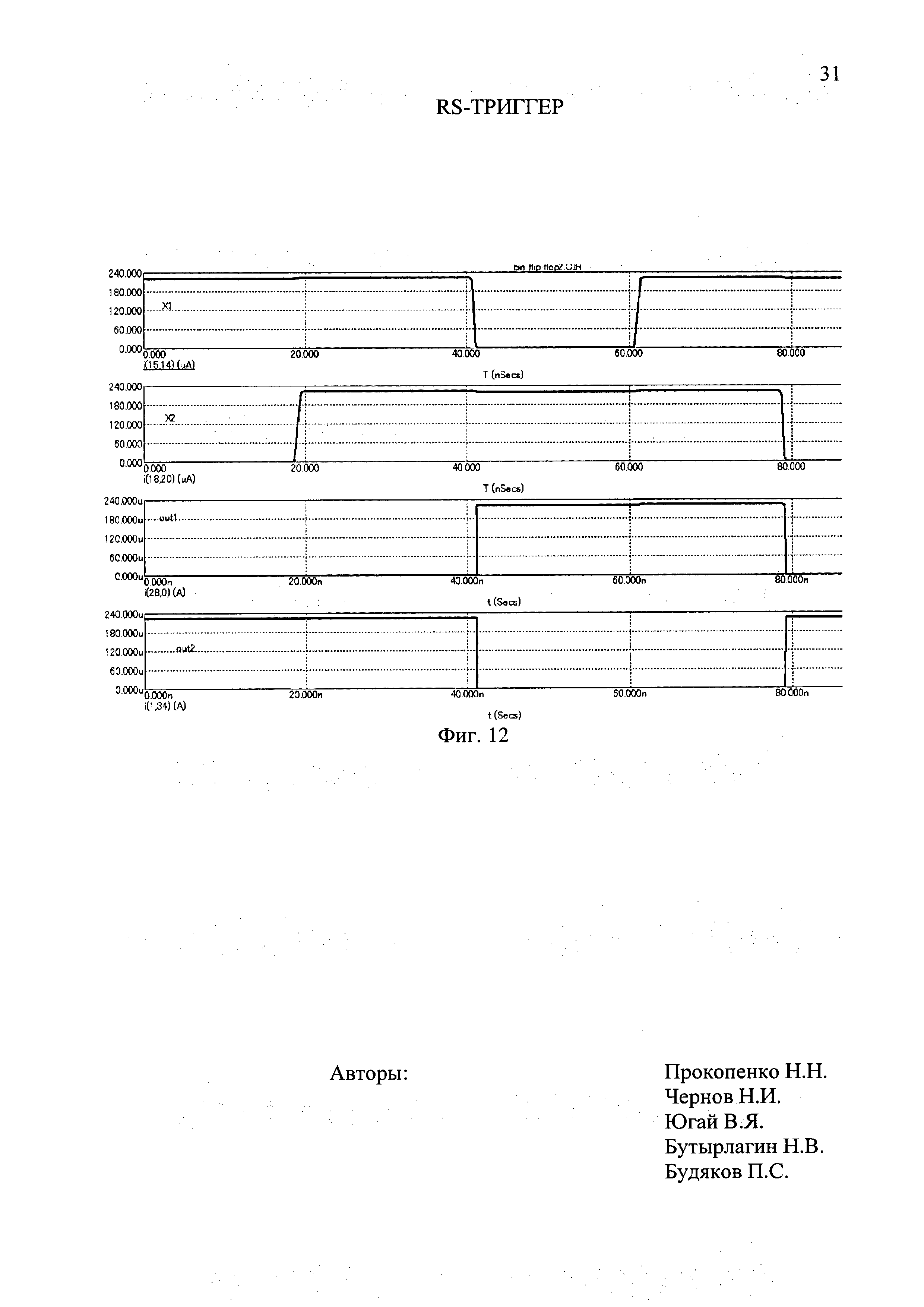

На чертеже фиг. 12 представлена результаты компьютерного моделирования схемы RS триггера фиг. 11 в среде компьютерного моделирования МС9.

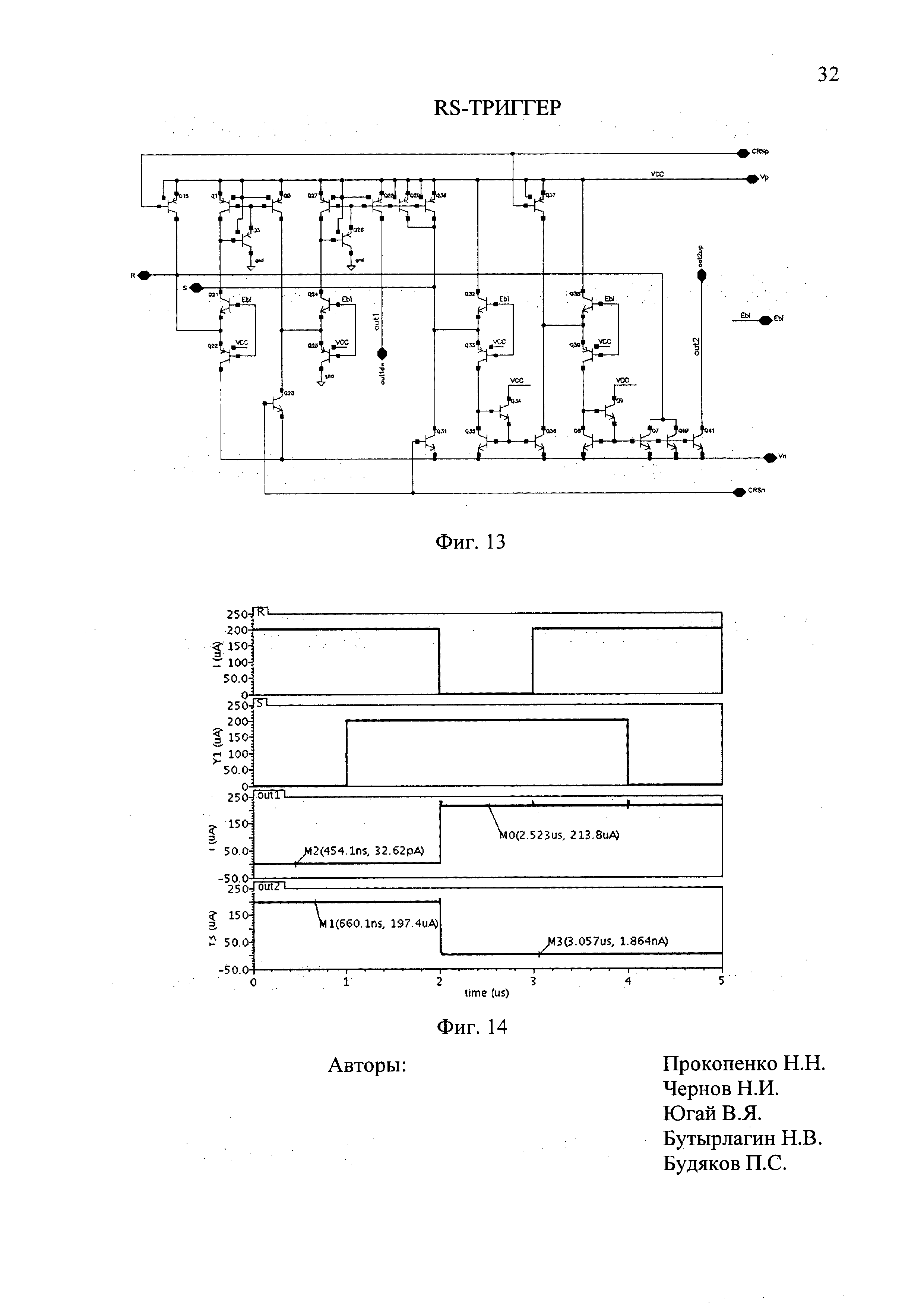

На чертеже фиг. 13 показана схема RS-триггера фиг. 10 на моделях HJV_TCMS.

На чертеже фиг. 14 приведены результаты компьютерного моделирования RS триггера фиг. 13.

RS-триггер фиг. 2 содержит RS-триггер, содержащий первый 1 (S) и второй 2 (R) логические входы устройства, первый 3 инвертирующий логический элемент «И» с первым 4 и вторым 5 логическими входами первого 3 инвертирующего логического элемента «И», а также первым 6 выходом первого 3 инвертирующего логического элемента «И», второй 7 инвертирующий логический элемент «И» с первым 8 и вторым 9 логическими входами второго 7 инвертирующего логического элемента «И», а также вторым 10 выходом второго 7 инвертирующего логического элемента «И», причем первый 6 выход первого 3 инвертирующего логического элемента «И» связан с первым 8 логическим входом второго 7 инвертирующего логического элемента «И», первый 10 выход второго 7 инвертирующего логического элемента «И» соединен с первым 4 логическим входом первого 3 инвертирующего логического элемента «И», противофазные первый  и второй 12 (Q) логические выходы устройства, причем первый 1 (S) логический вход устройства соединен со вторым 5 логическим входом первого 3 инвертирующего логического элемента «И», второй 2 (R) логический вход устройства соединен со вторым 9 логическим входом второго 7 инвертирующего логического элемента «И». В качестве первого 3 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 4 и второй 5 логические входы первого 3 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют вытекающие входные токи, которые соответствуют входным логическим переменным, причем первый 6 выход первого 3 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет вытекающий выходной ток, в качестве второго 7 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 8 и второй 9 логические входы второго 7 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют втекающие входные токи, которые соответствуют входным логическим переменным, причем первый 10 выход второго 7 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет втекающий выходной ток, первый 3 инвертирующий логический элемент «И» имеет дополнительный токовый выход 13 первого 3 инвертирующего логического элемента «И», синфазный с первым 6 токовым выходом первого 3 инвертирующего логического элемента «И» и подключенный к первому

и второй 12 (Q) логические выходы устройства, причем первый 1 (S) логический вход устройства соединен со вторым 5 логическим входом первого 3 инвертирующего логического элемента «И», второй 2 (R) логический вход устройства соединен со вторым 9 логическим входом второго 7 инвертирующего логического элемента «И». В качестве первого 3 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 4 и второй 5 логические входы первого 3 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют вытекающие входные токи, которые соответствуют входным логическим переменным, причем первый 6 выход первого 3 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет вытекающий выходной ток, в качестве второго 7 инвертирующего логического элемента «И» используется логический элемент «И», у которого первый 8 и второй 9 логические входы второго 7 инвертирующего логического элемента «И» характеризуются входными токовыми координатами и имеют втекающие входные токи, которые соответствуют входным логическим переменным, причем первый 10 выход второго 7 инвертирующего логического элемента «И» характеризуется выходной токовой координатой и имеет втекающий выходной ток, первый 3 инвертирующий логический элемент «И» имеет дополнительный токовый выход 13 первого 3 инвертирующего логического элемента «И», синфазный с первым 6 токовым выходом первого 3 инвертирующего логического элемента «И» и подключенный к первому  логическому выходу устройства, второй 7 инвертирующий логический элемент «И» имеет дополнительный токовый выход 14 второго 7 инвертирующего логического элемента «И», синфазный с первым 10 токовым выходом второго 7 инвертирующего логического элемента «И» и подключенный ко второму 12 (Q) логическому выходу устройства.

логическому выходу устройства, второй 7 инвертирующий логический элемент «И» имеет дополнительный токовый выход 14 второго 7 инвертирующего логического элемента «И», синфазный с первым 10 токовым выходом второго 7 инвертирующего логического элемента «И» и подключенный ко второму 12 (Q) логическому выходу устройства.

Первый 1 (S) логический вход устройства в схеме фиг. 2 соответствует принятому в технической литературе буквенному обозначению как S вход триггера, а второй 2 (R) логический вход устройства - как R вход триггера.

На чертеже фиг. 5, в соответствии с п. 2 формулы изобретения, первый 3 инвертирующий логический элемент «И» содержит первый 15 и второй 16 выходные транзисторы, базы которых подключены к первому 17 источнику напряжения смещения, первый 18 и второй 19 вспомогательные транзисторы противоположного типа проводимости, базы которых подключены ко второму 20 источнику напряжения смещения, объединенные эмиттеры первого 15 выходного транзистора и первого 18 вспомогательного транзистора подключены к первому 4 и второму 5 логическим входам первого 3 инвертирующего логического элемента «И» и через первый 21 источник опорного тока соединены с первой 22 шиной источника питания, коллектор первого 15 выходного транзистора подключен ко входу первого 23 токового зеркала, согласованного с первой 22 шиной источника питания, выход первого 23 токового зеркала подключен к объединенным эмиттерами второго 16 выходного транзистора и второго 19 вспомогательного транзистора и через второй 24 источник опорного тока соединен со второй 25 шиной источника питания, коллектор второго 16 выходного транзистора связан со входом второго 26 токового зеркала, согласованного с первой 22 шиной источника питания, коллекторы первого 18 и второго 19 вспомогательных транзисторов подключены ко второй 25 шине источника питания, причем первый токовый выход второго 26 токового зеркала соединен с первым 6 токовым выходом первого 3 инвертирующего логического элемента «И», а синфазный с ним второй токовый выход второго 26 токового зеркала соединен с дополнительным токовым выходом 13 первого 3 инвертирующего логического элемента «И».

На чертеже фиг. 8, в соответствии с п. 3 формулы изобретения, второй 7 инвертирующий логический элемент «И» содержит третий 27 и четвертый 28 выходные транзисторы, базы которых подключены к третьему 29 источнику напряжения смещения, третий 30 и четвертый 31 вспомогательные транзисторы противоположного типа проводимости, базы которых подключены ко четвертому 32 источнику напряжения смещения, объединенные эмиттеры третьего 27 выходного транзистора и третьего 30 вспомогательного транзистора подключены к первому 8 и второму 9 токовым логическим входам второго 7 логического элемента «И» и через третий 33 источник опорного тока соединены со второй 25 шиной источника питания, коллектор третьего 30 вспомогательного транзистора подключен ко входу третьего 34 токового зеркала, согласованного со второй 25 шиной источника питания, выход третьего 34 токового зеркала подключен к объединенным эмиттерами четвертого 28 выходного транзистора и четвертого 31 вспомогательного транзистора и через четвертый 35 источник опорного тока соединен с первой 22 шиной источника питания, коллектор четвертого 31 вспомогательного транзистора связан со входом четвертого 36 токового зеркала, согласованного со второй 25 шиной источника питания, коллекторы третьего 27 и четвертого 28 выходных транзисторов подключены к первой 22 шине источника питания, причем первый токовый выход четвертого 36 токового зеркала соединен с первым 10 токовым логическим выходом второго 7 инвертирующего логического элемента «И», а синфазный с ним второй токовый выход четвертого 36 токового зеркала соединен с дополнительным токовым выходом 14 второго 7 инвертирующего логического элемента «И».

Кроме этого на чертеже фиг. 8 показаны резисторы 37 и 38, которые моделируют нагрузку по второму 10 выходу второго 7 инвертирующего логического элемента «И» и второму 12 (Q) логическому выходу устройства.

На чертеже фиг. 10 первый 17 и третий 29 источники напряжения смещения имеют одинаковые напряжения и поэтому в ряде случаев могут быть объединены. Аналогично вместо второго 20 и четвертого 32 источников напряжения смещения может использоваться одна шина питания.

Рассмотрим работу заявляемого устройства фиг. 8. Структура и принцип его работы аналогичны структуре и принципу работы классического RS-триггера (фиг. 1): он представляет собой систему двух инвертирующих логических элементов «И» (2И-НЕ), охваченных положительной обратной связью. Отличием является иное построение первого 3 и второго 7 инвертирующего логического элемента «И» (2И-НЕ) и способ реализации токовых обратных связей.

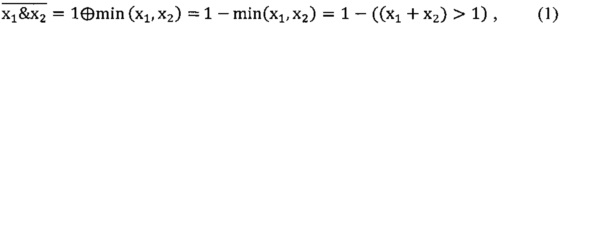

Логическая реализация элемента «2И-НЕ» производится в линейной алгебре [35-37] на основе выражения

где x1, x2 - входные логические токовые переменные.

Для схемотехнической реализации логических элементов на основе выражения (1) используются токовые зеркала. Для двоичных переменных логический ноль представляется отсутствием некоторого заданного кванта тока I0, а единица - наличием кванта тока I0. При этом знак кванта определяется его направлением (втекающим, вытекающим). При токовом сигнальном представлении логических переменных направление тока не влияет на значение переменной, а зависит только от знака слагаемых в операциях алгебраического суммирования, реализующих выражения линейной алгебры (1). Объединение таких логических элементов в более сложные структуры требует согласования не только уровней квантов тока I0, но и направлений входных и выходных токовых логических сигналов (фиг. 3, фиг. 4).

Структурная организация элемента «2И-НЕ» с учетом особенностей токового представления сигналов приведена на чертеже фиг. 3. Она отличается наличием двух идентичных выходных токовых сигналов, один из которых предназначен для организации цепи положительной обратной связи, а второй - для подключения к внешним элементам схемы, в которой триггер используется.

Схемотехническая реализация первого 3 инвертирующего логического элемента «И» с токовыми входным и выходным логическими сигналами показана на чертежах фиг. 5. На фиг. 6 приведена схема фиг. 5 в среде компьютерного моделирования МС9, а на чертеже фиг. 7 - результаты моделирования логического элемента «2И-НЕ» фиг. 6 с токовыми логическими сигналами.

В соответствии с п. 3 формулы изобретения на чертеже фиг. 8 представлена схема второго 7 инвертирующего логического элемента «И». На фиг. 9 приведена схема фиг. 8 в среде компьютерного моделирования МС9.

Заявляемое устройство фиг. 10 состоит из двух логических элементов «2И-НЕ» фиг. 5 и фиг. 8 с токовыми входными и выходными логическими сигналами. Выходной логический токовый сигнал обратной связи подается на первый 4 логический вход первого 3 инвертирующего логического элемента «И» с коэффициентом передачи по току Ki=2 в четвертом 36 токовом зеркале.

Традиционные сигналы установки заявляемого RS-триггера в единичное (S) или нулевое (R) состояния поступают в виде квантов тока на первый 1 (S) или второй 2 (R) логические входы устройства соответственно (фиг. 10).

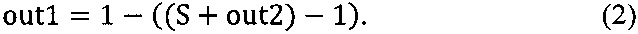

В точке алгебраического суммирования токов (узел 5 логического токового входа 5) (фиг. 10) реализуется операция вычитания (S+out2)-1, в которой сигналом единицы является выходной сигнал первого 21 источника опорного тока. Результат операции подается на объединенные эмиттеры первого 15 выходного и первого 18 вспомогательного транзисторов. Если разность положительна, то разностный квант тока замыкается на вторую 25 шину источника питания через первый 18 вспомогательный транзистор. В противном случае результат в виде соответствующего кванта тока поступает на вход первого 23 токового зеркала, где инвертируется в квант вытекающего тока и поступает в точку алгебраического суммирования, в которой реализуется операция 1 - ((S+out2)-1), где единицей является выходной ток I0 второго 24 источника опорного тока. Результат операции поступает на объединенные эмиттеры второго 16 выходного и второго 19 вспомогательного транзисторов. Если разность положительна, то разностный квант тока замыкается на вторую 25 шину источника питания через второй 19 вспомогательный транзистор. В противном случае сигнал в виде кванта разностного тока поступает на вход второго 26 токового зеркала, где «размножается» и передается на первый 6 выход и дополнительный токовый выход 13 первого 3 инвертирующего логического элемента «И». Дополнительный токовый выход 13 первого 3 инвертирующего логического элемента «И» второго 26 токового зеркала является первым  выходом заявляемого RS-триггера. Его логическая функция описывается выражением

выходом заявляемого RS-триггера. Его логическая функция описывается выражением

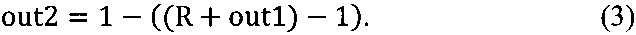

В точке алгебраического суммирования, которая соответствует первому 8 логическому входу второго 7 инвертирующего логического элемента «И», выполняется операция ((R+out1)-1), в которой сигналом единицы является выходной сигнал опорного источника тока 33. Результат операции подается на объединенные эмиттеры третьего 27 выходного транзистора и третьего 30 вспомогательного транзистора. Если разность положительна, то квант разностного тока замыкается на первую 22 шину источника питания через третий 30 вспомогательный транзистор. В противном случае сигнал в виде кванта разностного тока поступает на вход третьего 34 токового зеркала, где он инвертируется по направлению.

С токового выхода третьего 34 токового зеркала квант тока подается в точку алгебраического суммирования, в которой реализуется операция 1 - ((R+out1)-1), где единицей является квант тока четвертого 35 источника опорного тока. Результат операции поступает на объединенные эмиттеры четвертого 28 выходного и четвертого 31 вспомогательного транзисторов. Если разность положительна, то квант разностного тока замыкается на первую 22 шину источника питания через четвертый 28 выходной транзистор. В противном случае сигнал в виде кванта разностного тока поступает на вход четвертого 36 токового зеркала, где он инвертируется по направлению. Со второго 14 логического токового выхода четвертого 36 токового зеркала снимается выходной сигнал второго 12 (Q) логического выхода устройства в виде кванта разностного тока. Дополнительный токовый выход 14 второго 7 инвертирующего логического элемента «И» четвертого 36 токового зеркала является вторым 12 (Q) логическим выходом заявляемого устройства. Его логическая функция описывается выражением

Резисторы 38 и 39 используются для определения наличия тока в процессе экспериментальных исследований схемы фиг. 10.

Как видно из приведенного описания, реализация логической функции RS-триггера фиг. 10 производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенной схемы фиг. 10 работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие RS-триггера. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи в сложных системах на кристалле, что уменьшает их количество. Использование стабильных значений квантов тока I0, а также определение выходного логического сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Показанные на чертежах фиг. 12, фиг. 14 результаты моделирования подтверждают указанные свойства заявляемой схемы RS-триггера фиг. 10.

Таким образом, рассмотренное схемотехническое решение RS-триггера характеризуется многозначным состоянием внутренних сигналов и сигналов на его токовых входах и выходах, что может быть положено в основу специализированных вычислительных и управляющих устройств, использующих токовое представление информационных сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 2011/0121877, fig. 9

2. Патент EP 06011821, fig. 2

3. Патент US 5.994.936, fig. 3

4. Патент US 5.327.020, fig. 1

5. Патент US 6.362.674, fig. 4A

6. Патент US 6.535.024

7. Патент US 7.098.652, fig. 1, fig. 10

8. Патент US 4.441.075 fig. 1

9. Авторское свидетельство СССР 1390790

10. Авторское свидетельство СССР 1193798

11. Авторское свидетельство СССР 1370732

12. Патент US 5.065.052, fig. 3, fig. 10

13. Патент US 7.697.319, fig. 2

14. Патент US 8.232.825, fig. 9

15. Патент US 8.115.522 fig.2

16. Патент US 7.626.433

17. Патент US 7.236.029 fig. 3

18. Патент US 6.268.752 fig. 4

19. Патент US 6.486.720

20. Патентная заявка US 2002/0003443 fig. 4

21. Патент US 6.714.060

22. Патент US 5.025.174

23. Патент US 5.945.858

24. Патент US 5.892.382 fig. 2

25. Патент US 5.844.437 fig. 2

26. Патент US 5.220.212

27. Патент US 5.815.019 fig. 1

28. Патент US 5.541.544 fig. 1

29. Патент US 5.001.361 fig. 3

30. Патент US 5.969.556 fig. 1

31. Патент US 4.156.819 fig. 2

32. Патент US 4.779.009 fig. 4

33. Патент US 4.309.625 fig. 4

34. Патент US 3.305.728

35. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С. 84-93.

36. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

37. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.