Результат интеллектуальной деятельности: СПОСОБ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ИЗБЫТОЧНОСТЬЮ НЕОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ

Вид РИД

Изобретение

Изобретение относится к области вычислительной и контрольно-измерительной техники и может использоваться в системах цифровой обработки информации и управления технических объектов, обладающих избыточными аппаратными и программными средствами, разрабатываемыми и/или производимыми с использованием независимых исполнителей и/или технологий, с целью обеспечения повышенной отказоустойчивости.

Согласно общепринятому определению [http://slogos.ru/story/izbytochnost.html], избыточностью технического изделия называется наличие в нем возможностей сверх тех, которые могли бы обеспечить его нормальное функционирование. Такая избыточность в зависимости от предназначения изделия, характера решаемой задачи и других обстоятельств может использоваться либо для повышения общей его производительности (путем параллельного выполнения надлежащих функций), либо для обеспечения необходимого уровня безотказности (путем организации горячего или холодного резервирования различной кратности).

В качестве технического изделия рассматривается вычислительная система (ВС), в общем случае неоднородная, используемая для обработки информации (сбор, получение, анализ, пересылка информации, выработка управляющих воздействий, команд индикации) в составе сложной технической системы, часто называемой комплексом. Избыточность ВС заключается в том, что число используемых процессорных узлов (ПУ), каждый из которых состоит из одного процессора, устройств памяти и обеспечивающей совокупности других элементов, больше единицы. При этом ВС может обладать неоднородной аппаратной и программной реализацией, т.е. различные ПУ или их части, а также соответствующие программные компоненты могут быть созданы различными разработчиками и/или с использованием различных технологий.

Известен способ повышения надежности вычислительно-информационных систем путем побитового восстановления слов (информации) на основе их функциональной избыточности [Шульга Т.Э. Метод построения восстанавливающих последовательностей для систем без потери информации // Системы управления и информационные технологии. 2009. №3(35). С. 407-411]. Такой подход потенциально предоставляет возможность парирования неблагоприятных последствий сбоев и частичных отказов процессоров, однако его практическое применение ограничено жесткими структурными требованиями как к содержанию обрабатываемой информации, так и характеру неблагоприятных воздействий.

Известен способ повышения надежности и достоверности обработки критических функций отказоустойчивой вычислительной системы [Патент на изобретение №2413975 от 17.11.2008], когда эффект достигается за счет многократного резервирования трактов реализации критических функций, при которой процессы управления избыточностью и вычислительный процесс разделены в цикле реального времени и частично аппаратными средствами. В качестве резервируемых единиц вычислителя выделяются так называемые вычислительные тракты, состоящие из неразрывно связанных цепочек входного интерфейса, процессора и выходного интерфейса. В каждом из вычислительных трактов производится мажоритарное сравнение сигналов, прошедших через каждый тракт. Неоднозначность мажоритарного сравнения сигналов в различных трактах устраняют мажоритарным сравнением результатов сравнения сигналов. Достоверность мажоритарного контроля сигналов достигается путем статистической обработки случайного процесса изменения критического параметра, вычисления остаточной дисперсии и ее мажоритарного сравнения. Этот способ и устройство для его реализации выбраны в качестве прототипа.

К недостаткам этого способа относятся:

- низкая эффективность мажоритарного сравнения сигналов при неоднородной избыточности вычислительных средств;

- заведомое завышение объемов потребного резервирования из-за объединения нескольких аппаратных компонентов в одну неразрывную единицу;

- слишком высокий объем вычислений, связанных с многоуровневым мажоритарным контролем в сочетании со статистической обработкой сигналов трактов;

- сложность самого устройства, что вместе с отсутствием у него встроенного самоконтроля снижает надежность достижения соответствующего технического эффекта.

Известно устройство для управления избыточностью модулей в многопроцессорной вычислительной системе [Патент US 4503534 А, G06F 11/00, опубл. 05.03.1985] в виде матрицы, составленной из процессорной шины с линиями ошибок и управления линиями; и шин памяти с соответственными линиями ошибок и управления линиями. Каждый узел матрицы имеет средства регистрации ошибок в вышеуказанных линиях. Вычислительные и интерфейсные модули вычислительной системы делятся на основные и теневые и связаны соответственно с основными и теневыми узлами матрицы, которые управляют доступом к шинам памяти. При этом предполагается идентичность всех вычислительных и интерфейсных модулей. Управление избыточностью вычислительной системы заключается в сравнении результатов основных и теневых модулей, а также пар «основной - теневой» с последующей блокировкой доступа к памяти модулям с неподтвержденными результатами. Основным недостатком является невозможность использования изобретения для систем с неоднородной избыточностью, когда разные модули одного и того же предназначения созданы разными разработчиками на разной технологической базе.

Целью изобретения является улучшение технико-эксплуатационных характеристик неоднородной вычислительной системы (ВС). А именно, предлагаемые способ и устройство позволяют обеспечить повышенную отказоустойчивость ВС, т.е. сохранить работоспособность ВС с разнородными элементами в условиях возникновения множественных разнотипных отказов.

Эта цель достигается тем, что в способе автоматического управления избыточностью неоднородной вычислительной системы, содержащем множество параллельных содержательных вычислений решаемой задачи, выбор предпочтительного решения на конкурсной основе и распределение функции контроля по всем процессорным узлам, содержательные вычисления задачи разбиваются на этапы, включающие определение значения показателя успешности завершения текущего этапа, с сохранением входных внутренних и выходных данных, затем путем сопоставления значений показателя успешности этапа осуществляют попарный арбитраж процессорных узлов по иерархической схеме и реконфигурацию вычислительной системы с выделением пассивных и ведущих процессорных узлов в парах всех уровней иерархической схемы, причем ведущий процессорный узел верхнего уровня формирует и выдает во все процессорные узлы сигналы синхронизации (СС), по которым выполняются все фазы циклического процесса, соответствующего одному текущему этапу вычисления решаемой задачи, а именно ввод данных и обмен ими, вычисления решаемой задачи и арбитраж процессорных узлов, а также выдает результаты вычислений в основной и резервный выходные каналы вычислительной системы, каждый ведущий процессорный узел, кроме верхнего уровня, принимает от узлов более высокого уровня своей ветви иерархии сигналы синхронизации и аутентификации, осуществляет вычисления текущего этапа решаемой задачи, формирует показатель успешности выполнения этапа и выдает в нижние уровни своей ветви иерархии сигнал аутентификации, подтверждающий исполнение им отведенной роли, а также со своим показателем успешности выполнения этапа участвует в арбитраже за право получить роль ведущего процессорного узла более высокого уровня иерархии, пассивные процессорные узлы принимают сигналы синхронизации и аутентификации от узлов своей ветви иерархии, осуществляют вычисления текущего этапа решаемой задачи, формируют показатель успешности выполнения этапа, а также со своими показателями успешности выполнения этапа участвуют в арбитраже за право получения статуса ведущего процессорного узла первого уровня иерархии, кроме того, каждый процессорный узел может восстанавливать свои входные и внутренние данные путем обращения к другим процессорным узлам.

Дополнительно: показатели успешности этапа могут принимать только два значения, при этом ноль - результат выполнения этапа неудовлетворительный, а единица - результат выполнения удовлетворительный.

Также поставленная цель достигается тем, что в резервный выходной канал подаются результаты вычислений любого другого узла, определяемого по оговоренному правилу.

Кроме того, для решения той же задачи в устройстве автоматического управлении избыточностью неоднородной вычислительной системы, содержащем несколько параллельных процессорных узлов, входной буфер и демультипликатор, каждый процессорный узел содержит процессор, пулы входных, внутренних и выходных данных, а также вспомогательные входы и выходы для сигналов синхронизации, аутентификации и показателя успешности завершения текущего этапа, и управляемые каналы обмена данными между пулами.

В основе способа управления избыточностью ВС лежат периодические вычисления и сравнение показателей успешности выполнения этапа (ПУЭ). В зависимости от содержания этапа вычислительной задачи такими показателями могут быть: различные невязки или нормы полученных данных, доверительные или гарантированные оценки погрешностей данных, флаги прохождения запросов или завершения определенных операций, различные индикаторные числа типа контрольных сумм и пр.

Изобретение поясняется чертежами.

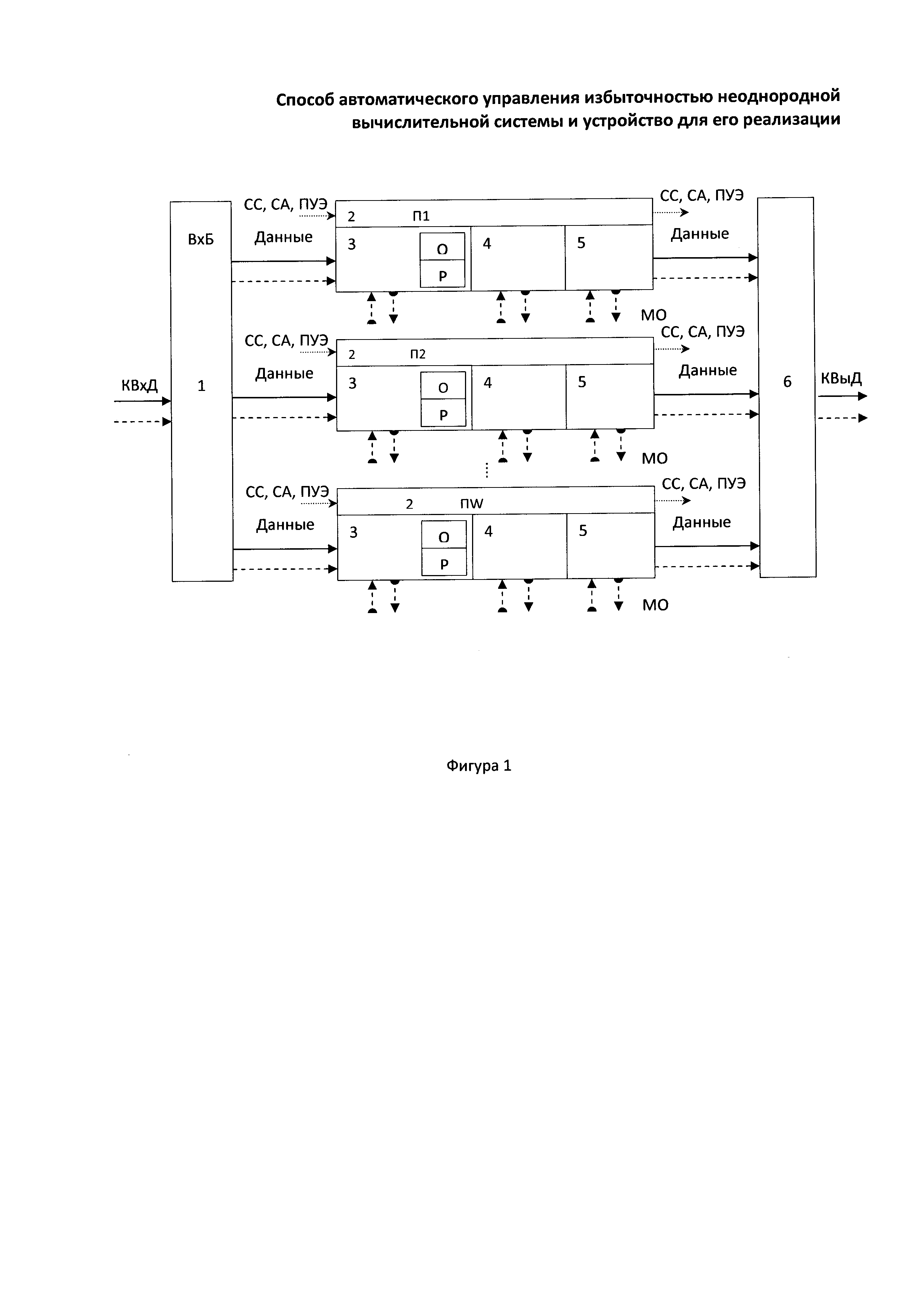

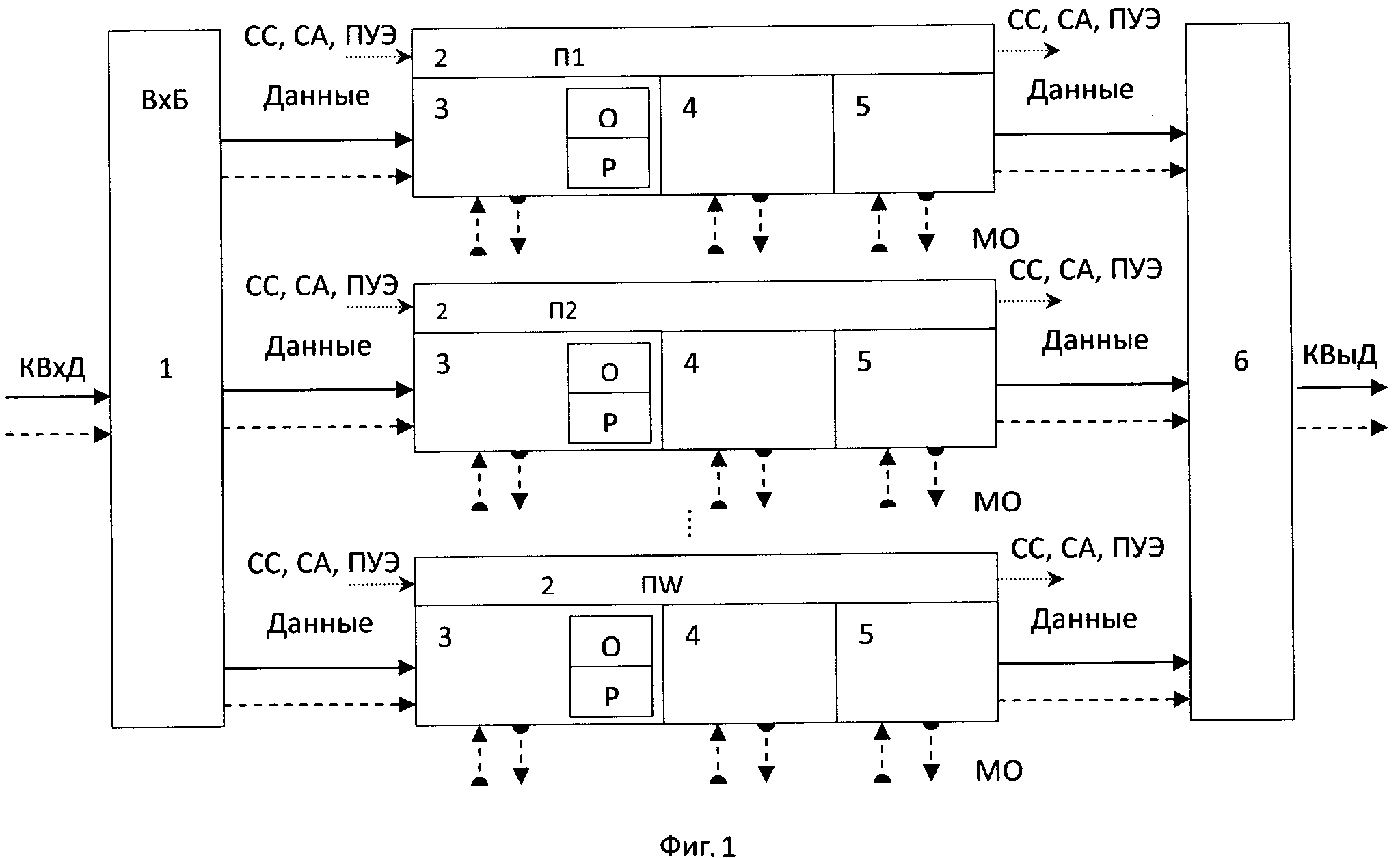

Фиг. 1 изображает функциональную схему ВС согласно изобретению, где:

1 - Входной буфер ВхБ;

2 - Процессорные узлы в количестве от П1 до ПW;

3 - Пулы входных данных ВхД;

4 - Пулы внутренних данных ВнД;

5 - Пулы выходных данных ВыД;

6 - Демультипликатор выходных данных ДВыД.

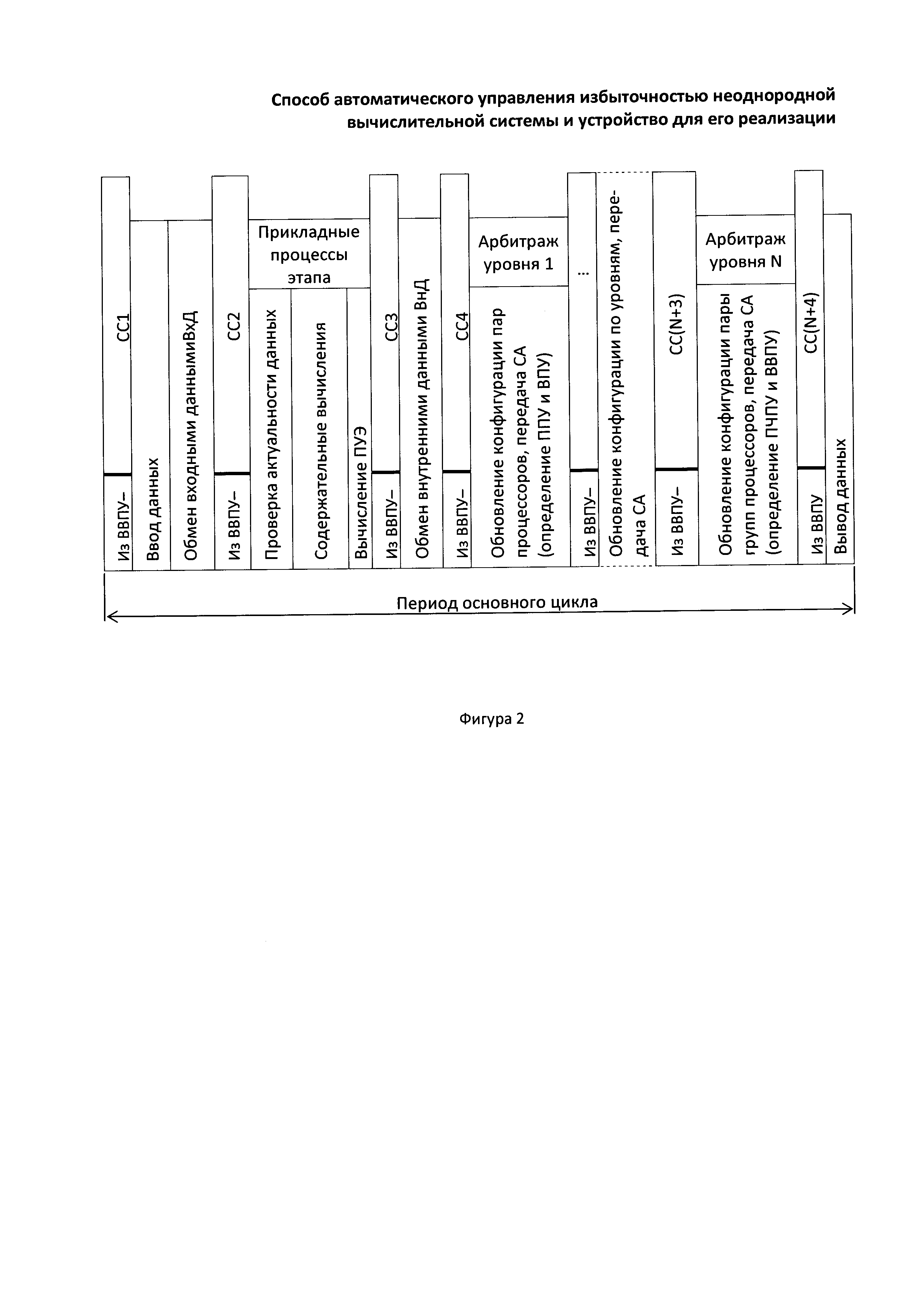

Фиг.2 отображает структуру основного рабочего цикла управления избыточностью.

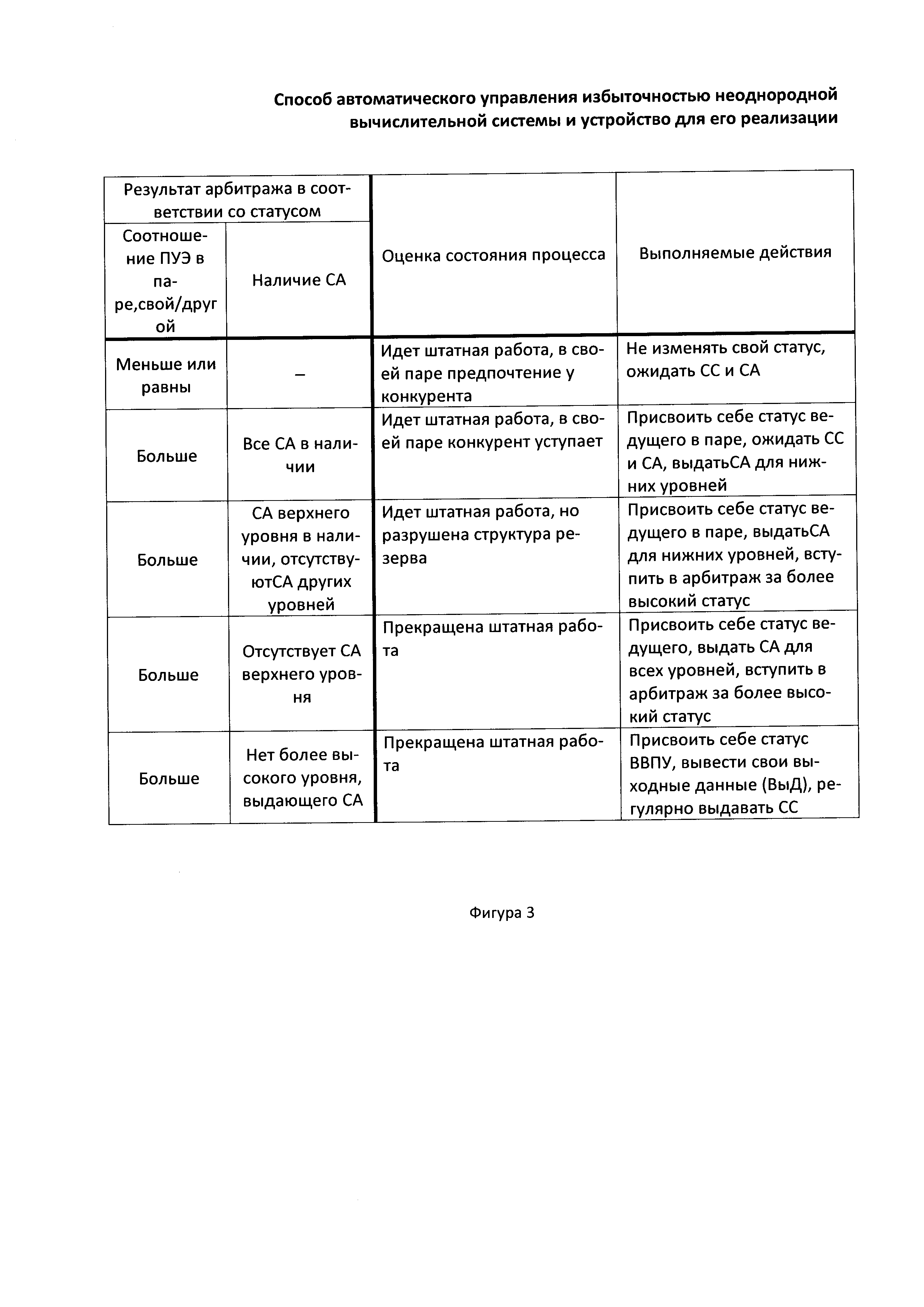

Фиг. 3 - правила действия ПУ по результатам арбитража.

Поскольку способ реализуется при помощи работы устройства (фиг. 1), то полное его описание приведено в разделе пояснения работы этого устройства.

ВС с устройством автоматического управления избыточностью содержит основной и резервный каналы входных данных КВхД, соединенные с входным буфером ВхБ (1), реализующим основную и резервную раздачу данных. С этой целью ВхБ соединен с пулами входных данных всех процессорных узлов ПУ (2) от 1 до W. Каждый ПУ содержит три пула: пул входных данных - Пул ВхД (3), пул внутренних данных - Пул ВнД (4) и пул выходных данных - Пул ВыД (5). Пулы выходных данных соединены с демультипликатором выходных данных ДВыД (6), предназначенным для выборочной передачи основных и резервных выходных данных из ПУ. Для этого блок ДВыД соединен с основным и резервным каналами выходных данных КВыД вычислительной системы. При этом принято, что входные и выходные данные сгруппированы в пакеты, защищенные контрольными кодами. Считается, что ввод и вывод производятся одним действием. После завершения ввода и проверки контрольного кода актуальность данных отмечается соответствующим флагом. Детали операции обмена данными (протоколы, ретрейны) не имеют принципиального значения. В вычислительном процессе помимо входных данных используются внутренние данные, расположенные в соответствующих пулах.

Кроме того, между ПУ имеются межпроцессорные связи (показанные на чертеже условно пунктирными стрелками с полукруглыми окончаниями), позволяющие каждому ПУ обращаться к одноименным пулам других ПУ для получения их входных и внутренних данных с целью восстановления своих данных. Каждый ПУ это осуществляет самостоятельно при отсутствии флага у какого-либо своего пула в определенный промежуток времени. Может оказаться так, что вообще не будет необходимых (ВхД, ВнД) данных. Тогда вычислительный цикл прерывается и выдается сообщение о неисправности в служебный канал индикации.

Работает устройство (фиг. 1) следующим образом.

По входным каналам (основному и резервному) поступают входные данные очередного этапа вычислительного процесса. Эти данные поступают в пулы (основной и резервный соответственно) каждого из 2N ПУ, участвующего в работе ВС. В начале каждого рабочего цикла все флаги, отражающие актуальность данных, обнуляются и устанавливаются после успешного завершения операции по заполнению соответствующего пула.

Причем свои данные выбираются непосредственно из каналов, подключенных к ВС. Остальные данные выбираются из каналов межмашинного обмена (МО).

Основной рабочий цикл вычислительной системы, как показано на фиг. 2, содержит N+4 фаз, где N - число уровней иерархии ВС. Фазы размечаются СС, которые представляют собой пакеты, выдаваемые ВВПУ (ведущий процессорный узел верхнего уровня) во все доступные адреса. СС выдаются как датаграммы без подтверждения. Если какой либо пакет оказался утерянным, то проблема вхождения в синхронизм решается в следующем цикле. Синхропакеты кроме признаков типа пакета и адреса источника имеют в своем составе счетчик циклов, который (в дополнение к таймингу) может использоваться для определения целостности общей обстановки и служить начальными данными для тестовой задачи.

Фазы основного рабочего цикла представляют собой следующие последовательно выполняемые действия:

1. Получение СС1 из текущего ВВПУ-, определенного в предыдущем цикле (на это указывает наличие знака «минус»). Ввод через ВхБ данных из основного и резервного каналов КВхД. Обмен входными данными в случае отсутствия соответствующих флагов актуальности у каких либо пулов ВхД.

2. Получение СС2 из текущего ВВПУ-. Выполнение прикладных процессов, включая проверку актуальности данных, содержательные вычисления решаемой задачи, вычисление показателя успешности решения задачи на текущем этапе (ПУЭ).

3. Получение СС3 из текущего ВВПУ-. Обмен внутренними данными при необходимости восстановления вычислительного процесса в процессорах, не достигших успешного завершения этапа.

4. Получение СС4 из текущего ВВПУ-. Проведение арбитража ПУ на первом (нижнем) уровне иерархии ВС. Присвоение статусов ППУ и В1ПУ на основе сопоставления ПУЭ в парах с учетом правил, приведенных на фиг. 3. В случае отсутствия преимущества какого-либо из ПУ решение принимается на основе дискриминационного правила (например, по порядковому номеру ПУ).

5. Получение СС5 из текущего ВВПУ-. Выдача СА из В1ПУ (подтверждение выполнения роли в соответствии со статусом) для ППУ своей пары. Проведение арбитража процессоров В1ПУ на втором уровне иерархии ВС на роль В2ПУ по правилам, аналогичным п. 4.

N+2. …

N+3. Получение CC(N+3) из текущего ВВПУ-. Выдача ПА из В(N+3)ПУ для более низких уровней иерархии ВС. Проведение арбитража на роль ВВПУ по правилам, аналогичным п. 4.

N+4. Получение CC(N+4) из вновь определенного ВВПУ (на это указывает отсутствие знака «минус»). Выдача данных ВыД из ВВПУ через ДВыД в основной КВыД. Выдача данных ВыД из B(N-1)ПУ через ДВыД в резервный КВыД. После завершения выдачи данных переход к началу цикла.

Каждый ПУ контролирует по таймеру время приема СС и СА, поступающих из ПУ более высокого уровня иерархии. Отсутствие СС или СА в ожидаемое время интерпретируется ПУ как основание для восстановления вычислений и повторного арбитража. Если на этот момент в системе был хотя бы один резервный ПУ, то сохранившиеся в его пуле внутренние данные позволяют восстановить вычисления с минимальной задержкой.

Процедура реконфигурации ВС происходит в фазах, инициируемых сигналами синхронизации, начиная с СС4 и заканчивая CC(N+3) включительно в зависимости от статуса каждого из ПУ. Первоначально каждому ПУ присваивается статус ППУ. Далее процедура предусматривает два процесса: вхождение ПУ в цикл и выход ПУ из цикла. Действия, выполняемые при вхождении в цикл и основания для их выполнения, показаны на фиг. 3. При этом каждым ПУ учитываются как его успешность решения задачи на текущем этапе, так и блокировки, вызванные СА, поступающими от ВчПУ более высокого уровня. Выход (выключение) ППУ никак не сказывается на выполнении основного цикла. Выход (отказ, сбой или неправильное функционирование) любого ВчПУ не вызывает перебоев в выдаче результатов вычислений, но разрушает структуру (цепочку) резервов, которая восстанавливается после проведения арбитража в следующем цикле. Выход ВВПУ приводит к сбою выдачи выходных данных в текущем цикле, вычислительный процесс восстанавливается вместе с новой иерархией ВС в следующем цикле.

Промышленная применимость

Наиболее успешно заявленные способ автоматического управления избыточностью вычислительной системы и устройство для его реализации промышленно применимы в вычислительной и контрольно-измерительной технике и может использоваться для создания отказоустойчивой интегрированной вычислительной среды в перспективных комплексах бортового оборудования подвижных объектов и комплексах автоматизированного управления функционированием производственных и энергетических объектов с целью обеспечения их безотказности и безопасности функционирования.

Примером такого применения является функционирующий прототип фрагмента бортовой интегрированной вычислительной среды авиационного назначения, созданный в ОАО «НИИ авиационного оборудования) в рамках проекта по договору с Минобрнауки в соответствии с Постановлением Правительства РФ от 2010 года №218.

Источники информации

1. Избыточность понятие, определение на Slogos.ru - http://slogos.ru/story/izbytochnost.html

2. Шульга Т.Э. Метод построения восстанавливающих последовательностей для систем без потери информации // Системы управления и информационные технологии. 2009. №3(35). С. 407-411.

3. Патент на изобретение №2413975 с приоритетом от 17.11.2008.

4. Волик Б.Г., Буянов Б.Б., Лубков Н.В. и др. Методы анализа и синтеза структур управляющих систем / Под ред. Б.Г. Волика. - М.: Энергоатомиздат, 1988. С. 242-244.

5. Патенты на изобретение №2430400 с приоритетом от 20.08.2010 и №2431174 с приоритетом от 20.08.2010.