Результат интеллектуальной деятельности: УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x)

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть применено в специализированных ЭВМ, использующих двоичную систему счисления с целочисленным форматом представления исходных данных.

Известно устройство [Гречишников А.Н., Лутай В.Н., Челбасов Н.Г. Использование операций над векторами при выполнении быстрого преобразования Фурье, "Автометрия", №3, 1973] для вычисления функции arctg (y/x) по координатным составляющим у и х, содержащее сумматоры-вычитатели, сдвиговые регистры, логические элементы И.

Его недостатком является низкое быстродействие при большой разрядности вычислительного устройства.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для вычисления функции arctg (y/x) [А.с. 748418 СССР, 1980], содержащее блок управления, три накопительных сдвиговых регистра, регистр записи, два сдвиговых регистра и три сумматора-вычитателя, выходы которых соединены с первыми входами соответствующих накопительных сдвиговых регистров, выход знакового разряда первого накопительного сдвигового регистра соединен с первым входом блока управления, первый, второй, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к управляющим входам первого, второго и третьего накопительных сдвиговых регистров, первого, второго сдвиговых регистров и регистра записи, выходы младшего разряда первого и второго накопительного регистра соединены с первыми входами соответственно первого и второго сумматоров-вычитателей, второй вход второго сумматора-вычитателя подключен к выходу младшего разряда первого сдвигового регистра, соединенного входом с выходом первого накопительного сдвигового регистра, а выход второго накопительного сдвигового регистра соединен с входом второго сдвигового регистра, выход младшего разряда которого соединен со вторым входом первого сумматора-вычитателя, управляющий вход которого соединен с седьмым выходом блока управления и управляющими входами второго и третьего сумматоров-вычитателей, первый и второй входы третьего сумматора-вычитателя соединены соответственно с выходами младших разрядов третьего накопительного сдвигового регистра и регистра записи, элементы И и шифратор, причем выходы одноименных разрядов первого накопительного сдвигового регистра и регистра записи соединены соответственно с первыми и вторыми входами соответствующих элементов И, третьи входы которых соединены с восьмым выходом блока управления, выходы элементов И подключены ко входам шифратора, выходы которого соединены с соответствующими вторыми ÷(n+1)-м входами блока управления.

Недостатком этого устройства является невозможность с его помощью вычисления функции arctg (y/x) в случае, если x и(или) y имеют отрицательный знак. Это не позволяет, например, вычислять аргумент комплексных чисел.

Задачей настоящего изобретения является расширение функциональных возможностей вычисления функции arctg (y/x) при отрицательных значениях входных данных.

Технический результат настоящего изобретения - возможность вычисления аргумента комплексных чисел (в т.ч. при x<0 и/или y<0).

Технический результат достигается предложенным устройством для вычисления функции arctg (y/x), которое содержит блок управления, три накопительных сдвиговых регистра, регистр записи, два сдвиговых регистра и три сумматора-вычитателя, выходы которых соединены с первыми входами соответствующих накопительных сдвиговых регистров, выход знакового разряда первого накопительного сдвигового регистра соединен с первым входом блока управления, первый, второй, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к управляющим входам первого, второго и третьего накопительных сдвиговых регистров, первого, второго сдвиговых регистров и регистра записи, выходы младшего разряда первого и второго накопительного сдвигового регистра соединены с первыми входами соответственно первого и второго сумматоров-вычитателей, второй вход второго сумматора-вычитателя подключен к выходу младшего разряда первого сдвигового регистра, а выход второго накопительного сдвигового регистра с входом второго сдвигового регистра, выход младшего разряда которого соединен с вторым входом первого сумматора-вычитателя, управляющий вход которого соединен с седьмым выходом блока управления и управляющими входами второго и третьего сумматоров-вычитателей, первый и второй входы третьего сумматора-вычитателя соединены соответственно с выходами младших разрядов третьего накопительного сдвигового регистра и регистра записи, а также содержит элементы И и шифратор, причем выходы одноименных разрядов первого накопительного сдвигового регистра и регистра записи соединены соответственно с первыми и вторыми входами соответствующих элементов И, третьи входы которых соединены с восьмым выходом блока управления, выходы элементов И подключены ко входам шифратора, выходы которого соединены с соответствующими вторыми ÷(n+1)-м входами блока управления, кроме того, в него дополнительно введены логико-коммутационный блок и его связи с другими узлами и блоками устройства.

Введение логико-коммутационного блока и его связей с узлами и блоками прототипа позволило расширить функциональные возможности устройства за счет его способности вычислять функцию arctg (y/x) в случае любых знаков (+ или -) входных данных x и y. Это является новым техническим решением в технике цифровых вычислительных устройств, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволило выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют расширить функциональные возможности устройства, в частности вычисление функции arctg (y/x) при разных значениях (+ или -) исходных величин.

Предложенное устройство для вычисления arctg (y/x) промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических элементов).

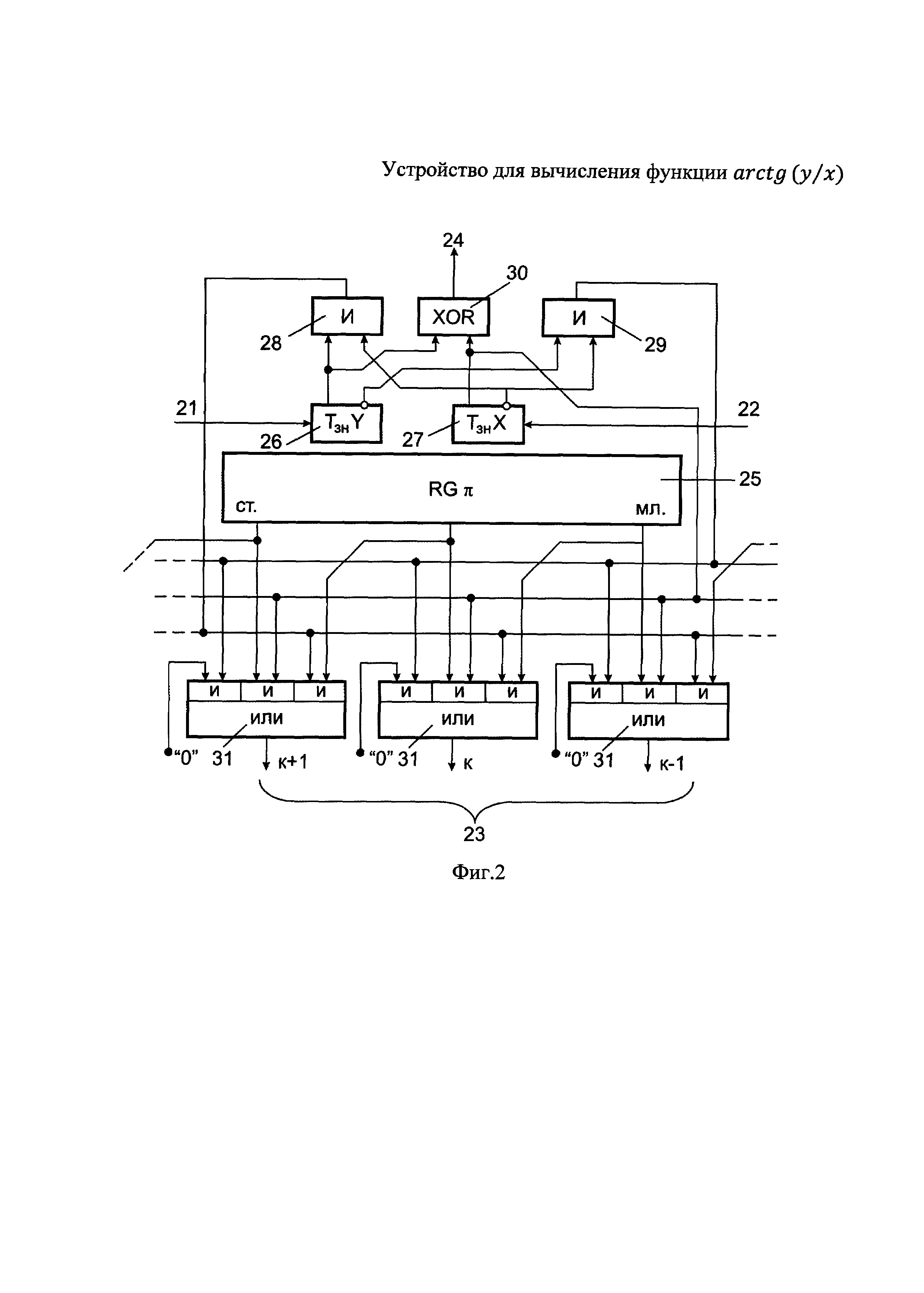

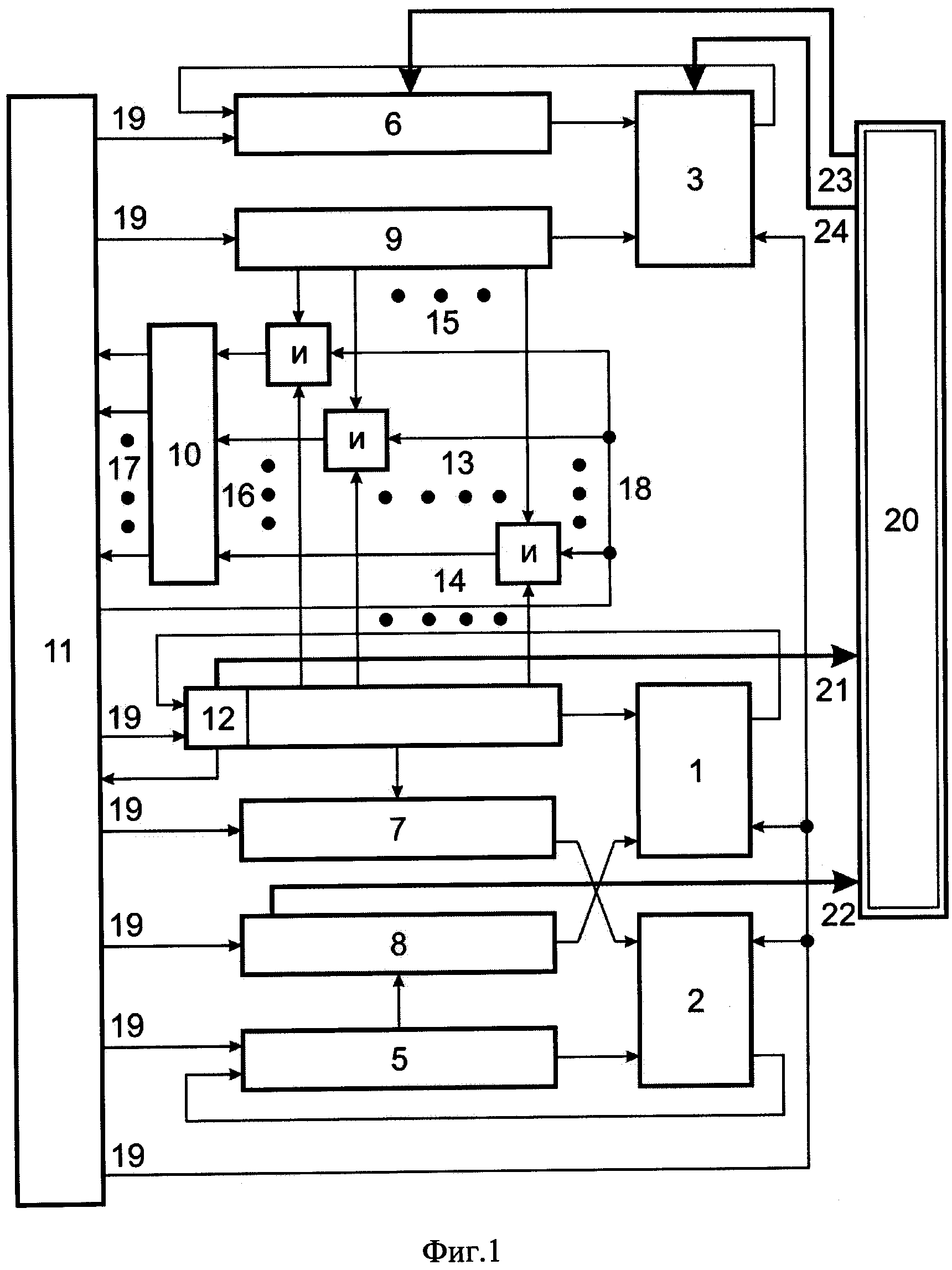

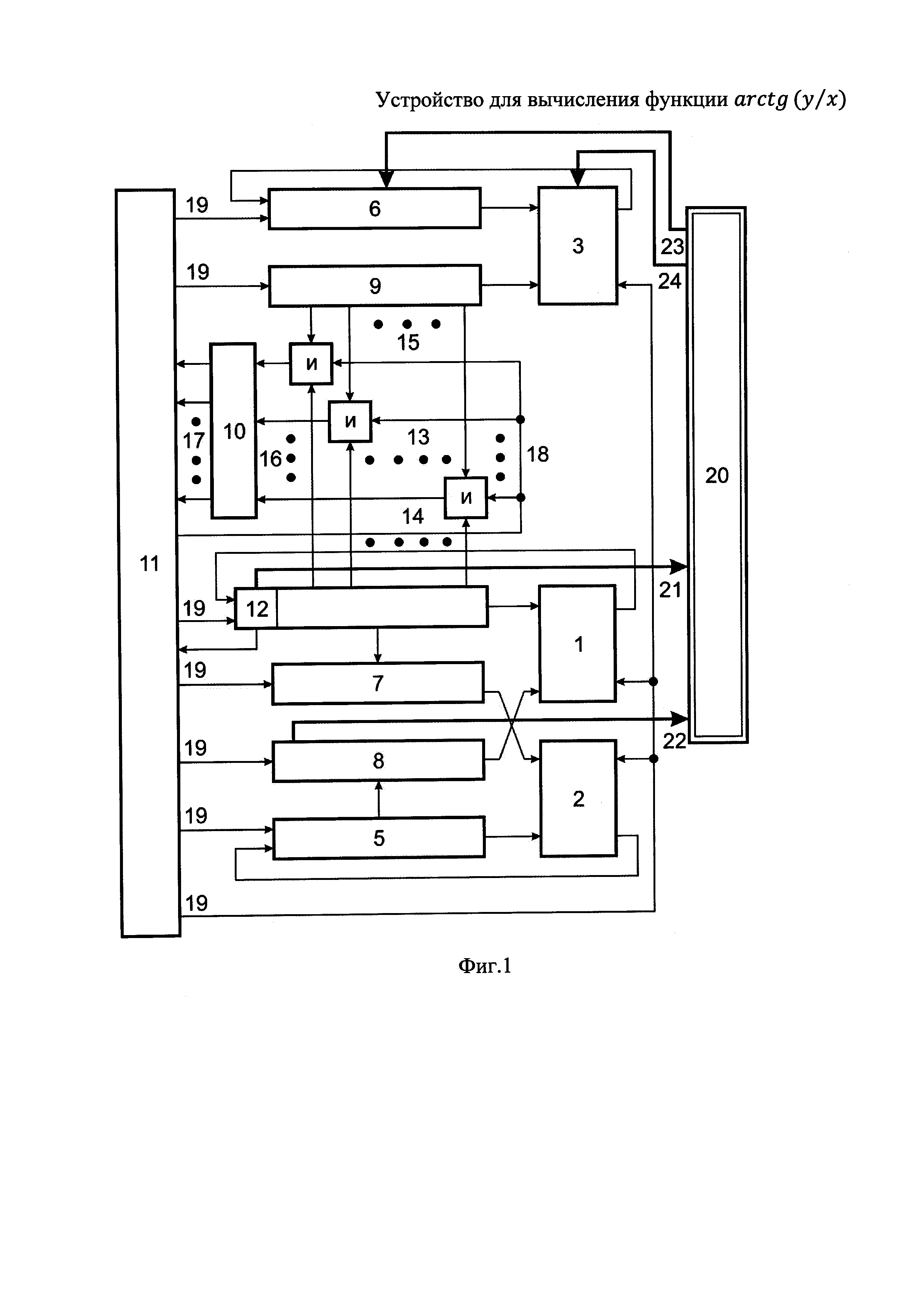

На фиг. 1 представлена структурная схема устройства для вычисления функции arctg (y/x), а на фиг. 2 - функциональная схема логико-коммутационного блока этого устройства.

Заявленное устройство содержит блок управления 11, три накопительных сдвиговых регистра 4, 5, 6, регистр записи 9, два сдвиговых регистра 7, 8 и три сумматора-вычитателя 1, 2, 3, выходы которых соединены с первыми входами соответствующих накопительных сдвиговых регистров 4, 5, 6, выход знакового разряда 12 первого накопительного сдвигового регистра 4 соединен с первым входом блока управления 11, первый, второй, третий, четвертый, пятый и шестой выходы 19 блока управления 11 подключены соответственно к управляющим входам первого, второго и третьего накопительных сдвиговых регистров 4, 5, 6, первого, второго сдвиговых регистров 7, 8 и регистра записи 9, выходы младшего разряда первого и второго накопительных сдвиговых регистров 4, 5 соединены с первыми входами соответственно первого и второго сумматоров-вычитателей 1, 2, второй вход второго сумматора-вычитателя 2 подключен к выходу младшего разряда первого сдвигающего регистра 7, соединенного входом с выходом первого накопительного сдвигового регистра 4, а выход второго накопительного сдвигового регистра 5 - со входом второго сдвигового регистра 8, выход младшего разряда которого соединен со вторым входом первого сумматора-вычитателя 1, управляющий вход которого соединен с седьмым выходом блока управления 11 и управляющими входами второго и третьего сумматоров-вычитателей 2, 3, первый и второй входы третьего сумматора-вычитателя 3 соединены соответственно с выходами младших разрядов третьего накопительного сдвигового регистра 6 и регистра записи 9. Кроме того, входы 14, 15, 18 элементов И связаны с выходами одноименных разрядов первого накопительного сдвигового регистра 4, регистра записи 9 и блока управления 11, а выходы 16 элементов И подключены ко входам шифратора 10, выходы которого соединены с соответствующими вторым ÷(n+1)-м входами блока управления 11. Дополнительно введены логико-коммутационный блок 20 и связи его первого 21 и второго 22 входов со знаковыми разрядами накопительных сдвиговых регистров 4 и 8 соответственно, а его первый 23 и второй 24 выходы соединены с третьим накопительным сдвиговым регистром 6 и с третьим сумматором-вычитателем 3.

Логико-коммутационный блок 20 состоит из регистра 25 константы "π" в двоичном коде, первого 26 и второго 27 триггеров знака Y и X соответственно, первого 28 и второго 29 элементов И, элемента XOR 30 (Исключительное ИЛИ), (n+3) логических схем 2И-3ИЛИ 31 (по числу двоичных разрядов представления величины "2π"). При этом первый 21 и второй 22 входы логико-коммутационного блока связаны с первым 26 и вторым 27 триггерами знака соответственно, а их выходы (прямой и инверсивный) связаны со входами элементов И 28 и 29, а также элемента XOR 30, действующего в соответствии с ниже приведенным алгоритмом (формула 7). Выходы элементов И 28, 29 связаны со входами всех логических схем 2И-3ИЛИ 31, а выход элемента XOR - с первым выходом 24 логико-коммутационного блока 20.

Совокупность выходов всех логических схем 2И-3ИЛИ 31 образует многоканальный ((n+3) разрядов) второй выход 23 логико-коммутационного блока 20.

Работа устройства основана на следующем. Поскольку в конце операции величина Y сводится к нулю, то можно задавать для первого шага итерации вместо i=0 некоторое начальное значение i0, зависящее от разности между Y и нулем. То есть i0 определяется номером разряда, содержащего первую значащую единицу в двоичном представлении аргумента. Например, Y представлен кодом 0,000001101… Тогда i0=6, и число итераций будет равно n - i0+1.

Устройство работает следующим образом. В регистр 9 записывается число, представленное единицами во всех разрядах после запятой, в регистр 4 заносится значение аргумента Υ. Затем на входы элементов И 13 поочередно, в соответствии с сигналами управления входов 18, начиная со старшего разряда, подаются значения содержимого одноименных разрядов 14 и 15 регистров 4 и 9.

По сигналу первого же элемента И, на входы которого поступают обе единицы с регистров 4 и 9 и разрешающий сигнал из блока 11 управления, опрос регистров прекращается, а с соответствующего выхода 17 шифратора 10 на блок 11 управления передается код начального шага итерации i0. Так элемент И на своем выходе 16 выделяет первую значащую единицу аргумента Y.

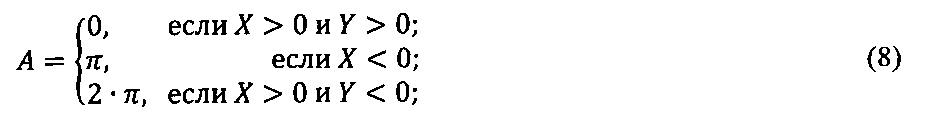

В соответствии с итерационными соотношениями (1)÷(8) блок 11 управления передает команду сдвига содержимого регистра 4 на i0 разрядов в сторону младших разрядов. Регистр 9 сбрасывается в нуль, и на него из регистра записи вызывается константа arctg 2-i. В регистр 5 заносится единица, в регистр 6 записывается ноль. Затем из содержимого регистра 4 в сумматоре-вычитателе 1, с учетом знака φi, вычитается сдвинутое в сторону младших разрядов содержимое регистра 5, поступающее из второго сдвигового регистра 8, а содержимое регистра 5 складывается с учетом знака φi в сумматоре-вычитателе 2 со сдвинутым в сторону младших разрядов содержимым регистра 4, поступающим из первого сдвигового регистра 7. Содержимое регистра 6 суммируется с учетом знака φi с содержимым регистра 9 в сумматоре-вычитателе 3. На следующем цикле значение i0 увеличивается на единицу, в регистр 9 заносится из регистра записи константа  и определяется очередное значение рекуррентного оператора φi, и итерационные соотношения (1)÷(8) реализуются согласно описанному алгоритму с учетом i, φi и α.

и определяется очередное значение рекуррентного оператора φi, и итерационные соотношения (1)÷(8) реализуются согласно описанному алгоритму с учетом i, φi и α.

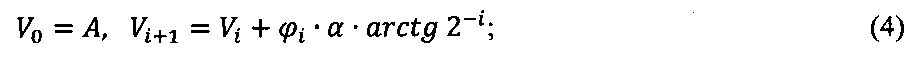

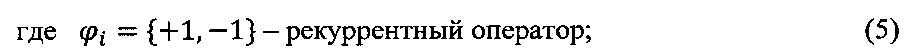

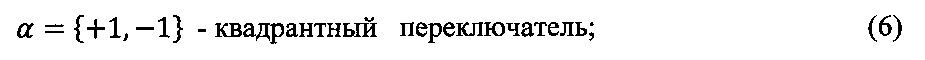

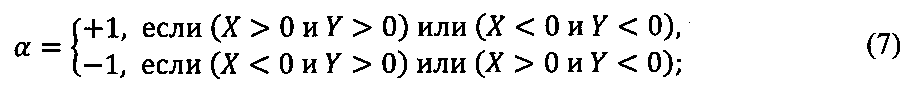

Устройство работает, используя следующие рекуррентные соотношения:

i=0, 1, 2, …, m - номер итерации (m≤n), n - разрядность входных величин (без знака) Y и X.

Роль определителей значений α и А по формулам (7) и (8) выполняет логико-коммутационный блок 20 с помощью регистра 25, содержащего число "π", и ряда логических схем И 28 и 29, XOR 30, (n+3) логических схем 2И-3ИЛИ 31 по информации от двух триггеров знака 26 и 27. Они получают ее по входу 21 и входу 22 от знаковых разрядов первого 4 и второго 8 накопительных сдвиговых регистров. В зависимости от номера квадранта в алгоритм (4) вносится поправка V0=А={0, π, 2π} (8), а также в знак (+ или -) констант arctg 2-i (4).

Квадрантный переключатель α определяется логической схемой XOR 30 по сигналам от прямых выходов двух триггеров 26 и 27 знака. Этот сигнал α подается через первый выход 24 на управляющий вход третьего 3 сумматора-вычитателя, изменяя сложение на вычитание или наоборот. Значение А, выработанное в логико-коммутационном блоке 20, передается через его второй 24 выход в третий накопительный сдвиговый регистр 6, где оно участвует в итерационном процессе (1)÷(4). В конце итераций в первом накопительном сдвиговом регистре 4 получается ноль, а в третьем накопительном сдвиговом регистре 6 хранится значение, равное arctg (y/x).

Устройство для вычисления функции arctg (y/x), содержащее блок управления, три накопительных сдвиговых регистра, регистр записи, два сдвигающих регистра и три сумматора-вычитателя, выходы которых соединены с первыми входами соответствующих накопительных сдвиговых регистров, выход знакового разряда первого накопительного сдвигового регистра соединен с первым входом блока управления, первый, второй, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к управляющим входам первого, второго и третьего накопительных сдвиговых регистров, первого, второго сдвиговых регистров и регистра записи, выходы младшего разряда первого и второго накопительных сдвиговых регистров соединены с первыми входами соответственно первого и второго сумматоров-вычитателей, второй вход второго сумматора-вычитателя подключен к выходу младшего разряда первого сдвигового регистра, соединенного входом с выходом первого накопительного сдвигового регистра, а выход второго накопительного сдвигового регистра - с входом второго сдвигающего регистра, выход младшего разряда которого соединен со вторым входом первого сумматора-вычитателя, управляющий вход которого соединен с седьмым выходом блока управления и управляющими входами второго и третьего сумматоров-вычитателей, первый и второй входы третьего сумматора-вычитателя соединены соответственно с выходами младших разрядов третьего накопительного сдвигового регистра и регистра записи, элементы И и шифратор, причем выходы одноименных разрядов первого накопительного сдвигового регистра и регистра записи соединены соответственно с первыми и вторыми входами соответствующих элементов И, третьи входы которых соединены с восьмым выходом блока управления, выходы элементов И подключены ко входам шифратора, выходы которого соединены с соответствующими вторым ÷(+1)-м входами блоками управления, отличающееся тем, что дополнительно содержит логико-коммутационный блок, содержащий регистр константы "π", два триггера знака, два логических элемента И, логический элемент XOR (Исключительное ИЛИ), поразрядные логические схемы 2И-3ИЛИ, при этом первый и второй входы логико-коммутационного блока связаны с знаковыми разрядами первого и второго накопительных сдвиговых регистров соответственно, кроме того, первый и второй входы логико-коммутационного блока связаны с установочными входами первого и второго триггеров знака соответственно, а их выходы связаны со входами двух элементов И, а также элемента XOR, выходы элементов И связаны с входами поразрядных логических схем 2И-3ИЛИ, а выход элемента XOR - с первым выходом логико-коммутационного блока, в свою очередь связанного с управляющим входом третьего сумматора-вычитателя, а выходы всех поразрядных логических схем 2И-3ИЛИ связаны со вторым выходом логико-коммутационного блока, который связан с третьим накопительным сдвиговым регистром.