Результат интеллектуальной деятельности: ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ

Вид РИД

Изобретение

Изобретение относится к области радиотехники и автоматики и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре быстродействующих аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ), мультидифференциальных ОУ и т.п.).

Известны схемы комплементарных входных каскадов ОУ на КМОП-транзисторах [1-18]. Дифференциальные входные каскады данного класса стали основным усилительным элементом многих аналоговых интерфейсов.

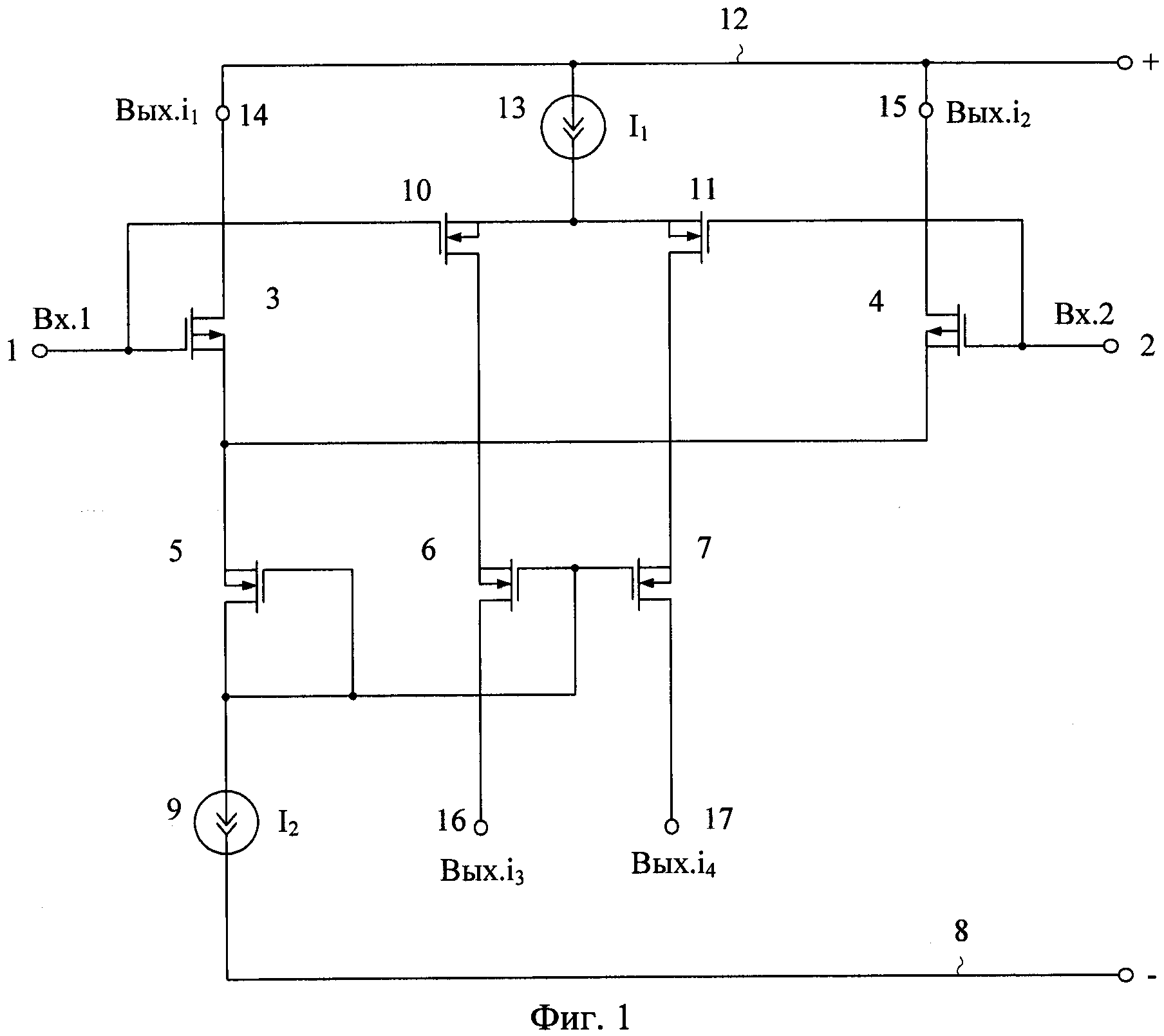

Ближайшим прототипом (фиг. 1) заявляемого устройства является комплементарный дифференциальный входной каскад по патенту US 5.444.413, содержащий первый 1 и второй 2 входы, первый 3 и второй 4 входные полевые транзисторы, истоки которых объединены, а затворы связаны с соответствующими первым 1 и вторым 2 входами, объединенные истоки первого 3 и второго 4 входных полевых транзисторов подключены через цепь смещения потенциалов 5 к объединенным затворам первого 6 и второго 7 выходных транзисторов, объединенные затворы первого 6 и второго 7 выходных транзисторов связаны с первой 8 шиной источника питания через токостабилизирующий двухполюсник 9, третий 10 и четвертый 11 входные полевые транзисторы, объединенные истоки которых соединены со второй 12 шиной источника питания через второй 13 токостабилизирующий двухполюсник, затвор третьего 10 входного полевого транзистора подключен к первому 1 входу устройства, затвор четвертого 11 входного полевого транзистора соединен со вторым 2 входом устройства, сток третьего 10 входного полевого транзистора соединен с истоком первого 6 выходного транзистора, сток четвертого 11 входного полевого транзистора соединен с истоком второго 7 выходного транзистора, причем первый 14 токовый выход устройства, согласованный со второй 12 шиной источника питания, соединен со стоком первого 3 входного полевого транзистора, второй 15 токовый выход устройства, согласованный со второй 12 шиной источника питания, соединен со стоком второго 4 входного полевого транзистора, третий 16 токовый выход устройства, согласованный с первой 8 шиной источника питания, соединен со стоком первого 6 выходного транзистора, а четвертый 17 токовый выход устройства, согласованный с первой 8 шиной источника питания, соединен со стоком второго 7 выходного транзистора.

Существенный недостаток известного дифференциального входного каскада (ДК) состоит в том, что он имеет сравнительно узкий динамический диапазон (Uгр) линейного усиления дифференциальных сигналов (Uвх.max<Uгр≈100÷150 мВ) [19]. Как показано в монографиях авторов настоящей заявки [19-20], это обстоятельство является главной причиной невысокого быстродействия современных операционных усилителей, обусловленной нелинейным режимом работы их входного ДК. При этом для большинства ОУ с высокоимпедансным узлом и одним корректирующим конденсатором (Ск) максимальная скорость нарастания выходного напряжения определяется формулой [19-20]:

где fcp - частота единичного усиления (частота среза) скорректированного ОУ;

Uгр - напряжение ограничения проходной характеристики iвых=f(uвх) входного каскада (для классических ДК на биполярных транзисторах и полевых транзисторах в микрорежиме Uгр=50÷100 мВ).

Из (1) следует, что повышение υΒΜΧ можно осуществить двумя качественно разными путями [19-20]:

1. Увеличением диапазона активной работы входного ДК (т.е. напряжения Uгр) без изменения крутизны преобразования входного напряжения в выходные токи ДК.

2. Повышением fcp за счет улучшения частотных свойств транзисторов, что связано, прежде всего, с использованием более высокочастотных и дорогостоящих техпроцессов (SG25VD, SG25H1,SG25RH и др.).

Заявляемый входной каскад ОУ решает задачу повышения быстродействия за счет увеличения в несколько раз диапазона активной работы входного каскада (без изменения его крутизны), измеряемого напряжением ограничения (Uгр).

Кроме этого предлагаемый ДК достаточно эффективен в мультидифференциальных ОУ [21, 22], где от входных каскадов требуется достаточно широкий диапазон линейной работы.

Таким образом, основная задача предлагаемого изобретения состоит в расширении диапазона активной работы дифференциального входного каскада - получении граничных напряжений его проходной характеристики iвых=f(uвх) на уровне нескольких вольт.

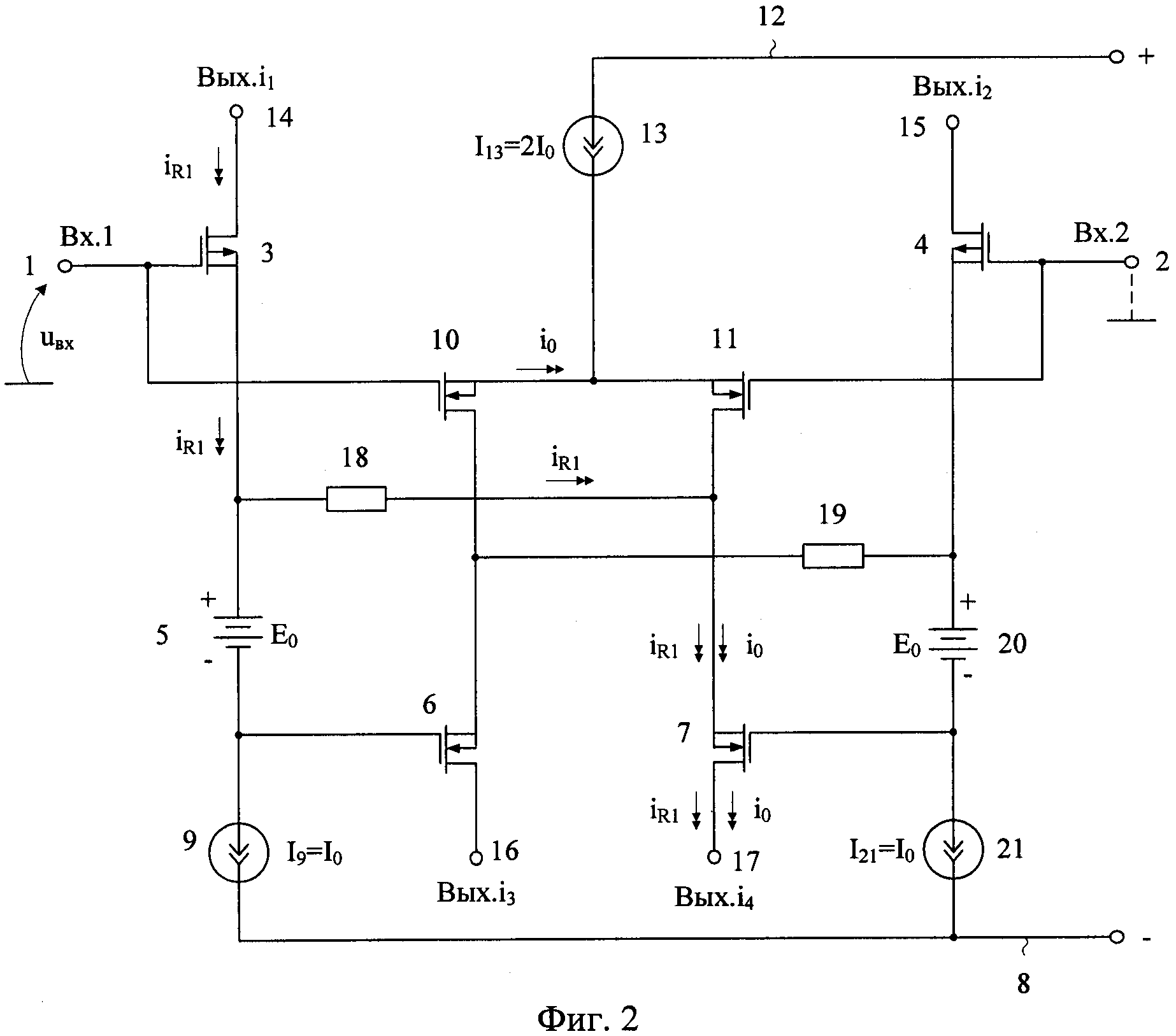

Поставленная задача достигается тем, что в дифференциальном входном каскаде быстродействующего операционного усилителя для КМОП-техпроцессов (фиг. 1), содержащем первый 1 и второй 2 входы, первый 3 и второй 4 входные полевые транзисторы, истоки которых объединены, а затворы связаны с соответствующими первым 1 и вторым 2 входами, объединенные истоки первого 3 и второго 4 входных полевых транзисторов подключены через цепь смещения потенциалов 5 к объединенным затворам первого 6 и второго 7 выходных транзисторов, объединенные затворы первого 6 и второго 7 выходных транзисторов связаны с первой 8 шиной источника питания через токостабилизирующий двухполюсник 9, третий 10 и четвертый 11 входные полевые транзисторы, объединенные истоки которых соединены со второй 12 шиной источника питания через второй 13 токостабилизирующий двухполюсник, затвор третьего 10 входного полевого транзистора подключен к первому 1 входу устройства, затвор четвертого 11 входного полевого транзистора соединен со вторым 2 входом устройства, сток третьего 10 входного полевого транзистора соединен с истоком первого 6 выходного транзистора, сток четвертого 11 входного полевого транзистора соединен с истоком второго 7 выходного транзистора, причем первый 14 токовый выход устройства, согласованный со второй 12 шиной источника питания, соединен со стоком первого 3 входного полевого транзистора, второй 15 токовый выход устройства, согласованный со второй 12 шиной источника питания, соединен со стоком второго 4 входного полевого транзистора, третий 16 токовый выход устройства, согласованный с первой 8 шиной источника питания, соединен со стоком первого 6 выходного транзистора, а четвертый 17 токовый выход устройства, согласованный с первой 8 шиной источника питания, соединен со стоком второго 7 выходного транзистора, предусмотрены новые элементы и связи - исток первого 3 входного транзистора соединен со стоком четвертого 11 входного полевого транзистора через первый 18 дополнительный резистор, исток второго 4 входного транзистора соединен со стоком третьего 10 входного полевого транзистора через второй 19 дополнительный резистор и через дополнительную цепь смещения потенциалов 20 связан с затвором второго 7 выходного транзистора, который подключен ко второй 12 шине источника питания через дополнительный токостабилизирующий двухполюсник 21.

Схема усилителя-прототипа представлена на фиг. 1. На фиг. 2 показано заявляемое устройство в соответствии с формулой изобретения.

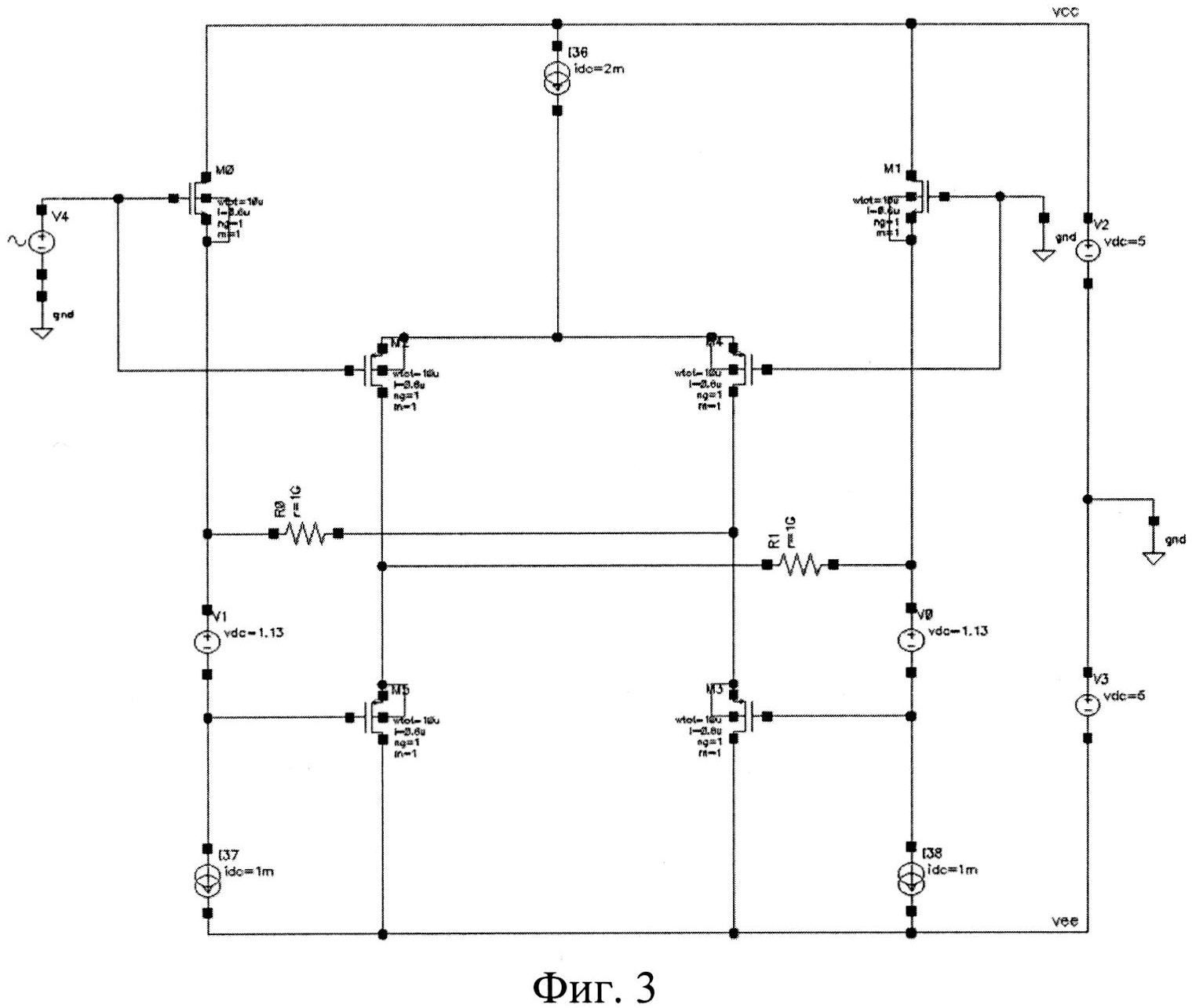

На фиг. 3 показана схема заявляемого дифференциального каскада с идеальными источниками цепи смещения потенциалов 5 и дополнительной цепи смещения потенциалов 20 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НЛП «Пульсар».

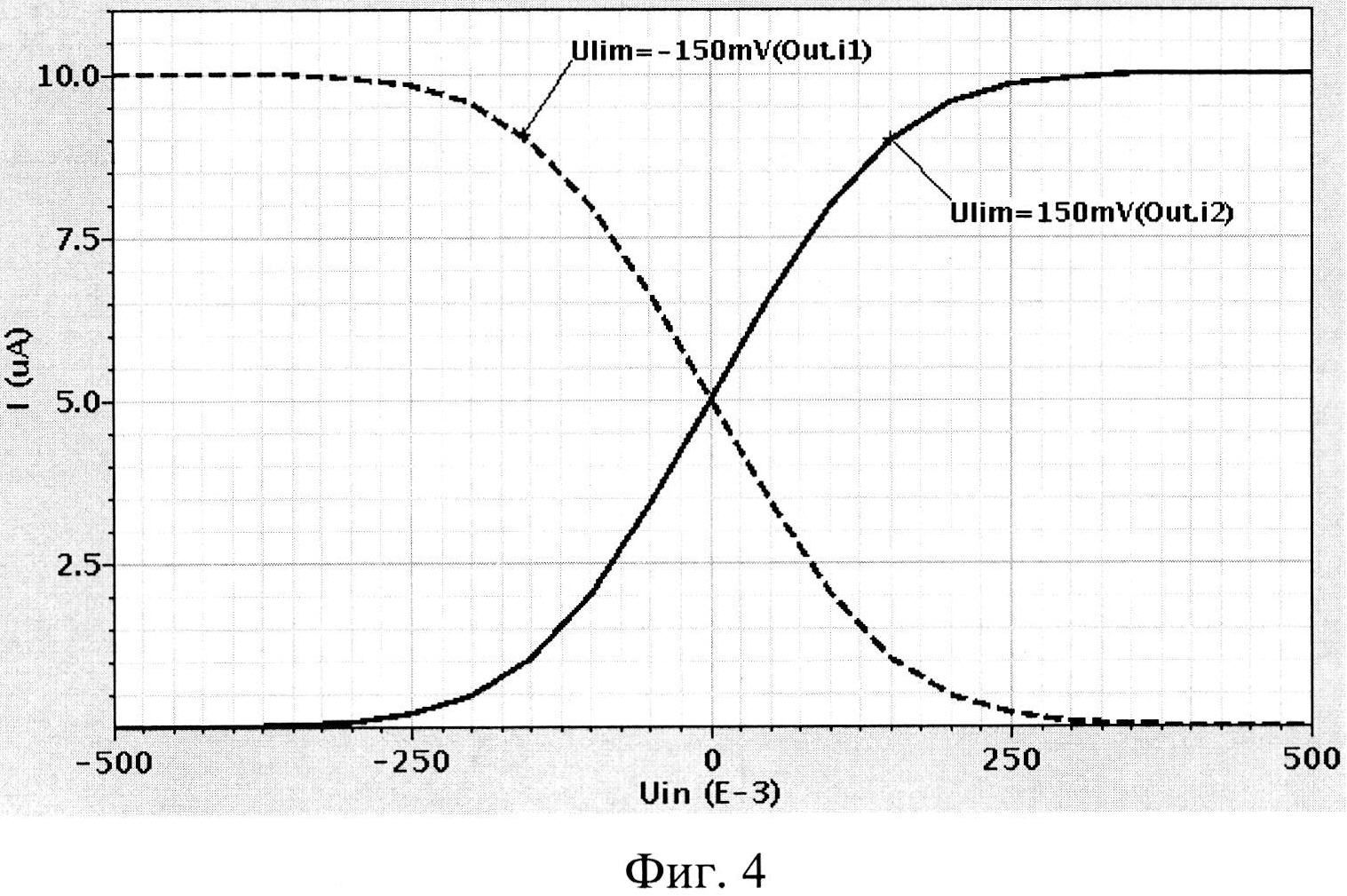

На фиг. 4 показана зависимость выходных токов ДК-прототипа от изменения входного дифференциального напряжения при малом суммарном токе его общей истоковой цепи (I1=10 мкА). Из данного графика следует, что диапазон активной работы ДК-прототипа лежит в пределах 100-150 мВ и практически не отличается от диапазона активной работы классических дифференциальных каскадов на биполярных транзисторах [19, 20]. Данное обстоятельство является основной причиной невысокого быстродействия КМОП-операционных усилителей на основе известной схемы ДК.

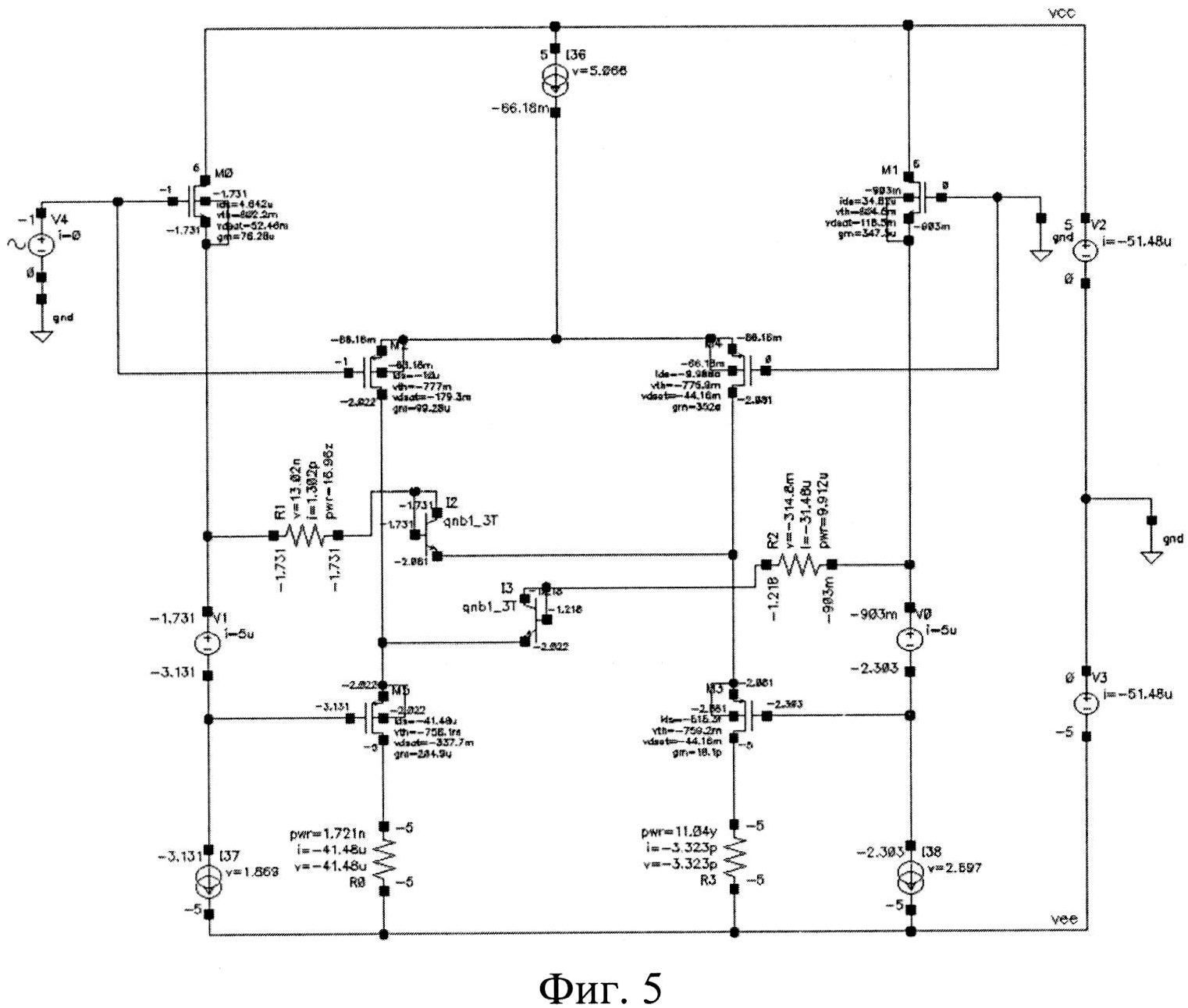

На фиг. 5 приведена схема фиг. 3, в которой последовательно с первым 18 и вторым 19 дополнительными резисторами введены дополнительные нелинейные элементы (p-n переходы), расширяющие возможности исходной схемы при работе с большими входными сигналами.

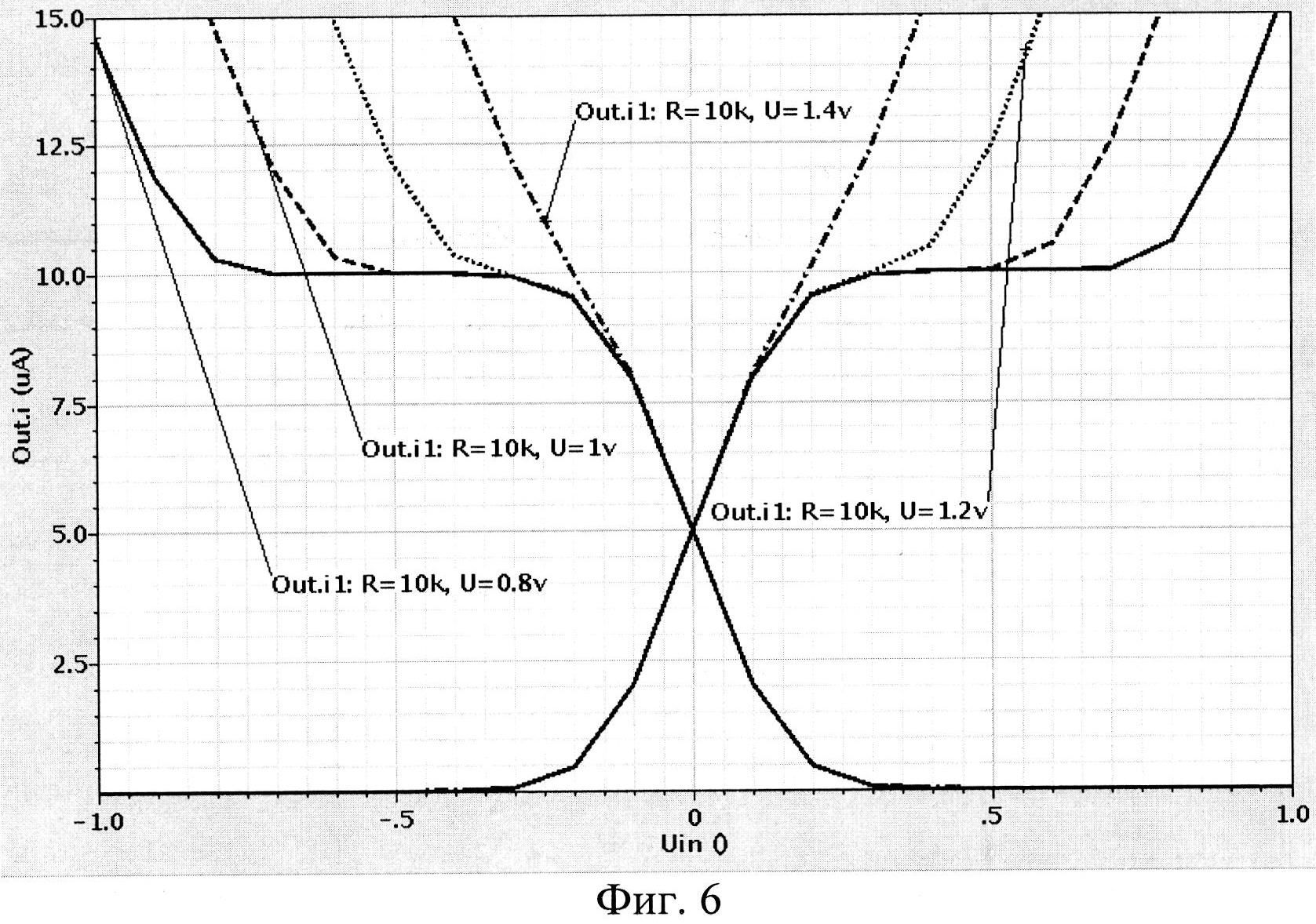

На фиг. 6 представлена зависимость выходных токов ДК фиг. 5 при разных значениях напряжений цепи смещения потенциалов 5 и дополнительной цепи смещения потенциалов 20. Данный график показывает, что в схеме фиг. 5 возможно формирование зон нечувствительности на проходной характеристике, что расширяет возможности исходной схемы.

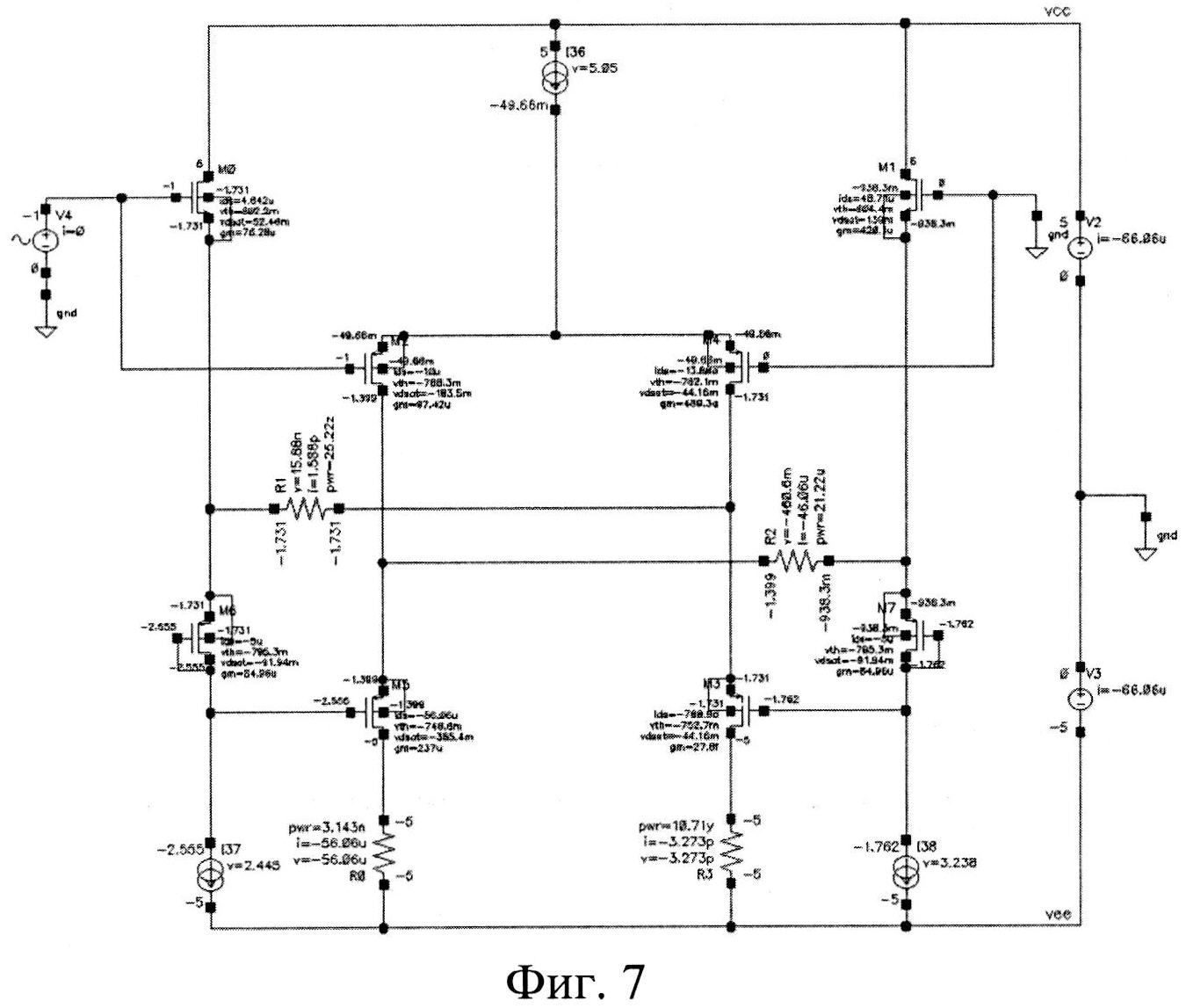

На фиг. 7 представлена схема заявляемого ДК фиг. 2, в котором источники напряжения цепи смещения потенциалов 5 и дополнительной цепи смещения потенциалов 20 выполнены, в частном случае, на полевых транзисторах с закороченными выводами затвора и стока.

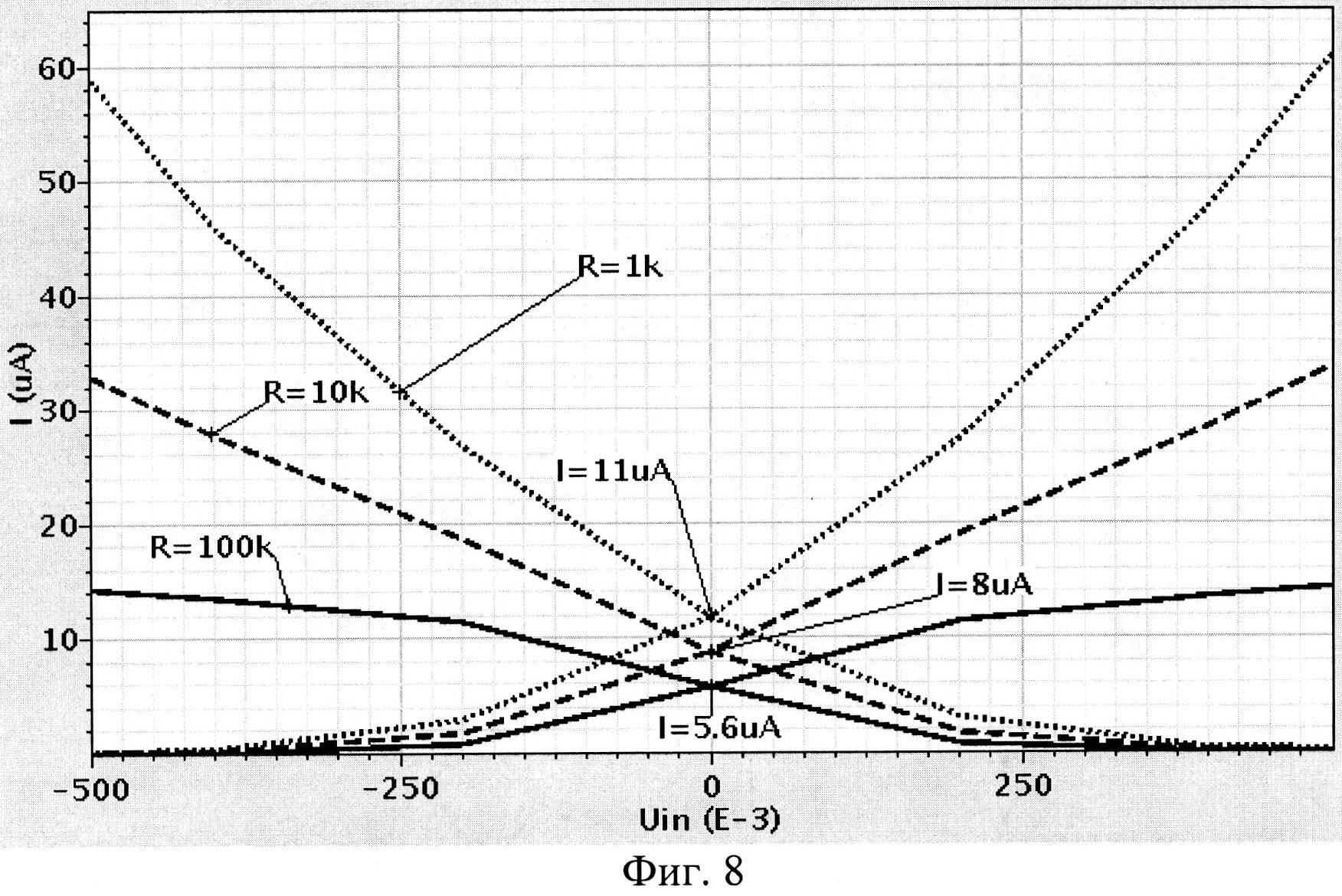

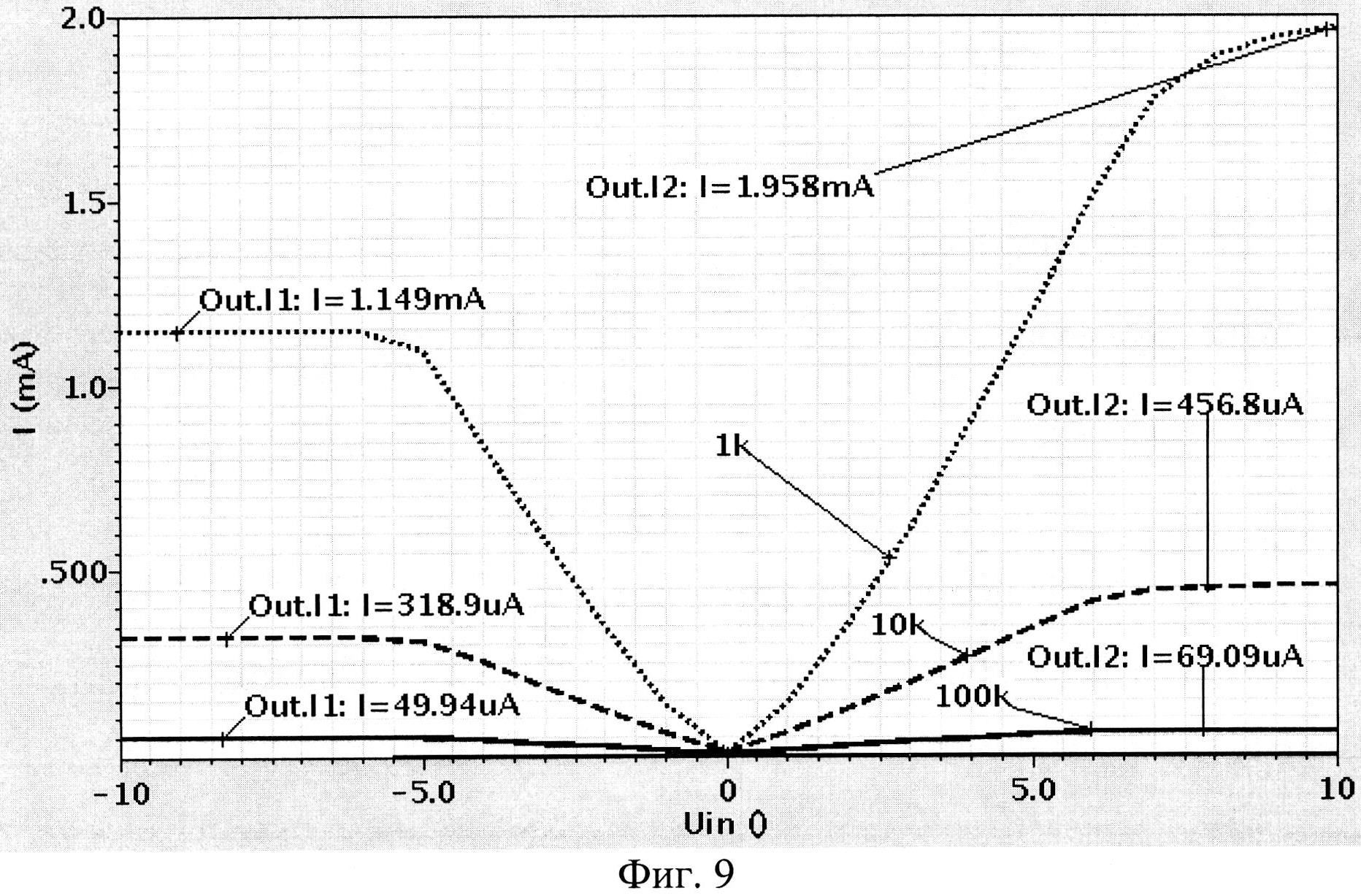

На фиг. 8 приведены проходные характеристики съемы фиг. 7 в мелком, а на фиг. 9 - в крупном масштабах при разных значениях сопротивлений первого 18 и второго 19 дополнительных резисторов.

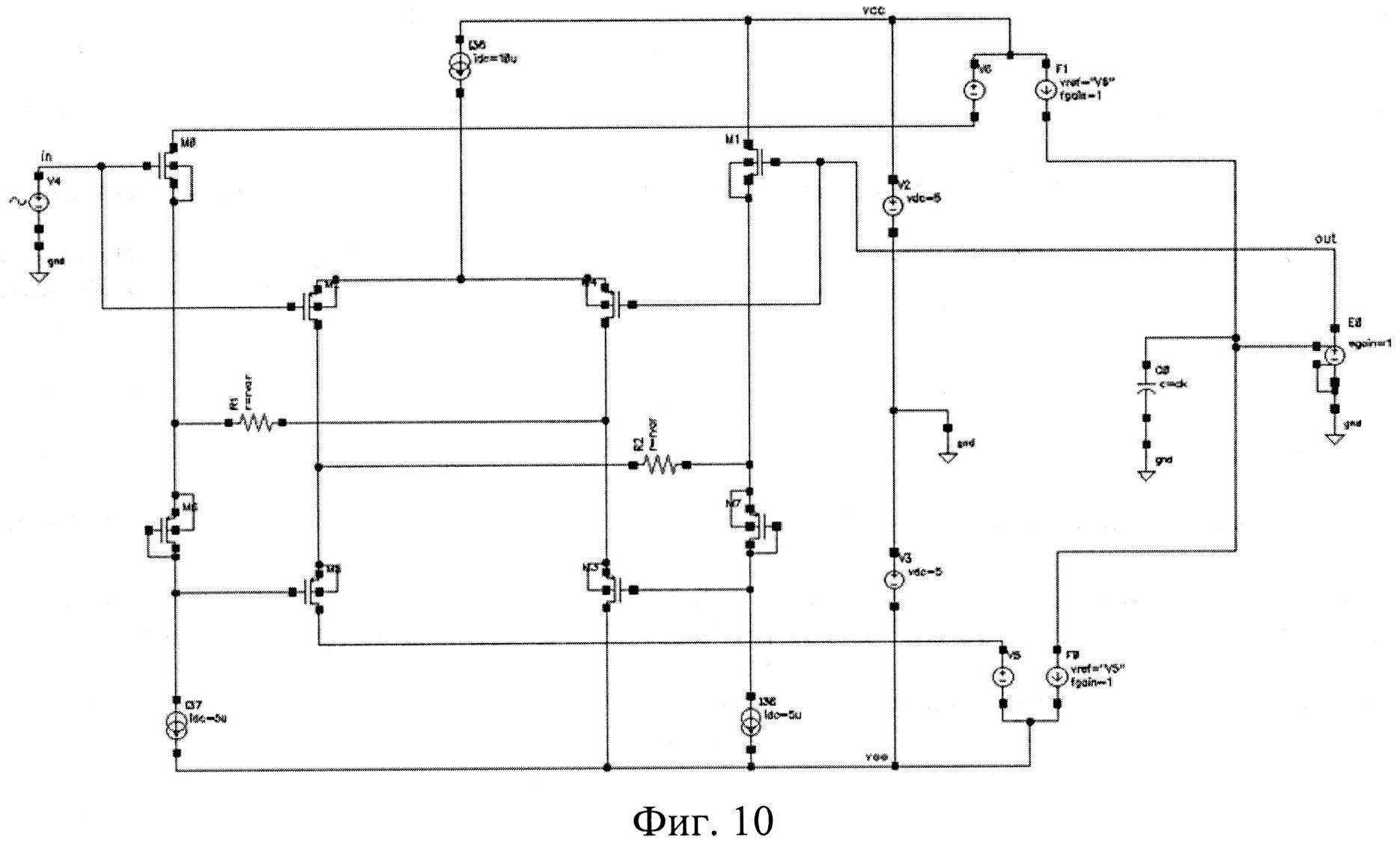

На фиг. 10 в качестве примера показана схема микромощного (I13=10 мкА) быстродействующего КМОП-операционного усилителя в среде Cadence на базе заявляемого ДК фиг. 2.

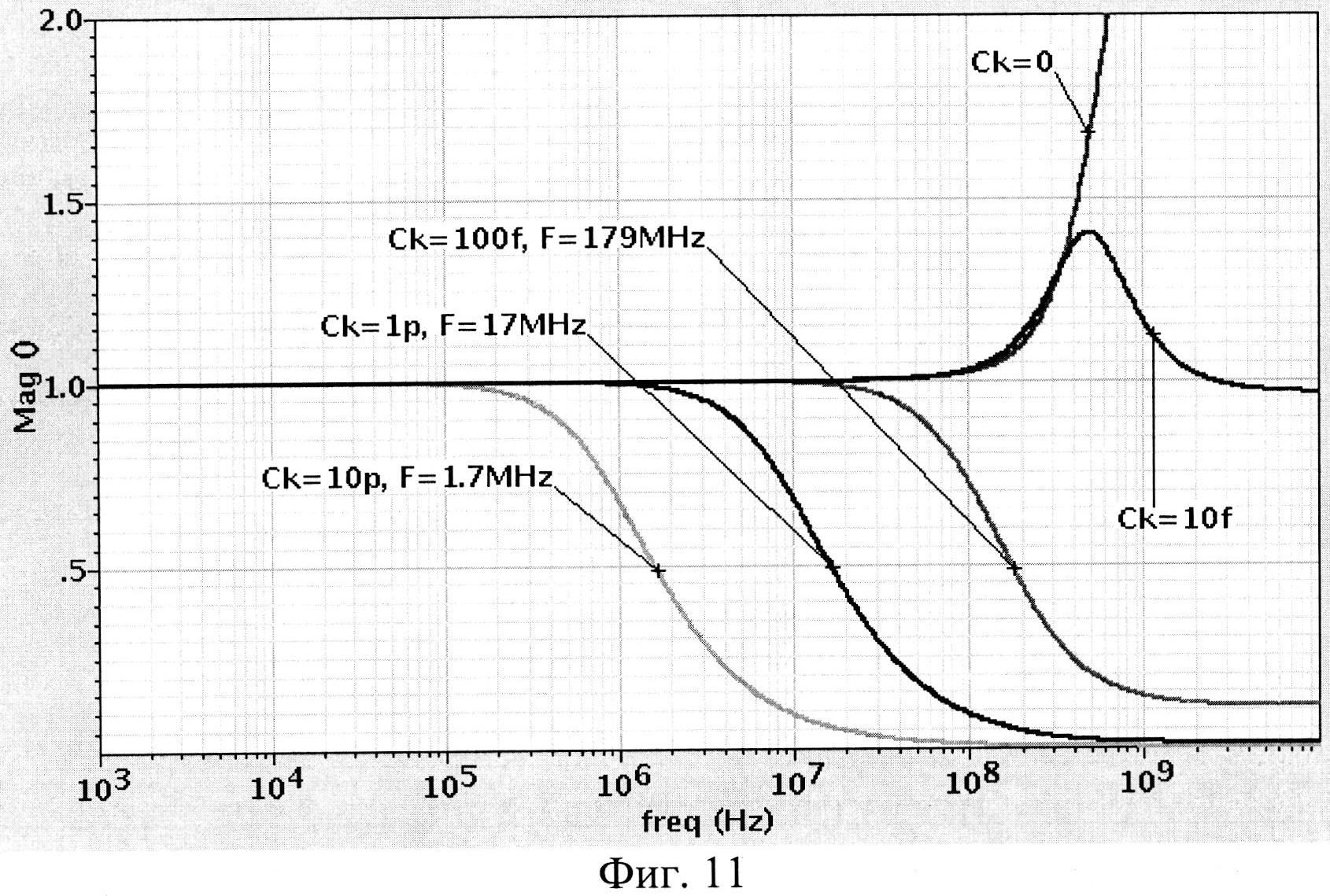

На фиг. 11 приведены амплитудно-частотные характеристики операционного усилителя фиг. 10 со 100% отрицательной обратной связью при различных значениях традиционной емкости коррекции Ck.

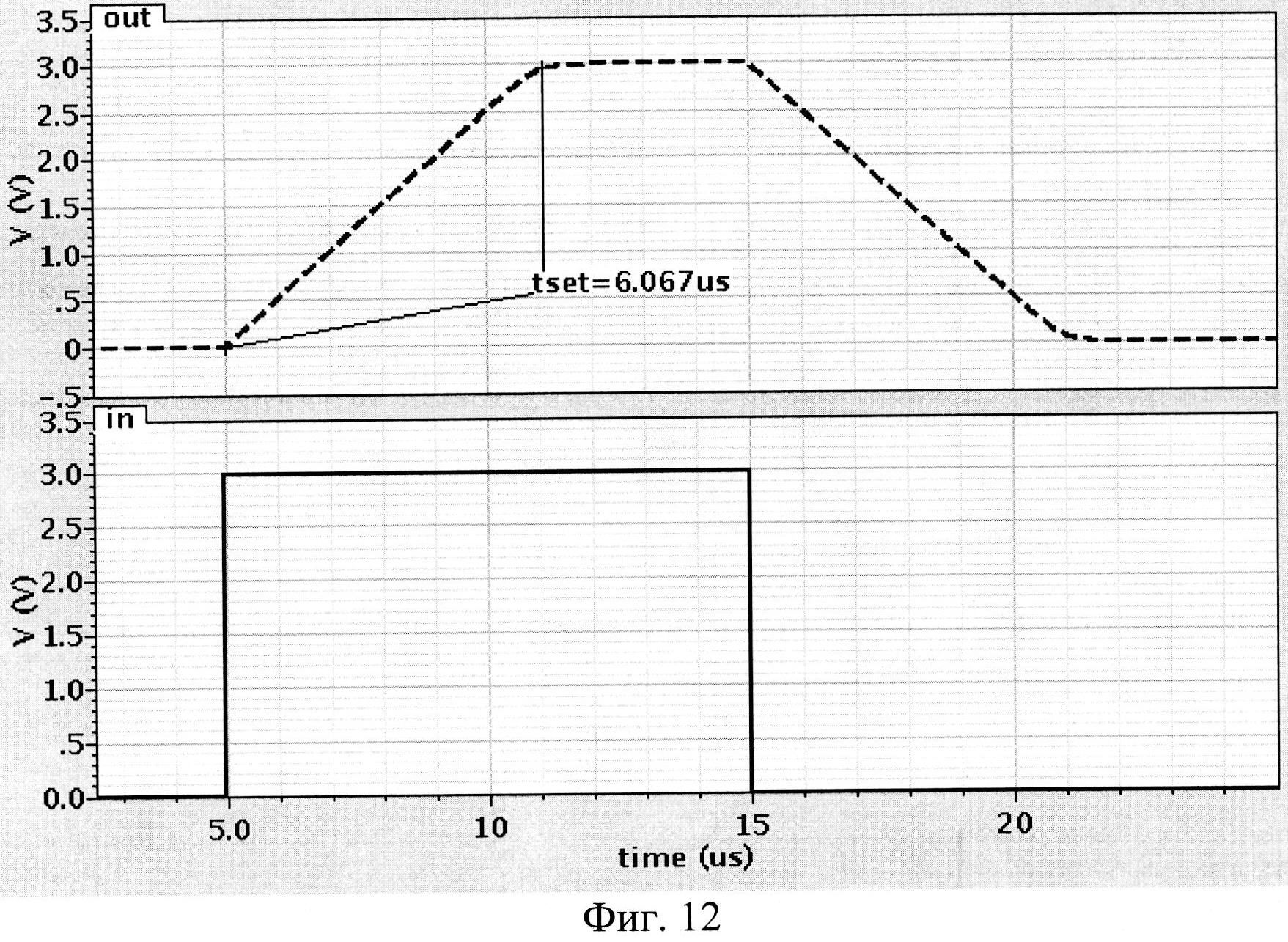

На фиг. 12 приведены графики переходных процессов в ОУ фиг. 10 при бесконечно больших сопротивлениях первого 18 и второго 19 дополнительных резисторов. В данном режиме схема фиг. 10 соответствует применению в ОУ схемы ДК-прототипа фиг. 1. Рассмотрение графиков фиг. 10 показывает, что максимальная скорость нарастания выходного напряжения ОУ на базе известного ДК составляет ϑвых=0,5 В/мкс.

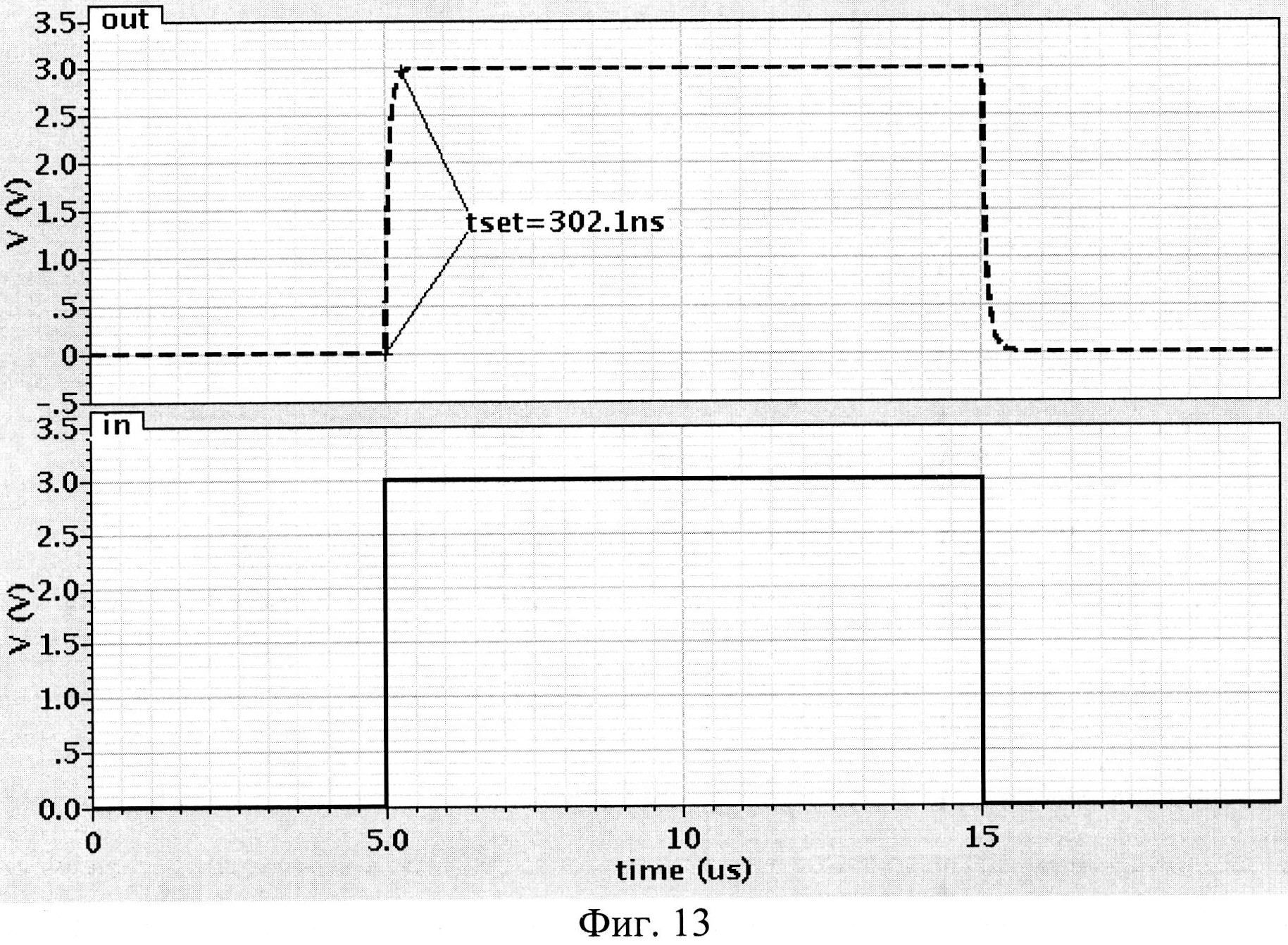

На фиг. 13 приведены графики переходных процессов в ОУ фиг. 10 при сопротивлениях первого 18 и второго 19 дополнительных резисторов, равных 1 кОм. Рассмотрение графиков фиг. 10 показывает, что максимальная скорость нарастания выходного напряжения ОУ на базе заявляемого ДК при работе его транзисторов в микрорежиме (5÷10 мкА) составляет ϑвых=10 В/мкс.

Дифференциальный входной каскад быстродействующего операционного усилителя для КМОП-техпроцессов фиг. 2 содержит первый 1 и второй 2 входы, первый 3 и второй 4 входные полевые транзисторы, истоки которых объединены, а затворы связаны с соответствующими первым 1 и вторым 2 входами, объединенные истоки первого 3 и второго 4 входных полевых транзисторов подключены через цепь смещения потенциалов 5 к объединенным затворам первого 6 и второго 7 выходных транзисторов, объединенные затворы первого 6 и второго 7 выходных транзисторов связаны с первой 8 шиной источника питания через токостабилизирующий двухполюсник 9, третий 10 и четвертый 11 входные полевые транзисторы, объединенные истоки которых соединены со второй 12 шиной источника питания через второй 13 токостабилизирующий двухполюсник, затвор третьего 10 входного полевого транзистора подключен к первому 1 входу устройства, затвор четвертого 11 входного полевого транзистора соединен со вторым 2 входом устройства, сток третьего 10 входного полевого транзистора соединен с истоком первого 6 выходного транзистора, сток четвертого 11 входного полевого транзистора соединен с истоком второго 7 выходного транзистора, причем первый 14 токовый выход устройства, согласованный со второй 12 шиной источника питания, соединен со стоком первого 3 входного полевого транзистора, второй 15 токовый выход устройства, согласованный со второй 12 шиной источника питания, соединен со стоком второго 4 входного полевого транзистора, третий 16 токовый выход устройства, согласованный с первой 8 шиной источника питания, соединен со стоком первого 6 выходного транзистора, а четвертый 17 токовый выход устройства, согласованный с первой 8 шиной источника питания, соединен со стоком второго 7 выходного транзистора. Исток первого 3 входного транзистора соединен со стоком четвертого 11 входного полевого транзистора через первый 18 дополнительный резистор, исток второго 4 входного транзистора соединен со стоком третьего 10 входного полевого транзистора через второй 19 дополнительный резистор и через дополнительную цепь смещения потенциалов 20 связан с затвором второго 7 выходного транзистора, который подключен ко второй 12 шине источника питания через дополнительный токостабилизирующий двухполюсник 21.

Рассмотрим работу заявляемого устройства фиг.2. Статические токи всех транзисторов схемы (при uвх1-2=0, R18=R19=∞) определяются токами I9 и Ι21 токостабилизирующего двухполюсника 9 и дополнительного токостабилизирующего двухполюсника 21.

Если на вход Вх. 1 подается положительное напряжение uвх1-2, то оно с единичным коэффициентом передается в исток первого 3 входного полевого транзистора. При малых токах второго 13 токостабилизирующего двухполюсника (5÷10 мкА) третий 10 входной полевой транзистор «запирается» уже при uвх1-2=100÷150 мВ. Практически весь ток Ι13 перераспределяется далее в исток четвертого 11 входного полевого транзистора. Следует также заметить, что напряжение на истоках второго 4 входного полевого и второго 7 выходного полевого транзисторов (при дальнейшем увеличении uвх) не изменяется.

Рассмотрим далее работу схемы фиг. 2 при R18=R19=0,5÷2 кОм, а также дальнейшем (uвх1-2>150 мВ) увеличении амплитуды входного сигнала. Если в статическом режиме выбрать напряжение смещения Е0 цепи смещения потенциалов 5 и дополнительной цепи смещения потенциалов 20 таким образом, что статические токи через первый 18 и второй 19 дополнительные резисторы будут близки к нулю, то дальнейшее увеличение uвх1-2>100÷50 мВ будет «выделяться» на первом 18 и втором 19 дополнительных резисторах. Как следствие, в этом режиме начинает увеличиваться ток истока (стока) первого 3 входного полевого и второго 7 выходного транзисторов, а также выходной ток ДК (для первого 14 и второго 17 токовых выходов устройства). Графики фиг. 6, фиг. 8, фиг. 9 подтверждают, что предлагаемый ДК обеспечивает достаточно большие выходные токи (значительно превышающие статический ток I13=5÷10 мкА). Заметим, что данный режим характерен для транзисторных каскадов класса «АВ».

Таким образом, ДК фиг. 2 работает как каскад класса «АВ». Его максимальные выходные токи существенно превышают микроамперные статические токи транзисторов (3, 4, 6, 7). Наряду с более высоким значением Uгр это является существенным достоинством ДК, фиг. 2, позволяющим более чем на порядок (в 20 раз) повысить максимальную скорость нарастания выходного напряжения, например, в операционном усилителе или уменьшить время установления переходного процесса в компенсационном стабилизаторе напряжения с использованием ДК, фиг. 2.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент EP 0601560 fig.3.

2. Патент US №7.701.291 fig. 3.

3. Патентная заявка US 2006/0139098.

4. Патентная заявка US 2010/0327974 fig. 4.

5. Патент US №7.408.410.

6. Патентная заявка US 2009/0237163 fig. 2.

7. Патент US №7.595.695.

8. Патент WO 2007049390.

9. Патент US №7.567.124.

10. Патент US №7.741.911.

11. Патент US №4.377.789.

12. Патент US №6.794.940.

13. Патент US №6.538.512.

14. Патент US №6.590.980.

15. Патент US №7.265.621.

16. Патент US №7.259.626.

17. Патент US №7.209.006.

18. Патент US №6.842.073.

19. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н.Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. - С.11, формула (1.5).

20. Прокопенко Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

21. Прокопенко Н.Н. Основные параметры и уравнения базовых схем включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, Н.В. Бутырлагин, И.В. Пахомов // Проблемы разработки перспективных микро- и наноэлектронных систем - 2014. Сборник трудов. Часть 3 / Под общ. ред. академика РАН А.Л. Стемпковского. - М.: ИППМ РАН, 2014. - С. 111-116.

22. Прокопенко Н.Н. Основные свойства, параметры и базовые схемы включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, О.В. Дворников, П.С. Будяков // Электронная техника. Серия 2. Полупроводниковые приборы, выпуск 2 (233) 2014. - С. 53-64.

Дифференциальный входной каскад быстродействующего операционного усилителя для КМОП-техпроцессов, содержащий первый (1) и второй (2) входы, первый (3) и второй (4) входные полевые транзисторы, истоки которых объединены, а затворы связаны с соответствующими первым (1) и вторым (2) входами, объединенные истоки первого (3) и второго (4) входных полевых транзисторов подключены через цепь смещения потенциалов (5) к объединенным затворам первого (6) и второго (7) выходных транзисторов, объединенные затворы первого (6) и второго (7) выходных транзисторов связаны с первой (8) шиной источника питания через токостабилизирующий двухполюсник (9), третий (10) и четвертый (11) входные полевые транзисторы, объединенные истоки которых соединены со второй (12) шиной источника питания через второй (13) токостабилизирующий двухполюсник, затвор третьего (10) входного полевого транзистора подключен к первому (1) входу устройства, затвор четвертого (11) входного полевого транзистора соединен со вторым (2) входом устройства, сток третьего (10) входного полевого транзистора соединен с истоком первого (6) выходного транзистора, сток четвертого (11) входного полевого транзистора соединен с истоком второго (7) выходного транзистора, причем первый (14) токовый выход устройства, согласованный со второй (12) шиной источника питания, соединен со стоком первого (3) входного полевого транзистора, второй (15) токовый выход устройства, согласованный со второй (12) шиной источника питания, соединен со стоком второго (4) входного полевого транзистора, третий (16) токовый выход устройства, согласованный с первой (8) шиной источника питания, соединен со стоком первого (6) выходного транзистора, а четвертый (17) токовый выход устройства, согласованный с первой (8) шиной источника питания, соединен со стоком второго (7) выходного транзистора, отличающийся тем, что исток первого (3) входного транзистора соединен со стоком четвертого (11) входного полевого транзистора через первый (18) дополнительный резистор, исток второго (4) входного транзистора соединен со стоком третьего (10) входного полевого транзистора через второй (19) дополнительный резистор и через дополнительную цепь смещения потенциалов (20) связан с затвором второго (7) выходного транзистора, который подключен ко второй (12) шине источника питания через дополнительный токостабилизирующий двухполюсник (21).