Результат интеллектуальной деятельности: СПОСОБ УПРАВЛЕНИЯ ПАМЯТЬЮ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, БЛОК УПРАВЛЕНИЯ ПАМЯТЬЮ И ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к области вычислительной техники, и в частности к способу управления памятью вычислительной системы, блоку управления памятью и вычислительной системе в области вычислительной техники.

УРОВЕНЬ ТЕХНИКИ

Для достижения определенной эксплуатационной гибкости требуется сервер средней или высокой производительности, при этом важной частью эксплуатационной гибкости является функция «горячей» замены устройства. То есть сервер может осуществлять динамическое подключение или отключение устройства без прерывания работы вычислительной системы для достижения целей наращивания емкости и обнаружения неисправностей, благодаря чему достигается соответствие требованиям надежности, работоспособности или энергосбережения вычислительной системы.

Как правило, устройства с функцией «горячей» замены включают в себя, к примеру, процессор, память или периферийное устройство ввода-вывода (IO), причем память является одной из важнейших частей, входящих в состав устройств с функцией «горячей» замены, поскольку память является одним из важных ресурсов вычислительной системы. «Горячее» подключение памяти относится к запоминающему устройству, которое подключается без прерывания работы вычислительной системы, а «горячее» отключение памяти относится к запоминающему устройству, которое отключается без прерывания работы вычислительной системы. При «горячем» отключении памяти должен выполняться перенос и восстановление занятой памяти в целевой памяти. Однако в вычислительной системе присутствует не переносимая страница, включающая в себя физическую страницу, которая занята ядром, и физическую страницу, которая блокируется пользовательским процессом.

В прикладном процессе, в связи с тем, что физическая страница, которая занята ядром, отмечается вычислительной системой в качестве не переносимой страницы, в процессе обращения ядра к памяти вычислительная система может выделить физическую память из определенной области (области не переносимой памяти) для достижения цели перевода целевой памяти в автономный режим. Когда пользовательский процесс обращается к памяти, память принадлежит общей переносимой памяти, но после того, как пользовательский процесс указывает блокировку памяти, память помечается в качестве не переносимой страницы, что является препятствием при переводе целевой памяти в автономный режим. Возможность перевода памяти, которая блокируется пользовательским процессом, в автономный режим является одним из ключевых факторов в процессе реализации «горячей» замены памяти.

При наличии проблемы, заключающейся в затруднении перевода памяти, которая блокируется пользовательским процессом, в автономный режим, могут неоднократно предприниматься попытки переноса памяти в ожидании того, что память будет разблокирована пользовательским процессом в процессе выполнения повторных попыток. Однако способ переноса посредством выполнения повторных попыток не может гарантировать того, что память будет переведена в автономный режим в связи с тем, что разблокировка памяти, которая блокируется пользовательским процессом, вовсе не будет затронута попытками переноса памяти, при этом между ними не будет существовать необходимая взаимосвязь. Исходя из вышесказанного, в процессе выполнения попыток перевода памяти в автономный режим память, которая блокируется пользовательским процессом, может постоянно находиться в заблокированном состоянии.

Исходя из вышесказанного, существует потребность в надлежащем решении для управления памятью вычислительной системы для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Варианты осуществления настоящего изобретения обеспечивают способ управления памятью вычислительной системы, блок управления памятью и вычислительную систему для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти.

В одном аспекте вариант осуществления настоящего изобретения обеспечивает способ управления памятью вычислительной системы, включающий в себя этапы: приема запроса на выделение, отправляемого пользовательским процессом, причем запрос на выделение используется для запроса выделения памяти вычислительной системы для пользовательского процесса; выделения памяти для пользовательского процесса в соответствии с запросом на выделение и установки маркера автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти; приема запроса на блокировку, отправляемого пользовательским процессом, причем запрос на блокировку используется для запроса блокировки памяти; блокировки памяти в соответствии с запросом на блокировку и маркером автономного режима памяти; и перевода памяти в автономный режим в соответствии с маркером автономного режима памяти.

В другом аспекте вариант осуществления настоящего изобретения обеспечивает блок управления памятью, включающий в себя: первый приемный модуль, выполненный с возможностью приема запроса на выделение, отправляемого пользовательским процессом, причем запрос на выделение используется для запроса выделения памяти вычислительной системы для пользовательского процесса; модуль выделения, выполненный с возможностью выделения памяти для пользовательского процесса в соответствии с запросом на выделение, который принимается первым приемным модулем, и установки маркера автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти; второй приемный модуль, выполненный с возможностью приема запроса на блокировку, отправляемого пользовательским процессом, причем запрос на блокировку используется для запроса блокировки памяти вычислительной системы; модуль блокировки, выполненный с возможностью блокировки памяти в соответствии с запросом на блокировку, принимаемым вторым приемным модулем, и маркером автономного режима памяти; и модуль перевода в автономный режим, выполненный с возможностью перевода памяти, которая блокируется модулем блокировки, в автономный режим в соответствии с маркером автономного режима памяти.

Еще в одном аспекте вариант осуществления настоящего изобретения обеспечивает вычислительную систему, включающую в себя по меньшей мере одно запоминающее устройство и блок управления памятью в соответствии с вариантом осуществления настоящего изобретения, который выполнен с возможностью управления по меньшей мере одним запоминающим устройством. Блок управления памятью включает в себя: первый приемный модуль, выполненный с возможностью приема запроса на выделение, отправляемого пользовательским процессом, причем запрос на выделение используется для запроса выделения памяти вычислительной системы для пользовательского процесса; модуль выделения, выполненный с возможностью выделения памяти для пользовательского процесса в соответствии с запросом на выделение, принимаемым первым приемным модулем, и установки маркера автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти; второй приемный модуль, выполненный с возможностью приема запроса на блокировку, отправляемого пользовательским процессом, причем запрос на блокировку используется для запроса блокировки памяти вычислительной системы; модуль блокировки, выполненный с возможностью блокировки памяти в соответствии с запросом на блокировку, принимаемым вторым приемным модулем, и маркером автономного режима памяти; и модуль перевода в автономный режим, выполненный с возможностью перевода памяти, блокированной модулем блокировки, в автономный режим в соответствии с маркером автономного режима памяти.

На основании вышеупомянутых технических решений, в способе управления памятью вычислительной системы, блоке управления памятью и вычислительной системе в соответствии с вариантами осуществления настоящего изобретения, после приема запроса на выделение, который отправляется пользовательским процессом, и используется для запроса выделения памяти вычислительной системы, ядро, операционная система или блок управления памятью вычислительной системы выделяет память для пользовательского процесса, и устанавливает маркер автономного режима для памяти, для указания автономного режима памяти, и после приема запроса, который направляется пользовательским процессом и используется для запроса блокировки памяти, ядро или операционная система могут блокировать память в соответствии с запросом блокировки пользовательского процесса и маркером автономного режима памяти, и могут переводить память в автономный режим в соответствии маркером автономного режима памяти, когда требуется перевести блокированную память в автономный режим так, что память, блокированная пользовательским процессом, переводится в автономный режим, благодаря чему реализуется «горячая» замена памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более ясной иллюстрации технических решений в соответствии с вариантами осуществления настоящего изобретения далее будут приведены сопровождающие чертежи для описания вариантов осуществления. Сопровождающие чертежи в нижеследующем описании иллюстрируют некоторые варианты осуществлениянастоящего изобретения, при этом специалисты в данной области техники могут без труда вывести из сопровождающих чертежей другие чертежи.

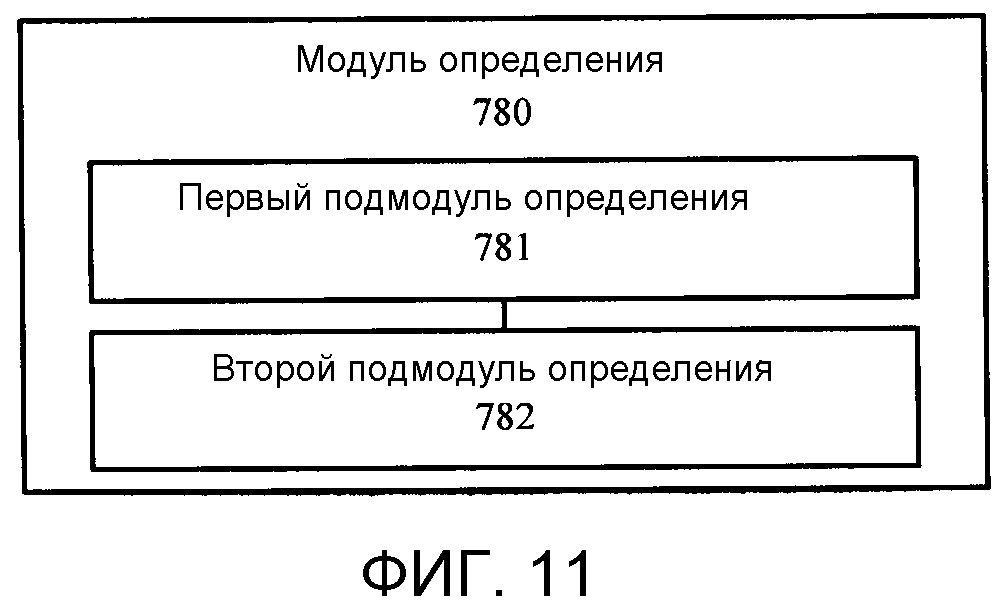

Фиг. 1А схематически изображает блок-схему последовательности операций способа управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения;

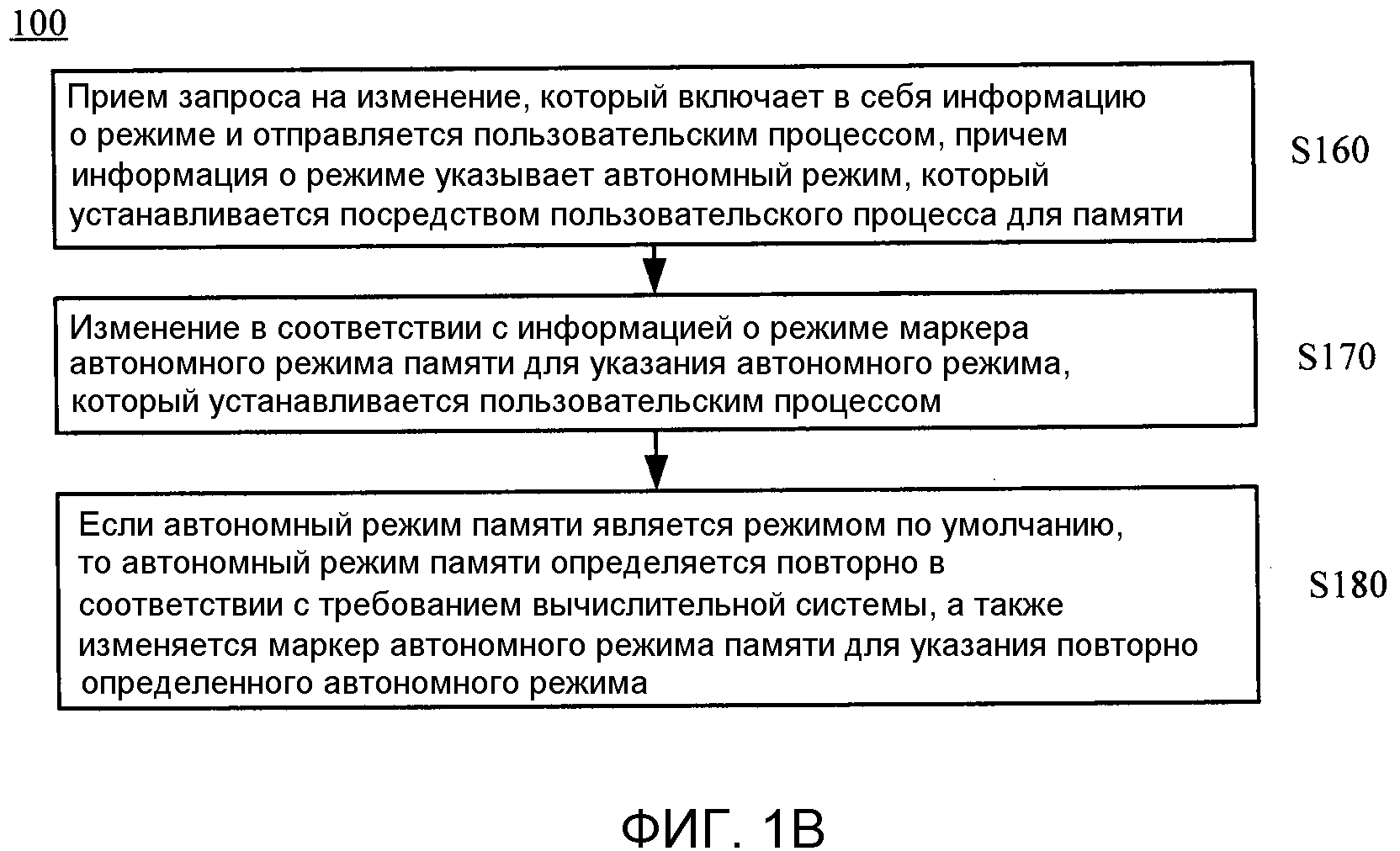

Фиг. 1В схематически изображает блок-схему последовательности операций способа управления памятьювычислительной системы в соответствии с другим вариантом осуществления настоящего изобретения;

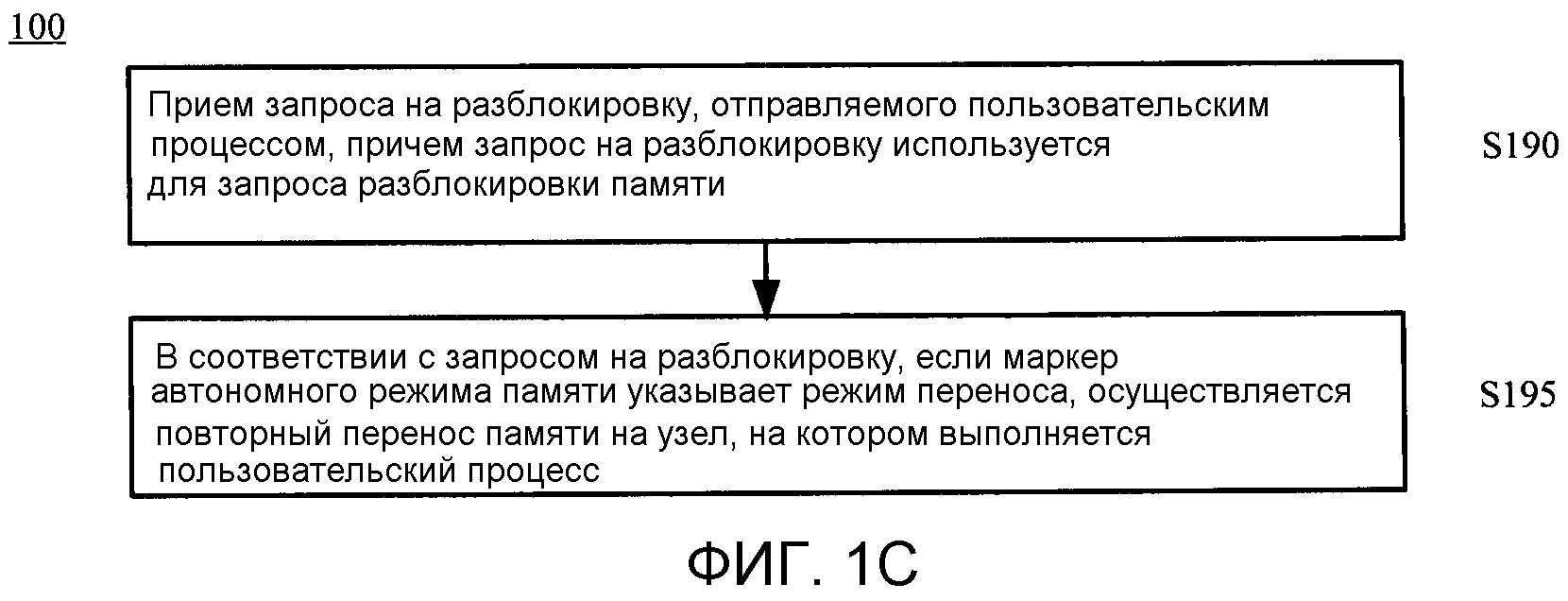

Фиг.1C схематически изображает блок-схему последовательности операций способа управления памятью вычислительной системы в соответствии с еще одним вариантом осуществления настоящего изобретения;

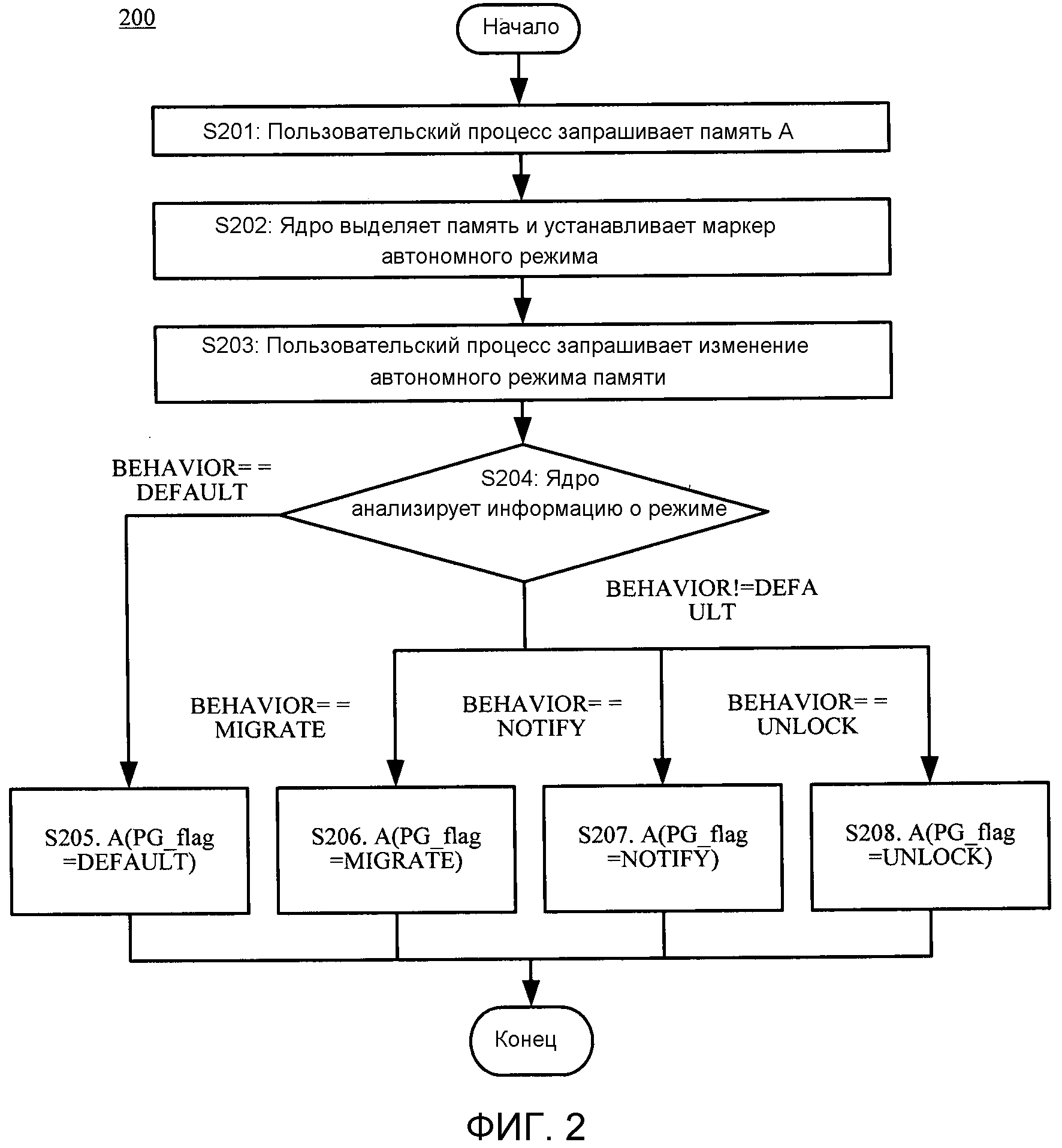

Фиг.2 схематически изображает блок-схему последовательности операций способа изменения автономного режима памяти в соответствии с вариантом осуществления настоящего изобретения;

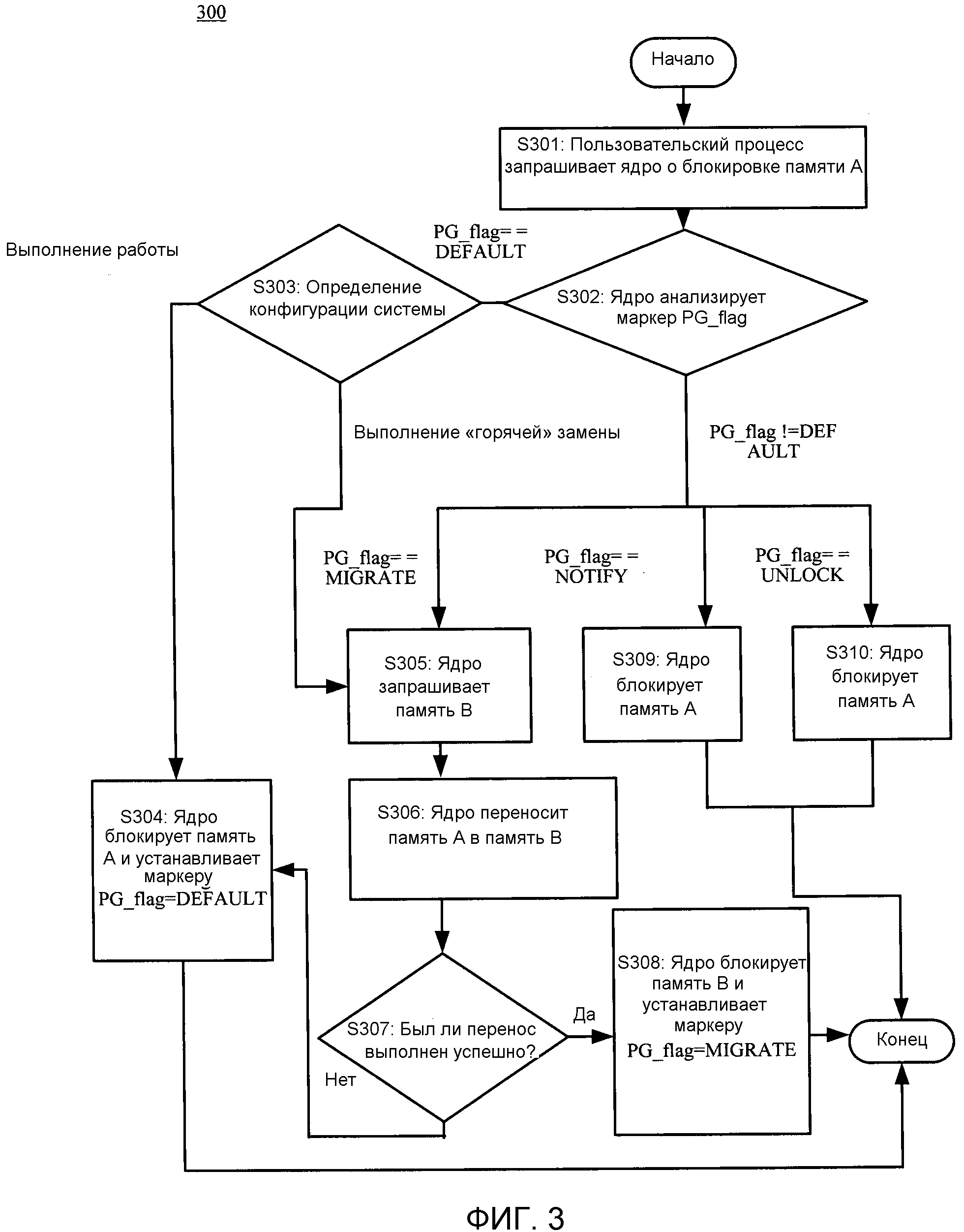

Фиг.3 схематически изображает блок-схему последовательности операций способа блокировки памяти в соответствии с вариантом осуществления настоящего изобретения;

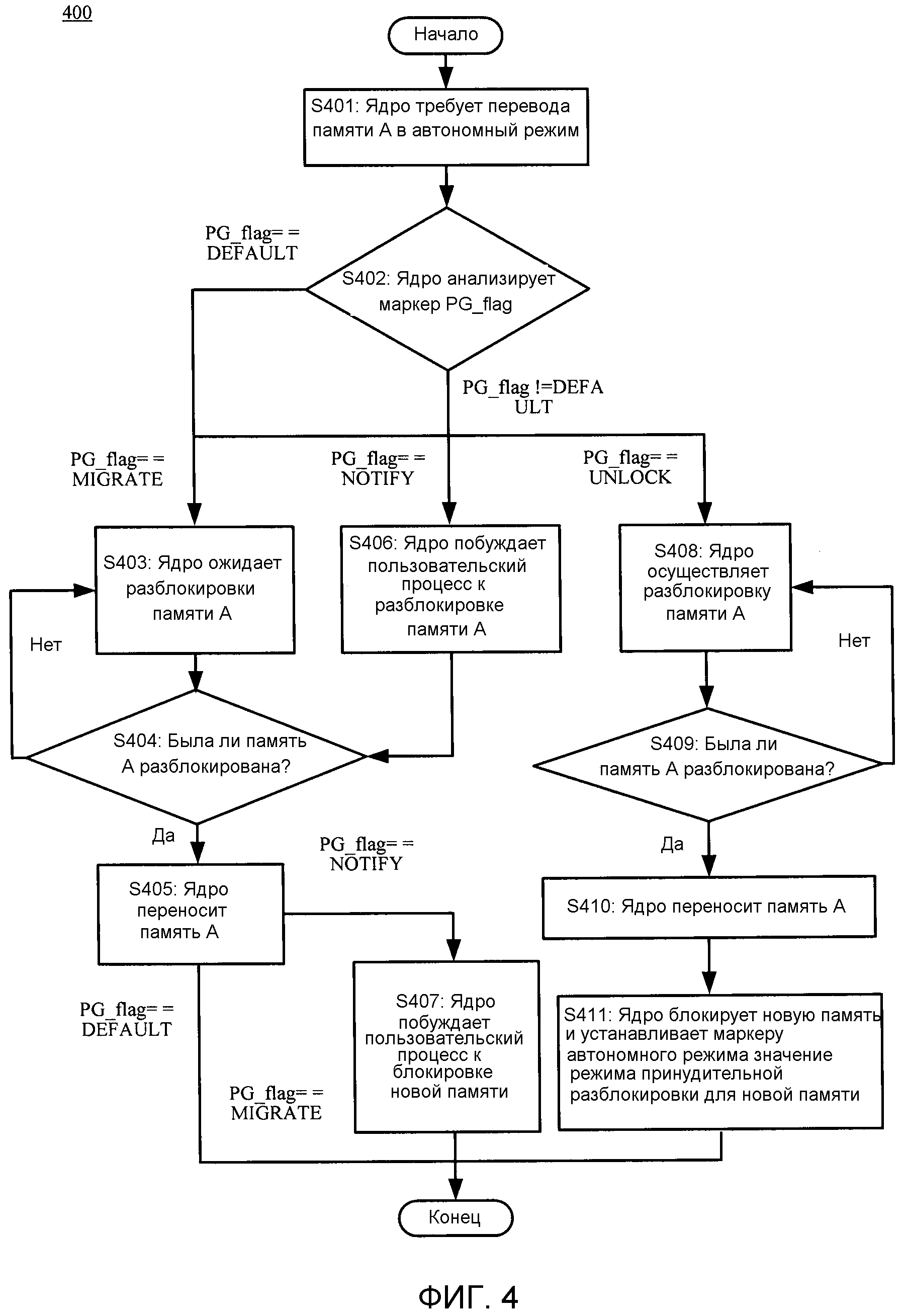

Фиг.4 схематически изображает блок-схему последовательности операций способа перевода заблокированной памяти в автономный режим в соответствии с вариантом осуществления настоящего изобретения;

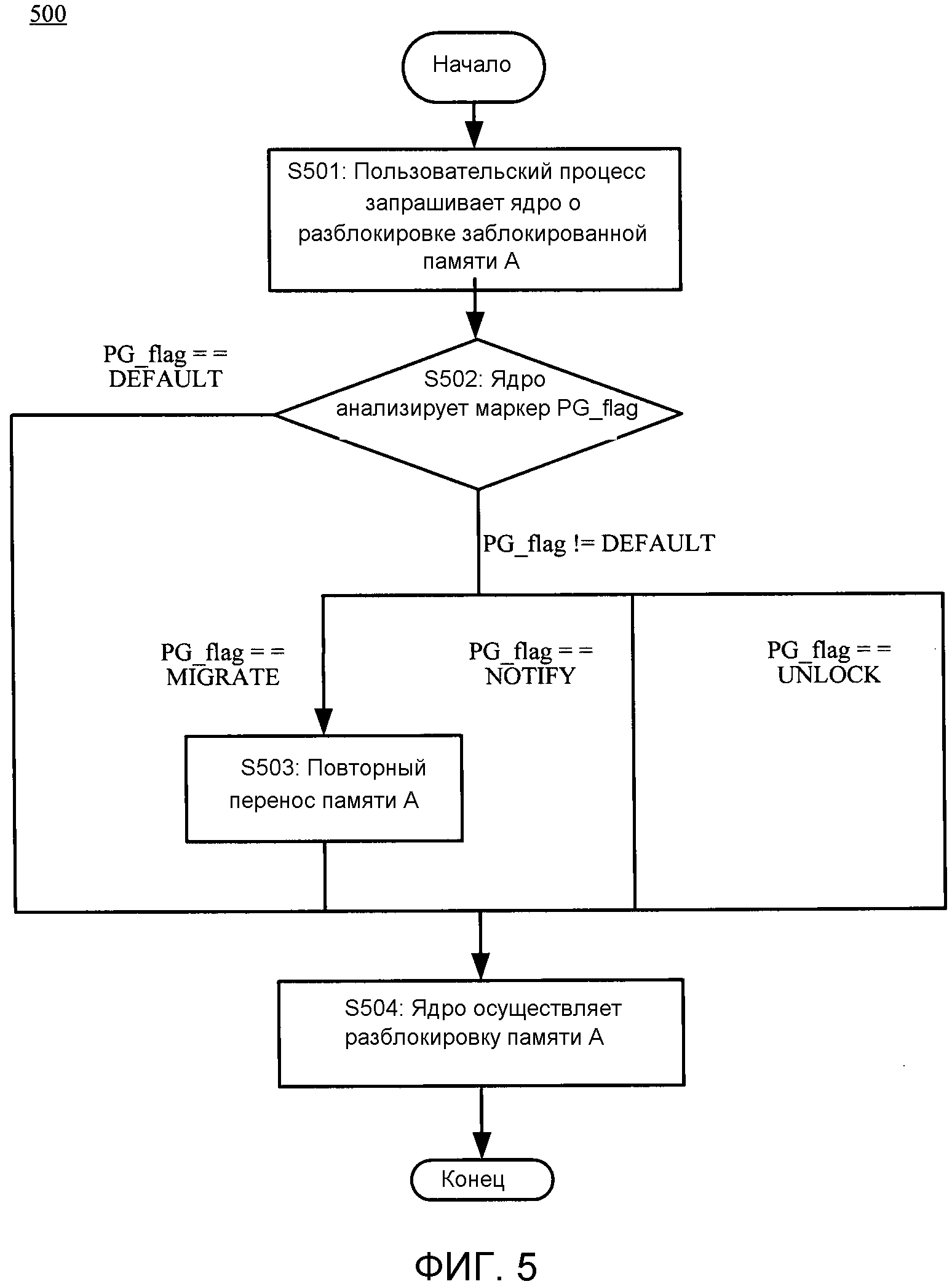

Фиг.5 схематически изображает блок-схему последовательности операций способа разблокировки памяти в соответствии с вариантом осуществления настоящего изобретения;

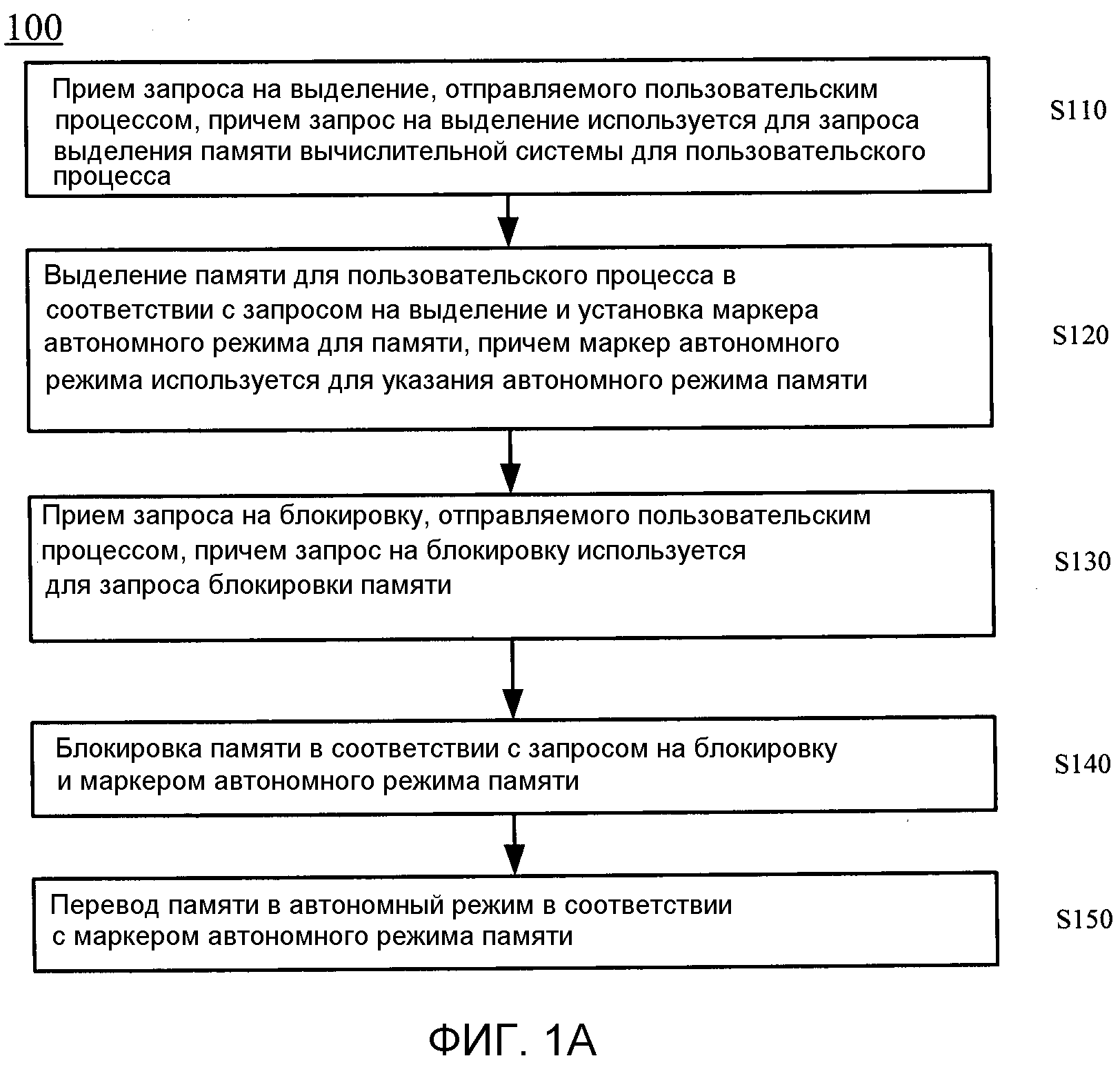

Фиг.6 схематически изображает блок-схему блока управления памятью в соответствии с вариантом осуществления настоящего изобретения;

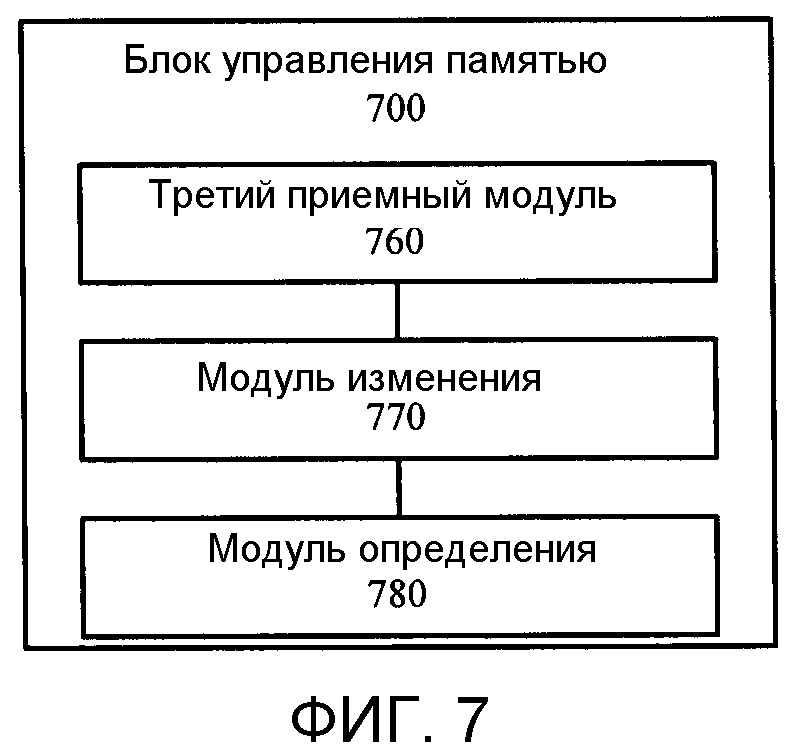

Фиг.7 схематически изображает блок-схему блока управления памятью в соответствии с другим вариантом осуществления настоящего изобретения;

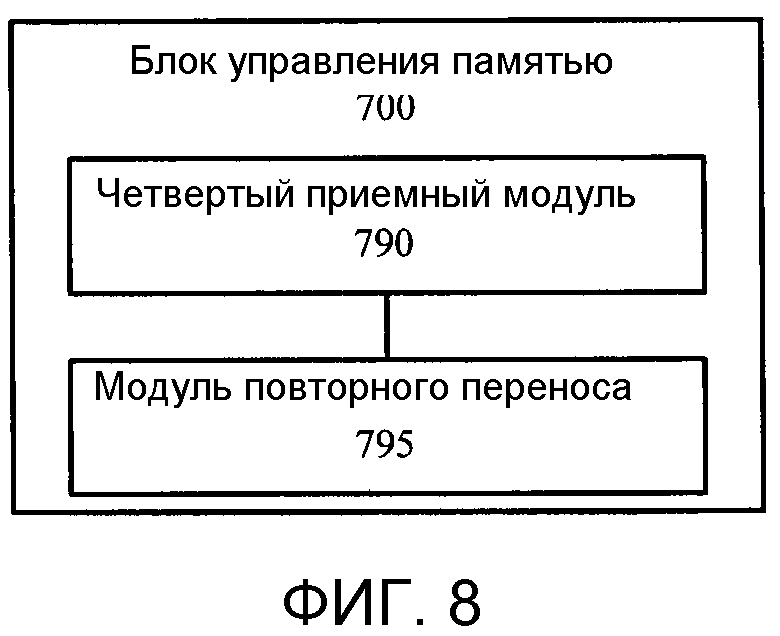

Фиг.8 схематически изображает блок-схему блока управления памятью в соответствии с еще одним вариантом осуществления настоящего изобретения;

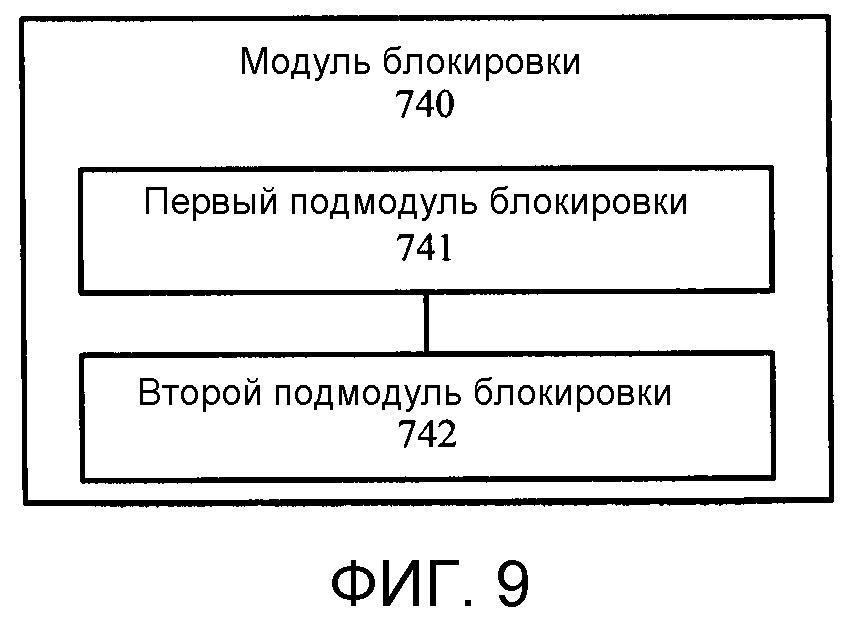

Фиг.9 схематически изображает блок-схему модуля блокировки в соответствии с вариантом осуществления настоящего изобретения;

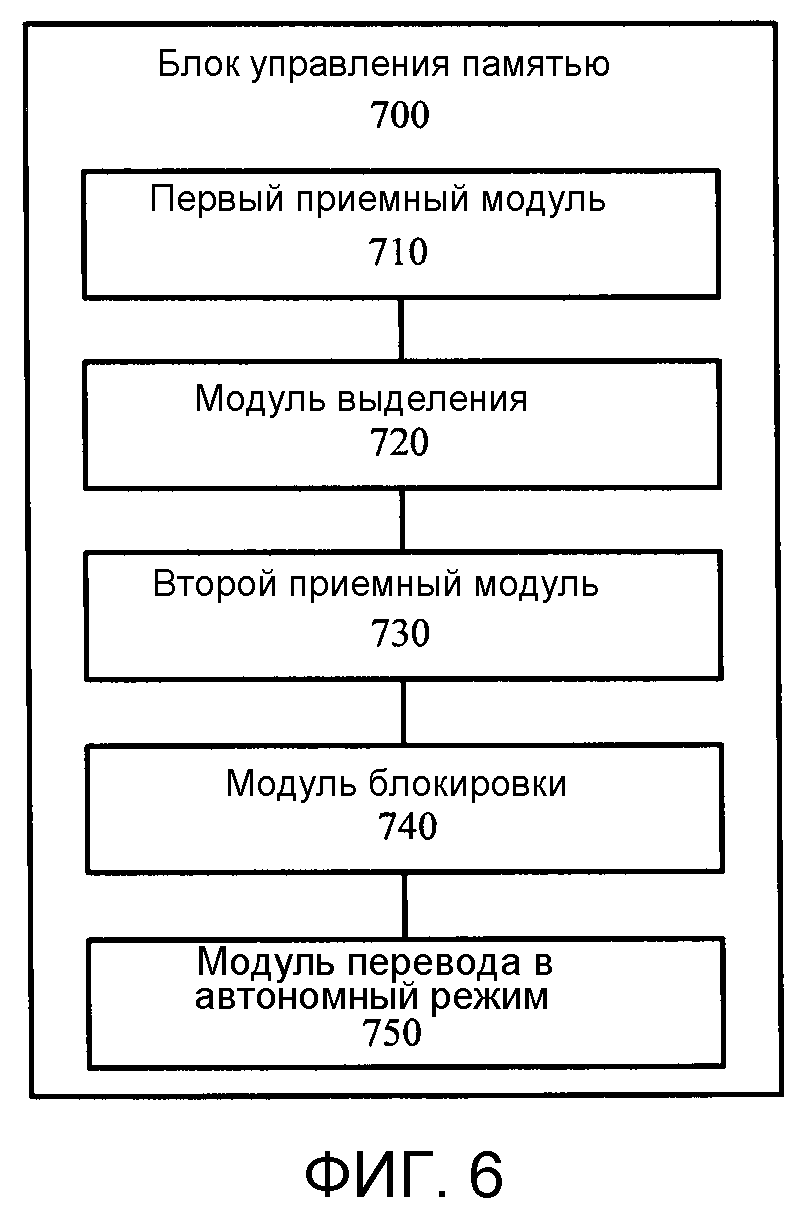

Фиг.10 схематически изображает блок-схему модуля перевода в автономный режим в соответствии с вариантом осуществления настоящего изобретения;

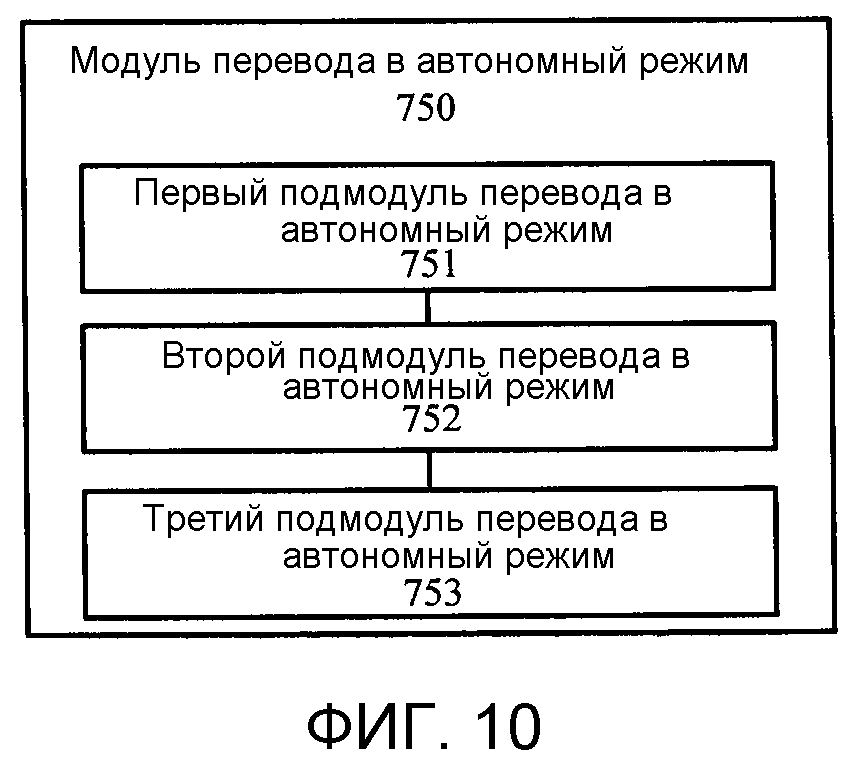

Фиг.11 схематически изображает блок-схему модуля определения в соответствии с вариантом осуществления настоящего изобретения; и

Фиг.12 схематически изображает блок-схему вычислительной системы в соответствии с вариантом осуществления настоящего изобретения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Далее со ссылкой на сопровождающие чертежи в вариантах осуществления настоящего изобретения будут ясно описаны технические решения в соответствии с вариантами осуществления настоящего изобретения. Очевидно, что описываемые варианты осуществления являются лишь некоторыми вариантами осуществления настоящего изобретения среди множества возможных. Все остальные варианты осуществления, выводимые специалистами в данной области техники на основе вариантов осуществления настоящего изобретения, безусловно должны находиться в рамках объема защиты настоящего изобретения.

Следует отметить, что технические решения в соответствии с вариантами осуществления настоящего изобретения могут быть использованы применительно к различным вычислительным системам, включающим в себя персональный компьютер (PC), большую вычислительную систему или различные сверхмощные компьютеры. В вариантах осуществления настоящего изобретения в качестве примера для описания берется вычислительная система, включающая в себя по меньшей мере одно запоминающее устройство, при этом варианты осуществления настоящего изобретения не ограничиваются этим.

Фиг.1A схематически изображает блок-схему последовательности операций способа 100 управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения. Как изображено на Фиг.1А, способ 100 включает в себя следующие этапы:

S110: Прием запроса на выделение, который отправляется пользовательским процессом, причем запрос на выделение используется для запроса выделения памяти вычислительной системы для пользовательского процесса.

S120: Выделение памяти для пользовательского процесса в соответствии с запросом на выделение и установка маркера автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти.

S130: Прием запроса на блокировку, который отправляется пользовательским процессом, причем запрос на блокировку используется для запроса блокировки памяти.

S140: Блокировка памяти в соответствии с запросом на блокировку и маркером автономного режима памяти.

S150: Перевод памяти в автономный режим в соответствии с маркером автономного режима памяти.

После приема запроса на выделение, который отправляется пользовательским процессом и используется для запроса выделения памяти вычислительной системы, ядро, операционная система или блок управления памятью вычислительной системы выделяет память для пользовательского процесса и устанавливает маркер автономного режима для памяти для указания автономного режима памяти; а после приема запроса (на блокировку), который отправляется пользовательским процессом и используется для запроса блокировки памяти, ядро или операционная система может заблокировать память в соответствии с запросом на блокировку пользовательского процесса и маркером автономного режима памяти, а также может перевести память в автономный режим в соответствии с маркером автономного режима памяти, когда требуется перевести заблокированную память в автономный режим.

Исходя из вышесказанного, в способе управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, а также устраняются потери системных ресурсов.

В варианте осуществления настоящего изобретения автономный режим или автономная политика может включать в себя по меньшей мере один из следующих режимов: режим по умолчанию, режим переноса, режим уведомления и режим принудительной разблокировки. При необходимости автономный режим включает в себя режим по умолчанию, режим переноса, режим уведомления и режим принудительной разблокировки.

В режиме по умолчанию пользовательский процесс может указывать на то, что память переводится в автономный режим посредством режима по умолчанию, и если пользовательский процесс не указывает автономную политику, то такой режим также может быть использован. В режиме переноса, перед блокировкой памяти, она должна быть перенесена в не переносимую область, а затем заблокирована. В режиме уведомления, перед тем как ядро затребует перевод памяти в автономный режим, оно побуждает пользовательский процесс к разблокировке памяти. В режиме принудительной разблокировки ядро может принудительно разблокировать память, когда ядро затребует перевод памяти в автономный режим, а затем переводит память в автономный режим. Следует отметить, что названия и краткое описание четырех автономных режимов, представленных в варианте осуществления настоящего изобретения, приведены попросту для упрощения понимания варианта осуществления настоящего изобретения, при этом вариант осуществления настоящего изобретения не ограничивается ими. Кроме того, конкретный смысл этих четырех автономных режимов должен быть воспринят с учетом конкретных операций, которые описаны в варианте осуществления настоящего изобретения.

В варианте осуществления настоящего изобретения пользовательский процесс может изменить автономный режим задействованной памяти в соответствии с требованием, то есть пользовательский процесс может установить автономный режим памяти. Исходя из вышесказанного, как изображено на Фиг.1B, способ 100 управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения, может дополнительно включать в себя следующие этапы:

S160: Прием запроса на изменение, который включает в себя информацию о режиме и отправляется пользовательским процессом, причем информация о режиме указывает автономный режим, который устанавливается пользовательским процессом для памяти.

S170: Изменение в соответствии с информацией о режиме маркера автономного режима памяти для указания автономного режима, установленного пользовательским процессом.

То есть после обращения пользовательского процесса к памяти, пользовательский процесс может установить автономный режим для задействованной памяти в соответствии с требованием и отправляет запрос на изменение, включающий в себя информацию о режиме, в ядро для того, чтобы ядро в соответствии с информацией о режиме изменило маркер автономного режима памяти для указания автономного режима, установленного пользовательским процессом.

В варианте осуществления настоящего изобретения, после того, как ядро приняло запрос на блокировку, который отправляется пользовательским процессом, ядро может определить автономный режим памяти в соответствии с маркером автономного режима памяти, и если автономный режим памяти является режимом по умолчанию, то ядро может повторно установить желаемый автономный режим памяти. То есть, как изображено на Фиг.1B, способ 100 в соответствии с вариантом осуществления настоящего изобретения может дополнительно включать в себя следующие этапы:

S180: Если автономный режим памяти является режимом по умолчанию, то автономный режим памяти определяется повторно в соответствии с требованием вычислительной системы, а также изменяется маркер автономного режима памяти для указания повторно определенного автономного режима.

При необходимости, если вычислительная система требует выполнения работы системы, то ядро определяет автономный режим памяти в качестве режима по умолчанию; а если вычислительная система требует выполнения «горячей» замены, то ядро определяет автономный режим памяти в качестве режима переноса.

Следует отметить, что способ в соответствии с вариантом осуществления настоящего изобретения может быть выполнен ядром, операционной системой или блоком управления памятью. Для упрощения дальнейшего описания ядро будет использовано в качестве исполнительного объекта, при этом вариант осуществления настоящего изобретения не ограничивается этим.

В частности, на этапе S110, пользовательский процесс в соответствии с требованием пользовательского процесса, может отправить запрос на выделение ядру для запроса выделения памяти.

На этапе S120 ядро в соответствии с запросом на выделение, выделяет память для пользовательского процесса, а также устанавливает маркер автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти. При необходимости ядро устанавливает маркер автономного режима, который указывает режим по умолчанию, для выделенной памяти. К примеру, ядро может добавить маркер PG_flag автономного режима для памяти, а также присвоить маркеру автономного режима значение «DEFAULT» («ПО УМОЛЧАНИЮ»), то есть PG_flag = DEFAULT. Разумеется, ядро также может установить и другие автономные режимы для памяти, при этом вариант осуществления настоящего изобретения не ограничивается вышеупомянутым.

При необходимости пользовательский процесс может установить или составить автономный режим или автономную политику для задействованной памяти при помощи интерфейса, который обеспечивается ядром. В частности, на этапе S160 пользовательский процесс в соответствии с требованием пользовательского процесса, может отправить запрос на изменение ядру для изменения автономного режима памяти, причем запрос на изменение включает в себя информацию о режиме для указания автономного режима, который устанавливается пользовательским процессом для памяти. К примеру, запрос на изменение может включать в себя параметр «BEHAVIOR» («РЕЖИМ»), причем параметру «BEHAVIOR» («РЕЖИМ») можно присвоить значение, такое как «DEFAULT» («ПО УМОЛЧАНИЮ»), «MIGRATE» («ПЕРЕНОС»), «NOTIFY» («УВЕДОМЛЕНИЕ») и «UNLOCK» («РАЗБЛОКИРОВКА»), которые соответствующим образом указывают на то, что пользовательский процесс устанавливает автономный режим памяти в качестве режима по умолчанию, режима переноса, режима уведомления и режима принудительной разблокировки.

На этапе S170 ядро в соответствии с информацией о режиме, изменяет автономный режим памяти. В частности, ядро в соответствии с параметром «BEHAVIOR» («РЕЖИМ»), который обеспечивается в запросе на изменение, может изменить маркер автономного режима памяти для указания автономного режима, который устанавливается пользовательским процессом.

В частности, к примеру, для памяти А, автономный режим которой должен быть изменен, ядро может проанализировать параметр «BEHAVIOR» («РЕЖИМ»), который включается в запрос на изменение. Если параметр «BEHAVIOR» («РЕЖИМ») имеет значение «DEFAULT» («ПО УМОЛЧАНИЮ»), то ядро может определить, что пользовательский процесс устанавливает автономный режим памяти А в качестве режима по умолчанию. При этом ядро может изменить маркер PG_flag автономного режима памяти A, то есть присвоить маркеру автономного режима значение «DEFAULT» («ПО УМОЛЧАНИЮ»), то есть PG_flag = «DEFAULT» («ПО УМОЛЧАНИЮ»). Если параметр «BEHAVIOR» («РЕЖИМ») имеет значение «MIGRATE» («ПЕРЕНОС»), то ядро может определить, что пользовательский процесс устанавливает автономный режим памяти А в качестве режима переноса, при этом ядро может присвоить маркеру автономного режима памяти A значение «MIGRATE» («ПЕРЕНОС»), то есть PGflag = «MIGRATE» («ПЕРЕНОС»). Аналогичным образом, если параметр «BEHAVIOR» («РЕЖИМ») имеет значение «NOTIFY» («УВЕДОМЛЕНИЕ»), то ядро может определить, что пользовательский процесс устанавливает автономный режим памяти А в качестве режима уведомления, при этом ядро может присвоить маркеру автономного режима памяти A значение «NOTIFY» («УВЕДОМЛЕНИЕ»), то есть PG_flag = «NOTIFY» («УВЕДОМЛЕНИЕ»). Если параметр «BEHAVIOR» («РЕЖИМ») имеет значение «UNLOCK» («РАЗБЛОКИРОВКА»), то ядро может определить, что пользовательский процесс устанавливает автономный режим памяти А в качестве режима принудительной разблокировки, при этом ядро могут присвоить маркеру автономного режима памяти A значение «UNLOCK» («РАЗБЛОКИРОВКА»), то есть PG_flag = «UNLOCK» («РАЗБЛОКИРОВКА»).

На этапе S130 в соответствии с требованием пользовательского процесса, пользовательский процесс может запросить ядро о блокировке памяти вычислительной системы.

На этапе S140, после того, как ядро приняло запрос на блокировку, который отправляется пользовательским процессом, ядро должно определить автономный режим памяти, в отношении которой запрашивается блокировка, и блокирует память в соответствии с конкретным автономным режимом и запросом на блокировку.

В частности, ядро может определить автономный режим памяти посредством анализа маркера автономного режима памяти. К примеру, если ядро определяет, что маркер автономного режима памяти является PG_flag = «DEFAULT» («ПО УМОЛЧАНИЮ»), то автономный режим памяти является режимом по умолчанию. Аналогичным образом, если ядро определяет, что маркер автономного режима памяти является PG_flag = «MIGRATE» («ПЕРЕНОС»), «NOTIFY» («УВЕДОМЛЕНИЕ») или «UNLOCK» («РАЗБЛОКИРОВКА»), то ядро может определить, что автономный режим памяти является режимом переноса, режимом уведомления или режимом принудительной разблокировки.

При необходимости, если маркер автономного режима памяти указывает режим по умолчанию, режим уведомления или режим принудительной разблокировки, то память блокируется. Если маркер автономного режима памяти указывает режим переноса, то память переносится, при этом если память переносится успешно, то перенесенная память блокируется и для перенесенной памяти устанавливается маркер автономного режима, указывающий режим переноса. Если память переносится неудачно, то память блокируется, а маркер автономного режима памяти изменяется для указания режима по умолчанию.

При необходимости, если ядро определяет, что автономный режим памяти является режимом по умолчанию, то ядро может повторно определить более подходящий автономный режим для памяти. То есть на этапе S180 ядро повторно определяет автономный режим памяти в соответствии с требованием вычислительной системы, и изменяет маркер автономного режима памяти для указания повторно определенного автономного режима.

На этапе S150, если ядро должно перевести память, которая блокируется пользовательским процессом, в автономный режим, то ядро может определить автономный режим памяти посредством анализа маркера автономного режима памяти, и переводит память в автономный режим в соответствии с автономным режимом.

При необходимости, если маркер автономного режима памяти указывает режим по умолчанию или режим переноса, то память ожидает разблокировки и переносится после разблокировки памяти. Если маркер автономного режима памяти указывает режим уведомления, то инициируется пользовательский процесс для разблокировки памяти, память переносится после разблокировки памяти, а пользовательский процесс инициируется для блокировки перенесенной памяти после переноса памяти. Если маркер автономного режима памяти указывает режим принудительной разблокировки, то осуществляется разблокировка памяти и память переноса после разблокировки памяти, перенесенная память блокируется, и для перенесенной памяти устанавливается маркер автономного режима, указывающий режим принудительной разблокировки.

Исходя из вышесказанного, в способе управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения, посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, а также устраняются потери системных ресурсов.

В варианте осуществления настоящего изобретения, при необходимости, если пользовательский процесс запрашивает разблокировку заблокированной памяти, как изображено на Фиг.1С, то способ 100 в соответствии с вариантом осуществления настоящего изобретения дополнительно включает в себя следующие этапы:

S190: Прием запроса на разблокировку, который отправляется пользовательским процессом, причем запрос на разблокировку используется для запроса разблокировки памяти.

S195: В соответствии с запросом на разблокировку, если маркер автономного режима памяти указывает режим переноса, то осуществляется повторный перенос памяти на узел, на котором выполняется пользовательский процесс.

То есть в процессе, в котором пользовательский процесс активно запрашивает разблокировку заблокированной памяти, если маркер автономного режима памяти указывает на то, что автономный режим памяти является режимом переноса, то перед разблокировкой заблокированной памяти ядро может запросить локальную память для повторного переноса заблокированной памяти на узел, на котором выполняется пользовательский процесс. В случае, когда заблокированная память имеет автономный режим, являющийся режимом по умолчанию, режимом уведомления или режимом принудительной разблокировки, ядро может напрямую разблокировать заблокированную память в соответствии с приложением пользовательского процесса. К примеру, в данном случае, когда заблокированная память имеет маркер автономного режима «MIGRATE» («ПЕРЕНОС»), перед разблокировкой память повторно переносится на узел, на котором выполняется пользовательский процесс, что может дополнительно повысить рабочие характеристики системы.

Следует отметить, что последовательные номера вышеупомянутых этапов не подразумевают последовательность выполнения, при этом последовательность выполнения этапов должна быть определена в соответствии с функциями и внутренней логикой, при этом она в любом случае не предназначается для ограничения процесса реализации варианта осуществления настоящего изобретения.

Исходя из вышесказанного, в способе управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения, посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, улучшаются рабочие характеристики системы, а также устраняются потери системных ресурсов.

Далее со ссылкой на конкретные варианты осуществления, изображенные на Фиг.2-5, будет подробно описан способ изменения автономного режима памяти, способ блокировки памяти, способ перевода заблокированной памяти в автономный режим и способ разблокировки памяти в соответствии с вариантами осуществления настоящего изобретения.

Как изображено на Фиг.2, способ 200 установки автономного режима памяти в соответствии с вариантом осуществления настоящего изобретения включает в себя следующие этапы:

S201: Пользовательский процесс запрашивает память А в соответствии с требованием пользовательского процесса.

S202: Ядро выделяет память для пользовательского процесса в соответствии с запросом на выделение, который отправляется пользовательским процессом, и устанавливает маркер автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти. При необходимости ядро задает маркер PG_flag автономного режима памяти значение режима по умолчанию «DEFAULT» («ПО УМОЛЧАНИЮ»), то есть PG_flag = DEFAULT («ПО УМОЛЧАНИЮ»).

При необходимости после того, как пользовательский процесс запросил и получил память A, пользовательский процесс может установить автономный режим памяти А при помощи интерфейса, обеспеченного ядром, причем автономный режим включает в себя режим по умолчанию, режим переноса, режим уведомления и режим принудительной разблокировки.

S203: Пользовательский процесс отправляет запрос на изменение к ядру для запроса изменения автономного режима памяти, причем запрос на изменение включает в себя информацию о режиме для указания автономного режима, который устанавливается пользовательским процессом для памяти, при этом информации о режиме является, к примеру, параметром «BEHAVIOR» («РЕЖИМ»).

S204: Ядро определяет автономный режим, который устанавливается пользовательским процессом для памяти А посредством анализа информации о режиме, такой как параметр «BEHAVIOR» («РЕЖИМ»), которая передается пользовательским процессом.

Если автономный режим, который устанавливается пользовательским процессом для памяти A, является режимом по умолчанию, то процесс переходит на этап S205; а если автономный режим, который устанавливается пользовательским процессом для памяти A, не является режимом по умолчанию, то процесс переходит на этап S206, S207 или S208. В частности, если автономный режим, который устанавливается пользовательским процессом для памяти A, является режимом переноса, то процесс переходит на этап S206; если автономный режим, который устанавливается пользовательским процессом для памяти A, является режимом уведомления, то процесс переходит на этап S207; а если автономный режим, который устанавливается пользовательским процессом для памяти A, является режимом принудительной разблокировки, то процесс переходит на этап S208.

S205: Ядро присваивает маркеру автономного режима памяти значение «DEFAULT» («ПО УМОЛЧАНИЮ»), то есть PGflag = «DEFAULT» («ПО УМОЛЧАНИЮ»). При этом автономный режим памяти А, который устанавливается пользовательским процессом, является режимом по умолчанию, и процесс установки автономного режима памяти A завершается.

S206: Ядро присваивает маркеру автономного режима памяти A значение «MIGRATE» («ПЕРЕНОС»), то есть PG_flag = «MIGRATE» («ПЕРЕНОС»). При этом автономный режим памяти А, устанавливаемый пользовательским процессом, является режимом переноса, и процесс установки автономного режима для памяти A завершается.

S207: Ядро присваивает маркеру автономного режима памяти A значение «NOTIFY» («УВЕДОМЛЕНИЕ»), то есть PG_flag = «NOTIFY» («УВЕДОМЛЕНИЕ»). При этом автономный режим памяти А, устанавливаемый пользовательским процессом, является режимом уведомления, и процесс установки автономного режима для памяти A завершается.

S208: Ядро присваивает маркеру автономного режима памяти A значение «UNLOCK» («РАЗБЛОКИРОВКА»), то есть PG_flag = «UNLOCK» («РАЗБЛОКИРОВКА»). При этом автономный режим памяти А, который устанавливается пользовательским процессом, является режимом принудительной разблокировки, и процесс установки автономного режима для памяти A завершается.

Следует отметить, что последовательные номера вышеупомянутых этапов не подразумевают последовательность выполнения, при этом последовательность выполнения этапов должна быть определена в соответствии с функциями и внутренней логикой, при этом она в любом случае не предназначается для ограничения процесса реализации варианта осуществления настоящего изобретения.

Исходя из вышесказанного, посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом заблокировать память и перевести память в автономный режим в соответствии с автономным режимом памяти для перевода памяти, которая блокируется пользовательским процессом, в автономный режим.

Фиг.3 схематически изображает блок-схему последовательности операций способа 300 для блокировки памяти в соответствии с вариантом осуществления настоящего изобретения. Как изображено на Фиг.3, способ 300 включает в себя следующие этапы:

S301: Пользовательский процесс в соответствии с требованием может запросить ядро о блокировке памяти A.

S302: Ядро определяет автономный режим, который устанавливается для памяти А, посредством анализа маркера PG_flag автономного режима памяти A.

Если ядро определяет, автономный режим памяти A является режимом по умолчанию, то есть PG_flag = «DEFAULT» («ПО УМОЛЧАНИЮ»), то процесс переходит на этап S303; а если ядро определяет, автономный режим памяти A не является режимом по умолчанию, то есть PG_flag ≠ «DEFAULT» («ПО УМОЛЧАНИЮ»), то процесс переходит на этап S305, S309 или S310. В частности, если ядро определяет, автономный режим памяти A является режимом переноса, то есть PG_flag = «MIGRATE» («ПЕРЕНОС»), то процесс переходит на этап S305; если ядро определяет, что автономный режим памяти A является режимом уведомления, то есть PG_flag = «NOTIFY» («УВЕДОМЛЕНИЕ»), то процесс переходит на этап S309; а если ядро определяет, что автономный режим памяти A является режимом принудительной разблокировки, то есть PG_flag = «UNLOCK» («РАЗБЛОКИРОВКА»), то процесс переходит на этап S310.

S303: Ядро определяет конфигурацию или требования вычислительной системы. Если ядро определяет, что вычислительной системе требуется выполнение системы, то процесс переходит на этап S304; а если вычислительной системе требуется выполнение «горячей» замены, то процесс переходит на этап S305.

S304: Если автономный режим памяти A является режимом по умолчанию, то ядро блокирует память A и присваивает маркеру автономного режима памяти значение «DEFAULT» («ПО УМОЛЧАНИЮ»), то есть PG_flag = «DEFAULT» («ПО УМОЛЧАНИЮ»). При этом автономный режим памяти А является режимом по умолчанию, и процесс блокировки памяти A завершается.

S305: Если автономный режим памяти A является режимом переноса, то ядро повторно запрашивает память В в намеченной области системы, причем намеченная область является не переносимой областью памяти и в общем ограничивается на основном узле.

S306: Ядро переносит память А в память B и отключает память A.

S307: Ядро определяет, была ли память A перенесена успешно. Если память A была перенесена успешно, то процесс переходит на этап S308; в противном случае процесс переходит на этап S304.

S308: Ядро блокирует память B, устанавливает маркер PG_flag автономного режима для памяти B и присваивает маркеру автономного режима значение «MIGRATE» («ПЕРЕНОС»), то есть PG_flag = «MIGRATE» («ПЕРЕНОС»). При этом автономный режим памяти А является режимом переноса, и процесс блокировки памяти A завершается.

S309: Если автономный режим памяти A является режимом уведомления, то ядро блокирует память A. При этом автономный режим памяти А является режимом уведомления, и процесс блокировки памяти A завершается.

S310: Если автономный режим памяти A является режимом принудительной разблокировки, то ядро блокирует память A. При этом автономный режим памяти А является режимом принудительной разблокировки, и процесс блокировки памяти A завершается.

Следует отметить, что последовательные номера вышеупомянутых этапов не подразумевают последовательность выполнения, при этом последовательность выполнения этапов должна быть определена в соответствии с функциями и внутренней логикой, при этом она в любом случае не предназначается для ограничения процесса реализации варианта осуществления настоящего изобретения.

Фиг.4 схематически изображает блок-схему последовательности операций способа 400 перевода заблокированной памяти в автономный режим в соответствии с вариантом осуществления настоящего изобретения. Как изображено на Фиг.4, способ 400 включает в себя следующие этапы:

S401: Ядро определяет перевод памяти А в автономный режим в соответствии с требованием.

S402: Ядро определяет автономный режим, который устанавливается для памяти А, посредством анализа маркера PG_flag автономного режима памяти A.

Если ядро определяет, что автономный режим памяти A является режимом по умолчанию, то есть PGflag = «DEFAULT» («ПО УМОЛЧАНИЮ»), то процесс переходит на этап S403; а если ядро определяет, что автономный режим памяти A не является режимом по умолчанию, то есть PG_flag ≠ «DEFAULT» («ПО УМОЛЧАНИЮ»), то процесс переходит на этап S403, S406 или S408. В частности, если ядро определяет, что автономный режим памяти A является режимом переноса, то есть PG_flag = «MIGRATE» («ПЕРЕНОС»), то процесс переходит на этап S403; если ядро определяет, что автономный режим памяти A является режимом уведомления, то есть PG_flag = «NOTIFY» («УВЕДОМЛЕНИЕ»), то процесс переходит на этап S406; а если ядро определяет, что автономный режим памяти A является режимом принудительной разблокировки, то есть PG_flag = «UNLOCK» («РАЗБЛОКИРОВКА»), то процесс переходит на этап S408.

S403: Если автономный режим памяти A является режимом по умолчанию или режимом переноса, то ядро ожидает разблокировки памяти пользовательским процессом.

S404: Ядро проверяет, была ли память A разблокирована пользовательским процессом. Если память A была разблокирована, то процесс переходит на этап S405; в противном случае процесс переходит на этап S403, то есть ядро продолжает ожидать разблокировки памяти А.

S405: Если память A была разблокирована пользовательским процессом, то ядро переносит память A. Следует отметить, что перенос памяти A является переносом памяти А в другие элементы памяти. Для новой памяти после переноса ядро может установить маркер автономного режима новой памяти со значением «DEFAULT» («ПО УМОЛЧАНИЮ»), то есть PG_flag = «DEFAULT» («ПО УМОЛЧАНИЮ»). При этом автономный режим памяти А является режимом по умолчанию или режимом переноса, и процесс перевода памяти А в автономный режим завершается.

S406: Если автономный режим памяти A является режимом уведомления, то ядро побуждает пользовательский процесс к разблокировке памяти и переносит память А после разблокировки памяти A пользовательским процессом. То есть в случае, когда автономный режим памяти A является режимом уведомления, процесс переходит с этапа S406 на этап S404, S405 и S407.

S407: После переноса памяти A ядро побуждает пользовательский процесс к блокировке новой памяти после переноса. Для новой памяти после переноса ядро может установить маркер автономного режима новой памяти со значением «NOTIFY» («УВЕДОМЛЕНИЕ»), то есть PG_flag = «NOTIFY» («УВЕДОМЛЕНИЕ»). При этом автономный режим памяти А является режимом уведомления, и процесс перевода памяти А в автономный режим завершается.

S408: Если автономный режим памяти A является режимом принудительной разблокировки, то ядро осуществляет разблокировку памяти A.

S409: Ядро проверяет, была ли память A разблокирована успешно. Если память A была разблокирована, то процесс переходит на этап S410; в противном случае процесс переходит на этап S408, то есть ядро продолжает осуществлять разблокировку памяти A.

S410: После разблокировки памяти A ядро переносит память A, к примеру ядро переносит память А в память B.

S411: Ядро блокирует новую память B и устанавливает маркер автономного режима для новой памяти B для идентификации того, что автономный режим новой памяти В является режимом принудительной разблокировки, то есть значением, присвоенным маркеру автономного режима, является значение «UNLOCK» («РАЗБЛОКИРОВКА»), то есть PG_flag = «UNLOCK» («РАЗБЛОКИРОВКА»). При этом автономный режим памяти А является режимом принудительной разблокировки, и процесс перевода памяти А в автономный режим завершается.

Фиг.5 схематически изображает блок-схему последовательности операций способа 500 разблокировки памяти в соответствии с вариантом осуществления настоящего изобретения. Как изображено на Фиг.5, способ 500 включает в себя следующие этапы:

S501: Пользовательский процесс запрашивает ядро о разблокировке заблокированной памяти A.

S502: Ядро определяет автономный режим памяти А посредством анализа маркера автономного режима памяти A.

Если ядро определяет, что автономный режим памяти A является режимом по умолчанию, то есть PG_flag = = «DEFAULT» («ПО УМОЛЧАНИЮ»), то процесс переходит на этап S504; а если ядро определяет, что автономный режим памяти A не является режимом по умолчанию, то есть PGflag ≠ «DEFAULT» («ПО УМОЛЧАНИЮ»), то процесс переходит на этап S503 или S504. В частности, если ядро определяет, что автономный режим памяти A является режимом переноса, то есть PG_flag = «MIGRATE» («ПЕРЕНОС»), то процесс переходит на этап S503 и S504; а если ядро определяет, что в автономный режим памяти A является режимом уведомления, то есть PG_flag = «NOTIFY» («УВЕДОМЛЕНИЕ»); или режимом принудительной разблокировки, то есть PG_flag = «UNLOCK» («РАЗБЛОКИРОВКА»), то процесс переходит непосредственно на этап S504.

S503: Ядро повторно переносит память на узел, на котором выполняется пользовательский процесс, для дополнительного повышения рабочих характеристик системы.

S504: Ядро осуществляет разблокировку памяти A. При этом процесс разблокировки памяти А, которая блокируется пользовательским процессом, завершается.

Следует отметить, что последовательные номера вышеупомянутых этапов не подразумевают последовательность выполнения, при этом последовательность выполнения этапов должна быть определена в соответствии с функциями и внутренней логикой, при этом она в любом случае не предназначается для ограничения процесса реализации варианта осуществления настоящего изобретения.

Исходя из вышесказанного, в способе управления памятью вычислительной системы в соответствии с вариантом осуществления настоящего изобретения, посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, повышаются рабочие характеристики системы, а также устраняются потери системных ресурсов.

Выше со ссылкой на Фиг.1А-5 был подробно описан способ управления памятью вычислительной системы в соответствии с вариантами осуществления настоящего изобретения, а ниже, со ссылкой на Фиг.6-12, будет подробно описываться блок управления памятью и вычислительная система в соответствии с вариантами осуществления настоящего изобретения.

Фиг.6 схематически изображает блок-схему блока 700 управления памятью в соответствии с вариантом осуществления настоящего изобретения. Как изображено на Фиг.6, блок 700 управления памятью включает в себя: первый приемный модуль 710, выполненный с возможностью приема запроса на выделение, отправляемого пользовательским процессом, причем запрос на выделение используется для запроса выделения памяти вычислительной системы для пользовательского процесса; модуль 720 выделения, выполненный с возможностью выделения памяти для пользовательского процесса в соответствии с запросом на выделение, который принимается первым приемным модулем 710, и для установки маркера автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти; второй приемный модуль 730, приема запроса на блокировку, отправляемого пользовательским процессом, причем запрос на блокировку используется для запроса блокировки памяти вычислительной системы; модуль 740 блокировки, блокировки памяти в соответствии с запросом на блокировку, который принимается вторым приемным модулем 730, а также в соответствии с маркером автономного режима памяти; и модуль 750 перевода в автономный режим, перевода памяти, которая блокируется модулем блокировки, в автономный режим в соответствии с маркером автономного режима памяти.

В блоке управления памятью в соответствии с вариантом осуществления настоящего изобретения посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти, для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, повышаются рабочие характеристики системы, а также устраняются потери системных ресурсов.

При необходимости в варианте осуществления настоящего изобретения автономный режим или автономная политика может включать в себя по меньшей мере один из следующих режимов: режим «DEFAULT» («ПО УМОЛЧАНИЮ»), режим «MIGRATE» («ПЕРЕНОС»), режим «NOTIFY» («УВЕДОМЛЕНИЕ») и режим «UNLOCK» (принудительная «РАЗБЛОКИРОВКА»). При необходимости автономный режим включает в себя режим по умолчанию, режим переноса, режим уведомления и режим принудительной разблокировки.

При необходимости в варианте осуществления настоящего изобретения, как изображено на Фиг.7, блок 700 управления памятью дополнительно включает в себя: третий приемный модуль 760, выполненный с возможностью приема запроса на изменение, который включает в себя информацию о режиме и отправляется посредством пользовательского процесса, причем информация о режиме указывает автономный режим, который устанавливается посредством пользовательского процесса для памяти; и модуль 770 изменения, выполненный с возможностью изменения маркера автономного режима памяти в соответствии с информацией о режиме, которая принимается третьим приемным модулем 760, для указания автономного режима, который устанавливается пользовательским процессом.

При необходимости в варианте осуществления настоящего изобретения, как изображено на Фиг.7, блок 700 управления памятью дополнительно включает в себя: модуль 780 определения, выполненный с возможностью повторного определения автономного режима памяти в соответствии с требованием вычислительной системы, и изменения маркера автономного режима памяти для указания повторно определенного автономного режима в случае, когда автономный режим памяти является режимом по умолчанию.

При необходимости, как изображено на Фиг.8, блок 700 управления памятью дополнительно включает в себя: четвертый приемный модуль 790, выполненный с возможностью приема запроса на разблокировку, отправляемого пользовательским процессом, причем запрос на разблокировку используется для запроса разблокировки памяти; и модуль 795 повторного переноса, выполненный с возможностью повторного переноса памяти на узел, на котором выполняется пользовательский процесс в соответствии с запросом на разблокировку, который принимается четвертым приемным модулем, и в случае, когда маркер автономного режима памяти указывает режим переноса.

В варианте осуществления настоящего изобретения, как изображено на Фиг.9, модуль 740 блокировки в соответствии с вариантом осуществления настоящего изобретения, может включать в себя: первый подмодуль 741 блокировки, выполненный с возможностью блокировки памяти, когда маркер автономного режима памяти указывает режим по умолчанию, режим уведомления или режим принудительной разблокировки; и второй подмодуль 742 блокировки, выполненный с возможностью переноса памяти, когда маркер автономного режима памяти указывает режим переноса, если память перенесена успешно, блокировки перенесенной памяти и установки маркера автономного режима, указывающего режим переноса, для перенесенной памяти; а в случае, если память была перенесена неудачно, для блокировки памяти и изменения маркера автономного режима памяти для указания режима по умолчанию.

При необходимости, как изображено на Фиг.10, модуль 750 перевода в автономный режим включает в себя: первый подмодуль 751 перевода в автономный режим, выполненный с возможностью ожидания разблокировки памяти, когда маркер автономного режима памяти указывает режим по умолчанию или режим переноса, а также для переноса памяти после разблокировки памяти; второй подмодуль 752 перевода в автономный режим, выполненный с возможностью побуждения пользовательского процесса к разблокировке памяти, когда маркер автономного режима памяти указывает режим уведомления, переноса памяти после разблокировки памяти, и побуждения пользовательского процесса к блокировке перенесенной памяти после переноса памяти; и третий подмодуль 753 перевода в автономный режим, выполненный с возможностью разблокировки памяти, когда маркер автономного режима памяти указывает режим принудительной разблокировки, переноса памяти после разблокировки памяти, блокировки перенесенной памяти, и установки для перенесенной памяти маркера автономного режима, указывающего режим принудительной разблокировки.

При необходимости, как изображено на Фиг.11, модуль 780 определения включает в себя: первый подмодуль 781 определения, выполненный с возможностью определения автономного режима памяти в качестве режима по умолчанию, когда вычислительная система требует выполнения работы системы; и второй подмодуль 782 определения, выполненный с возможностью определения автономного режима памяти в качестве режима переноса, когда вычислительная система требует выполнения «горячей» замены.

Блок 700 управления памятью в соответствии с вариантом осуществления настоящего изобретения, может представлять собой ядро или операционную систему в способе в соответствии с вариантами осуществления настоящего изобретения, причем вышеперечисленные и другие операции и/или функции каждого модуля в блоке 700 управления памятью соответствующим образом обеспечиваются для реализации соответствующих этапов способов 100-500 на Фиг.1А-5, которые в целях упрощения далее не будут описаны повторно.

В блоке управления памятью в соответствии с вариантом осуществления настоящего изобретения, посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, повышаются рабочие характеристики системы, а также устраняются потери системных ресурсов.

Фиг.12 схематически изображает блок-схему вычислительной системы 800 в соответствии с вариантом осуществления настоящего изобретения. Как изображено на Фиг.12, вычислительная система включает в себя по меньшей мере одну память 810 и блок 820 управления памятью в соответствии с вариантом осуществления настоящего изобретения, причем блок 820 управления памятью конфигурируется для управления по меньшей мере одной памятью 810 и может включать в себя: первый приемный модуль, выполненный с возможностью приема запроса на выделение, отправляемого пользовательским процессом, причем запрос на выделение используется для запроса выделения памяти вычислительной системы для пользовательского процесса; модуль выделения, выполненный с возможностью выделения памяти для пользовательского процесса в соответствии с запросом на выделение, который принимается первым приемным модулем, и установки маркера автономного режима для памяти, причем маркер автономного режима используется для указания автономного режима памяти; второй приемный модуль, выполненный с возможностью приема запроса на блокировку, который отправляется пользовательским процессом, причем запрос на блокировку используется для запроса блокировки памяти вычислительной системы; модуль блокировки, выполненный с возможностью блокировки памяти в соответствии с запросом на блокировку, принимаемого вторым приемным модулем, и маркером автономного режима памяти; и модуль перевода в автономный режим, выполненный с возможностью перевода памяти, которая блокируется модулем блокировки, в автономный режим в соответствии с маркером автономного режима памяти.

При необходимости в варианте осуществления настоящего изобретения автономный режим включает в себя по меньшей мере один из режима по умолчанию, режима переноса, режима уведомления и режима принудительной разблокировки. При необходимости блок 820 управления памятью дополнительно включает в себя: третий приемный модуль, выполненный с возможностью приема запроса на изменение, который включает в себя информацию о режиме и отправляется пользовательским процессом, причем информация о режиме указывает автономный режим, который устанавливается пользовательским процессом для памяти; и модуль изменения, выполненный с возможностью изменения маркера автономного режима памяти в соответствии с информацией о режиме, которая принимается третьим приемным модулем, для указания автономного режима, который устанавливается пользовательским процессом.

При необходимости блок 820 управления памятью дополнительно включает в себя: модуль определения, выполненный с возможностью повторного определения автономного режима памяти в соответствии с требованием вычислительной системы, и изменения маркера автономного режима памяти для указания повторно определенного автономного режима в случае, когда автономный режим памяти является режимом по умолчанию.

При необходимости блок 820 управления памятью дополнительно включает в себя: четвертый приемный модуль, выполненный с возможностью приема запроса на разблокировку, который отправляется пользовательским процессом, причем запрос на разблокировку используется для запроса разблокировки памяти; и модуль повторного переноса, выполненный с возможностью повторного переноса памяти на узел, на котором выполняется пользовательский процесс в соответствии с запросом на разблокировку, который принимается четвертым приемным модулем, когда маркер автономного режима памяти указывает режим переноса.

При необходимости в варианте осуществления настоящего изобретения модуль блокировки включает в себя: первый подмодуль блокировки, выполненный с возможностью блокировки памяти, когда маркер автономного режима памяти указывает режим по умолчанию, режим уведомления или режим принудительной разблокировки; и второй подмодуль блокировки, выполненный с возможностью переноса памяти, когда маркер автономного режима памяти указывает режим переноса, если память перенесена успешно, для блокировки перенесенной памяти и установки для перенесенной памяти маркера автономного режима, указывающего режим переноса; а в случае, если память была перенесена неудачно, для блокировки памяти и изменения маркера автономного режима памяти для указания режима по умолчанию.

При необходимости в варианте осуществления настоящего изобретения модуль перевода в автономный режим включает в себя: первый подмодуль перевода в автономный режим, выполненный с возможностью ожидания разблокировки памяти, когда маркер автономного режима памяти указывает режим по умолчанию или режим переноса, а также для переноса памяти после разблокировки памяти; второй подмодуль перевода в автономный режим, выполненный с возможностью побуждения пользовательского процесса к разблокировке памяти, когда маркер автономного режима памяти указывает режим уведомления, переноса памяти после разблокировки памяти, и побуждения пользовательского процесса к блокировке перенесенной памяти после переноса памяти; и третий подмодуль перевода в автономный режим, выполненный с возможностью разблокировки памяти, когда маркер автономного режима памяти указывает режим принудительной разблокировки, переноса памяти после разблокировки памяти, блокировки перенесенной памяти, и установки для перенесенной памяти маркера автономного режима, указывающего режим принудительной разблокировки.

Блок 820 управления памятью в соответствии с вариантом осуществления настоящего изобретения может являться аналогичным блоку 700 управления памятью в устройстве в соответствии с вариантом осуществления настоящего изобретения, причем вышеперечисленные и другие операции и/или функции каждого модуля в блоке 820 управления памятью соответствующим образом обеспечиваются для реализации соответствующих этапов способов 100-500 на Фиг.1А-5, которые в целях упрощения далее не будут описаны повторно.

В вычислительной системе в соответствии с вариантом осуществления настоящего изобретения, посредством взаимодействия между ядром и пользовательским процессом, а также посредством установки автономного режима для памяти, ядро может соответствующим образом перевести память в автономный режим в соответствии с автономным режимом памяти, для перевода памяти, которая блокируется пользовательским процессом, в автономный режим, благодаря чему реализуется «горячая» замена памяти, повышаются рабочие характеристики системы, а также устраняются потери системных ресурсов.

Следует отметить, что заблокированная память в вариантах осуществления настоящего изобретения не ограничивается заблокированной памятью, запрашиваемой пользовательским процессом, а также что заблокированная память для других целей также может быть переведена в автономный режим при помощи решения в соответствии с вариантами осуществления настоящего изобретения. Кроме того, политика переноса в автономной политике для заблокированной памяти не ограничивается решением, которое формулируется пользовательским процессом и выполняется ядром, при этом политика переноса может заключаться в том, что пользовательский процесс определяет память для запроса для переноса в специальную область памяти, благодаря чему реализуется требование перевода памяти в автономный режим без переноса.

Специалистам в данной области техники должно быть понятно, что блоки и этапы алгоритма примеров, описанных в сочетании с раскрытыми в данном документе вариантами осуществления, могут быть реализованы электронными аппаратными средствами, программными средствами или их сочетанием. Для четкого описания взаимозаменяемости между аппаратными и программными средствами, композиции и этапы каждого примера, в целом, были описаны выше в соответствии с функциями. Выполнение функции либо аппаратными средствами, либо программными средствами зависит от конкретных вариантов использования и условий конструктивных ограничений. Специалисты в данной области техники могут использовать различные способы для реализации описанных функций для каждого конкретного варианта использования, при этом нельзя считать, что вариант реализации выходит за пределы объема настоящего изобретения.

Специалистам в данной области техники должно быть понятно, что для удобства и краткости описания подробного рабочего процесса вышеупомянутой системы, устройства и блока, может быть упомянут соответствующий процесс в вариантах осуществления способа, при этом подробности не должны быть описаны повторно.

В некоторых вариантах осуществления, представленных в настоящем документе, следует подразумевать, что раскрытая система, устройство и способ могут быть реализованы другими способами. К примеру, описанные варианты осуществления устройства попросту являются иллюстративными. К примеру, деление блока попросту является логическим функциональным делением, при этом в конкретном варианте реализации оно может являться делением другого типа. К примеру, множество блоков или компонентов могут быть объединены или интегрированы в другую систему, или же некоторые отличительные признаки могут быть проигнорированы или не выполнены. Помимо всего прочего, изображенная или обсуждаемая связь, прямая связь или коммуникационное соединение может быть осуществлена посредством опосредованной связи или соединения передачи данных между некоторыми интерфейсами, устройствами или блоками, или же может являться электрической, механической или иметь другую форму.

Блоки, описанные в качестве отдельных компонентов, могут быть физически разделены. Компоненты, изображенные в качестве блоков, могут являться физическими блоками, то есть могут быть интегрированы или распределены среди множества сетевых блоков. Некоторые или все блоки могут быть выбраны для достижения цели решения варианта осуществления в соответствии с фактическими требованиями.

Кроме того, функциональные блоки в вариантах осуществления настоящего изобретения могут быть либо интегрированы в процессорном модуле, либо каждый из них может являться отдельным физическим блоком; в альтернативном варианте два и более блоков интегрируются в одном блоке. Интегрированные блоки могут быть реализованы при помощи аппаратных или программных функциональных блоков.

Если реализация осуществляется в виде программных функциональных блоков, а продажа или использование осуществляется в качестве независимого продукта, то интегрированные блоки также могут быть сохранены на машиночитаемом носителе. На основании такого подхода техническое решение настоящего изобретения или части, которая вносит свой вклад в уровень техники, или полное или часть технического решения, по существу могут быть реализованы в виде программного продукта. Компьютерный программный продукт сохраняется на носителе и включает в себя несколько команд, побуждающих компьютерное оборудование (такое как, персональный компьютер, сервер или сетевое оборудование) к выполнению всех или части этапов способа, описанного в вариантах осуществления настоящего изобретения. Носитель включает в себя различные среды с функцией хранения программных кодов, такие как флэш-память USB, переносной жесткий диск, постоянную память (ROM), оперативную память (RAM), магнитный или оптический диск.

Вышеприведенное описание представляет лишь конкретные варианты осуществления настоящего изобретения, при этом объем правовой охраны настоящего изобретения не ограничивается ими. Любая равноценная модификация или замена, легко осуществимая специалистами в данной области техники в пределах технического объема настоящего изобретения, должна находиться в пределах объема правовой охраны настоящего изобретения. Исходя из вышесказанного, объем правовой охраны настоящего изобретения определяется приложенной формулой изобретения.