Результат интеллектуальной деятельности: УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Известны устройства для вычисления модуля комплексного числа [А.с. 1001085 СССР. Устройство для вычисления модуля комплексного числа, 1983 г.], а также [А.с. 1508206 A1 СССР. Устройство для вычисления модуля комплексного числа, 1989 г.].

Недостатком обоих устройств является большое количество аппаратуры (электронных компонентов).

Наиболее близким по технической сущности является устройство для вычисления модуля комплексного числа [А.с. 1693599 A1 СССР. Устройство для вычисления модуля комплексного числа. 1991 г.].

Оно содержит два регистра аргумента, три сумматора и первый коммутатор, причем n-разрядный выход первого регистра аргумента соединен с n-разрядными входами первых слагаемых первого и второго сумматоров, выходы n-2 старших разрядов первого регистра аргумента соединены с n-2 младшими разрядами входа первого слагаемого третьего сумматора, n-разрядные прямые и инверсные выходы второго регистра аргумента соединены с входами вторых слагаемых, соответственно, третьего и второго сумматоров, выходы n-2 старших разрядов прямого выхода второго регистра аргумента соединены с n-2 младшими разрядами второго слагаемого первого сумматора, выходы первого и третьего сумматоров соединены, соответственно, с первым и вторым информационными входами первого коммутатора, кроме того, дополнительно устройство содержит пять коммутаторов, схему сравнения, буферный регистр, пять триггеров, логические схемы НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ и блок управления.

Недостатками этого устройства являются большие аппаратурные затраты и малое быстродействие (результат его работы проявляется за несколько тактов).

Задачей настоящего изобретения является повышение технической эффективности.

Технический результат настоящего изобретения - повышенное быстродействие устройства при вычислении модуля комплексного числа при уменьшении аппаратурных затрат и при неснижении точности вычисления.

Поставленная задача решена предложенным устройством для вычисления модуля комплексного числа, который содержит первый и второй регистры аргумента, первый, второй, третий и четвертый коммутаторы, первую и вторую схему сравнения, сумматор, при этом информационные выходы первого и второго регистров аргумента соединены с информационными входами первой, а через одноименные коммутаторы также и со входами второй схемы сравнения, прямой и инверсный выходы первой схемы сравнения связаны с управляющими входами первого и второго коммутаторов соответственно, кроме того, информационные выходы первого и второго регистра аргумента связаны также с информационными входами третьего и четвертого коммутаторов соответственно, чьи управляющие входы связаны с выходами первой и второй схемы сравнения, а выходы связаны со входами сумматора, выход которого является выходом устройства.

Введение дополнительно второй схемы сравнения, причем, как и первой - в виде комбинационных схем, позволило резко сократить время вычисления, а также уменьшить объем оборудования без снижения точности вычисления модуля комплексного числа. Это является новым техническим решением в технике цифрового функционального преобразования, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяет сократить время вычисления и уменьшить объем оборудования (микросхемы).

Предложенное устройство для вычисления модуля комплексного числа промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральные логические схемы).

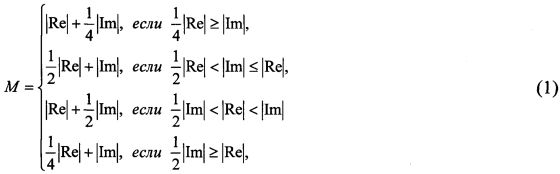

Сущность изобретения заключается в реализации вычисления модуля комплексного числа по следующей формуле:

где M - значение модуля комплексного числа, Re - значение действительной части, Im - значение мнимой части.

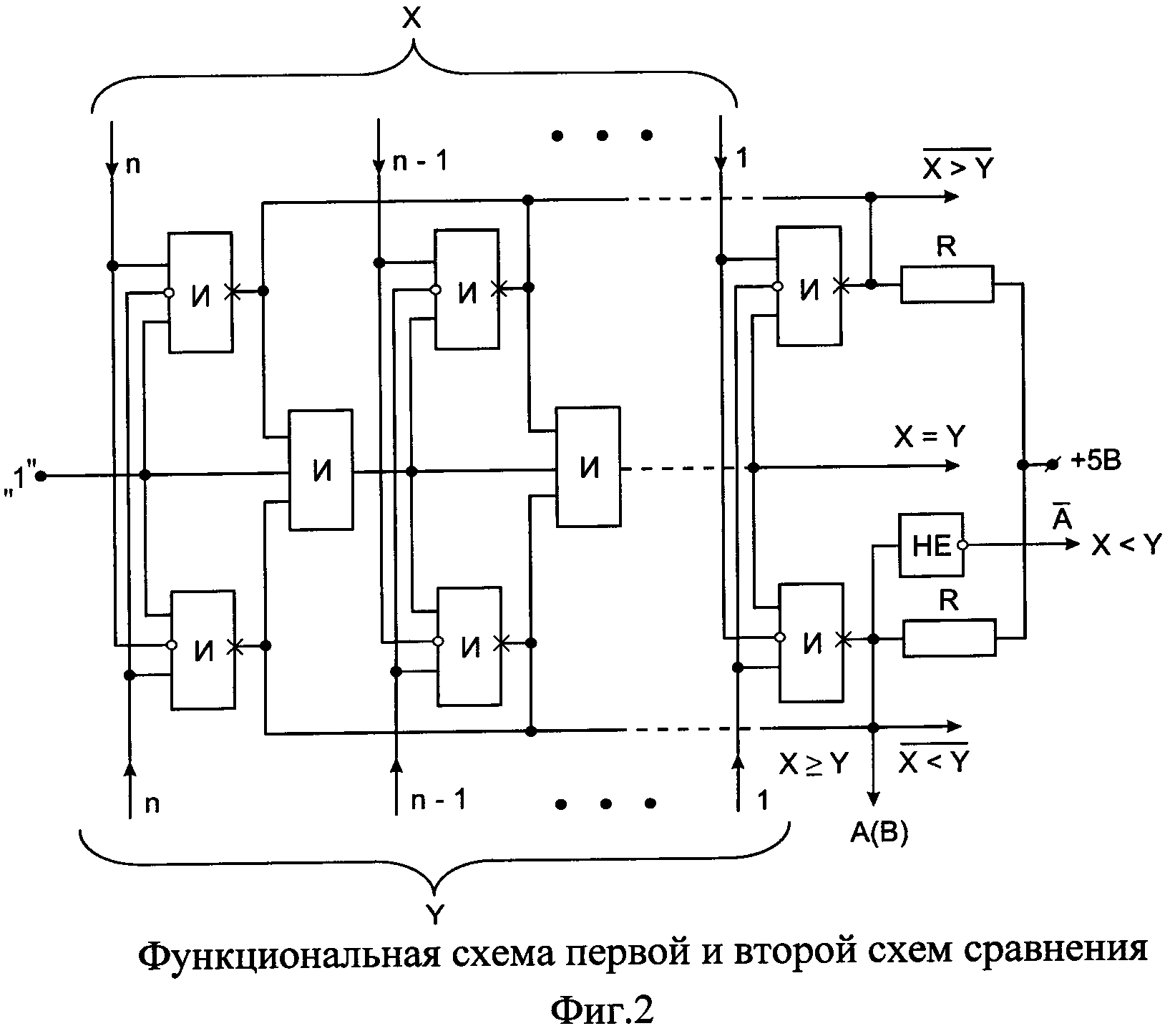

На фиг. 1 приведена структурная схема устройства для вычисления

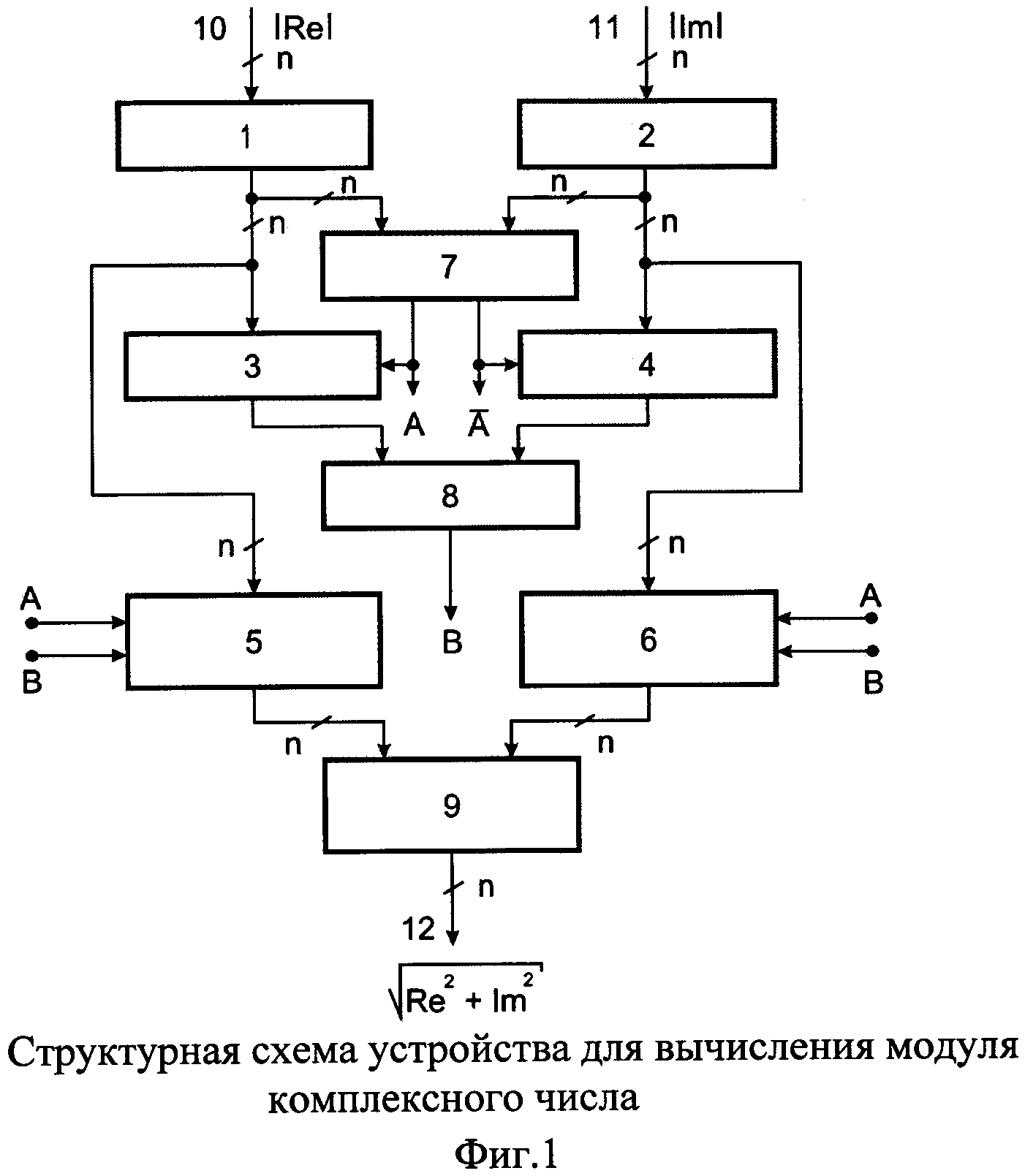

модуля комплексного числа, на фиг. 2 - функциональные схемы первой и второй схем сравнения. На ней буквами X и Y обозначены  (или

(или  ) и

) и  (или

(или  ) соответственно. Кроме того, A

) соответственно. Кроме того, A  и B помечены выходы первой и второй схем сравнения соответственно.

и B помечены выходы первой и второй схем сравнения соответственно.

Заявленное устройство содержит первый 1 и второй 2 регистры аргумента, первый 3, второй 4, третий 5 и четвертый 6 коммутаторы, первую 7 и вторую 8 схемы сравнения и сумматор 9, причем блоки 7, 8 и 9 - комбинационного типа, 10, 11 - входные n-разрядные, а 12 - выходный n-разрядный выход.

Для повышения быстродействия устройства используются дополнительная вторая схема сравнения, причем как первая, так и вторая - комбинационного типа (а не с помощью сумматоров, как у прототипа).

При этом первая и вторая схемы сравнения построены по регулярному принципу: каждый разряд схемы сравнения использует три логические схемы И и "монтажное" ИЛИ.

При этом информационные выходы первого 1 регистра аргумента соединены с информационными входами первой 7, а через первый 3 и третий 5 коммутаторы - со второй 8 схемами сравнения, а информационные выходы второго 2 регистра аргумента связаны с информационными входами первой 7, а через второй 4 коммутатор - со второй 8 схемами сравнения. Информационные выходы регистров 1 и 2 аргументов также связаны с информационными входами третьего 5 и четвертого 6 коммутаторов соответственно, выходы которых соединены со входами сумматора 9 комбинационного типа.

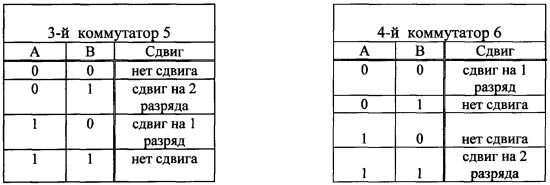

Управляющие входы первого 3 и второго 4 коммутаторов связаны с выходами первой 7 схемы сравнения, а управляющие входы A, B третьего 5 и четвертого 6 коммутаторов связаны с выходом A первой 7 и выходом В второй 8 схем сравнения. Первый 3 и второй 4 коммутаторы пропускают входное двоичное число с арифметическим сдвигом на 1 разряд в сторону младших разрядов, либо без сдвига в зависимости от значения сигналов A и  , получаемых с выхода первой схемы сравнения. A третий 5 и четвертый 6 коммутаторы пропускают либо с арифметическим сдвигом на 1 разряд, либо - 2 разряда в сторону младших разрядов, либо без сдвига в зависимости от сочетания сигналов A и B, получаемых на выходах первой 7 и второй 8 схем сравнения.

, получаемых с выхода первой схемы сравнения. A третий 5 и четвертый 6 коммутаторы пропускают либо с арифметическим сдвигом на 1 разряд, либо - 2 разряда в сторону младших разрядов, либо без сдвига в зависимости от сочетания сигналов A и B, получаемых на выходах первой 7 и второй 8 схем сравнения.

Для каждого коммутатора приводятся таблицы сдвигов (см. далее), которые обеспечены монтажным способом.

Достоверность достижения поставленной цели изобретения - повышение технической эффективности устройства - подтверждается математическими расчетами реального быстродействия и потребного количества аппаратурного оборудования, так как в нем используются функциональные устройства комбинационного типа, то есть срабатывающие за один такт времени.

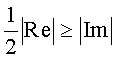

Устройство работает следующим образом. Как только в регистрах 1, 2 аргумента окажутся мантиссы действительной Re и мнимой Im частей комплексного числа в прямом двоичном коде, n разрядов мантисс каждой части поступают на первую 7 схему сравнения. На ее выходе появляется сигнал A в виде высокого уровня напряжения, соответствующего "1", и сигнал  в виде низкого уровня напряжения, соответствующий "0", если

в виде низкого уровня напряжения, соответствующий "0", если  . Если

. Если  , значения A и

, значения A и  меняются на противоположные, т.е. A=0,

меняются на противоположные, т.е. A=0,  .

.

Один из сигналов A или  , равный "1", арифметически сдвигает через один из коммутаторов 3 или 4 содержимое большей части (

, равный "1", арифметически сдвигает через один из коммутаторов 3 или 4 содержимое большей части ( или

или  ) на один разряд в сторону младших разрядов, т.е. уменьшает в два раза и подает на один из входов второй 8 схемы сравнения. Меньшая же часть (

) на один разряд в сторону младших разрядов, т.е. уменьшает в два раза и подает на один из входов второй 8 схемы сравнения. Меньшая же часть ( или

или  ) проходит через другой коммутатор из пары 3 или 4 без сдвига на другой вход второй 8 схемы сравнения. На ее выходе появляется сигнал B, равный "1", если

) проходит через другой коммутатор из пары 3 или 4 без сдвига на другой вход второй 8 схемы сравнения. На ее выходе появляется сигнал B, равный "1", если  , и "0", если

, и "0", если  , или такие же сигналы если

, или такие же сигналы если  или

или  .

.

Сигналы A и B в виде сочетаний "0" и "1" поступают на управляющие входы третьего 5 и четвертого 6 коммутаторов, на информационные входы которых поступают n разрядов мантисс в прямом двоичном коде чисел  или

или  , соответственно 5, 6. Коммутаторы передают эти числа с арифметическим сдвигом на один, два разряда в сторону младших разрядов или без сдвига, причем, каждый по своему правилу в зависимости от значений A и B, в соответствии с таблицами.

, соответственно 5, 6. Коммутаторы передают эти числа с арифметическим сдвигом на один, два разряда в сторону младших разрядов или без сдвига, причем, каждый по своему правилу в зависимости от значений A и B, в соответствии с таблицами.

На выходе сумматора 9 появляется n-разрядный двоичный код результата - модуль комплексного числа.

Благодаря использованию функциональных логических схем комбинационного типа результат появляется в одном такте, т.е. спустя время переходных процессов в высокоскоростных микросхемах.

Устройство для вычисления модуля комплексного числа, содержащее первый и второй регистры аргумента, первый и второй коммутаторы, сумматор, первую схему сравнения, причем n-разрядные выходы первого и второго регистров аргументов связаны с информационными входами первого и второго коммутаторов соответственно, а также с двумя входами первой схемы сравнения, выходы которой связаны с управляющими входами первого и второго коммутаторов, отличающееся тем, что в него дополнительно введены третий и четвертый коммутаторы, вторая схема сравнения, первый и второй входы которой связаны с выходами первого и второго коммутаторов соответственно, а выходы первого и второго регистров аргумента соединены с информационными входами третьего и четвертого коммутаторов соответственно, чьи управляющие входы связаны с выходами первой и второй схем сравнения, кроме того, выходы третьего и четвертого коммутаторов связаны со входами сумматора, выход которого является выходом устройства.