Результат интеллектуальной деятельности: ВЫХОДНОЙ КАСКАД ДЛЯ КМОП МИКРОСХЕМ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ

Вид РИД

Изобретение

Предлагаемое изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано преимущественно для защиты выходов высокочастотных металлооксидных полупроводниковых (МОП) микросхем от электростатических разрядов (ЭСР).

Известно устройство защиты входов интегральных микросхем от перенапряжения, состоящее из двух каскадов[1]. Первый каскад содержит две шунтирующие цепи для различных величин входного напряжения и дополнительный резистор с большим сопротивлением. Второй каскад содержит шунтирующую цепь в виде мелалл-диэлектрик-полупроводник (МДП) с толстым окислом и дополнительный резистор с большим сопротивлением.

Недостатком данного устройства является то, что оно имеет на входе резисторы большого номинала, функциональные возможности устройства ограничены областью применения для микросхем низкого быстродействия.

Известно устройство защиты входов интегральных микросхем от перенапряжения, включающее резистор, соединенный с двумя последовательно соединенными диодами, один из которых соединен с общей шиной питания, а второй - с общей шиной, а свободный конец резистора соединен с входной шиной [2].

Устройство может применяться для быстродействующих микросхем. Однако данная микросхема обладает инерционностью, в результате чего при попадании на вход интегральной микросхемы высокого потенциала статического электричества вероятность пробоя подзатворного окисла резко увеличивается.

Наиболее близким по технической сущности и достигаемому эффекту является устройство защиты выводов интегральных схем со структурой МДП от электростатических разрядов, содержащее два ключевых транзистора, которые обеспечивают протекание разрядного тока большой величины, два управляющих транзистора, которые, в свою очередь, обеспечивают разделение тока на две равновеликие (одинаковые) составляющие, а также два нагрузочных резистора [3].

Однако основным недостатком известного из уровня техники решения по отношению к заявленному изобретению является то, что паразитная емкость больших ключевых транзисторов в устройстве защиты складывается с емкостью выходных транзисторов и ухудшает быстродействие выходного каскада.

Задачей изобретения является уменьшение электрической емкости и площади на кристалле выходного каскада для КМОП микросхем с устройством защиты от электростатических разрядов за счет уменьшения площади его функциональных элементов при сохранении качественных характеристик.

Выходной каскад для КМОП микросхем с устройством защиты от электростатических разрядов, содержащий выходной p-канальный транзистор и выходной n-канальный транзистор, стоками подключенные к выходной шине, логические элементы ИЛИ-НЕ и И-НЕ, управляющие напряжениями на затворах выходных транзисторов, ключевой p-канальный транзистор и ключевой n-канальный транзистор, которые обеспечивают протекание разрядного тока большой величины, два управляющих симметричных p-канальных транзистора, два управляющих симметричных n-канальных транзистора, которые, в свою очередь, обеспечивают разделение тока на четыре равновеликие (одинаковые) составляющие, а также нагрузочные резисторы.

Логические элементы ИЛИ-НЕ и И-НЕ обеспечивают включение выходных транзисторов одновременно с ключевыми транзисторами устройства защиты при воздействии электростатического разряда любой полярности (положительной, отрицательной) на выход микросхемы.

Одновременное включение ключевых и выходных транзисторов ведет к уменьшению вдвое сопротивления в цепи разрядного тока и дает возможность использовать в устройстве защиты менее мощные ключевые транзисторы и, соответственно, уменьшить его массогабаритные характеристики в целом.

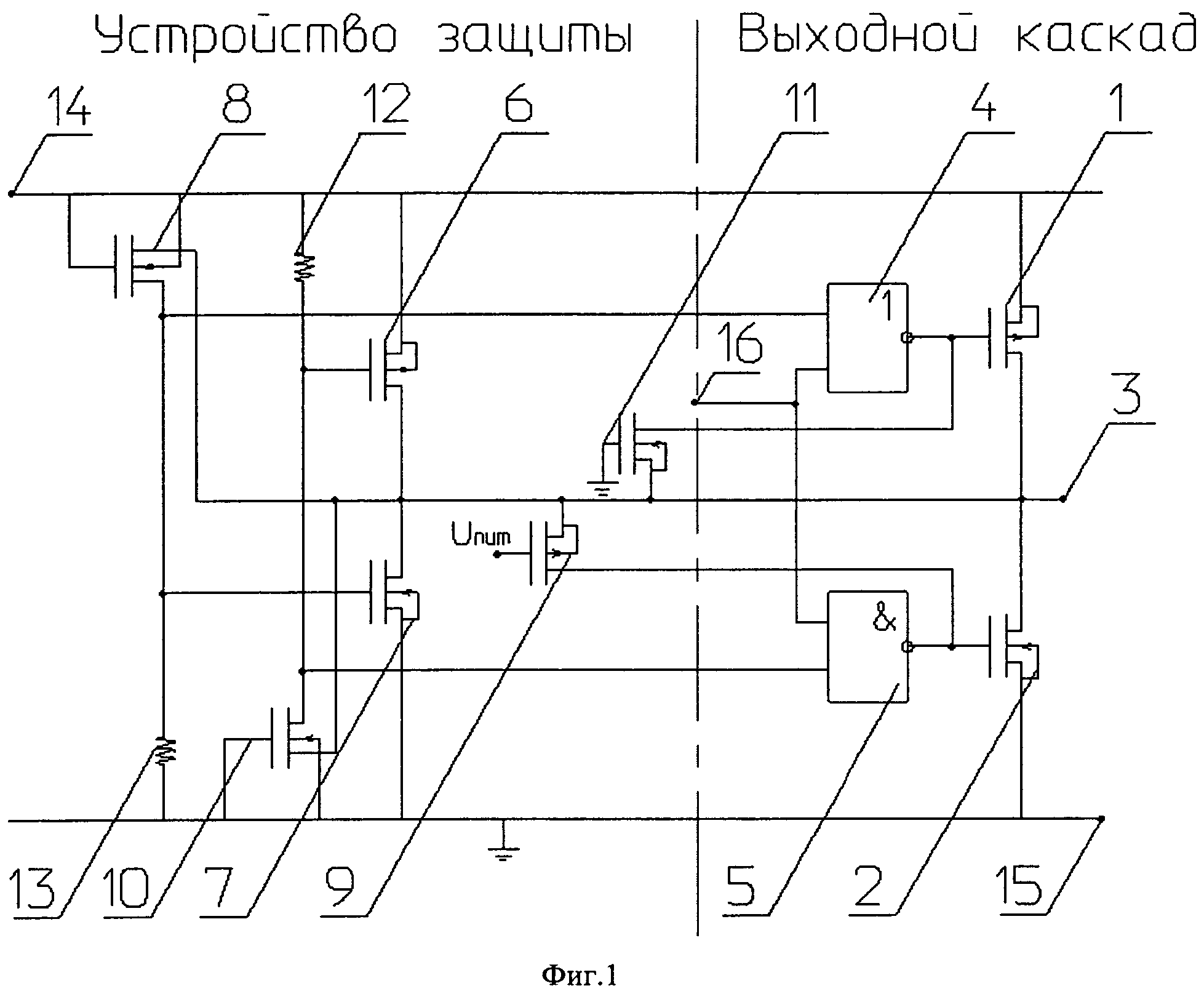

Сущность изобретения поясняется Фиг. 1, где представлена функциональная схема и введены следующие обозначения:

1 - Выходной p-канальный транзистор

2 - Выходной n-канальный транзистор

3 - Выходная шина

4 - Логический элемент ИЛИ-НЕ

5 - Логический элемент И-НЕ

6 - Ключевой p-канальный транзистор

7 - Ключевой n-канальный транзистор

8 - Первый управляющий p-канальный транзистор

9 - Второй управляющий p-канальный транзистор

10 - Первый управляющий n-канальный транзистор

11 - Второй управляющий n-канальный транзистор

12 - Первый нагрузочный резистор

13 - Второй нагрузочный резистор

14 - Шина питания

15 - Шина земли

16 - Входная шина

Предлагаемый выходной каскад включает устройство защиты, содержащий выходной p-канальный транзистор 1 и выходной n-канальный транзистор 2, стоками подключенные к выходной шине 3, логические элементы ИЛИ-НЕ 4 и И-НЕ 5, управляющие напряжениями на затворах выходных транзисторов, а также устройство защиты от электростатических разрядов, содержащее ключевой p-канальный транзистор 6 и ключевой n-канальный транзистор 7, которые обеспечивают протекание разрядного тока большой величины, два управляющих симметричных p-канальных транзистора 8 и 9, два управляющих симметричных n-канальных транзистора 10 и 11, которые, в свою очередь, обеспечивают разделение тока на четыре равновеликие (одинаковые) составляющие, а также нагрузочные резисторы 12 и 13, функционально служащие нагрузками ключевому транзистору 10 и ключевому транзистору 9 соответственно. Истоки ключевого транзистора 6 и ключевого транзистора 7 соединены между собой и с выходной шиной 3 (функционально являющейся и общей шиной), а их стоки соединены с шиной питания 14 и шиной земли 3 соответственно. Затвор ключевого транзистора 6, сток управляющего транзистора 10 и вход логического элемента И-НЕ 5 через нагрузочный резистор 12 подключены к шине питания 14, а затвор ключевого транзистора 7, исток управляющего транзистора 8 и вход логического элемента ИЛИ-НЕ 4 через нагрузочный резистор 13 подключены к шине земли 3. При этом затвор управляющего транзистора 10 соединен с шиной земли 15, а его исток - с выходной шиной 3, а затвор управляющего транзистора 8 соединен с шиной питания 14, а его сток - с упомянутой выходной шиной 3. Стоки выходных транзисторов 1 и 2 соединены между собой и с выходной шиной 3, а их истоки соединены с шиной питания 14 и шиной земли 3 соответственно, затвор транзистора 1 и сток транзистора 11 соединены и подключены к выходу логического элемента ИЛИ-НЕ 4, а затвор транзистора 2 и сток транзистора 9 соединены и подключены к выходу логического элемента И-НЕ 5, при этом истоки транзисторов 11 и 9 подключены к выходной шине 3, а их затворы к шине земли 15 и шине питания 14 соответственно. Входы логических элементов ИЛИ-НЕ 4 и И-НЕ 5 соединены между собой и с входной шиной 16.

Выходной каскад для КМОП микросхем с устройством защиты от электростатических разрядов работает следующим образом.

Основная функция устройства защиты состоит в ограничении напряжения на затворах выходных МОП элементов путем переключения разрядного тока из выходной цепи в шины питания и земли. При нормальном режиме работы (при рабочем напряжении) информационный сигнал проходит от входной шины на входы логических элементов ИЛИ-НЕ и И-НЕ, при этом устройство защиты не работает, а логические элементы ИЛИ-НЕ и И-НЕ функционируют как инверторы входного логического сигнала. При возникновении на выходе электростатического разряда положительной полярности втекающий ток открывает p-канальные управляющие транзисторы 8 и 9. На выходе элемента ИЛИ-НЕ и на затворе p-канального выходного транзистора 1 устанавливается низкий логический уровень, а на выходе элемента И-НЕ и на затворе n-канального выходного транзистора - высокий. Выходные транзисторы 1 и 2 и ключевые транзисторы 6 и 7 открыты. При возникновении электростатического разряда отрицательной полярности вытекающий ток открывает n-канальные управляющие транзисторы 10 и 11. На выходе элемента И-НЕ и на затворе n-канального выходного транзистора 2 устанавливается низкий логический уровень, а на выходе элемента ИЛИ-НЕ и на затворе p-канального выходного транзистора - высокий. Выходные транзисторы 1 и 2 и ключевые транзисторы 6 и 7 открыты. Таким образом, при возникновении ЭСР любой полярности на выходной шине 3 происходит разделение разрядного тока на четыре равновеликие составляющие (на одинаковые четыре плеча) и функционально обеспечивается протекание разрядного тока по двум выходным транзисторам 1 и 2 и по двум ключевым транзисторам 6 и 7 одновременно, что ведет к уменьшению вдвое сопротивления в цепи разрядного тока и дает возможность использовать в устройстве защиты менее мощные ключевые транзисторы и, соответственно, уменьшить его массогабаритные характеристики в целом.

Изобретение планируется использовать в быстродействующих КМОП микросхемах для систем связи. Техническое решение позволяет уменьшить выходную емкость выхода микросхемы на 40% и площадь выходного формирователя на 25%. Количественные оценки показывают, что поставленная задача решена.

Источники информации

1. Патент Франции №2323232.

2. Патент Великобритании №1305391.

3. Патент РФ №2308146 - прототип.

Выходной каскад для КМОП микросхем с устройством защиты от электростатических разрядов, содержащий два ключевых транзистора, которые обеспечивают протекание разрядного тока большой величины, два управляющих транзистора n-канальных и p-канальных, два нагрузочных резистора, шину питания и шину земли, отличающийся тем, что дополнительно введены два логических элемента ИЛИ-НЕ и И-НЕ, два выходных транзистора, два управляющих транзистора, причем один из них управляющий n-канальный транзистор истоком подключен к выходной шине, затвором - к шине земли, а стоком - к затвору выходного p-канального транзистора, в свою очередь, другой управляющий p-канальный транзистор истоком подключен к выходной шине, затвором - к шине питания, а стоком - к затвору выходного n-канального транзистора, а также затвор ключевого n-канального транзистора соединен с входом логического элемента И-НЕ, а затвор ключевого p-канального транзистора соединен с входом логического элемента ИЛИ-НЕ.