Результат интеллектуальной деятельности: К-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "МАКСИМУМ"

Вид РИД

Изобретение

Предлагаемое изобретение относится к области вычислительной техники, автоматики, связи и может использоваться в цифровых вычислительных структурах, системах автоматического управления, передачи и обработки цифровой информации и т.п.

В различных аналого-цифровых вычислительных и управляющих устройствах широко используются транзисторные каскады преобразования входных логических переменных (токов), реализованные на основе токовых зеркал [1-14, 18, 19]. Данные функциональные узлы используются, например, во входных каскадах операционных преобразователей сигналов с так называемой «токовой отрицательной обратной связью» [1-14], а также в качестве самостоятельных нелинейных преобразователей входных токов без цепей обратной связи [9, 18, 19], реализующих функцию логической обработки входных токовых переменных.

В работе [15], а также монографиях соавтора настоящей заявки [16-17] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока. Заявляемое устройство относится к этому типу логических элементов.

Ближайшим прототипом заявляемого устройства является логический элемент, представленный в патентной заявке US 2004/227477, структура которого присутствует во многих других патентах [1-14, 18, 19], в т.ч. JP 2004/328427. Он содержит первый 1 и второй 2 логические входы устройства, выход 3 устройства, первый 4 вспомогательный транзистор, база которого подключена к первому 5 источнику напряжения смещения, второй 6 вспомогательный транзистор другого типа проводимости, база которого подключена ко второму 7 источнику напряжения смещения, причем эмиттеры первого 4 и второго 6 вспомогательных транзисторов объединены, первое 8 токовое зеркало, согласованное с первой 9 шиной источника питания, вход которого соединен с первым 1 логическим входом устройства, второе 10 токовое зеркало, согласованное с первой 9 шиной источника питания, вход которого подключен ко второму 2 логическому входу устройства, третье 11 и четвертое 12 токовые зеркала, согласованные со второй 13 шиной источника питания, первый 14 и второй 15 согласующие транзисторы, базы которых связаны с соответствующими третьим 16 и четвертым 17 источниками напряжения смещения, причем первый 18 токовый выход второго 10 токового зеркала соединен с объединенными эмиттерами первого 4 и второго 6 вспомогательных транзисторов.

Существенный недостаток известного устройства состоит в том, что он не реализует функцию «максимум» двух многозначных входных переменных (x1, x2), соответствующих многоуровневым значениям входных токов I1, I2. Это не позволяет на его основе создать полный базис средств вычислительной техники, функционирующих на принципах преобразования многозначных токовых сигналов.

Основная задача предлагаемого изобретения состоит в создании логического элемента, обеспечивающего реализацию функции «максимум» двух многозначных переменных (x1, x2), в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов. В конечном итоге это позволяет повысить быстродействие устройств преобразования информации и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [16-17].

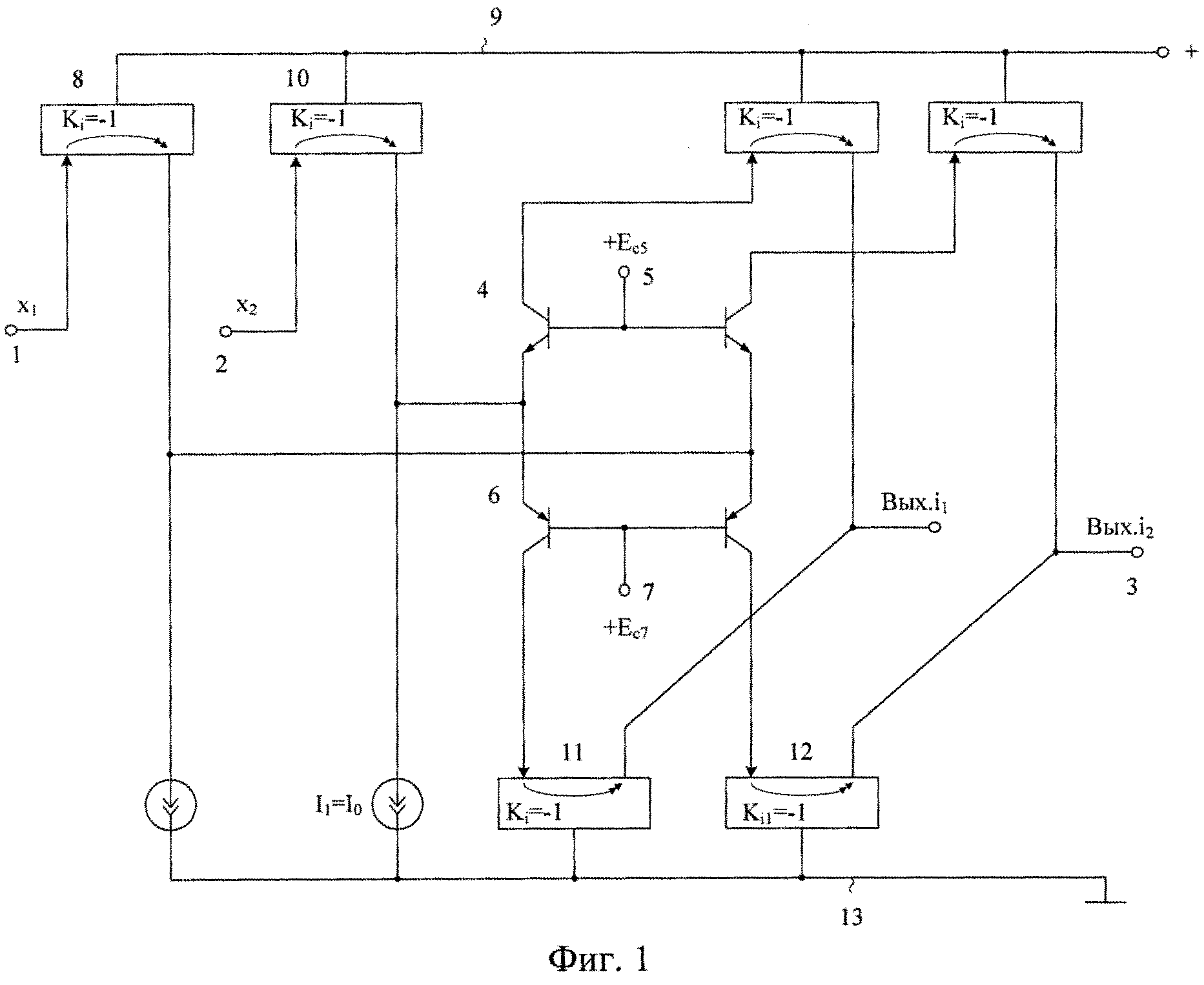

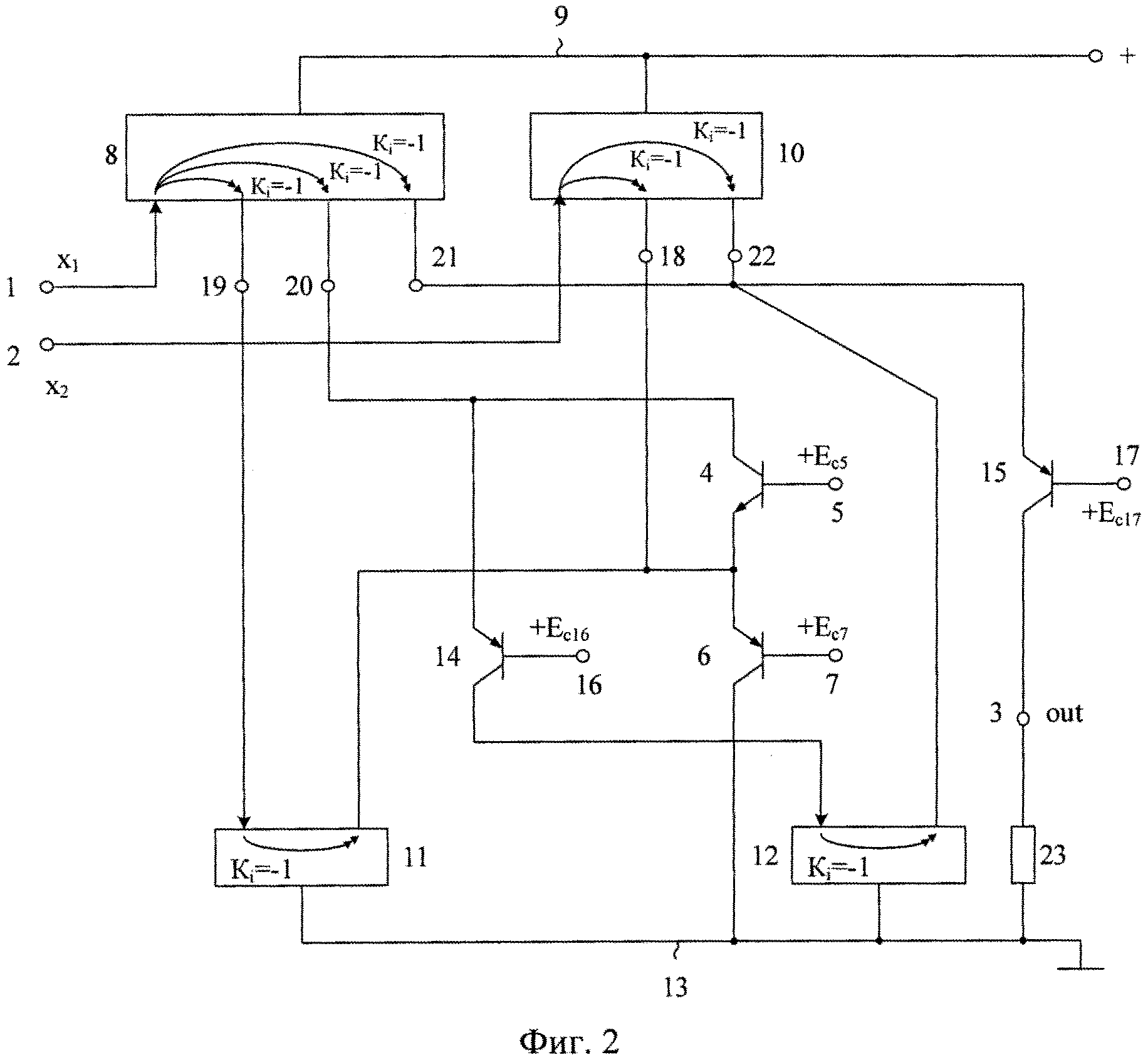

Поставленная задача решается тем, что в известном логическом элементе (фиг. 1), содержащем первый 1 и второй 2 логические входы устройства, выход 3 устройства, первый 4 вспомогательный транзистор, база которого подключена к первому 5 источнику напряжения смещения, второй 6 вспомогательный транзистор другого типа проводимости, база которого подключена ко второму 7 источнику напряжения смещения, причем эмиттеры первого 4 и второго 6 вспомогательных транзисторов объединены, первое 8 токовое зеркало, согласованное с первой 9 шиной источника питания, вход которого соединен с первым 1 логическим входом устройства, второе 10 токовое зеркало, согласованное с первой 9 шиной источника питания, вход которого подключен ко второму 2 логическому входу устройства, третье 11 и четвертое 12 токовые зеркала, согласованные со второй 13 шиной источника питания, первый 14 и второй 15 согласующие транзисторы, базы которых связаны с соответствующими третьим 16 и четвертым 17 источниками напряжения смещения, причем первый 18 токовый выход второго 10 токового зеркала соединен с объединенными эмиттерами первого 4 и второго 6 вспомогательных транзисторов, предусмотрены новые элементы и связи - первый 19 токовый выход первого 8 токового зеркала соединен с токовым входом третьего 11 токового зеркала, выход которого соединен с объединенными эмиттерами первого 4 и второго 6 вспомогательных транзисторов, второй 20 токовый выход первого 8 токового зеркала подключен к коллектору первого 4 вспомогательного транзистора и эмиттеру первого 14 согласующего транзистора, коллектор которого связан со входом четвертого 12 токового зеркала, третий 21 токовый выход первого 8 токового зеркала соединен со вторым 22 токовым выходом второго 10 токового зеркала, подключен к эмиттеру второго 15 согласующего транзистора и связан с токовым выходом четвертого 12 токового зеркала, причем коллектор второго 6 вспомогательного транзистора связан со второй 13 шиной источника питания, а коллектор второго 15 согласующего транзистора соединен с выходом 3 устройства.

Схема известного устройства показана на фиг. 1. На фиг. 2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

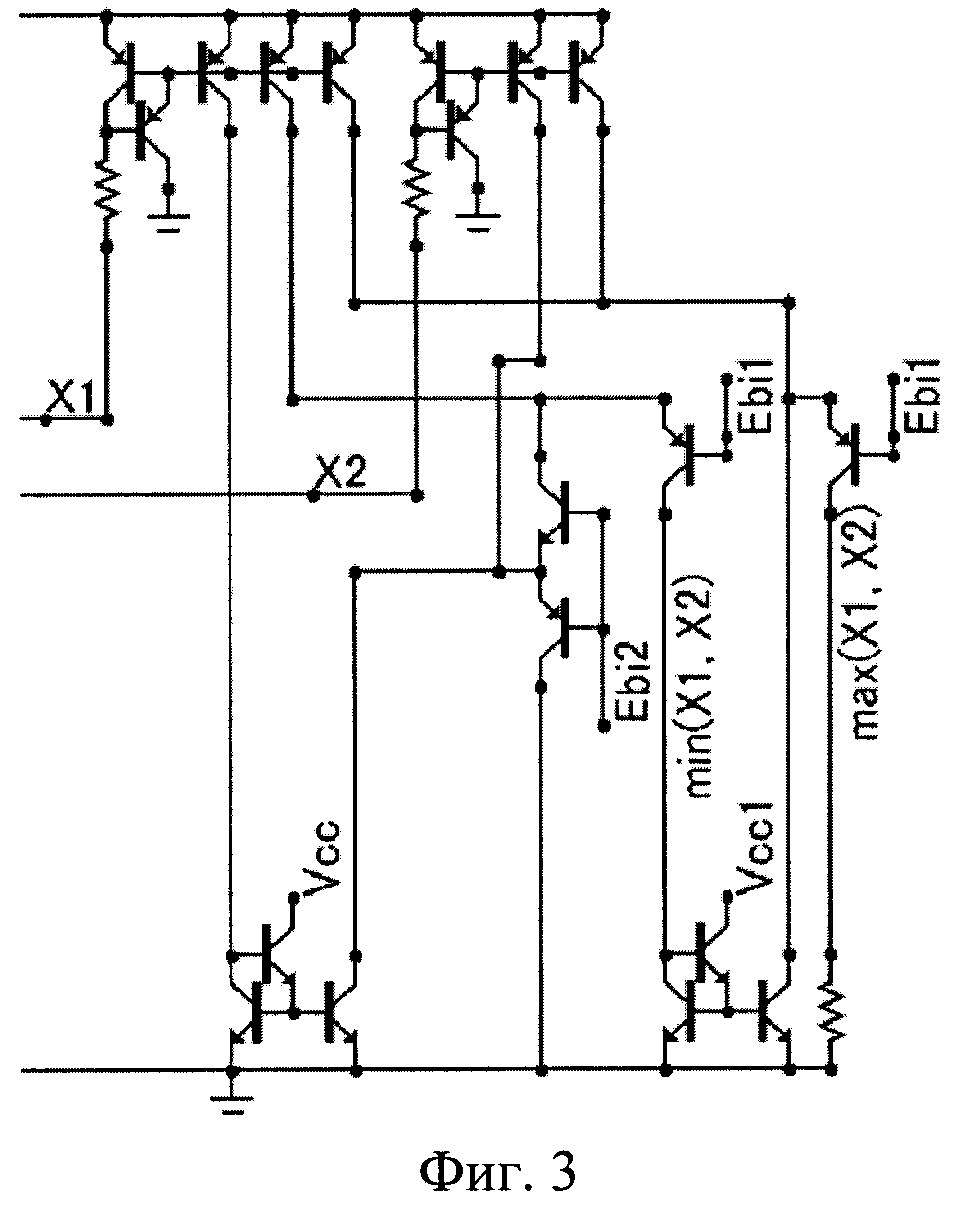

На фиг. 3 представлена принципиальная схема заявляемого устройства фиг. 2 в среде компьютерного моделирования MC9.

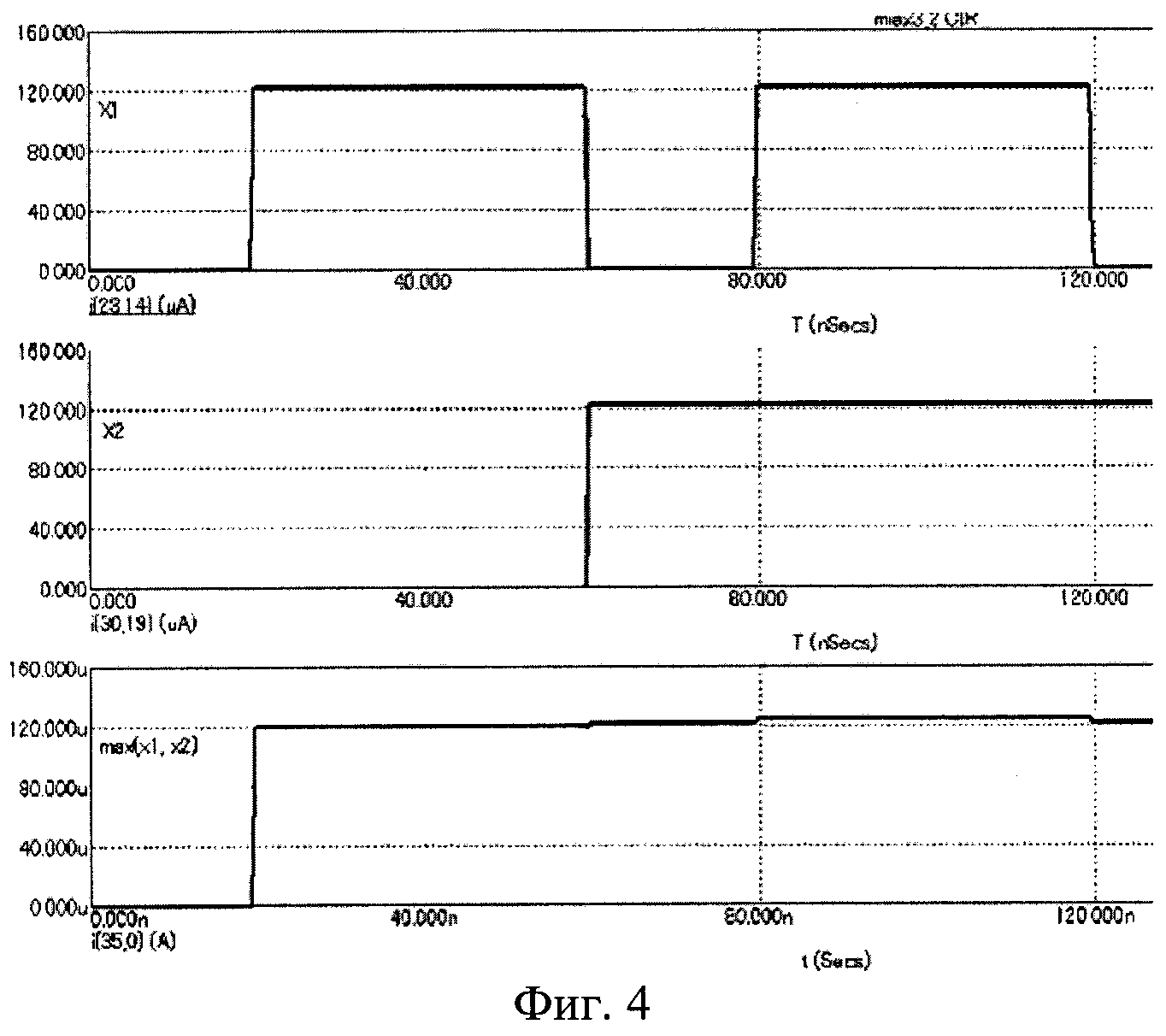

На фиг. 4 приведены временные диаграммы работы заявляемого устройства фиг. 3 для двоичных входных сигналов x1, x2.

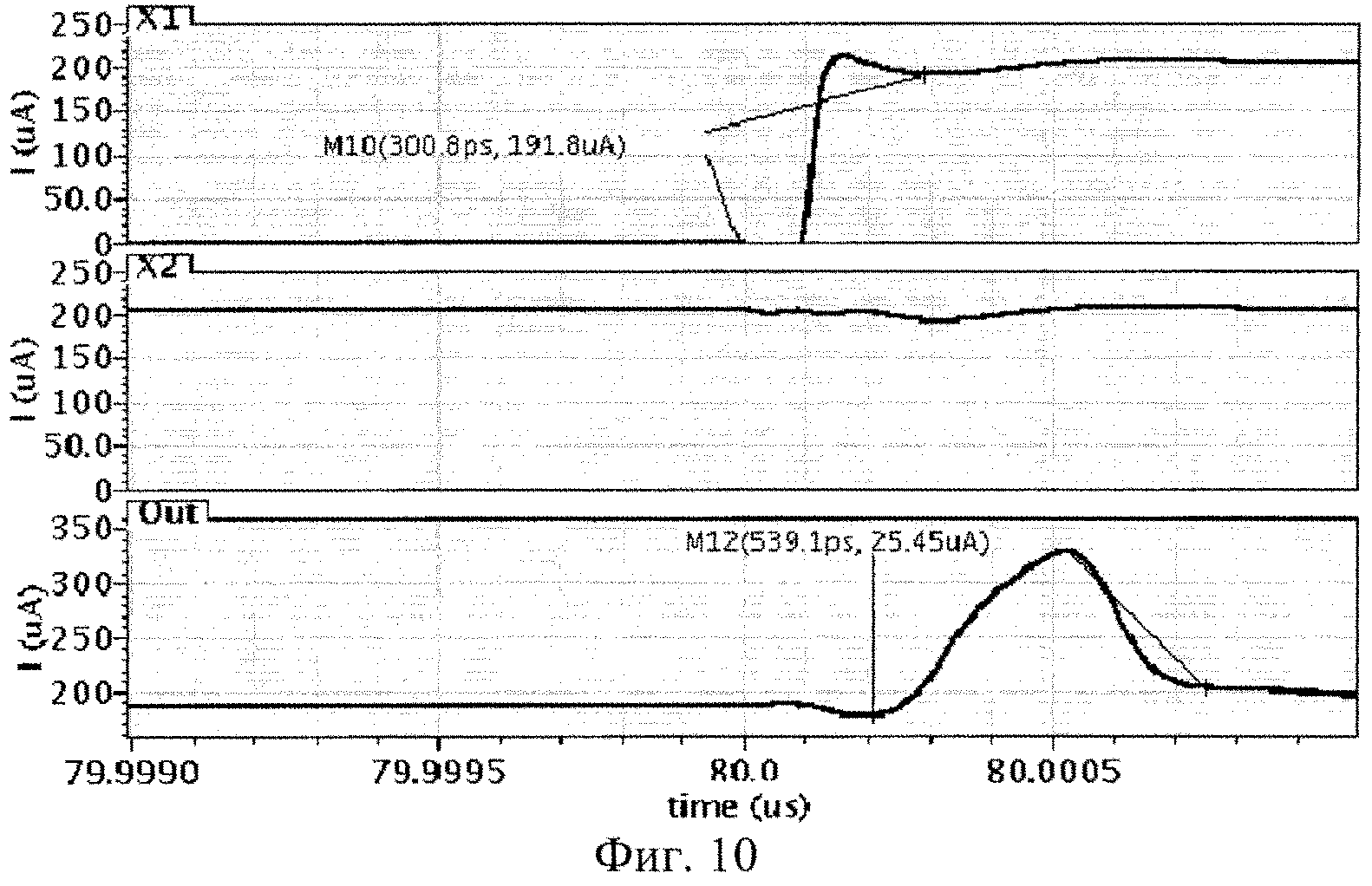

На фиг. 5 представлены временные диаграммы работы заявляемого устройства фиг. 3 для троичных входных сигналов x1, x2.

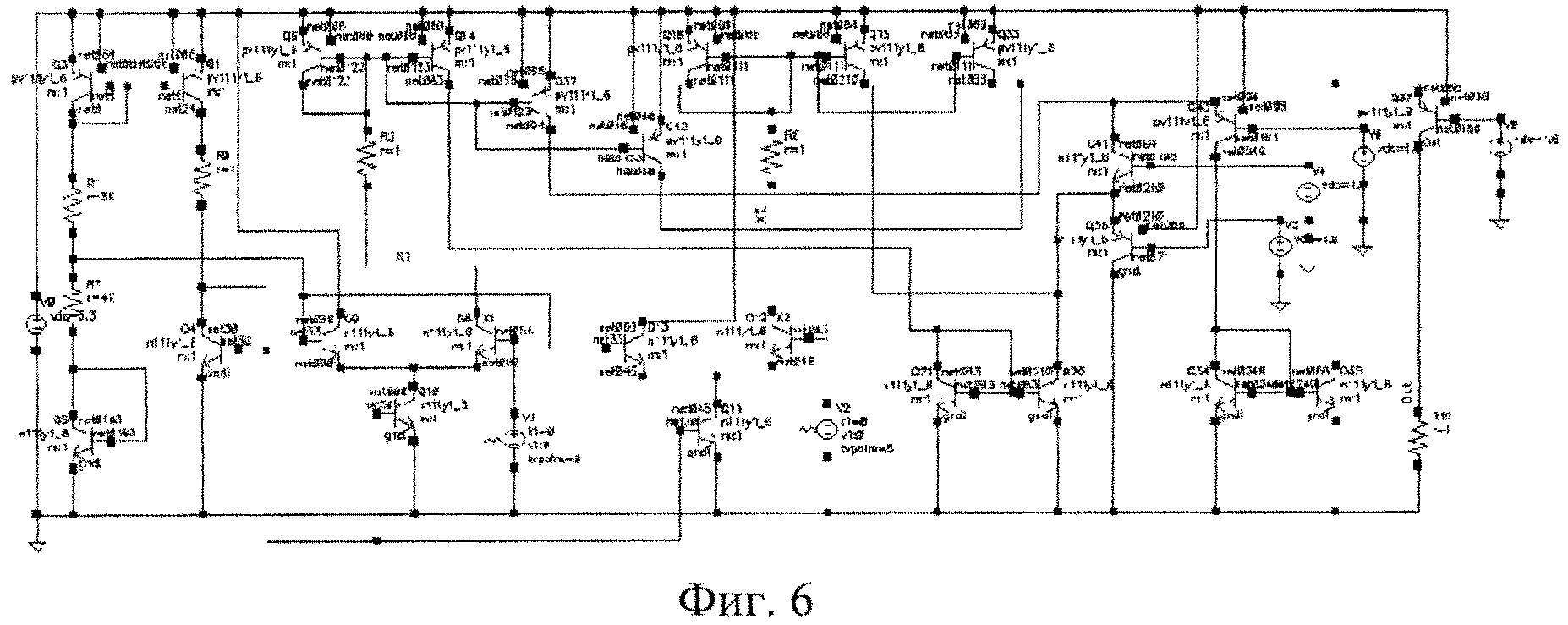

На фиг. 6 представлена принципиальная схема фиг. 2 в другой среде компьютерного моделирования Cadence Virtuoso (модели транзисторов npn vpnp NJV) при работе с двоичными входными сигналами, которые моделируются вспомогательными дифференциальными каскадами. При этом для измерения входных токовых координат в схему введены вспомогательные измерительные резисторы.

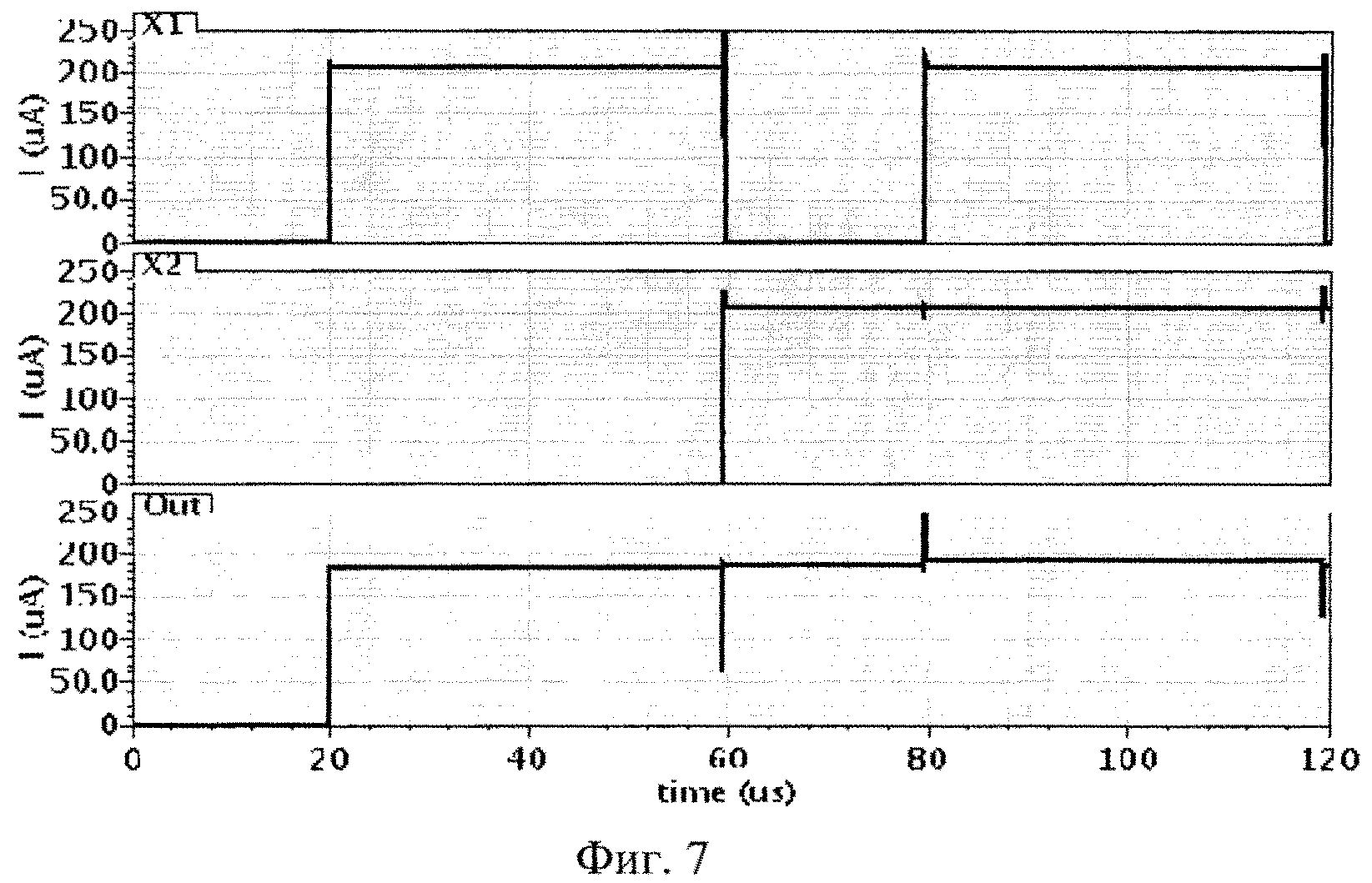

На фиг. 7 показаны осциллограммы входных и выходных двоичных сигналов.

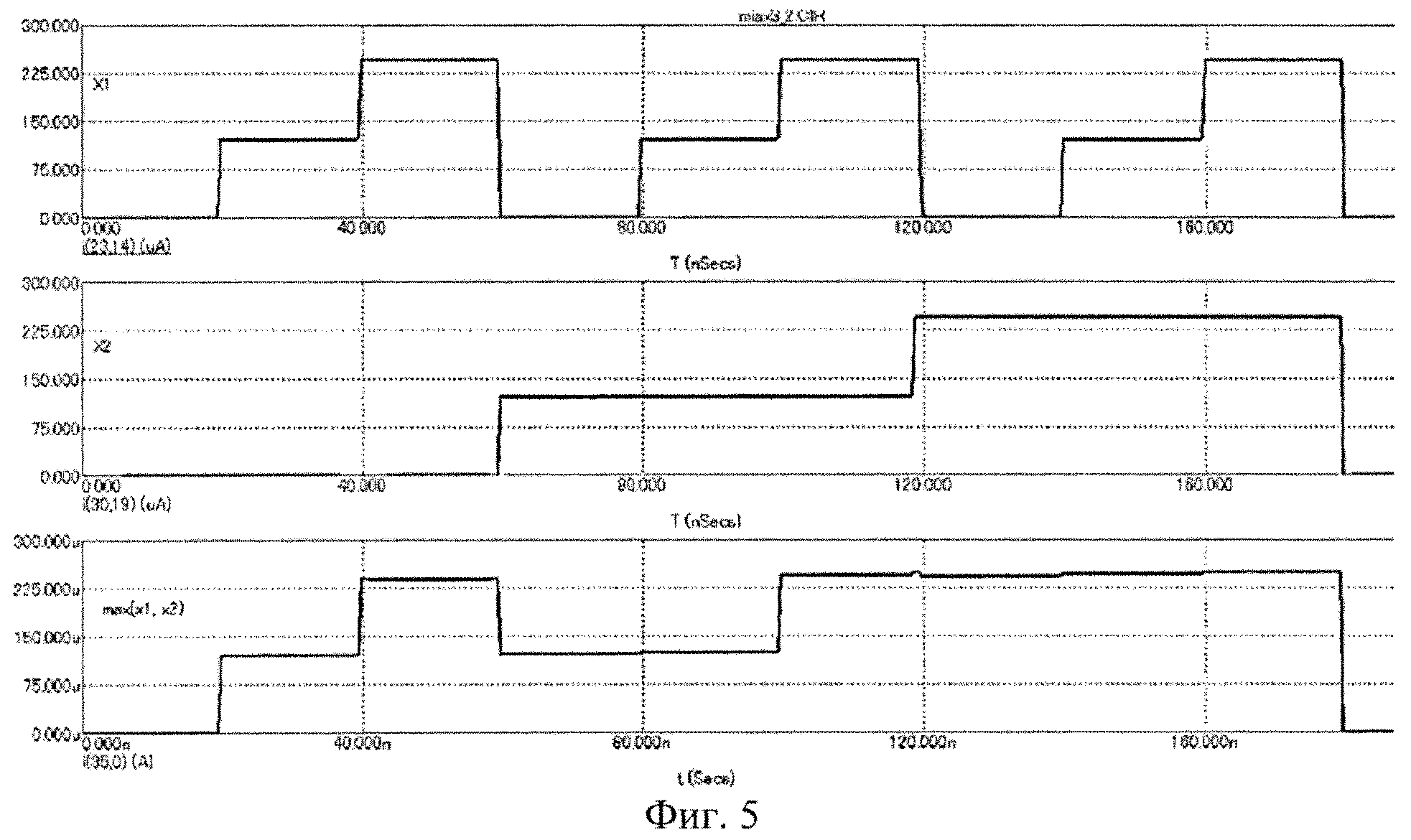

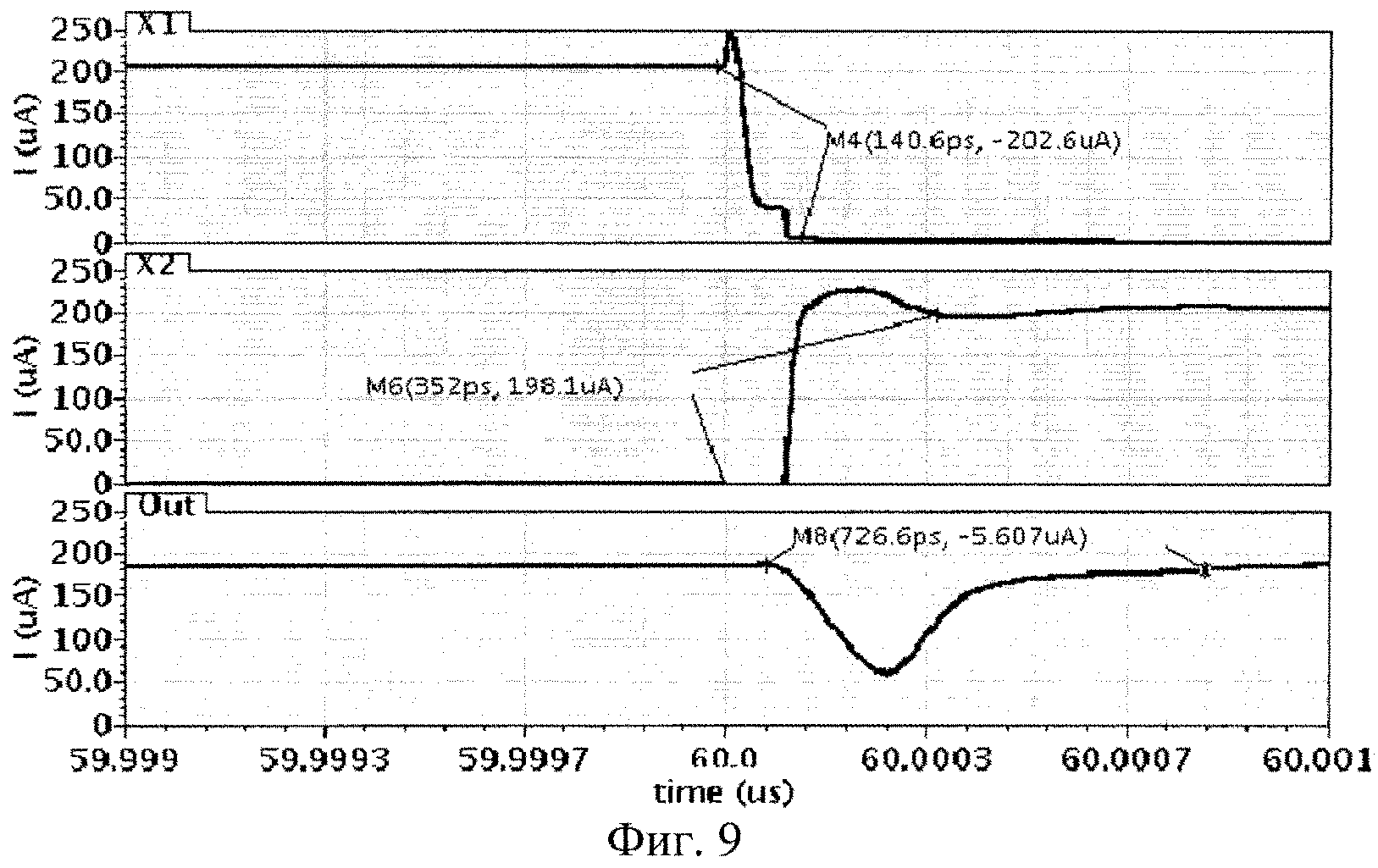

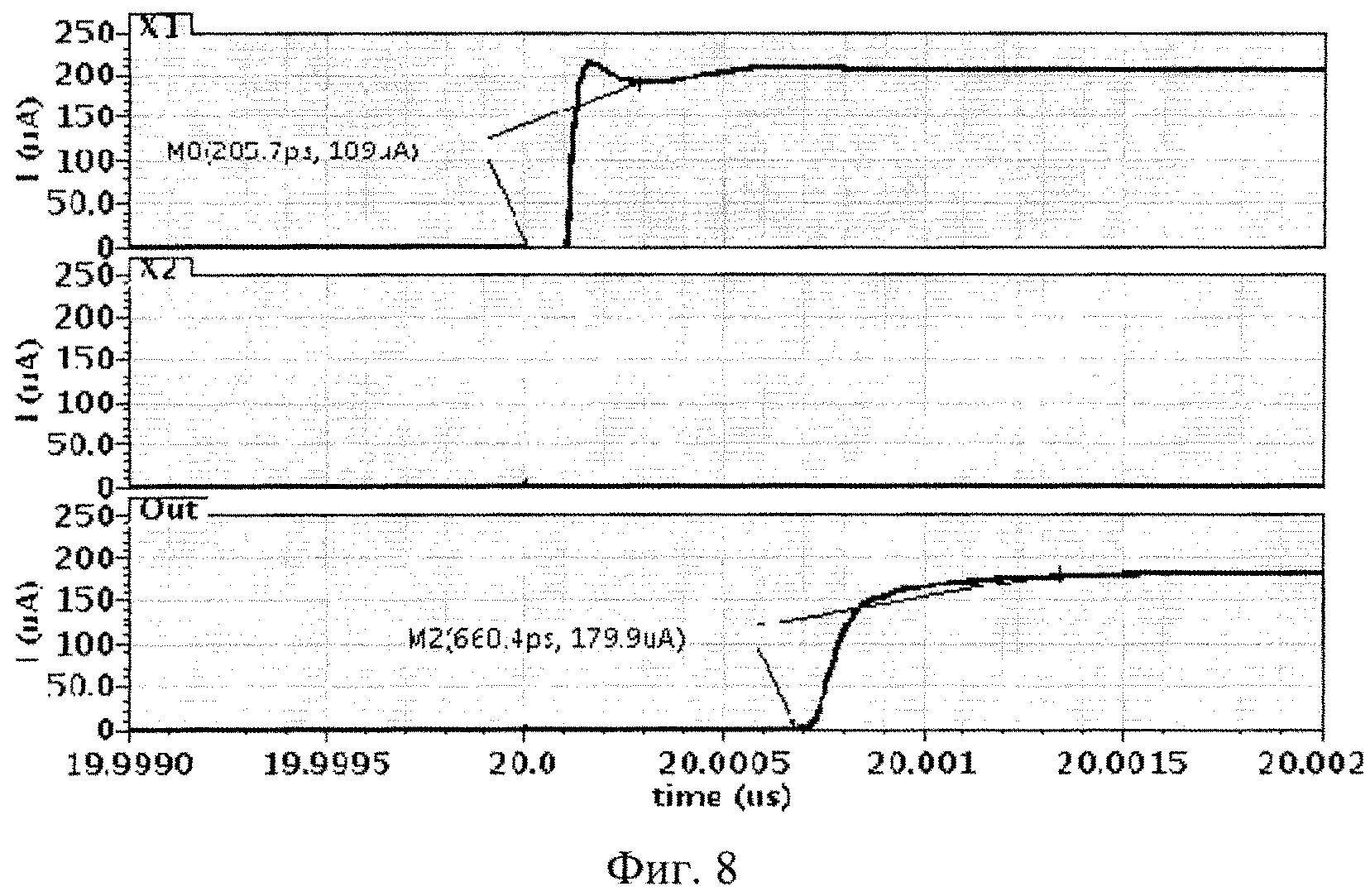

На фиг. 8, 9 и 10 показаны временные диаграммы работы устройства фиг. 6, характеризующие задержки входных и выходных двоичных сигналов.

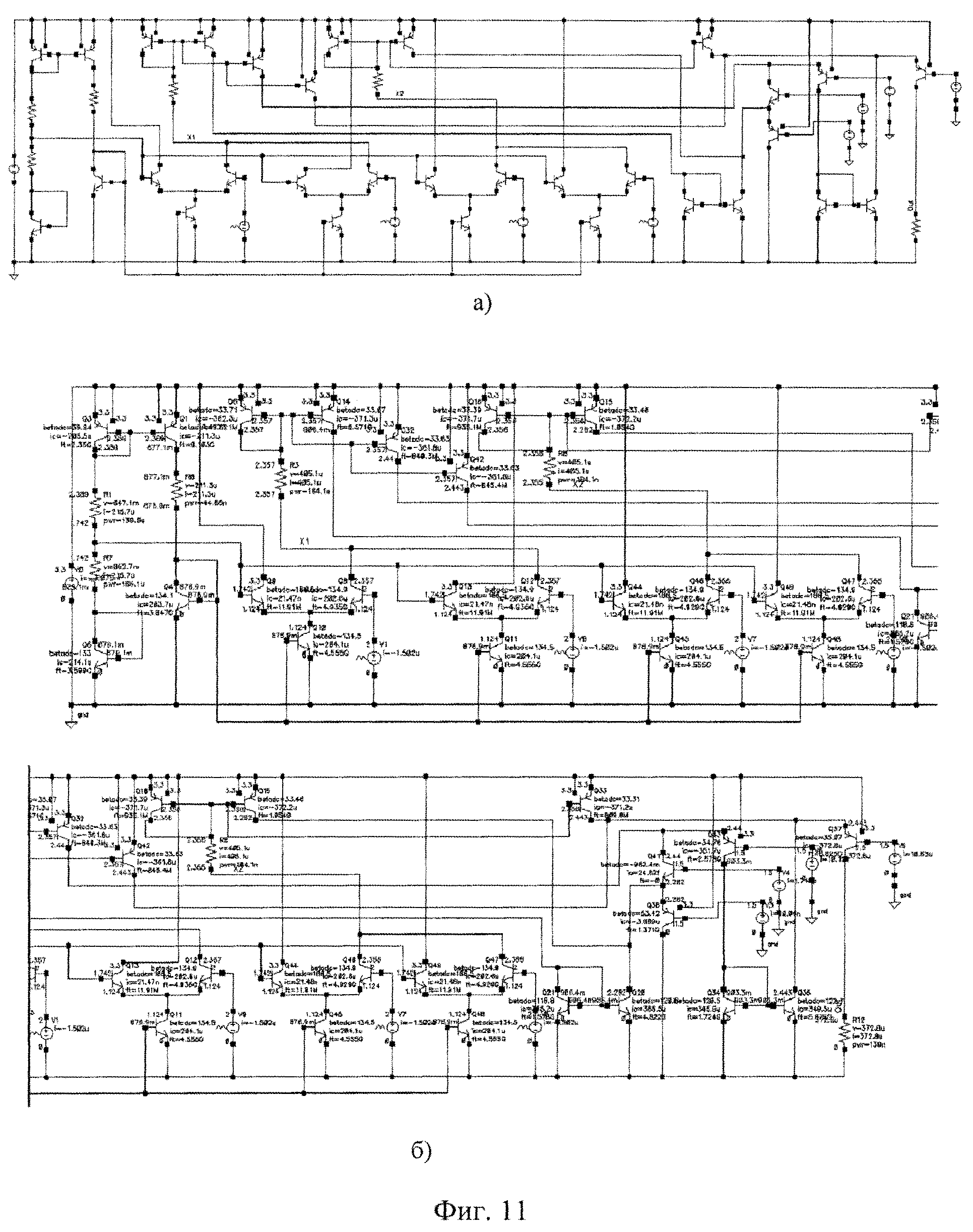

На фиг. 11 представлена принципиальная схема заявляемого устройства фиг. 2 при работе с троичными входными сигналами в среде компьютерного моделирования Cadence Virtuoso (модели транзисторов npn vpnp NJV), которые моделируются дифференциальными каскадами. При этом для измерения входных токовых координат в схему введены вспомогательные измерительные резисторы.

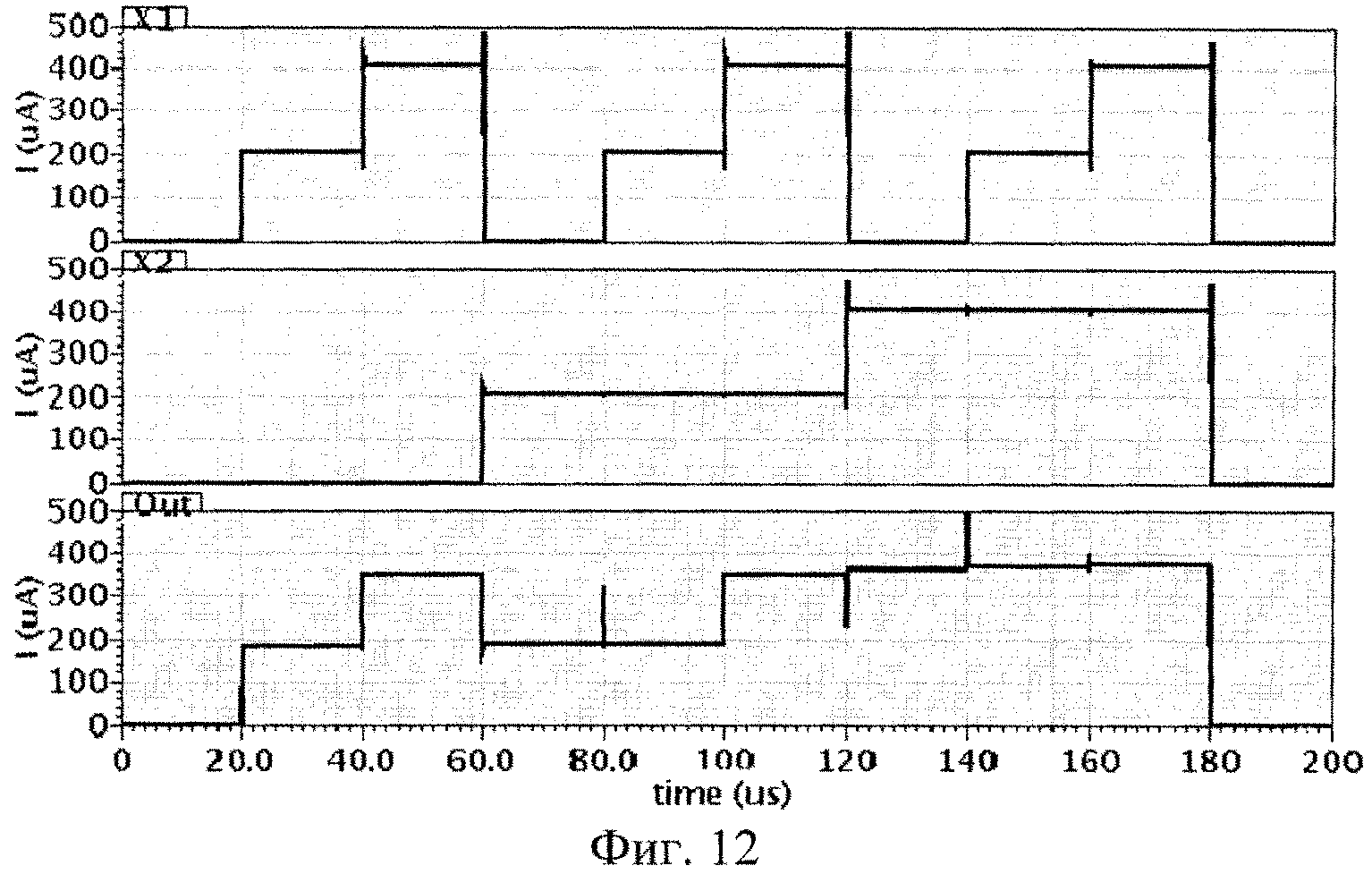

На фиг. 12 показаны осциллограммы входных и выходных троичных сигналов в схеме фиг. 11.

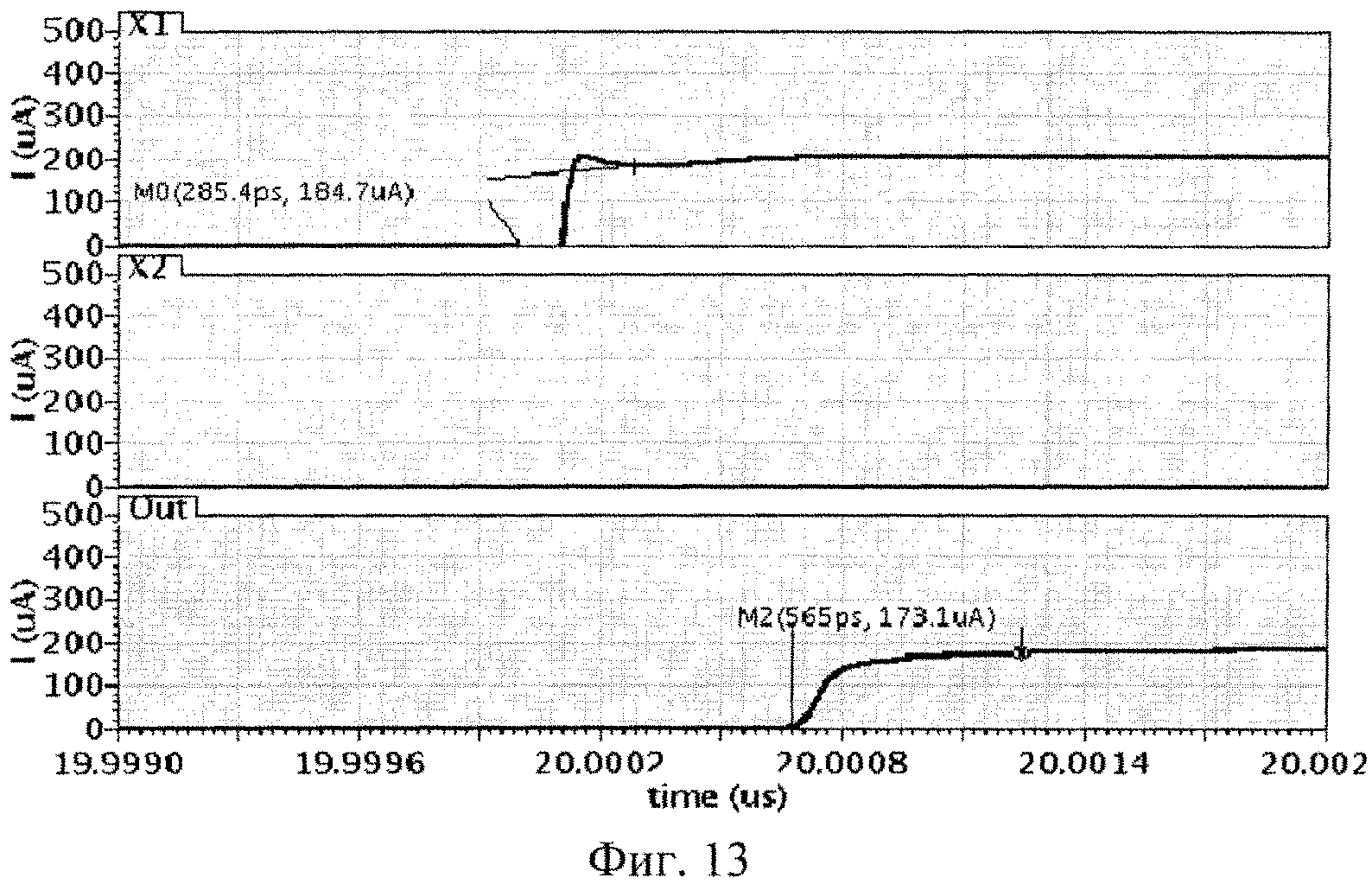

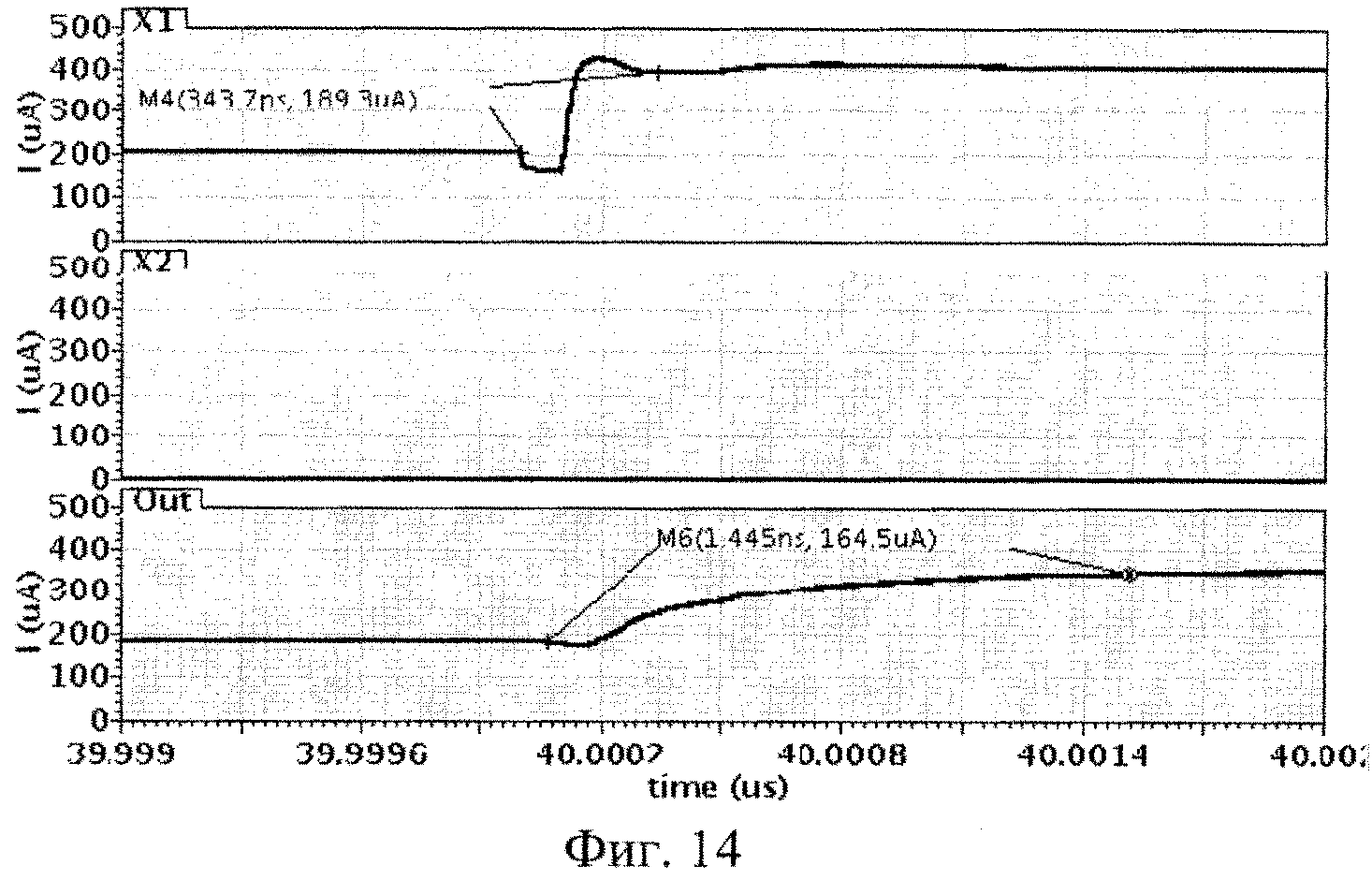

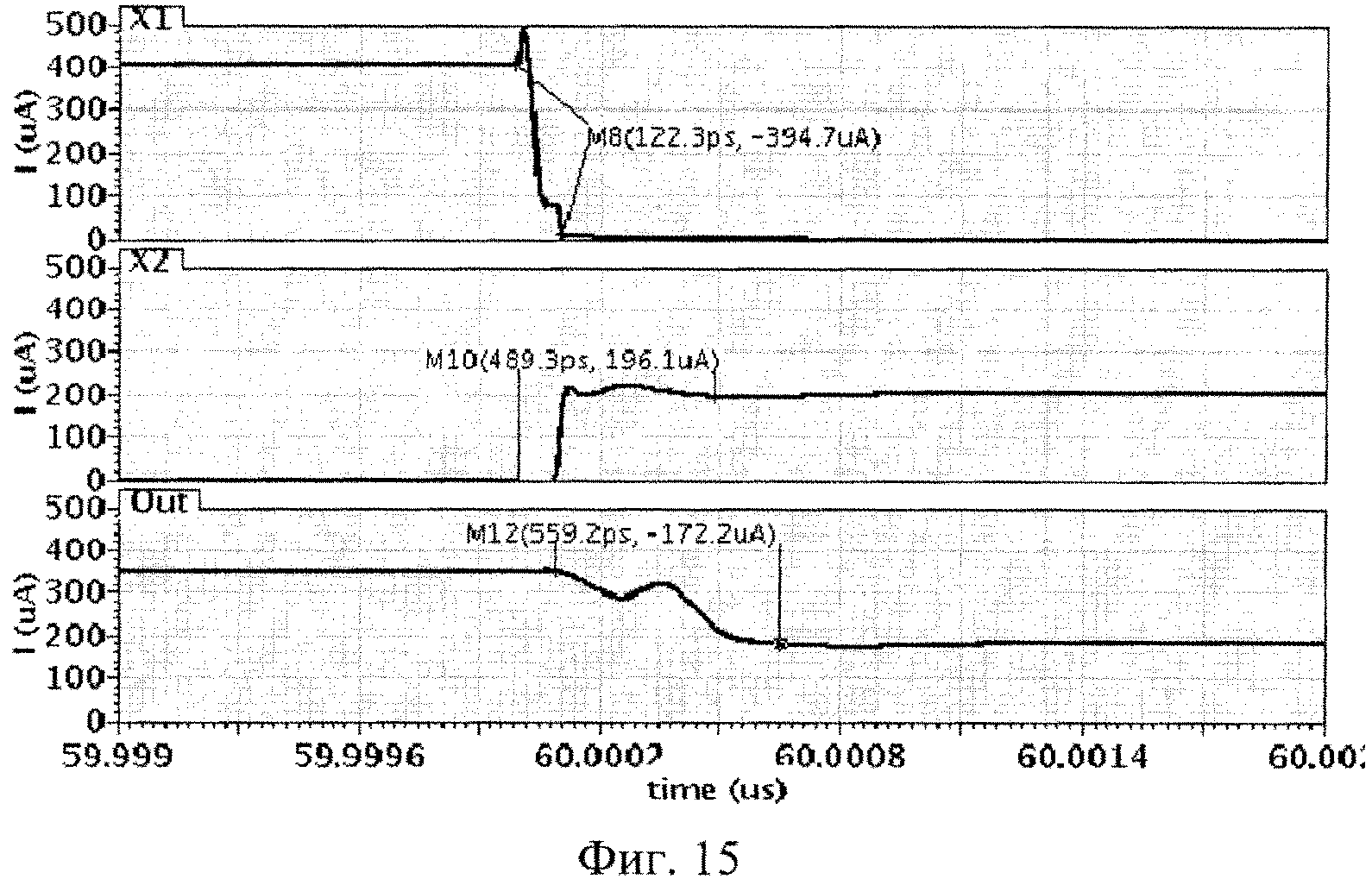

На фиг. 13, 14 и 15 показаны временные диаграммы работы устройства фиг. 11, характеризующие задержки входных и выходных троичных сигналов.

k-значный логический элемент «максимум» фиг. 2 содержит первый 1 и второй 2 логические входы устройства, выход 3 устройства, первый 4 вспомогательный транзистор, база которого подключена к первому 5 источнику напряжения смещения, второй 6 вспомогательный транзистор другого типа проводимости, база которого подключена ко второму 7 источнику напряжения смещения, причем эмиттеры первого 4 и второго 6 вспомогательных транзисторов объединены, первое 8 токовое зеркало, согласованное с первой 9 шиной источника питания, вход которого соединен с первым 1 логическим входом устройства, второе 10 токовое зеркало, согласованное с первой 9 шиной источника питания, вход которого подключен ко второму 2 логическому входу устройства, третье 11 и четвертое 12 токовые зеркала, согласованные со второй 13 шиной источника питания, первый 14 и второй 15 согласующие транзисторы, базы которых связаны с соответствующими третьим 16 и четвертым 17 источниками напряжения смещения, причем первый 18 токовый выход второго 10 токового зеркала соединен с объединенными эмиттерами первого 4 и второго 6 вспомогательных транзисторов. Первый 19 токовый выход первого 8 токового зеркала соединен с токовым входом третьего 11 токового зеркала, выход которого соединен с объединенными эмиттерами первого 4 и второго 6 вспомогательных транзисторов, второй 20 токовый выход первого 8 токового зеркала подключен к коллектору первого 4 вспомогательного транзистора и эмиттеру первого 14 согласующего транзистора, коллектор которого связан со входом четвертого 12 токового зеркала, третий 21 токовый выход первого 8 токового зеркала соединен со вторым 22 токовым выходом второго 10 токового зеркала, подключен к эмиттеру второго 15 согласующего транзистора и связан с токовым выходом четвертого 12 токового зеркала, причем коллектор второго 6 вспомогательного транзистора связан со второй 13 шиной источника питания, а коллектор второго 15 согласующего транзистора соединен с выходом 3 устройства. Двухполюсник 23 моделирует свойства нагрузки, подключаемой к выходу 3 устройства.

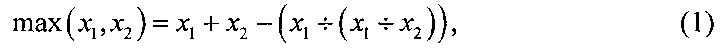

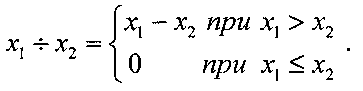

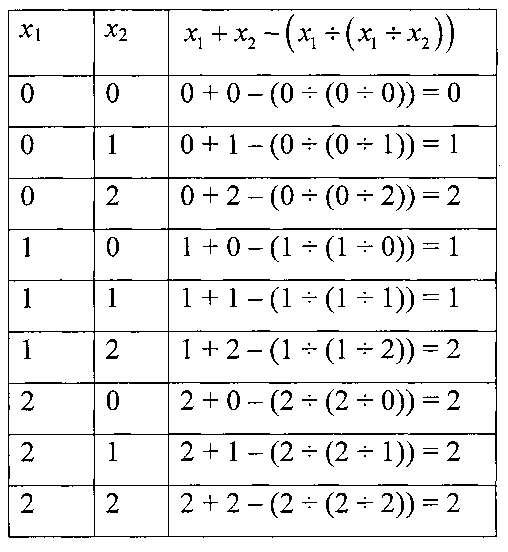

Рассмотрим работу устройства фиг. 2. Устройство реализует логическую функцию mах (x1, x2), представление которой в трехзначной логике с помощью линейной алгебры имеет следующий вид:

где

Таблица истинности реализуемой логической функции для трехзначного случая приведена ниже:

Как видно из таблицы, значения результата полностью совпадают со значениями трехзначной функции max(x1,x2).

Результат операции является суммой трех слагаемых. Первые два слагаемых представляют собой входные переменные, третье слагаемое представляет собой некоторую операцию над входными переменными.

Реализация указанной выше операции происходит следующим образом. Сигналы, соответствующие входным переменным x1 и x2 в виде квантов втекающего тока (т.е. в виде -x1 и -x2), через входы 1 и 2 поступают на входы первого 8 и второго 10 токовых зеркал соответственно. Сигнал x1 размножается и в виде квантов вытекающего тока (т.е. в виде +x1) снимается с выходов 19, 20 и 21 токового зеркала 8. Аналогично, сигнал x2 также в виде квантов вытекающего тока (т.е. в виде +x2) снимается с выходов 18 и 22 второго токового зеркала 10.

Сигнал x1 с выхода 19 токового зеркала 8 с помощью третьего токового зеркала 11 инвертируется по знаку (т.е. преобразуется в квант втекающего тока или -x1) и монтажно объединяется с выходным сигналом +x2 с выхода 18 второго токового зеркала 10. При этом в точке объединения формируется разностный сигнал x2-x1, подаваемый на объединенные выводы эмиттеров транзисторов 4 и 6, режимы работы которых задаются источниками напряжения смещения 5 и 7 (Ec5 и Ec7) соответственно.

Если разность квантов тока положительна (т.е. x2-x1>0), то транзистор 4 закрыт, а транзистор 6 открыт, разностный вытекающий ток через транзистор 6 уходит на «землю».

Если разность квантов тока неположительна (т.е. x2-x1≤0), то разностный ток равен нулю, транзистор 4 открыт и через него из сигнала x1 с выхода 20 первого токового зеркала 10 вычитается сигнал разности - (x1-x2), снимаемый с выхода третьего токового зеркала 11, тем самым реализуется разность x1÷(x1÷x2). Разностный сигнал поступает на эмиттер транзистора 14. Режим работы этого транзистора задается напряжением смещения на его базе, задаваемым источником смещения Ec16.

При x1÷(x1÷x2)>0 разностный сигнал в виде кванта вытекающего тока с коллектора транзистора 14 подается на вход четвертого токового зеркала 12, с выхода которого в виде кванта втекающего тока монтажно объединяется с квантами вытекающих токов x1 с выхода 21 первого токового зеркала 8 и с выхода 22 второго токового зеркала 10, при этом в точке их соединения образуется сигнал, соответствующий выражению (1).

Полученный сигнал в виде кванта тока поступает на эмиттер транзистора 15. Режим работы этого транзистора задается источником напряжения смещения 17. С коллектора транзистора 15 выходной сигнал поступает во внешнюю цепь. Резистор 23 служит для определения наличия кванта тока в выходной цепи в процессе экспериментальных исследований схемы.

Как видно из приведенного описания реализация логической функции max(x1,x2) в схеме фиг. 2 производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Показанные на фиг. 4, 5, 7, 12 результаты моделирования в разных средах компьютерного моделирования и на разных типах применяемых интегральных транзисторов подтверждают указанные свойства заявляемой схемы.

Таким образом, рассмотренное схемотехническое решение k-значного логического элемента «максимум» характеризуется многозначным состоянием внутренних сигналов и сигналов на его токовых входах и выходах, что может быть положено в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 8159304, fig. 5.

2. Патент US №5977829, fig. 1.

3. Патент US №5789982, fig. 2.

4. Патент US №5140282.

5. Патент US №6624701, fig. 4.

6. Патент US №6529078.

7. Патент US №5734294.

8. Патент US №5557220.

9. Патент US №6624701.

10. Патент RU №2319296.

11. Патент RU №2436224.

12. Патент RU №2319296.

13. Патент RU №2321157.

14. Патент RU №2383099.

15. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С. 84-93.

16. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

17. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.

18. Патент US 6556075, fig. 2.

19. Патент US 6556075, fig. 6.

k-значный логический элемент «максимум», содержащий первый (1) и второй (2) логические входы устройства, выход (3) устройства, первый (4) вспомогательный транзистор, база которого подключена к первому (5) источнику напряжения смещения, второй (6) вспомогательный транзистор другого типа проводимости, база которого подключена ко второму (7) источнику напряжения смещения, причем эмиттеры первого (4) и второго (6) вспомогательных транзисторов объединены, первое (8) токовое зеркало, согласованное с первой (9) шиной источника питания, вход которого соединен с первым (1) логическим входом устройства, второе (10) токовое зеркало, согласованное с первой (9) шиной источника питания, вход которого подключен ко второму (2) логическому входу устройства, третье (11) и четвертое (12) токовые зеркала, согласованные со второй (13) шиной источника питания, первый (14) и второй (15) согласующие транзисторы, базы которых связаны с соответствующими третьим (16) и четвертым (17) источниками напряжения смещения, причем первый (18) токовый выход второго (10) токового зеркала соединен с объединенными эмиттерами первого (4) и второго (6) вспомогательных транзисторов, отличающийся тем, что первый (19) токовый выход первого (8) токового зеркала соединен с токовым входом третьего (11) токового зеркала, выход которого соединен с объединенными эмиттерами первого (4) и второго (6) вспомогательных транзисторов, второй (20) токовый выход первого (8) токового зеркала подключен к коллектору первого (4) вспомогательного транзистора и эмиттеру первого (14) согласующего транзистора, коллектор которого связан со входом четвертого (12) токового зеркала, третий (21) токовый выход первого (8) токового зеркала соединен со вторым (22) токовым выходом второго (10) токового зеркала, подключен к эмиттеру второго (15) согласующего транзистора и связан с токовым выходом четвертого (12) токового зеркала, причем коллектор второго (6) вспомогательного транзистора связан со второй (13) шиной источника питания, а коллектор второго (15) согласующего транзистора соединен с выходом (3) устройства.