Результат интеллектуальной деятельности: СПОСОБ ПОВЫШЕНИЯ НАДЕЖНОСТИ МИКРОЭВМ

Вид РИД

Изобретение

Изобретение относится к цифровой вычислительной технике и предназначено для решения задачи обнаружения случайных срывов процессора микроЭВМ с заданной программы функционирования, что может быть вызвано действием случайных помех.

Известен способ обнаружения случайных «блужданий» в микроЭВМ, представленный в [1].

Данный способ обнаружения случайных «блужданий» в микроЭВМ заключается в том, что программу работы процессора в виде блока из его машинных кодов первоначально размещают с какого-либо адреса запоминающего устройства программ, в котором затем в некотором чередующемся порядке располагают блоки, содержащие машинные коды данных, необходимых для исполнения рабочей программы, и блоки-ловушки случайных «блужданий» процессора, в которые после всего записывают массивы самых коротких машинных кодов одних и тех же команд для обнаружения возможных случайных «блужданий» и целенаправленной реакции на них.

Случайные «блуждания» процессора возникают тогда, когда он срывается с заданной программы функционирования, интерпретируя машинные коды данных как коды команд, а коды команд - как операнды или как коды их адресов. Полагается, что при таком блуждании с некоторой вероятностью процессор извлечет данные из блоков-ловушек и интерпретирует их как код команды. Предлагается заполнять блоки-ловушки массивами самых коротких машинных кодов одних и тех же команд, например, «Сброс» или «Безусловный переход к команде с адресом А», что позволит обнаружить факт наличия случайного блуждания процессора и автоматически вернуть его к началу рабочей программы или некоторой заданной точке А программы. При правильном функционировании процессора его обращение к блокам-ловушкам исключается, что обеспечивается в процессе разработки программы работы микроЭВМ.

При случайном срыве процессора с заданной программы функционирования невозможно предсказать точку его входа в запоминающее устройство программ. Можно лишь предположить, что такой точкой входа с равной вероятностью может быть любая ячейка запоминающего устройства программ.

Однако известно, что в составе команд любой микроЭВМ содержатся команды условных и безусловных переходов, а так же команды организации циклических процессов. Это приводит к тому, что при возникновении срыва процессора с заданной программы функционирования траектория его случайного «блуждания» может длительное время находиться в блоке кодов рабочей программы или в блоках кодов данных. Такие ситуации либо принципиально не могут быть определены данным способом обнаружения случайных «блужданий», либо будут обнаружены через значительные промежутки времени, в течение которых может быть выполнена последовательность команд с непредсказуемыми последствиями.

Наиболее близким по технической сути является широко известный способ повышения надежности микроЭВМ (например, [2]), заключающийся в том, что к n-разрядному основному (программному) запоминающему устройству микроЭВМ предварительно добавляют дополнительное однобитовое запоминающее устройство, которые в рабочем режиме образуют единое (n+1)-разрядное запоминающее устройство, затем в n-разрядные ячейки основного запоминающего устройства загружают программу работы процессора в виде машинных кодов, после чего в каждую однобитовую ячейку дополнительного запоминающего устройства записывают единицу или ноль, таким образом, чтобы сумма единичных значений в кодах каждой (n+1)-разрядной ячейки основного и дополнительного запоминающих устройств была бы четной, что в режиме работы при чтении данных из основного и дополнительного запоминающих устройств автоматически проверяют многовходовым сумматором по модулю 2, сигнал с выхода которого подают на вход прерывания процессора, который переходит на подпрограмму обработки прерывания в случае неверного чтения кодов из основного и дополнительного запоминающих устройств.

Данный способ, известный более как «контроль четности», повышает надежность функционирования микроЭВМ за счет оперативного обнаружения случайных и/или фиксированных единичных искажений данных, считываемых из основного и дополнительного запоминающих устройств.

Недостатком данного способа повышения надежности является невозможность обнаружения фактов возникновения случайных «блужданий» процессора микроЭВМ.

Изобретение направлено на расширение функциональных возможностей способа повышения надежности микроЭВМ за счет дополнительной возможности обнаружения факта возникновения случайных «блужданий» и адекватной реакции на них с минимальными аппаратными затратами.

Это достигается тем, что предварительно количество входов сумматора по модулю два увеличивают до (n+2), на (n+2) вход которого дополнительно подают единичный признак чтения кода команды, который в режиме работы автоматически формируется процессором микроЭВМ, а на этапе записи данных в дополнительное запоминающее устройство в каждый его бит записывают единицу или ноль, таким образом, чтобы в (n+1) битах дополнительного запоминающего устройства и основного запоминающего устройства, в ячейках которого содержатся коды команд, сумма единичных значений была бы нечетной, а в ячейках которого содержатся все остальные коды - четной, при этом в режиме правильной работы микроЭВМ и отсутствии «блужданий» при чтении из основного и дополнительного запоминающих устройств будет сохраняться четность (n+2) бит, одновременно поступающих на вход сумматора по модулю два.

Рассмотрим осуществление заявляемого способа повышения надежности микроЭВМ.

Процессор микроЭВМ при выполнении рабочей программы должен обладать способностью формировать единичный признак чтения кода команды при обращении к основному запоминающему устройству, аналогично тому, как этот признак (M1) формируется в широко известном микропроцессоре КР 580 ВМ 80А [3].

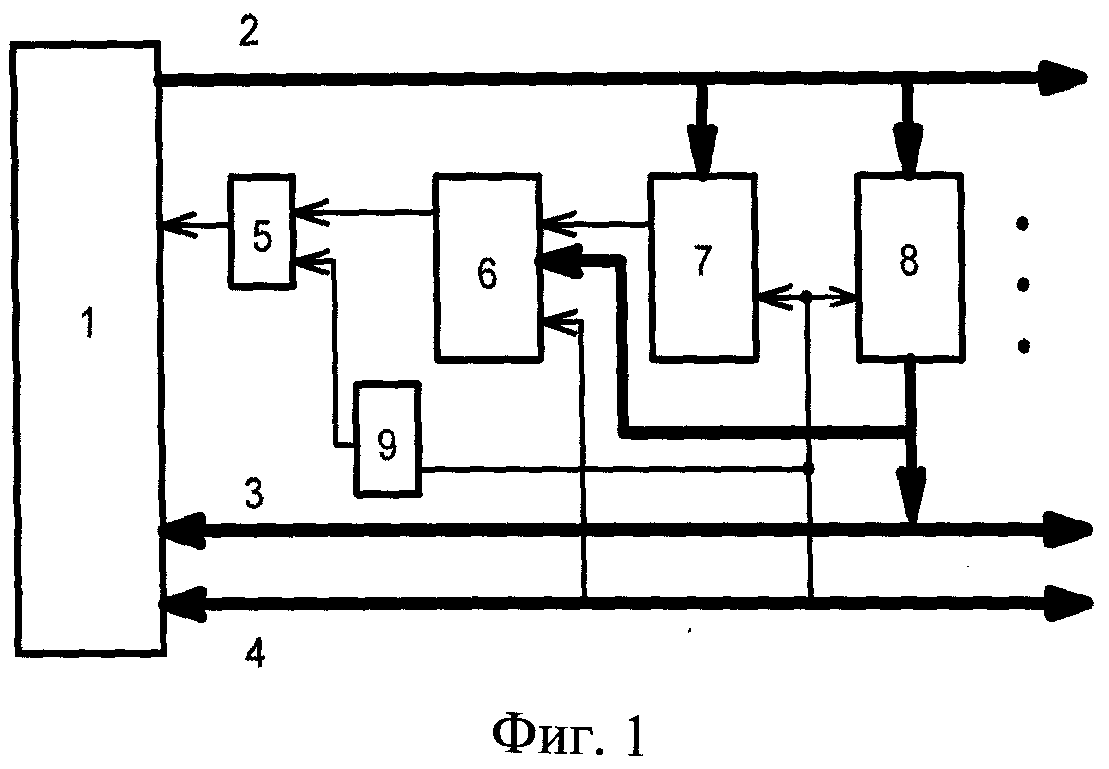

На фиг.1 представлен фрагмент структурной схемы микроЭВМ, где 1 - процессор; 2 - однонаправленная шина адреса; 3 - двунаправленная n-разрядная шина данных; 4 - шина управления; 5 - схема «И»; 6 - сумматор по модулю 2 на (n+2) входа; 7 - дополнительное однобитовое запоминающее устройство; 8 - основное (программное) n-разрядное запоминающее устройство; 9 - формирователь стробирующего сигнала (С).

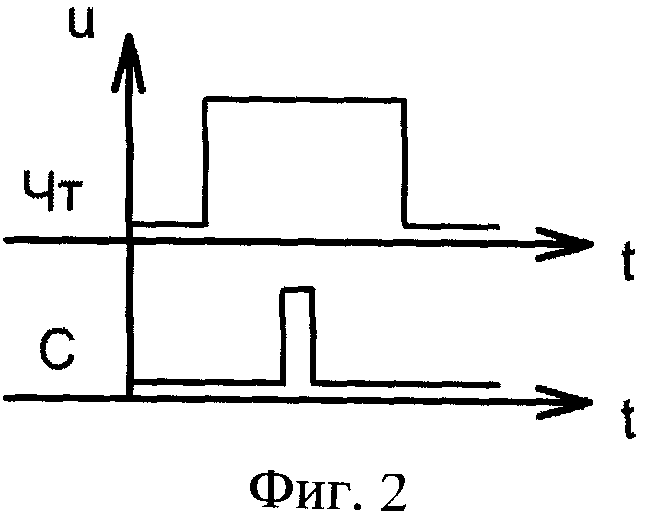

На фиг.2 представлена временная диаграмма, характеризующая временное соотношение между сигналом чтения (Чт) из основного и дополнительного запоминающего устройств и стробирующим сигналом (С).

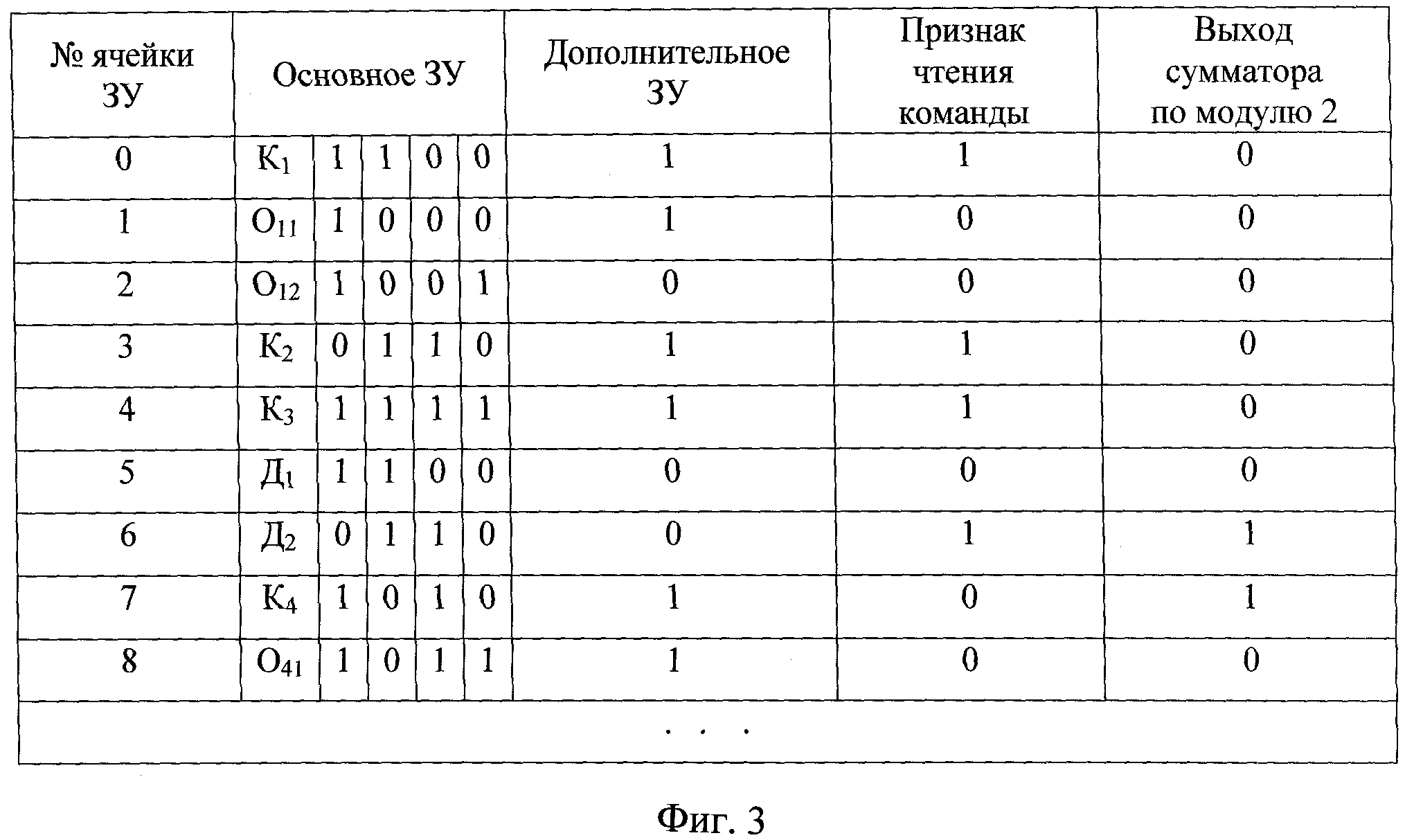

На фиг.3 представлен вариант размещения кодов в основном и дополнительном запоминающих устройствах в соответствии с заявляемым способом повышения надежности микроЭВМ, при этом

Кi - код i-ой команды;

Оij - код j-го операнда i-ой команды;

Дп - код n-ых данных.

Способ осуществляется следующим образом.

На основе предварительного анализа рабочей программы процессора 1, представленной в виде двоичных кодов, определяют адреса тех ячеек основного запоминающего устройства 8, в которых будут содержаться коды команд. Для каждой такой ячейки определяется количество единичных значений, содержащихся в коде команды, при этом если количество единичных значений в коде команде четное, то в соответствующий бит дополнительного запоминающего устройства 7 должна впоследствии записываться единица (то есть код команды дополняется до нечетности). Для всех других кодовых слов рабочей программы, включая и неиспользуемые программой ячейки основного запоминающего устройства 8, кодовые слова при помощи дополнительного запоминающего устройства 7 дополняются до четности.

Затем рабочая программа процессора 1, представленная в виде двоичных кодов, загружается в основное запоминающее устройство 8, а в дополнительное запоминающее устройство 7 загружаются найденные значения бит. Загрузка информации в основное 8 и дополнительное 7 запоминающие устройства может производиться как в составе микроЭВМ, так и вне нее.

В рабочем режиме функционирования основное 8 и дополнительное 7 запоминающие устройства образуют единое (n+1) разрядное запоминающее устройство, где n-разрядность шины данных процессора 1. На адресные входы основного 8 и дополнительного 7 запоминающих устройств одновременно подаются коды адреса, формируемые процессором 1 на шине адреса 2. Все n выходов основного запоминающего устройства 8 стандартно подключаются к шине данных 3 и дополнительно к n входам (n+2) входового сумматора по модулю два 6. К (n+1)-му входу сумматора 6 подключается выход дополнительного запоминающего устройства 7, а к (n+2)-му входу сумматора 6 подключается сигнал признака чтения кода команды, формируемый процессором 1 при выполнении программы и передаваемый по шине управления 4. Сигнал с выхода сумматора по модулю два 6 поступает на первый вход схемы «И» 5, на второй вход которой поступает стробирующий сигнал С, который в свою очередь формируется формирователем 9 из сигнала чтения (Чт), одновременно поступающего из шины управления 4 на соответствующие входы запоминающих устройств 7 и 8. Выход схемы «И» подключается к входу прерывания процессора 1. Временные соотношения между сигналами чтения (Чт) и стробирования (С) показаны на фиг.2.

Процессор 1 начинает свою работу с того, что устанавливает на шину адреса 2 двоичный код ячейки памяти основного 8 и дополнительного 7 запоминающих устройств, из которой будет считываться записанная в них информация. Одновременно с установкой кода на шине адреса 2 процессор 1 формирует на одной из линий шины управления 4 сигнал, поступающий на (n+2) вход сумматора 6 и свидетельствующий о том, что данные, считанные процессором 1 из данной ячейки основного запоминающего устройства 8, будут интерпретироваться процессором 1 как код команды. Иначе говоря, процессор формирует признак чтения кода команды из ячейки основного запоминающего устройства 8. Далее на одной из линий шины управления 4 формируется сигнал чтения из ячеек с одинаковым адресом основной 8 и дополнительной 7 памяти. Одновременно с фронтом сигнала чтения запускается формирователь 9, предназначенный для выработки сигнала стробирования схемы «И» 5. С началом действия сигнала чтения на выходах основного 8 и дополнительного 7 запоминающих устройств формируются коды, записанные в их ячейках памяти. Код из основного 8 запоминающего устройства поступает в шину данных 3 и на n входов сумматора 6. На (n+1) вход сумматора 6 поступает код с дополнительного 7 запоминающего устройства. К моменту формирования фронта сигнала стробирования сумматор 6 формирует на своем выходе стабильный признак четности или нечетности (n+2) разрядного входного кода. Сигнал с выхода сумматора 6 поступает на второй вход схемы «И» 5. При единичном значении стробирующего сигнала, поступающего на первый вход схемы «И» 5, проверяется значение сигнала с выхода сумматора 6. Если на выходе сумматора 6 сформирован «0», то это свидетельствует о том, что код, считанный из основного 8 и дополнительно 7 запоминающих устройств, не имеет единичных искажений и правильно интерпретируется процессором 1. Если на выходе сумматора 6 сформирована «1», то это свидетельствует о том, что код, считанный из основного 8 и дополнительно 7 запоминающих устройств, либо имеет единичные искажения, либо этот код не правильно интерпретируется процессором 1, при этом на выходе схемы «И» будет сформирован единичный сигнал, по длительности примерно равный стробирующему сигналу и вызывающий прерывание процессора. Подпрограмма обслуживания данного прерывания выбирается пользователем микроЭВМ и ориентируется на целенаправленную реакцию на возможные случайные сбои.

Как видно из фиг.3, процессор 1 начинает свою работу с команды, расположенной в нулевой ячейке основного запоминающего устройства 8, и правильно функционирует до команды, размещенной в четвертой ячейке основной памяти 8. Из пятой ячейки процессором 1 правильно считываются данные. При попытке процессора 1 интерпретации данных, находящихся в шестой ячейке, в качестве кода команды, будет сформирован сигнал ошибки с выхода сумматора 6. Аналогичным образом обнаруживается попытка процессора 1 интерпретации кода команды, расположенного в шестой ячейке, в качестве кода операнда или данных.

Из данных, представленных на фиг.3, однозначно следует также, что единичные искажения данных, считываемых процессором 1 из основного 8 и дополнительного 7 запоминающих устройств при правильной интерпретации процессором 1 кодов команд, будут обнаружены с минимальными временными задержками.

Техническим результатом от использования заявляемого изобретения является расширение функциональных возможностей способа повышения надежности микроЭВМ за счет оперативной реакции не только на случайные единичные искажения считываемых из основного запоминающего устройства кодов, но и на случайные срывы процессора с заданной программы функционирования.

Данный способ повышения надежности наиболее эффективен для микроЭВМ, базирующихся на процессорах с Гарвардской архитектурой и реализующих программу, содержащую большой объем табличных данных и/или кодов символьных переменных.

Источники информации

1. Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. - М.: Радио и связь, 1993. - 256 с., стр.89.

2. Карлащук В.И. Электронная лаборатория на IBM PC. Лабораторный практикум на базе Electronics Workbench и MATLAB. - М.: СОЛОН-Пресс, 204. - 800 с., стр.366.

3. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник. В 2 т. / В.-Б. Б.Абрайтис, Н.Н.Аверьянов, А.И.Белоус и др.; Под ред. В.А.Шахнова. - М.: Радио и связь, 1988. - T.1. - 386 с.

Способ повышения надежности микроЭВМ, заключающийся в том, что к n-разрядному основному (программному) запоминающему устройству микроЭВМ предварительно добавляют дополнительное однобитовое запоминающее устройство, которые в рабочем режиме образуют единое (n+1)-разрядное запоминающее устройство, затем в n-разрядные ячейки основного запоминающего устройства загружают программу работы процессора в виде машинных кодов, после чего в каждую однобитовую ячейку дополнительного запоминающего устройства записывают единицу или ноль, таким образом, чтобы сумма единичных значений в кодах каждой (n+1)-разрядной ячейки основного и дополнительного запоминающих устройств была бы четной, что в режиме работы при чтении данных из основного и дополнительного запоминающих устройств автоматически проверяют многовходовым сумматором по модулю 2, сигнал с выхода которого подают на вход прерывания процессора, который переходит на подпрограмму обработки прерывания в случае неверного чтения кодов из основного и дополнительного запоминающих устройств, отличающийся тем, что предварительно количество входов сумматора по модулю два увеличивают до (n+2), на (n+2) вход которого дополнительно подают единичный признак чтения кода команды, который в режиме работы автоматически формируется процессором микроЭВМ, а на этапе записи данных в дополнительное запоминающее устройство в каждый его бит записывают единицу или ноль, таким образом, чтобы в (n+1) битах дополнительного запоминающего устройства и основного запоминающего устройства, в ячейках которого содержатся коды команд, сумма единичных значений была бы нечетной, а в ячейках которого содержатся все остальные коды - четной, при этом в режиме правильной работы микроЭВМ и отсутствии «блужданий» при чтении из основного и дополнительного запоминающих устройств будет сохраняться четность (n+2) бит, одновременно поступающих на вход сумматора по модулю два.