Результат интеллектуальной деятельности: СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ)

Вид РИД

Изобретение

Изобретение относится к оптоэлектронике и микроэлектронике и может быть использовано для построения сдвиговых регистров в фотоприемных субмодулях для мозаичных фотоприемников, в частности в фотоприемниках на микроболометрах.

Известен сдвиговый регистр (Патент РФ на изобретение №2344498 «Сдвиговый регистр» МПК: G11C 19/00, H03K 3/037, H03K 9/001, опубликован 20.01.2009 г.), который выполнен на элементах И, ИЛИ, НЕ, содержащий в каждом разряде первый и второй RS-триггеры, четыре логических элемента И, один элемент ИЛИ, информационный вход, первую и вторую шины управления приемом кода в первый и второй триггеры при выполнении операции сдвига кода, информационный выход, при этом выходы первого и третьего элементов И соединены с R-входами первого и второго RS-триггеров соответственно, выход второго элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с информационным входом, а выход упомянутого элемента ИЛИ подключен к S-входу первого триггера, первые входы первого и второго элементов И связаны с первой шиной управления приемом кода в первый триггер, первые входы третьего и четвертого элементов И соединены с второй шиной управления приемом кода во второй триггер, причем нулевой и единичный выходы первого триггера i-го разряда соединены с вторыми входами третьего и четвертого элементов И (i+1)-го разряда соответственно, нулевой и единичный выходы второго триггера i-го разряда соединены со вторыми входами первого и второго элементов И (i+1)-го разряда соответственно, кроме того, первый и второй входы второго элемента ИЛИ соединены с S-входами первого и второго триггеров, выход упомянутого элемента ИЛИ является информационным выходом i-го разряда и т.д.

Недостатком этого сдвигового регистра является необходимость использования в каждом разряде двух RS-триггера, что увеличивает аппаратурные затраты и повышает потребление энергопитания.

Известен реверсивный сдвиговой регистр (Патент РФ на изобретение №2022372 «Реверсивный регистр сдвига», МПК: G11C 19/00, опубликован 30.10.1994 г.) Сущность которого состоит в том, что он содержит в каждом разряде JK-триггер, четыре элемента И, в каждом разряде, кроме первого и последнего, четыре элемента ИЛИ, в первом и последнем разрядах - три элемента ИЛИ, шины управления направлением сдвига вправо и влево, вход сброса регистра, вход сдвига, прямой и инверсный информационные входы регистра и выход информации в прямом последовательном коде при сдвиге вправо, прямой и инверсный информационные парафазные входы регистра и выход информации в прямом последовательном коде при сдвиге влево, вход управления режимом сдвига - уплотнение единиц и вход управления режимом сдвига - уплотнение нулей, причем прямой выход JK-триггера каждого разряда, кроме последнего, соединен соответственно с первым входом первого элемента И последующего разряда, а прямой выход JK-триггера каждого разряда, кроме первого, соединен соответственно с первым входом второго элемента И предыдущего разряда, выходы первого и второго элементов И каждого разряда соединены с входами первого элемента ИЛИ, вход которого соединен с J-входом JK-триггера данного разряда, вторые входы первого и второго элементов И всех разрядов являются соответственно входами управления сдвигом вправо и сдвигом влево регистра и т.д. Введение в известный сдвиговой регистр в каждый разряд, кроме первого и последнего, двух элементов ИЛИ (пятого и шестого), в первую ячейку пятого элемента ИЛИ, в последнюю ячейку шестого элемента ИЛИ, а также новых связей позволяет расширить функциональные возможности реверсивного регистра сдвига за счет уплотнения нулей кодовой комбинации как влево, так и вправо регистра.

Недостатком этого реверсивного сдвигового регистра, как и предыдущего, является то, что он имеет сложную структуру и управление, состоит из большого количества транзисторов и вследствие этого при использовании в качестве блока адресации по вертикали в мозаичных фотоприемниках приводит к падению эффективности преобразования изображений в мозаичном фотоприемнике в целом. (Эффективность преобразования изображений это отношение количества работающих фоточувствительных элементов (ФЧЭ) в мозаичном фотоприемнике, к сумме ФЧЭ, потерянных в «слепых зонах» и работающих в мозаичном фотоприемнике).

Известен регистр сдвига на МДП-транзисторах (Авторское свидетельство №1269210, МПК: G11C 19/00 опубликованное 07.11.1986 г.) в котором выход каждого из инверторов, составляющих регистр, через коммутирующие транзисторы соединен с входами последующего и предыдущего инверторов. При этом во время первого такта работы сдвигового регистра образуются триггеры, состоящие из четного и последующего нечетного инверторов, а во время второго такта работы - из четного и предыдущего нечетного инверторов.

Недостатком этого регистра сдвига на МДП-транзисторах является то, что он требует большого количества тактовых шин для управляющих сигналов и сложную диаграмму управляющих сигналов, что усложняет технологию его изготовления, снижает быстродействие, повышает стоимость устройства и существенно понижает эффективность мозаичного фотоприемника в целом.

Известен также сдвиговый регистр, принятый за прототип, приведенный в книге С. Мурога, Системное проектирование сверхбольших интегральных схем, изд. «Мир», М., 1985, стр.258, рис.4.9.19. Сдвиговый регистр содержит ячейки, каждая из которых состоит из информационного и коммутирующего МДП-транзисторов р-типа, информационного и коммутирующего МДП-транзисторов n-типа, шины питания, шины нулевого потенциала, первой, второй, третьей и четвертой тактовых шин, причем объединенные истоки коммутирующих МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-ключ, являются входом в ячейку, а в первой ячейке сдвигового регистра являются, одновременно, первым информационным входом сдвигового регистра при считывании информации слева направо, их объединенные стоки соединены с объединенными затворами информационных МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-инвертор; исток информационного МДП-транзистора р-типа соединен с шиной питания, объединенные стоки информационных МДП-транзисторов р- и n-типа являются выходом КМОП-инвертора и, одновременно, выходом ячейки, а в последней ячейке сдвигового регистра являются также и первым информационным выходом сдвигового регистра при считывании информации слева направо; исток информационного МДП-транзистора n-типа соединен с шиной нулевого потенциала, затвор коммутирующего МДП-транзистора n-типа соединен с первой тактовой шиной в нечетной ячейке или со второй тактовой шиной в четной ячейке, затвор коммутирующего МДП-транзистора р-типа соединен с третьей тактовой шиной в нечетной ячейке или с четвертой тактовой шиной в четной ячейке,

Этот сдвиговый регистр, принятый за прототип, содержит меньшее количество шин и МДП-транзисторов по сравнению с известными аналогами.

Однако он обладает существенными недостатками, а именно сдвигает информацию только в одном направлении и паразитные емкости его тактовых шин существенно влияют на работу сдвигового регистра.

Техническим результатом изобретения является:

- расширение функциональных возможностей за счет обеспечения реверсивности сдвига информации внутри сдвигового регистра,

- минимизация занимаемой площади кристалла ИС,

- расширение области применения за счет возможности двунаправленной передачи информации и стабильной работы сдвигового регистра в условиях существенных паразитных емкостей тактовых шин.

Технический результат достигается тремя вариантами изобретения. Технический результат первого варианта изобретения достигается тем, что в сдвиговом регистре, содержащем ячейки, каждая из которых состоит из информационного и коммутирующего МДП-транзисторов р-типа, информационного и коммутирующего МДП-транзисторов n-типа, шины питания, шины нулевого потенциала, первой, второй, третьей и четвертой тактовых шин, причем объединенные истоки коммутирующих МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-ключ, являются входом в ячейку, а в первой ячейке сдвигового регистра являются, одновременно, первым информационным входом сдвигового регистра при считывании информации слева направо; их объединенные стоки соединены с объединенными затворами информационных МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-инвертор; исток информационного МДП-транзистора р-типа соединен с шиной питания, объединенные стоки информационных МДП-транзисторов р- и n-типа являются выходом КМОП-инвертора и, одновременно, выходом ячейки, а в последней ячейке сдвигового регистра являются также и первым информационным выходом сдвигового регистра при считывании информации слева направо; исток информационного МДП-транзистора n-типа соединен с шиной нулевого потенциала; затвор коммутирующего МДП-транзистора n-типа соединен с первой тактовой шиной в нечетной ячейке или со второй тактовой шиной в четной ячейке; затвор коммутирующего МДП-транзистора р-типа соединен с третьей тактовой шиной в нечетной ячейке или с четвертой тактовой шиной в четной ячейке; в каждую ячейку введены пятая и шестая тактовые шины, и в каждую нечетную ячейку введен дополнительный КМОП-ключ, который функционально образуют дополнительный коммутирующий МДП-транзистор р-типа и дополнительный коммутирующий МДП-транзистор n-типа, причем объединенные истоки дополнительных коммутирующих МДП-транзисторов р- и n-типа являются вторым входом в ячейку и соединены с выходом второй последующей четной ячейки, а в последней нечетной ячейке сдвигового регистра являются, одновременно, и вторым информационным входом сдвигового регистра при считывании информации справа налево, их объединенные стоки соединены с объединенными затворами информационных МДП-транзисторов р- и n-типа и объединенными стоками коммутирующих МДП-транзисторов р- и n-типа этой ячейки, затвор дополнительного коммутирующего МДП-транзистора n-типа соединен с пятой тактовой шиной, затвор дополнительного коммутирующего МДП- транзистора р-типа соединен с шестой тактовой шиной, выход первой четной ячейки сдвигового регистра соединен с входом последующей нечетной ячейки и является, одновременно, вторым информационным выходом сдвигового регистра при считывании информации справа налево.

Технический результат второго варианта изобретения достигается тем, что в сдвиговом регистре, содержащем ячейки, каждая из которых состоит из информационного и коммутирующего МДП-транзисторов р-типа, информационного и коммутирующего МДП-транзисторов n-типа; шины питания, шины нулевого потенциала, первой, второй, третьей и четвертой тактовых шин, причем объединенные истоки коммутирующих МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-ключ, являются входом в ячейку, а в первой ячейке сдвигового регистра являются, одновременно, первым информационным входом сдвигового регистра при считывании информации слева направо; их объединенные стоки соединены с объединенными затворами информационных МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-инвертор; исток информационного МДП-транзистора р-типа соединен с шиной питания, объединенные стоки информационных МДП-транзисторов р- и n-типа являются выходом КМОП-инвертора и, одновременно, выходом ячейки, а в последней ячейке сдвигового регистра являются также первым информационным выходом сдвигового регистра при считывании информации слева направо; исток информационного МДП-транзистора n-типа соединен с шиной нулевого потенциала, затвор коммутирующего МДП-транзистора n-типа соединен с первой тактовой шиной в нечетной ячейке или со второй тактовой шиной в четной ячейке, затвор коммутирующего МДП-транзистора р-типа соединен с третьей тактовой шиной в нечетной ячейке или с четвертой тактовой шиной в четной ячейке; в каждую ячейку введены пятая, шестая, седьмая и восьмая тактовые шины и дополнительный КМОП-ключ, который функционально образуют дополнительный коммутирующий МДП-транзистор р-типа и дополнительный коммутирующий МДП-транзистор n-типа, причем объединенные истоки дополнительных коммутирующих МДП-транзисторов р- и n-типа являются вторым входом в ячейку, а в последней ячейке сдвигового регистра являются, одновременно, вторым информационным входом сдвигового регистра при считывании информации справа налево, их объединенные стоки соединены с объединенными затворами информационных МДП-транзисторов р- и n-типа и с объединенными стоками коммутирующих МДП-транзисторов р- и n-типа своей ячейки, в каждой нечетной ячейке затвор дополнительного коммутирующего МДП-транзистора п-типа соединен с пятой тактовой шиной, затвор дополнительного коммутирующего МДП-транзистора р-типа соединен с шестой тактовой шиной; в каждой четной ячейке затвор дополнительного коммутирующего МДП-транзистора n-типа соединен с седьмой тактовой шиной, затвор дополнительного коммутирующего МДП-транзистора р-типа соединен с восьмой тактовой шиной; второй вход каждой ячейки соединен с выходом последующей ячейки, выход первой ячейки является, одновременно, вторым информационным выходом сдвигового регистра при считывании информации справа налево.

Технический результат третьего варианта изобретения достигается тем, что в сдвиговом регистре, содержащем ячейки, каждая из которых состоит из информационного и коммутирующего МДП-транзисторов р-типа, информационного и коммутирующего МДП-транзисторов n-типа; шины питания, шины нулевого потенциала, первой, второй, третьей и четвертой тактовых шин, причем объединенные истоки коммутирующих МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-ключ, являются первым входом в ячейку, а в первой ячейке сдвигового регистра являются, одновременно, и первым информационным входом сдвигового регистра при считывании информации слева направо; их объединенные стоки соединены с объединенными затворами информационных МДП-транзисторов р- и n-типа, которые функционально образуют КМОП-инвертор; исток информационного МДП-транзистора р-типа соединен с шиной питания, объединенные стоки информационных МДП-транзисторов р- и n-типа являются выходом КМОП-инвертора и, одновременно, выходом ячейки, а в последней ячейке сдвигового регистра являются также и первым информационным выходом сдвигового регистра при считывании информации слева направо; исток информационного МДП-транзистора n-типа соединен с шиной нулевого потенциала; в каждую ячейку введены дополнительный коммутирующий МДП-транзистор n-типа, дополнительный коммутирующий МДП-транзистор р-типа, которые функционально образуют дополнительный КМОП-ключ, шесть дополнительных информационных МДП-транзисторов n-типа и шесть дополнительных информационных МДП-транзисторов р-типа, которые попарно n- и р-тип функционально образуют первый, второй, третий, четвертый, пятый и шестой дополнительные КМОП-инверторы; причем затвор коммутирующего МДП-транзистора n-типа соединен с выходом первого дополнительного КМОП-инвертора, образованным объединенными стоками первой пары дополнительных информационных МДП-транзисторов n- и р-типа, вход первого дополнительного КМОП-инвертора, образованный объединенными затворами этих МДП-транзисторов, соединен с первой тактовой шиной в нечетной ячейке или со второй тактовой шиной в четной ячейке; затвор коммутирующего МДП-транзистора р-типа соединен с выходом второго дополнительного КМОП-инвертора, образованным объединенными стоками второй пары дополнительных информационных МДП-транзисторов n- и р-типа, вход второго дополнительного КМОП-инвертора соединен с выходом третьего дополнительного КМОП-инвертора, образованным объединенными стоками третьей пары дополнительных информационных МДП-транзисторов n- и р-типа, вход третьего дополнительного КМОП-инвертора соединен с первой тактовой шиной в нечетной ячейке или со второй таковой шиной в четной ячейке; затвор дополнительного коммутирующего МДП-транзистора n-типа соединен с выходом четвертого дополнительного КМОП-инвертора, образованным объединенными стоками четвертой пары дополнительных информационных МДП-транзисторов n- и р-типа, вход четвертого дополнительного КМОП-инвертора соединен с третьей тактовой шиной в нечетной ячейке или с четвертой тактовой шиной в четной ячейке; затвор дополнительного коммутирующего МДП-транзистора р-типа соединен с выходом пятого дополнительного КМОП-инвертора, образованным объединенными стоками пятой пары дополнительных информационных МДП-транзисторов n- и р-типа, вход пятого дополнительного КМОП-инвертора соединен с выходом шестого дополнительного КМОП-инвертора, образованным объединенными стоками шестой пары дополнительных информационных МДП-транзисторов n- и р-типа, вход шестого дополнительного КМОП-инвертора соединен с третьей тактовой шиной в нечетной ячейке или с четвертой тактовой шиной в четной ячейке; объединенные истоки дополнительных коммутирующих МДП-транзисторов n- и р- типа являются вторым входом в ячейку и соединены с выходом последующей ячейки, а в последней ячейке сдвигового регистра являются, одновременно, вторым информационным входом сдвигового регистра при считывании информации справа налево, их объединенные стоки соединены с объединенными стоками коммутирующих МДП-транзисторов n- и р-типа и с объединенными затворами информационных МДП-транзисторов n- и р-типа, которые являются входом функционально образованного КМОП-инвертора, выход которого в первой ячейке сдвигового регистра является одновременно вторым информационным выходом сдвигового регистра при считывании информации справа налево. Истоки дополнительных информационных МДП-транзисторов р-типа соединены с шиной питания, истоки дополнительных информационных МДП-транзисторов n-типа соединены с шиной нулевого потенциала.

Сущность вариантов изобретения поясняется нижеследующим описанием и прилагаемыми фигурами.

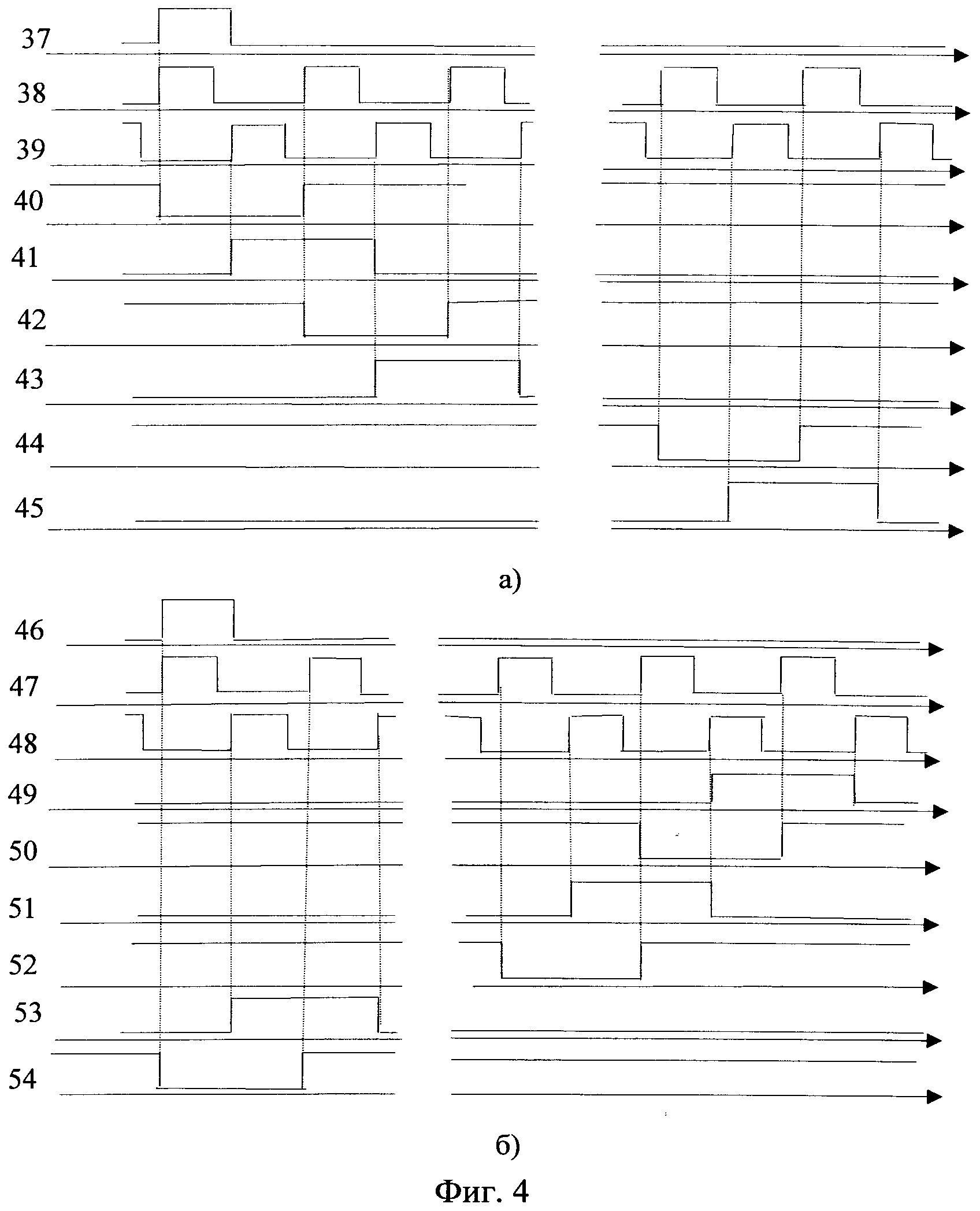

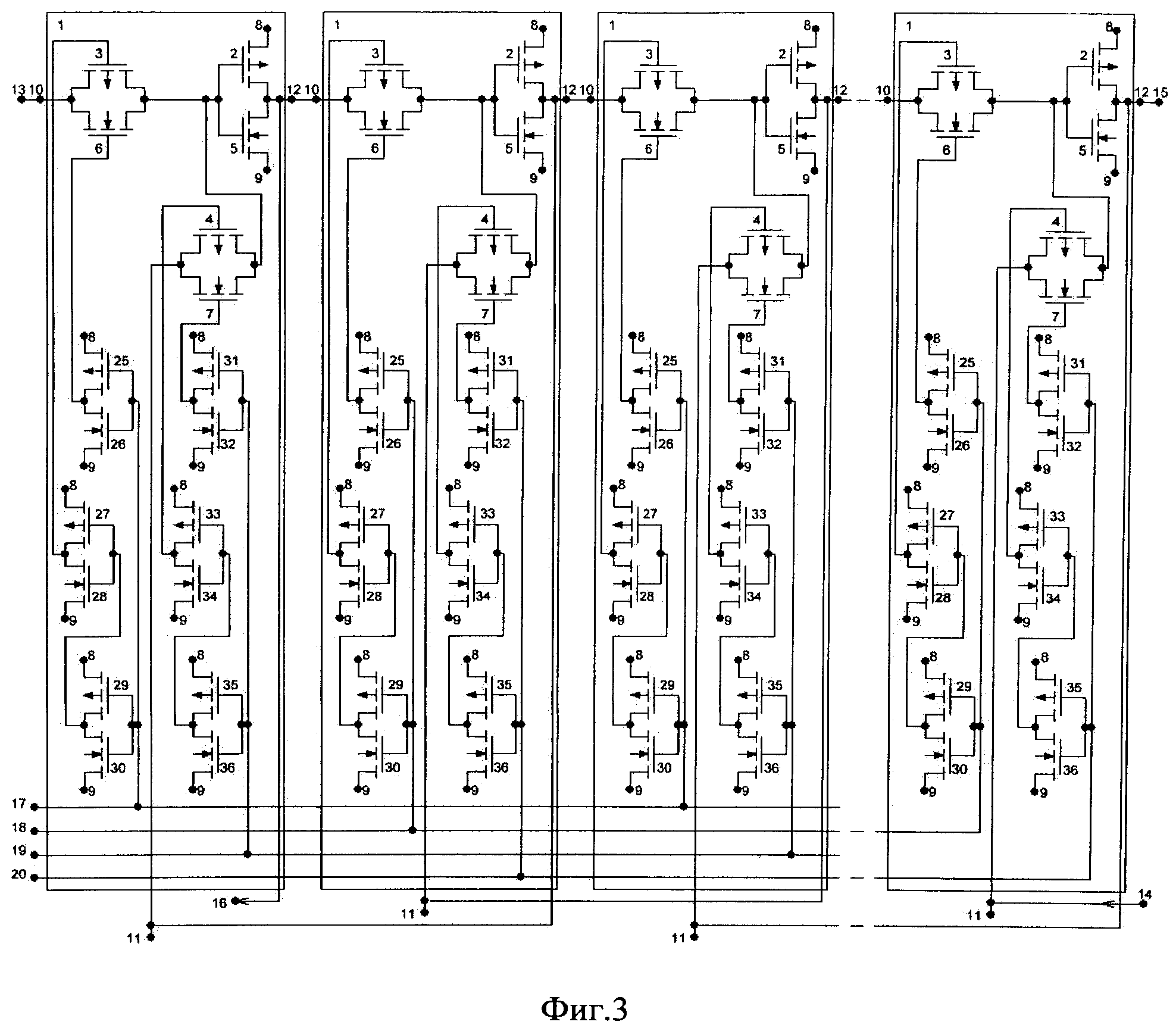

На фиг.1 приведена функциональная схема первого варианта сдвигового регистра. На фиг.2 приведена функциональная схема второго варианта сдвигового регистра. На фиг.3 приведена функциональная схема третьего варианта сдвигового регистра. На фиг.4 приведены временные диаграммы работы первого варианта сдвигового регистра при выполнении операции сдвига логической единицы вправо (сдвиг информации слева направо) и влево. На фиг.5 приведены временные диаграммы работы второго варианта сдвигового регистра при выполнении операции сдвига логической единицы вправо (сдвиг информации слева направо) и влево. На фиг.6 приведены временные диаграммы работы третьего варианта сдвигового регистра при выполнении операции сдвига логической единицы вправо (сдвиг информации слева направо) и влево.

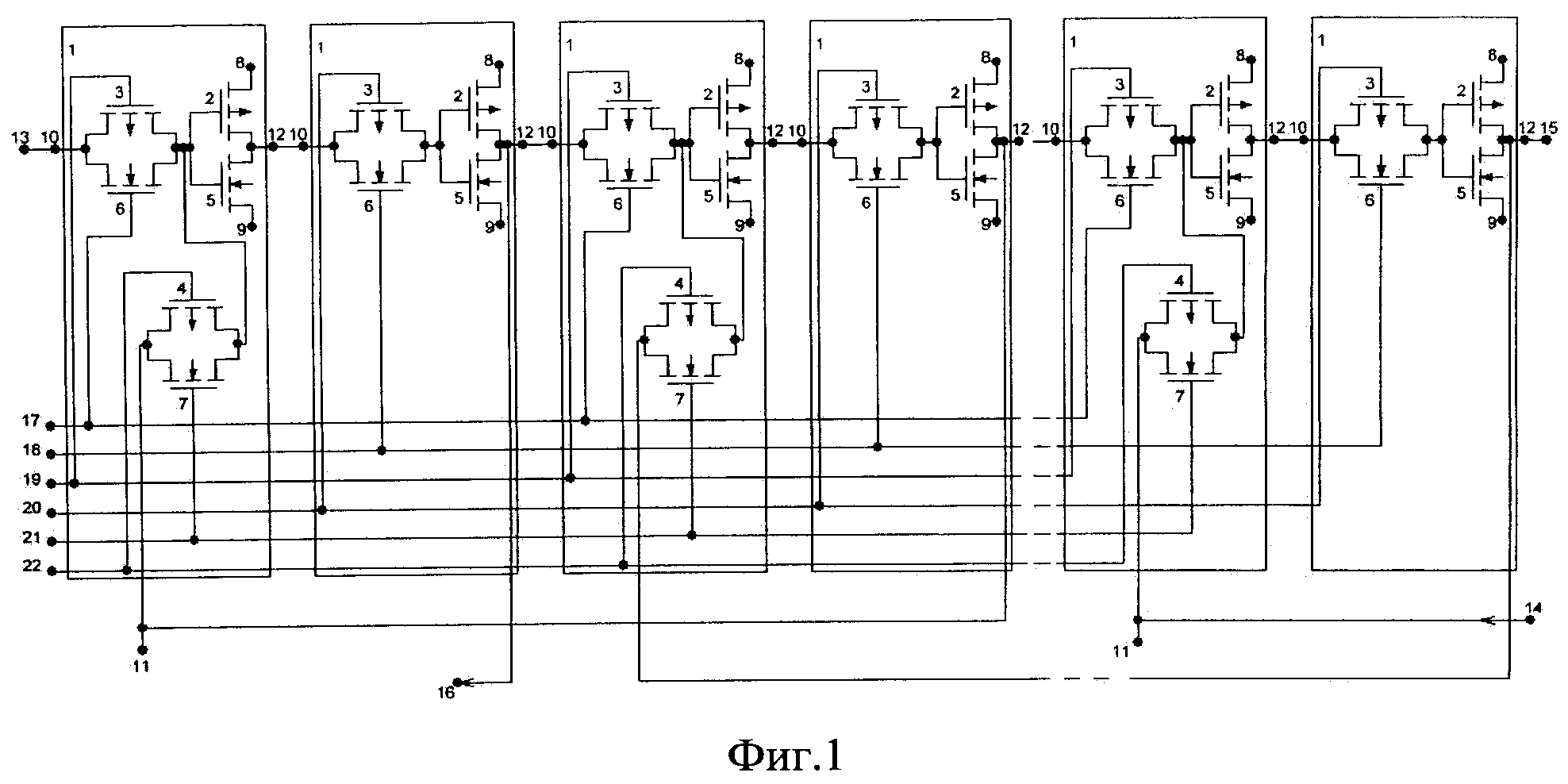

На фиг.1 приведена функциональная схема первого варианта сдвигового регистра, где 1 - ячейка, 2 - информационный МДП-транзистор р-типа, 3 - коммутирующий МДП-транзистор р-типа, 4 - дополнительный коммутирующий МДП-транзистор р-типа, 5 - информационный МДП-транзистор n-типа, 6 - коммутирующий МДП-транзистор n-типа, 7 - дополнительный коммутирующий МДП-транзистор n-типа, 8 - шина питания, 9 - шина нулевого потенциала, 10 - первый вход ячейки, 11 - второй вход ячейки, 12 - выход ячейки, 13 - первый информационный вход сдвигового регистра, 14 - второй информационный вход сдвигового регистра, 15 - первый информационный выход сдвигового регистра, 16 - второй информационный выход сдвигового регистра, 17 - первая тактовая шина, 18 - вторая тактовая шина, 19 - третья тактовая шина, 20 - четвертая тактовая шина, 21 - пятая тактовая шина, 22 - шестая тактовая шина.

Первый вариант сдвигового регистра организован следующим образом (фиг.1.). В каждой нечетной ячейке 1 объединенные истоки коммутирующих МДП-транзисторов р-типа 3 и n-типа 6, которые функционально образуют КМОП-ключ, являются первым входом 10 ячейки; в первой ячейке сдвигового регистра это соединение является одновременно и первым информационным входом сдвигового регистра 13 при выполнении операции сдвига логической единицы вправо; их объединенные стоки соединены в своей ячейке с объединенными стоками дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7, которые функционально образуют КМОП-ключ, и с объединенными затворами информационных МДП-транзисторов р-типа 2 и n-типа 5, которые функционально образуют КМОП-инвертор. Объединенные стоки информационных МДП-транзисторов р-типа 2 и n-типа 5 являются выходом КМОП-инвертора и одновременно образуют выход 12 нечетной ячейки. Объединенные истоки дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7, образуя второй вход 11 нечетной ячейки, соединены с выходом 12, образованным объединенными стоками информационных МДП-транзисторов р-типа 2 и n-типа 5 второй последующей четной ячейки. В последней нечетной ячейке сдвигового регистра второй вход 11 является, одновременно, вторым информационным входом сдвигового регистра 14 при выполнении операции сдвига информации слева направо. В каждой четной ячейке 1 объединенные истоки коммутирующих МДП-транзисторов р-типа 3 и n-типа 6, которые функционально образуют КМОП-ключ, являются входом 10 ячейки, объединенные стоки этих МДП-транзисторов в каждой ячейке соединены с объединенными затворами информационных МДП-транзисторов р-типа 2 и n-типа 5, которые функционально образуют КМОП-инвертор. Объединенные стоки информационных МДП-транзисторов р-типа 2 и n-типа 5 являются выходом КМОП-инвертора и образуют выход 12 четной ячейки. Выход 12 первой четной ячейки сдвигового регистра соединяется с первым входом 10 следующей ячейки и является, одновременно, вторым информационным выходом сдвигового регистра 16 при выполнении операции сдвига информации справа налево. Выход 12 последней четной ячейки соединяется со вторым входом 11 предстоящей второй от конца сдвигового регистра нечетной ячейки, и является, одновременно, первым информационным выходом сдвигового регистра 15 при операции сдвига информации слева направо. В нечетной ячейке на затвор коммутирующего МДП-транзистора n-типа 6 и на затвор дополнительного коммутирующего МДП-транзистора n-типа 7 поступают по первой 17 и пятой 21 тактовым шинам прямые тактовые сигналы ф1 и ф3, а на затвор коммутирующего МДП-транзистора р-типа 3 и на затвор дополнительного коммутирующего МДП-транзистора р-типа 4 по третьей 19 и шестой 22 тактовым шинам поступают инверсные им сигналы ф1* и ф3*, соответственно. В четной ячейке на затвор коммутирующего МДП-транзистора n-типа 6 поступают по второй тактовой шине 18 прямые тактовые сигналы ф2, а на затвор коммутирующего МДП-транзисторов р-типа 3 по четвертой тактовой шине 20 - инверсные им сигналы ф2*, соответственно. Питание КМОП-инвертора осуществляется соединением истока информационного МДП-транзистора р-типа 2 с шиной питания 8 и истока информационного МДП-транзистора n-типа 5 с шиной нулевого потенциала 9.

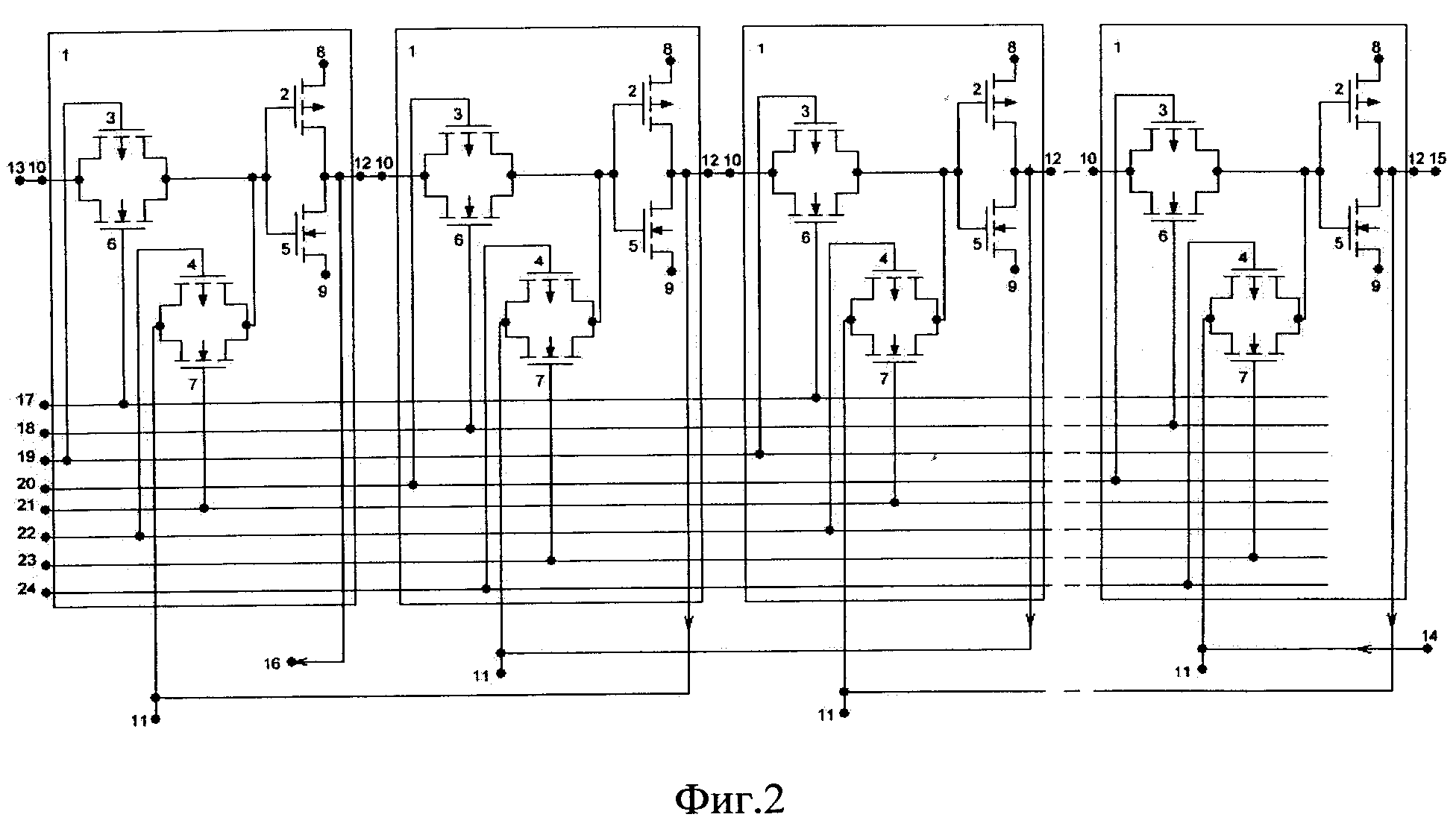

На фиг.2 приведена функциональная схема второго варианта сдвигового регистра, где 1 - ячейка, 2 - информационный МДП-транзистор р-типа, 3 - коммутирующий МДП-транзистор р-типа, 4 - дополнительный коммутирующий МДП-транзистор р-типа, 5 - информационный МДП-транзистор n-типа, 6 - коммутирующий МДП-транзистор n-типа, 7 - дополнительный коммутирующий МДП-транзистор n-типа, 8 - шина питания, 9 - шина нулевого потенциала, 10 - первый вход ячейки, 11 - второй вход ячейки, 12 - выход ячейки, 13 - первый информационный вход сдвигового регистра, 14 - второй информационный вход сдвигового регистра, 15 - первый информационный выход сдвигового регистра, 16 - второй информационный выход сдвигового регистра, 17 - первая тактовая шина, 18 - вторая тактовая шина, 19 - третья тактовая шина, 20 - четвертая тактовая шина, 21 - пятая тактовая шина, 22 - шестая тактовых шин, 23 - седьмая тактовая шина, 24 - восьмая тактовая шина.

Второй вариант сдвигового регистра организован следующим образом (фиг.2.). В каждой ячейке 1 объединенные истоки коммутирующих МДП-транзисторов р-типа 3 и n-типа 6, которые функционально образуют КМОП-ключ, являются первым входом 10 в ячейку, в первой ячейке сдвигового регистра это соединение является, одновременно, и первым информационным входом сдвигового регистра 13 при выполнении операции сдвига логической единицы вправо. Объединенные стоки этих коммутирующих МДП-транзисторов соединены с объединенными затворами информационных МДП-транзисторов р-типа 2 и n-типа 5, которые функционально образуют КМОП-инвертор, и с объединенными стоками дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7, которые, функционально образуют КМОП-ключ. Объединенные истоки дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7, образуя второй вход 11 ячейки, соединены с выходом 12, образованным объединенными стоками информационных МДП-транзисторов р-типа 2 и n-типа 5 последующей ячейки. В последней ячейке второй вход 11 является одновременно вторым информационным входом сдвигового регистра 14 при выполнении операции сдвига информации слева направо. Выход 12 первой ячейки соединяется с первым входом 10 следующей ячейки и является, одновременно, вторым информационным выходом сдвигового регистра 16 при выполнении операции сдвига информации справа налево. Выход 12 последней ячейки соединяется со вторым входом 11 предстоящей ячейки и является, одновременно, первым информационным выходом сдвигового регистра 15 при операции сдвига информации слева направо. В нечетной ячейке на затвор коммутирующего МДП-транзистора n-типа 6 и на затвор дополнительного коммутирующего МДП-транзистора n-типа 7 поступают по первой 17 и пятой 21 тактовым шинам прямые тактовые сигналы (ф1 и ф3), а на затвор коммутирующего МДП-транзистора р-типа 3 и на затвор дополнительного коммутирующего МДП-транзистора р-типа 4 по третьей 19 и шестой 22 тактовым шинам поступают инверсные им сигналы (ф1* и ф3*), соответственно. В четной ячейке на затвор коммутирующего МДП-транзистора n-типа 6 и на затвор дополнительного коммутирующего МДП-транзистора n-типа 7 поступают по второй 18 и седьмой 23 тактовым шинам поступают прямые тактовые сигналы (ф2 и ф4), а на затвор коммутирующего МДП-транзистора р-типа 3 и на затвор дополнительного коммутирующего МДП-транзистора р-типа 4 по четвертой 20 и восьмой 24 тактовым шинам -инверсные им сигналы (ф2* и ф4*), соответственно. Питание КМОП-инвертора осуществляется соединением истока информационного МДП-транзистора р-типа 2 с шиной питания 8 и истока информационного МДП-транзистора n-типа 5 с шиной нулевого потенциала 9.

На фиг.3 приведена функциональная схема третьего варианта сдвигового регистра, где 1 - ячейка, 2 - информационный МДП-транзистор р-типа, 3 - коммутирующий МДП-транзистор р-типа, 4 - дополнительный коммутирующий МДП-транзистор р-типа, 5 - информационный МДП-транзистор n-типа, 6 - коммутирующий МДП-транзистор n-типа, 7 -дополнительный коммутирующий МДП-транзистор n-типа, 8 - шина питания, 9 - шина нулевого потенциала, 10 - первый вход ячейки, 11 - второй вход ячейки, 12 - выход ячейки, 13 - первый информационный вход сдвигового регистра, 14 - второй информационный вход сдвигового регистра, 15 - первый информационный выход сдвигового регистра, 16 - второй информационный выход сдвигового регистра, 17 - первая тактовая шина, 18 - вторая тактовая шина, 19 - третья тактовая шина, 20 - четвертая тактовая шина, 25 - первый дополнительный информационный МДП-транзистор р-типа, 26 - первый дополнительный информационный МДП-транзистор n-типа, 27 - второй дополнительный информационный МДП-транзистор р-типа, 28 - второй дополнительный информационный МДП-транзистор n-типа, 29 - третий дополнительный информационный МДП-транзистор р-типа, 30 - третий дополнительный информационный МДП-транзистор n-типа, 31 - четвертый дополнительный информационный МДП-транзистор р-типа, 32 - четвертый дополнительный информационный МДП-транзистор n-типа, 33 - пятый дополнительный информационный МДП-транзистор р-типа, 34 - пятый дополнительный информационный МДП-транзистор n-типа, 35 - шестой дополнительный информационный МДП-транзистор р-типа, 36 - шестой дополнительный информационный МДП-транзистор n-типа.

Третий вариант сдвигового регистра организован следующим образом (фиг.3). В каждой ячейке 1 объединенные истоки коммутирующих МДП- транзисторов р-типа 3 и n-типа 6, которые функционально образуют КМОП-ключ, являются первым входом 10 в ячейку, в первой ячейке сдвигового регистра это соединение является, одновременно, и первым информационным входом сдвигового регистра 13 при выполнении операции сдвига логической единицы сигнала вправо. Объединенные стоки этих МДП-транзисторов соединены с объединенными затворами информационных МДП-транзисторов р-типа 2 и n-типа 5, которые функционально образуют КМОП-инвертор, и с объединенными стоками дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7, которые функционально образуют КМОП-ключ. Объединенные истоки этих дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7 образуют второй вход 11 ячейки и соединены с объединенными стоками информационных МДП-транзисторов р-типа 2 и n-типа 5, которые являются выходом КМОП-инвертора и одновременно выходом 12 последующей ячейки; в последней ячейке сдвигового регистра объединенные истоки дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7 являются, одновременно, и вторым информационным входом сдвигового регистра 14 при выполнении операции сдвига логической единицы сигнала влево. Вход первого дополнительного КМОП-инвертора, образованный соединением затворов первых дополнительных информационных МДТТ-транзисторов р-типа 25 и n-типа 26, соединен с первой тактовой шиной 17 в нечетной ячейке или со второй тактовой шиной 18 в четной ячейке; выход первого дополнительного КМОП-инвертора, образованный соединением стоков первых дополнительных информационных МДП-транзисторов р-типа 25 и n-типа 26, соединен с затвором коммутирующего МДП-транзистора n-типа 6.

Таким образом прямой тактовый сигнал ф1 с первой тактовой шины 17 в нечетной ячейке или прямой тактовый сигнал ф2 со второй тактовой шины 18 в четной ячейке без искажений поступает на затвор коммутирующего МДП-транзистора n-типа 6 в условиях существенных паразитных емкостей шин тактовых сигналов.

Затвор коммутирующего МДП-транзистора р-типа 3 соединен с выходом второго дополнительного КМОП-инвертора, образованным соединением стоков вторых дополнительных информационных МДП-транзисторов р-типа 27 и n-типа 28. Вход второго дополнительного КМОП-инвертора образован соединением затворов этих МДП-транзисторов и соединен с выходом третьего дополнительного КМОП-инвертора, образованным соединением стоков третьих дополнительных информационных МДП-транзисторов р-типа 29 и n-типа 30. Вход третьего дополнительного КМОП-инвертора образован соединением затворов этих МДП-транзисторов и соединен с первой тактовой шиной 17 в нечетной ячейке или со второй тактовой шиной 18 в четной ячейке.

Таким образом прямой тактовый сигнал ф1 с первой тактовой шины 17 в нечетной ячейке или прямой тактовый сигнал ф2 со второй тактовой шины 18 в четной ячейке, проходя третий дополнительный КМОП-инвертор, превращается в инверсный ф1* или ф2*, и проходя через второй дополнительный инвертор, без искажений поступает на затвор коммутирующего МДП-транзистора р-типа 3 в условиях существенных паразитных емкостей шин тактовых сигналов.

Вход четвертого дополнительного КМОП-инвертора, образованный соединением затворов четвертых дополнительных информационных МДП-транзисторов р-типа 31 и n-типа 32, соединен с третьей тактовой шиной 19 в нечетной ячейке или с четвертой тактовой шиной 20 в четной ячейке; выход четвертого дополнительного КМОП-инвертора, образованный соединением стоков четвертых дополнительных информационных МДП-транзисторов р-типа 31 и n-типа 32, соединен с затвором дополнительного коммутирующего МДП-транзистора n-типа 7.

Таким образом прямой тактовый сигнал ф3 с третьей тактовой шины 19 в нечетной ячейке или прямой тактовый сигнал ф4 с четвертой тактовой шиной 20 в четной ячейке без искажений поступает на затвор дополнительного коммутирующего МДП-транзистора n-типа 7 в условиях существенных паразитных емкостей шин тактовых сигналов.

Затвор дополнительного коммутирующего МДП-транзистора р-типа 4 соединен с выходом пятого дополнительного КМОП-инвертора, образованным соединением стоков пятых дополнительных информационных МДП-транзисторов р-типа 33 и n-типа 34. Вход пятого дополнительного КМОП-инвертора образован соединением затворов пятых дополнительных информационных МДП-транзисторов р-типа 33 и n-типа 34 и соединен с выходом шестого дополнительного КМОП-инвертора, образованным соединением стоков шестых дополнительных информационных МДП-транзисторов р-типа 35 и n-типа 36. Вход шестого дополнительного КМОП-инвертора образован соединением затворов шестых дополнительных информационных МДП-транзисторов р-типа 35 и n-типа 36 и соединен с третьей тактовой шиной 19 в нечетной ячейке или с четвертой тактовой шиной 20 в четной ячейке.

Таким образом прямой тактовый сигнал ф3 с третьей тактовой шины 19 в нечетной ячейке или прямой тактовый сигнал ф4 с четвертой тактовой шины 20 в четной ячейке, проходя шестой дополнительный КМОП-инвертор, превращается в инверсный ф3* или ф4*, и проходя через пятый дополнительный КМОП-инвертор, без искажений поступает на затвор коммутирующего МДП-транзистора р-типа 4 в условиях существенных паразитных емкостей шин тактовых сигналов.

Питание КМОП-инверторов осуществляется соединением истоков информационных МДП-транзисторов р-типа 2, 25, 27, 29, 31, 33 и 35 с шиной питания 8 и истоков информационных МДП-транзистора n-типа 5, 26, 28, 30, 32, 34 и 36 с шиной нулевого потенциала 9. Выход 12 первой ячейки сдвигового регистра является, одновременно, вторым информационным выходом 16 сдвигового регистра, выход 12 последней ячейки сдвигового регистра является, одновременно, первым информационным выходом 15 сдвигового регистра.

На фиг.4а приведена временная диаграмма работы первого варианта сдвигового регистра при выполнении операции сдвига логической единицы вправо (сдвиг информации слева направо), где

37 - сигнал на первом информационном входе сдвигового регистра 13,

38, 39 - сигналы (ф1, ф2) на первой 17 и второй 18 тактовых шинах, соответственно,

40, 41, 42, 43, 44, 45 - сигналы на выходах 12 первой, второй, третьей, четвертой и предпоследней и последней четной ячейки сдвигового регистра, соответственно. Сигналы (ф1* и ф2*) на третьей 19 и четвертой 20 тактовых шинах, которые имеют инверсное значение сигналам (ф1 и ф2) на первой 17 и второй 18 тактовых шинах на диаграмме не изображены, чтобы не усложнять наглядность принципа работы сдвигового регистра.

На фиг.4б приведена временная диаграмма работы первого варианта сдвигового регистра при выполнении операции сдвига логической единицы влево (сдвиг информации справа налево), где

46 - сигнал на втором информационном входе сдвигового регистра 14,

47, 48 - сигналы (ф3, ф2) на пятой 21 и второй 18 тактовых шинах, соответственно;

49 - сигнал на выходе 12 первой от начала сдвигового регистра ячейки,

50 - сигнал на выходе 12 второй от начала сдвигового регистра ячейки (этот выход является одновременно вторым информационным выходом 16 сдвигового регистра);

51 и 52 - сигналы на выходах 12 предпоследней нечетной и предпоследней четной ячеек сдвигового регистра,

53 и 54 - сигналы на выходах 12 последней нечетной и последней четной ячеек сдвигового регистра, соответственно. Сигналы (ф3* и ф2*) на шестой 22 и четвертой 20 тактовых шинах, которые имеют инверсное значение сигналам (ф3, ф2) на пятой 21 и второй 18 тактовых шинах на диаграмме не изображены, чтобы не усложнять наглядность принципа работы сдвигового регистра.

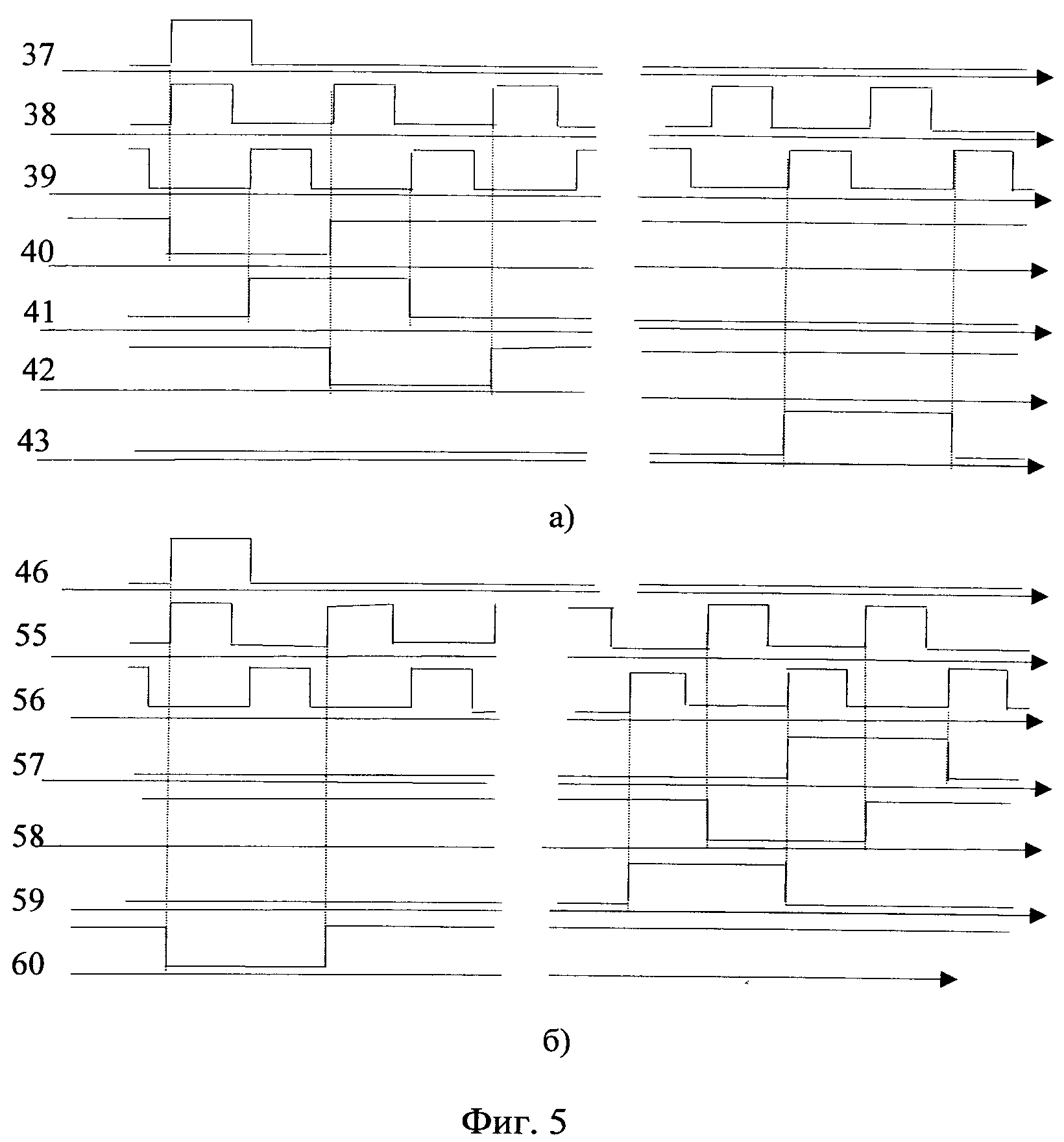

На фиг.5 а приведена временная диаграмма работы второго варианта сдвигового регистра при выполнении операции сдвига логической единицы вправо (сдвиг информации слева направо), где

37 - сигнал на первом информационном входе сдвигового регистра 13,

38, 39 - сигналы (ф1, ф2) на первой 17 и второй 18 тактовых шинах, соответственно,

40, 41, 42, 43 - сигналы на выходе 12 первой, второй, третьей и четвертой (последней четной) ячейки сдвигового регистра, соответственно. Выход 12 последней четной ячейки сдвигового регистра является одновременно первым информационным выходом сдвигового регистра 15. Сигналы (ф1* и ф2*) на третьей 19 и четвертой 20 тактовых шинах, которые имеют инверсное значение сигналам (ф1, ф2) на первой 17 и второй 18 тактовых шинах, на диаграмме не изображены, чтобы не усложнять наглядность принципа работы сдвигового регистра.

На фиг.5б приведена временная диаграмма работы второго варианта сдвигового регистра при выполнении операции сдвига логической единицы влево (сдвиг информации справа налево), где

46 - сигнал на втором информационном входе сдвигового регистра 14,

55, 56 - сигналы (ф4, ф3) на седьмой 23 и пятой 21 тактовых шинах, соответственно,

57, 58, 59, 60 - сигналы на втором информационном выходе сдвигового регистра 16, который одновременно является и выходом 12 первой ячейки, и на выходах 12 второй, третьей и четвертой (последней четной ячейки сдвигового регистра) ячеек, соответственно. Сигналы (ф4* и ф3*) на восьмой 24 и шестой 22 тактовых шинах, которые имеют инверсное значение сигналам (ф4, ф3) на седьмой 23 и пятой 21 тактовых шинах, на диаграмме не изображены, чтобы не усложнять наглядность принципа работы сдвигового регистра.

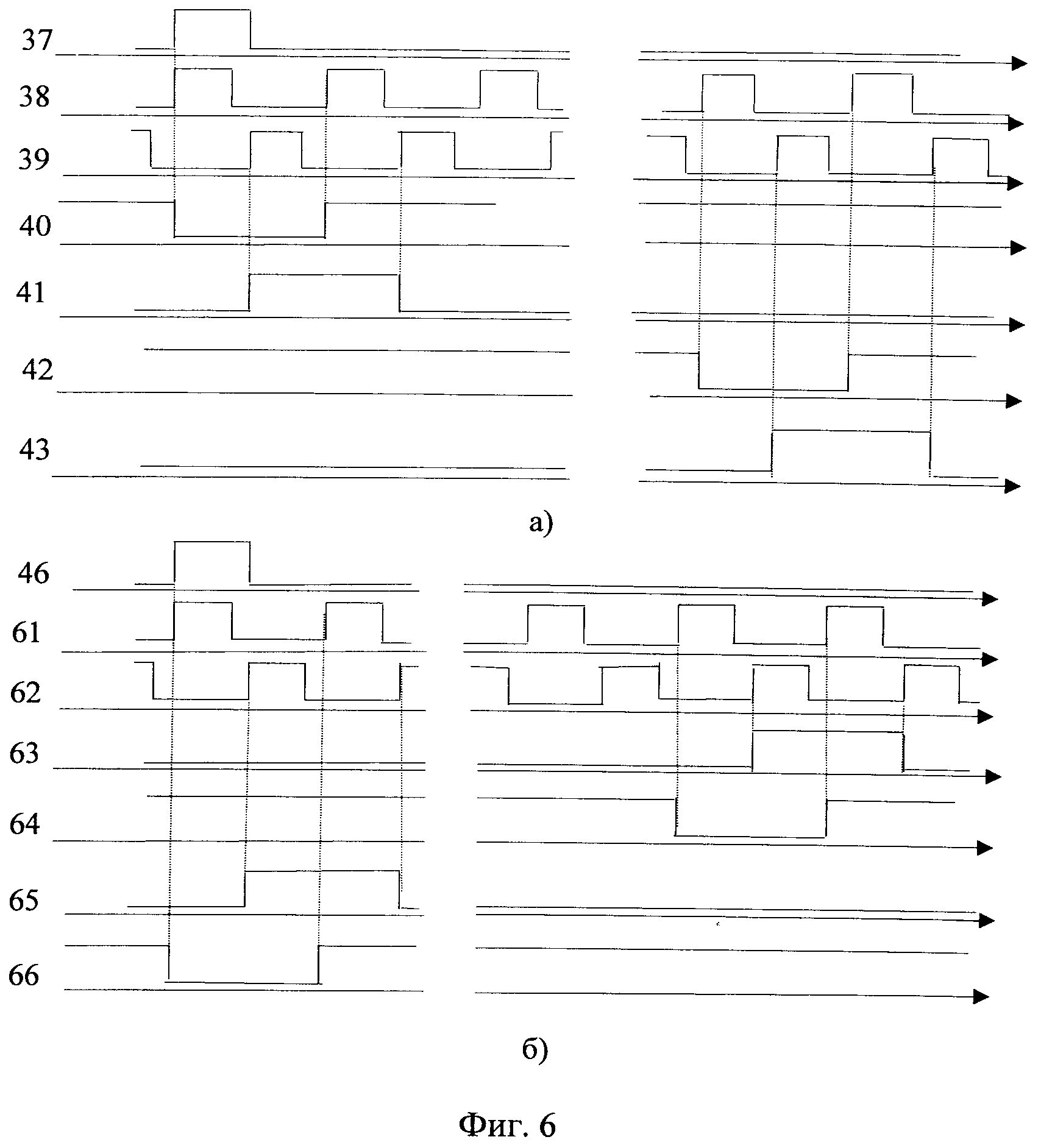

На фиг.6а приведена временная диаграмма работы третьего варианта сдвигового регистра при выполнении операции сдвига логической единицы вправо (сдвиг информации слева направо), где

37 - сигнал на первом информационном входе сдвигового регистра 13,

38, 39 - сигналы (ф1, ф2) на первой 17 и второй 18 тактовых шинах, соответственно,

40, 41, 42, 43 - сигналы на выходе 12 первой, второй и предпоследней и последней (в нашем случае четной) ячеек сдвигового регистра.

На фиг.6б приведена временная диаграмма работы третьего варианта сдвигового регистра при выполнении операции сдвига логической единицы влево (сдвиг информации справа налево), где

46 - сигнал на втором входе сдвигового регистра 14,

61, 62 - сигналы (ф4, ф3) на тактовых шинах четвертой 20 и третьей 19, соответственно;

63, 64, 65, 66 - сигналы на выходе 12 первой, второй и предпоследней и последней (в нашем случае четной) ячеек сдвигового регистра, соответственно.

Рассмотрим работу сдвигового регистра.

Первый вариант сдвигового регистра (фиг.1.) работает следующим образом при выполнении операции сдвига сигнала в виде логической единицы вправо (считывание информации слева направо, фиг.4а).

В исходном положении на первом входе 10 и втором входе 11 первой ячейки 1 сдвигового регистра нулевой потенциал. Первая логическая единица сигнала 38 и инверсный ему сигнал, которые приходят по первой тактовой шине 17 и третьей тактовой шине 19, открывают коммутирующие МДП-транзисторы р-типа 3 и n-типа 6 первой и всех последующих нечетных ячеек. Если на первый информационный вход сдвигового регистра 13 поступает логическая единица сигнала 37, то на выходе 12 первой ячейки сдвигового регистра устанавливается логический ноль сигнала 40, т.к. сигнал 37 проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 этой ячейки. Логический ноль сигнала 40 на выходе 12 первой ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 38 и заканчивается приходом второй единицы сигнала 38 (фиг.4а). Первая логическая единица сигнала 39 и инверсный ему сигнал, которые приходят по второй тактовой шине 18 и по четвертой тактовой шине 20, открывают коммутирующие МДП-транзисторы р-типа 3 и n-типа 6 второй ячейки и всех последующих четных ячеек (фиг.1.). На выходе 12 второй от начала сдвигового регистра ячейки устанавливается логическая единица сигнала 41, т.к. логический ноль с выхода 12 первой ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 второй ячейки. Логическая единица сигнала 41 на выходе 12 второй ячейки начинается с прихода первой логической единицы сигнала 39 и заканчивается приходом второй логической единицы сигнала 39 (фиг.4а). Далее, с приходом следующей логической единицы сигнала 38 логическая единица сигнала 41 с выхода 12 второй ячейки поступает на затворы информационных МДП-транзисторов р-типа 2 и n-типа 5 третьей ячейки, т.е. вход КМОП-инвертора третьей ячейки, на выходе которой устанавливается логический ноль сигнала 42, т.к. выход КМОП-инвертора является выходом 12 ячейки. С приходом второй логической единицы сигнала 39 на выходе 12 четвертой ячейки формируется логическая единица сигнала 43, т.к. логический ноль с выхода 12 третьей ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 четвертой ячейки. Логическая единица сигнала 43 на выходе 12 четвертой ячейки начинается с прихода второй логической единицы сигнала 39 и заканчивается приходом третьей логической единицы сигнала 39. Таким образом, сигнал 37 с первого информационного входа сдвигового регистра 13, т.е. с первого входа 10 первой ячейки сдвигового регистра, достигает первого информационного выхода сдвигового регистра 15, т.е. выхода 12 последней четной ячейки сдвигового регистра, двигаясь слева направо и образуя сигнал 45 с приходом логического нуля сигнала 44 с выхода 12 предпоследней ячейки сдвигового регистра. На первом информационном выходе 15 сдвигового регистра, например из десяти ячеек, логическая единица сигнала 45 начинается с прихода пятой логической единицы сигнала 39 и заканчивается с приходом шестой логической единицы сигнала 39.

Итак, логическая единица сигнала считывается с выхода каждой четной ячейки сдвигового регистра.

Питание КМОП-инверторов осуществляется соединением истока информационного МДП-транзистора р-типа 2 с шиной питания 8 и истока информационного МДП-транзистора n-типа 5 с шиной нулевого потенциала 9.

При операции сдвига сигнала влево первый вариант сдвигового регистра (фиг.1.) работает аналогично операции сдвига сигнала вправо. Временная диаграмма операции сдвига влево приведена на фиг.4б.

С приходом первой логической единицы сигнала 47 и инверсного ему сигналу по пятой тактовой шине 21 и по шестой тактовой шине 22 открываются дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7 последней и всех предыдущих нечетных ячеек 1. Если на второй информационный вход сдвигового регистра 14 поступает логическая единица сигнала 46, то на выходе 12 последней нечетной ячейки устанавливается логический ноль сигнала 54, т.к. сигнал 46 проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 этой ячейки. Логический ноль сигнала 54 на выходе 12 последней нечетной ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 47 и заканчивается приходом второй единицы сигнала 47 (фиг.4б). Далее, с приходом первой логической единицы сигнала 48 и его инверсии по второй 18 и четвертой 20 тактовым шинам открываются коммутирующие МДП-транзисторы р-типа 3 и п-типа 6 последней четной ячейки и всех предыдущих четных ячеек. На выходе 12 последней четной ячейки устанавливается логическая единица сигнала 53, т.к. логический ноль с выхода 12 последней нечетной ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 последней четной ячейки. Логическая единица сигнала 53 на выходе 12 последней четной ячейки начинается с прихода первой логической единицы сигнала 48 и заканчивается приходом второй логической единицы сигнала 48. Далее с приходом следующей логической единицы сигнала 47 логическая единица сигнала с выхода 12 последней четной ячейки поступает на объединенные истоки дополнительных коммутирующих МДП-транзисторов р-типа 4 и n-типа 7, т.е. на второй 11 вход второй от конца сдвигового регистра нечетной ячейки. КМОП-ключ, функционально образованный дополнительными коммутирующими МДП-транзисторами р-типа 4 и n-типа 7, передает полученную логическую единицу сигнала на вход КМОП-инвертора, т.е. на затворы информационных МДП-транзисторов р-типа 2 и n-типа 5 своей ячейки, на выходе КМОП-инвертора, а значит и выходе ячейки устанавливается логический ноль сигнала 52. С приходом второй логической единицы сигнала 48 на выходе 12 второй от конца четной ячейки начинается логическая единица сигнала 51, т.к. логический ноль с выхода 12 второй от конца сдвигового регистра нечетной ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 третьей от конца сдвигового регистра ячейки. Логическая единица сигнала 51 на выходе 12 третьей от конца сдвигового регистра ячейки начинается с приходом второй логической единицы сигнала 48 и заканчивается приходом третьей логической единицы сигнала 48. Таким образом, логическая единица сигнала 46 со второго информационного входа сдвигового регистра 14, т.е. со второго 11 входа последней нечетной ячейки, достигает второго информационного выхода 16 сдвигового регистра, т.е. выхода 12 первой четной ячейки, двигаясь слева направо и образуя сигнал 49 с приходом логического нуля сигнала 50 с выхода 12 первой от начала сдвигового регистра ячейки. На втором информационном выходе сдвигового регистра 16 из десяти ячеек, например, логическая единица сигнала 49 будет начинаться с прихода пятой логической единицы сигнала 48 и закончится приходом шестой логической единицы сигнала 48.

Итак, логическая единица сигнала считывается с выхода каждой четной ячейки сдвигового регистра.

Питание КМОП-инверторов осуществляется соединением истока информационного МДП-транзистора р-типа 2 с шиной питания 8 и истока информационного МДП-транзистора n-типа 5 с шиной нулевого потенциала 9.

Второй вариант сдвигового регистра (фиг.2.) работает следующим образом при выполнении операции сдвига сигнала в виде логической единицы вправо (считывание информации слева направо, фиг.5а).

В исходном положении на первом 10 и втором 11 входах первой ячейки сдвигового регистра нулевой потенциал. Первая логическая единица сигнала 38 и инверсный ему сигнал, которые приходят по первой 17 и третьей 19 тактовым шинам, открывают коммутирующие МДП-транзисторы р-типа 3 и n-типа 6 первой и всех последующих нечетных ячеек 1. (фиг.2.) Если на первый информационный вход сдвигового регистра 13 поступает логическая единица сигнала 37, то на выходе 12 первой ячейки устанавливается логический ноль сигнала 40, т.к. сигнал 37 проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 первой ячейки. Логический ноль сигнала 40 на выходе 12 первой ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 38 и заканчивается приходом второй единицы сигнала 38 (фиг.5а). Первая логическая единица сигнала 39 и инверсный ему сигнал, которые приходят по второй 18 и четвертой 20 тактовым шинам, открывают коммутирующие МДП-транзисторы р-типа 3 и n-типа 6 второй ячейки и всех последующих четных ячеек. На выходе 12 второй ячейки устанавливается логическая единица сигнала 41, т.к. логический ноль с выхода 12 первой ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 второй ячейки. Логическая единица сигнала 41 на выходе 12 второй ячейки начинается с прихода первой логической единицы сигнала 39 и заканчивается приходом второй логической единицы сигнала 39. Далее, с приходом второй логической единицы сигнала 38 логическая единица сигнала 41 с выхода 12 второй ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 третьей ячейки, на выходе 12 которой устанавливается логический ноль сигнала 42. С приходом второй логической единицы сигнала 39 на выходе 12 четвертой ячейки формируется логическая единица сигнала 43, т.к. логический ноль с выхода 12 третьей ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 четвертой ячейки. Логическая единица сигнала 43 на выходе 12 четвертой ячейки начинается с прихода второй логической единицы сигнала 39 и заканчивается приходом третьей логической единицы сигнала 39. Таким образом, сигнал 37 с первого информационного входа сдвигового регистра 13, или с первого входа 10 первой ячейки, достигает первого информационного выхода сдвигового регистра 15, или выхода 12 последней четной ячейки сдвигового регистра, двигаясь слева направо. На первом информационном выходе 15 сдвигового регистра, например из десяти ячеек, логическая единица сигнала 43 начинается с прихода пятой логической единицы сигнала 39 и заканчивается с приходом шестой логической единицы сигнала 39. (фиг.5а).

Итак, логическая единица сигнала считывается с выхода каждой четной ячейки сдвигового регистра.

Питание КМОП-инверторов осуществляется соединением истока информационного МДП-транзистора р-типа 2 с шиной питания 8 и истока информационного МДП-транзистора n-типа 5 с шиной нулевого потенциала 9.

При операции сдвига информации влево второй вариант сдвигового регистра (фиг.2.) работает аналогично операции сдвига вправо. Временная диаграмма операции сдвига влево приведена на фиг.5б.

С приходом первой логической единицы сигнала 55 и инверсного ему сигналу по седьмой 23 и восьмой 24 тактовым шинам открываются дополнительные МДП-транзисторы р-типа 4 и n-типа 7 последней и всех предыдущих четных ячеек 1. Если на второй информационный вход сдвигового регистра 14 поступает логическая единица сигнала 46, то на выходе 12 последней четной ячейки устанавливается логически ноль сигнала 60, т.к. сигнал проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 последней четной ячейки. Логический ноль сигнала 60 на выходе 12 последней четной ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 55 и заканчивается приходом второй единицы сигнала 55 (фиг.5б). Далее, с приходом первой логической единицы сигнала 56 и его инверсии по пятой 21 и шестой 22 тактовым шинам открываются дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7 последней нечетной ячейки и всех предыдущих нечетных ячеек. На выходе 12 последней нечетной ячейки устанавливается логическая единица сигнала 59, т.к. логический ноль сигнала 60 с выхода 12 последней четной ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 последней нечетной ячейки сдвигового регистра. Логическая единица сигнала 59 на выходе 12 последней нечетной ячейки начинается с прихода первой логической единицы сигнала 56 и заканчивается приходом второй логической единицы сигнала 56. Далее с приходом следующей логической единицы сигнала 55 логическая единица сигнала с выхода 12 последней нечетной ячейки поступает на затворы информационных МДП-транзисторов р-типа 2 и n-типа 5 третьей от конца ячейки, на выходе которой устанавливается логический ноль сигнала 58. С приходом второй логической единицы сигнала 56 на выходе 12 четвертой от конца ячейки начинается логическая единица сигнала 57, т.к. логический ноль сигнала 58 с выхода 12 третьей ячейки проходит КМОП-инвертор, функционально образованный информационными МДП-транзисторами р-типа 2 и n-типа 5 четвертой от конца ячейки. Логическая единица сигнала 57 на выходе 12 четвертой от конца ячейки начинается с приходом второй логической единицы сигнала 56 и заканчивается приходом третьей логической единицы сигнала 56. Таким образом, логическая единица сигнала 46 со второго информационного входа сдвигового регистра 14 достигает второго информационного выхода сдвигового регистра 16, или выхода 12 первой ячейки сдвигового регистра, двигаясь слева направо. На втором информационном выходе 16 сдвигового регистра из десяти ячеек, например, логическая единица сигнала 57 будет начинаться с прихода пятой логической единицы сигнала 56 и закончится приходом шестой логической единицы сигнала 56.

Итак, логическая единица сигнала считывается с выхода каждой нечетной ячейки сдвигового регистра.

Питание КМОП-инверторов осуществляется соединением истока информационного МДП-транзистора р-типа 2 с шиной питания 8 и истока информационного МДП-транзистора n-типа 5 с шиной нулевого потенциала 9.

Рассмотрим работу третьего варианта сдвигового регистра.

Третий вариант сдвигового регистра (фиг.3.) работает следующим образом при выполнении операции сдвига логической единицы сигнала вправо (считывание информации слева направо, фиг.6а).

В исходном положении на первом информационном входе 13 и втором информационном входе 14 сдвигового регистра, на первом входе 10 и на втором входе 11 первой ячейки сдвигового регистра нулевой потенциал. Первая логическая единица сигнала 38, которая поступит по первой тактовой шине 17, пройдя через первый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 25 и n-типа 26, откроет коммутирующий МДП-транзистор n-типа 6а, пройдя через третий дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 29 и n-типа 30, и второй дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 27 и n-типа 28, откроет коммутирующий МДП-транзистор р-типа 3 первой и всех нечетных ячеек 1 сдвигового регистра. (фиг.3.) Если на первый информационный вход сдвигового регистра 13 поступает логическая единица сигнала 37, то, пройдя через КМОП-инвертор первой ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5, на выходе 12 первой ячейки устанавливается логический ноль сигнала 40. Логический ноль сигнала 40 на выходе 12 первой ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 38 и заканчивается приходом второй единицы сигнала 38 (фиг.6а). Далее с приходом первой логической единицы сигнала 39, который поступит по второй тактовой шине 18, пройдя через первый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 25 и n-типа 26, откроется коммутирующий МДП-транзистор n-типа 6 и, пройдя через третий дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 29 и n-типа 30, и второй дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 27 и n-типа 28, откроется коммутирующий МДП-транзистор р-типа 3 второй и всех четных ячеек сдвигового регистра. Логический ноль с выхода 12 первой ячейки поступит на вход КМОП-инвертора второй ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5 этой ячейки, и на его выходе, а значит и выходе 12 второй ячейки, установится логическая единица сигнала 41. Логическая единица сигнала 41 на выходе 12 второй ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 39 и заканчивается с приходом второй логической единицы сигнала 39. Далее с приходом второй логической единицы сигнала 38 логическая единица сигнала 41 с выхода 12 второй ячейки поступит через открывшийся КМОП-ключ третьей ячейки, функционально образованный коммутирующими МДП-транзисторами р-типа 3 и n-типа 6, на вход КМОП-инвертора третьей ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5 и на входе которого, а значит и выходе 12 третьей ячейки, установится логический ноль сигнала 42. С приходом второй логической единицы сигнала 39, который поступит по второй тактовой шине 18, пройдя через первый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 25 и n-типа 26, откроет коммутирующий МДП-транзистор п-типа 6 а, пройдя через третий дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 29 и n-типа 30, и второй дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 27 и n-типа 28, откроет коммутирующий МДП-транзистор р-типа 3 четвертой и всех четных ячеек сдвигового регистра. Логический ноль сигнала 42 с выхода 12 третьей ячейки поступит на вход КМОП-инвертора четвертой ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5, и на его выходе, а значит и выходе 12 четвертой ячейки, установится логическая единица сигнала 43. Логическая единица сигнала 43 на выходе 12 четвертой ячейки сдвигового регистра начинается с прихода второй логической единицы сигнала 39 и заканчивается с приходом третьей логической единицы сигнала 39. Так логическая единица сигнала 37 с первого информационного входа сдвигового регистра 13, или первого входа 10 первой ячейки, достигает первого информационного выхода сдвигового регистра 15 или выхода 12 последней (четной в нашем случае) ячейки, двигаясь слева направо и образуя сигнал 43 (фиг.6а). На первом информационном выходе 15 сдвигового регистра, например из десяти ячеек, логическая единица сигнала 43 начинается с прихода пятой логической единицы сигнала 39 и заканчивается с приходом шестой логической единицы сигнала 39. (фиг.6а).

Второй информационный вход 14 сдвигового регистра и второй информационный выход 16 сдвигового регистра в операции сдвига информации вправо не участвуют.

Питание КМОП-инверторов осуществляется соединением истоков информационных МДП-транзисторов р-типа 2, 25, 27, 29, 31, 33 и 35 с шиной питания 8 и истоков информационных МДП-транзисторов n-типа 5, 26, 28, 30, 32, 34, и 36 с шиной нулевого потенциала 9.

При операции сдвига информации влево третий вариант сдвигового регистра работает аналогично операции сдвига вправо. Временная диаграмма операции сдвига информации влево приведена на фиг.6б.

С приходом первой логической единицы сигнала 61, которая поступит по четвертой тактовой шине 20, пройдя через шестой дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 35 и n-типа 36, и пятый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 33 и n-типа 34, и пройдя четвертый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 31 и n-типа 32, откроются допонительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, которые функционально образуют КМОП-ключ, последней и всех предстоящих четных ячеек 1 сдвигового регистра. Если на второй информационный вход 14 сдвигового регистра, т.е. на второй вход 11 последней ячейки сдвигового регистра, поступает логическая единица сигнала 46, то, пройдя через открытые допонительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7 и через КМОП-инвертор последней ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5, на выходе 12 последней ячейки устанавливается логический ноль сигнала 66. Логический ноль сигнала 66 на выходе 12 последней четной ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 61 и заканчивается приходом второй единицы сигнала 61 (фиг.6б). Далее с приходом первой логической единицы сигнала 62, который поступит по третьей тактовой шине 19, пройдя через шестой дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 35 и n-типа 36, и пятый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 33 и n-типа 34, и пройдя четвертый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 31 и n-типа 32, откроются дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, которые функционально образуют КМОП-ключ, предпоследней и всех предстоящих нечетных ячеек сдвигового регистра. Логический ноль с выхода 12 последней ячейки поступит через открытые дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, т.е. открытый КМОП-ключ, на вход КМОП-инвертора предпоследней ячейки, который образован информационными МДП-транзисторами р-типа 2 и n-типа 5, и на его выходе, а значит и выходе 12 предпоследней ячейки, установится логическая единица сигнала 65 (фиг.66). Логическая единица сигнала 65 на выходе 12 предпоследней ячейки сдвигового регистра начинается с прихода первой логической единицы сигнала 62 и заканчивается с приходом второй логической единицы сигнала 62. С приходом второй логической единицы сигнала 61, которая поступит по четвертой тактовой шине 20, пройдя через шестой дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 35 и n-типа 36, и пятый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 33 и n-типа 34, и пройдя четвертый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 31 и n-типа 32, откроются дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, которые функционально образуют КМОП-ключ, третьей от конца и всех предстоящих четных ячеек сдвигового регистра. Логическая единица сигнала с выхода 12 предпоследней ячейки поступит через открытые дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, т.е. открытый КМОП-ключ, на вход КМОП-инвертора третьей от конца ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5, и на его выходе, а значит и выходе 12 третьей от конца сдвигового регистра ячейки, установится логический ноль сигнала 64.

Далее с приходом второй логической единицы сигнала 62, которая поступит по третьей тактовой шине 19, пройдя через шестой дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 35 и n-типа 36, и пятый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 33 и n-типа 34, и пройдя четвертый дополнительный КМОП-инвертор, который функционально образован дополнительными информационными МДП-транзисторами р-типа 31 и n-типа 32, откроются дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, которые функционально образуют КМОП-ключ четвертой от конца сдвигового регистра. Логический ноль с выхода 12 третьей от конца сдвигового регистра ячейки поступит через открытые дополнительные коммутирующие МДП-транзисторы р-типа 4 и n-типа 7, т.е. открытый КМОП-ключ, на вход КМОП-инвертора четвертой от конца сдвигового регистра ячейки, который функционально образован информационными МДП-транзисторами р-типа 2 и n-типа 5, и на его выходе, а значит и выходе 12 четвертой от конца сдвигового регистра ячейки, установится логическая единица сигнала 63.

Логическая единица сигнала 63 на выходе 12 четвертой от конца сдвигового регистра ячейки (на фиг.3 первая ячейка от начала сдвигового регистра и значит ее выход 12, одновременно, является вторым информационным выходом 16 сдвигового регистра) начинается с прихода второй логической единицы сигнала 62 и заканчивается с приходом третьей логической единицы сигнала 62. На втором информационном выходе 16 сдвигового регистра из десяти ячеек, например, логическая единица сигнала 63 будет начинаться с прихода пятой логической единицы сигнала 62 и закончится приходом шестой логической единицы сигнала 62.

Первый вход 10 ячейки, первый информационный вход 13 сдвигового регистра и первый информационный выход 15 сдвигового регистра в операции сдвига информации влево не участвуют.

Питание КМОП-инверторов осуществляется соединением истоков информационных МДП-транзисторов р-типа 2, 25, 27, 29, 31, 33 и 35 с шиной питания 8 и истоков информационных МДП-транзисторов n-типа 5, 26, 28, 30, 32, 34, и 36 с шиной нулевого потенциала 9.