Результат интеллектуальной деятельности: СДВИГОВЫЙ РЕГИСТР

Вид РИД

Изобретение

Изобретение относится к оптоэлектронике и микроэлектронике и может быть использовано для построения сдвиговых регистров в фотоприемных субмодулях для мозаичных фотоприемников, в частности, в фотоприемниках на микроболометрах.

Известен сдвиговый регистр (Патент РФ на изобретение №2344498 «Сдвиговый регистр» МПК: G11С 19/00, Н03К 3/037, Н03К 9/001, опубликован 20.01.2009 г.), который выполнен на элементах И, ИЛИ, НЕ, содержащий в каждом разряде первый и второй RS-триггеры, четыре логических элемента И, один элемент ИЛИ, информационный вход, первую и вторую шины управления приемом кода в первый и второй триггеры при выполнении операции сдвига кода, информационный выход, при этом выходы первого и третьего элементов И соединены с R-входами первого и второго RS-триггеров соответственно, выход второго элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с информационным входом, а выход упомянутого элемента ИЛИ подключен к S-входу первого триггера, первые входы первого и второго элементов И связаны с первой шиной управления приемом кода в первый триггер, первые входы третьего и четвертого элементов И соединены с второй шиной управления приемом кода во второй триггер, причем нулевой и единичный выходы первого триггера i-го разряда соединены с вторыми входами третьего и четвертого элементов И (i+1)-го разряда соответственно, нулевой и единичный выходы второго триггера i-го разряда соединены со вторыми входами первого и второго элементов И (i+1)-го разряда соответственно, кроме того, первый и второй входы второго элемента ИЛИ соединены с S-входами первого и второго триггеров, выход упомянутого элемента ИЛИ является информационным выходом i-го разряда и т.д.

Недостатком этого сдвигового регистра является необходимость использования в каждом разряде двух RS-триггеров, что увеличивает аппаратурные затраты и повышает потребление энергопитания.

Известен реверсивный сдвиговой регистр (Патент РФ на изобретение №2022372 «Реверсивный регистр сдвига», МПК: G11С 19/00, опубликован 30.10.1994 г.) Сущность которого состоит в том, что он содержит в каждом разряде JK-триггер, четыре элемента И, в каждом разряде, кроме первого и последнего, четыре элемента ИЛИ, в первом и последнем разрядах - три элемента ИЛИ, шины управления направлением сдвига вправо и влево, вход сброса регистра, вход сдвига, прямой и инверсный информационные входы регистра и выход информации в прямом последовательном коде при сдвиге вправо, прямой и инверсный информационные парафазные входы регистра и выход информации в прямом последовательном коде при сдвиге влево, вход управления режимом сдвига - уплотнение единиц и вход управления режимом сдвига - уплотнение нулей, причем прямой выход JK-триггера каждого разряда, кроме последнего, соединен соответственно с первым входом первого элемента И последующего разряда, а прямой выход JK-триггера каждого разряда, кроме первого, соединен соответственно с первым входом второго элемента И предыдущего разряда, выходы первого и второго элементов И каждого разряда соединены с входами первого элемента ИЛИ, вход которого соединен с J-входом JK-триггера данного разряда, вторые входы первого и второго элементов И всех разрядов являются соответственно входами управления сдвигом вправо и сдвигом влево регистра и т.д. Введение в известный сдвиговой регистр в каждый разряд, кроме первого и последнего, двух элементов ИЛИ (пятого и шестого), в первую ячейку пятого элемента ИЛИ, в последнюю ячейку шестого элемента ИЛИ, а также новых связей позволяет расширить функциональные возможности реверсивного регистра сдвига за счет уплотнения нулей кодовой комбинации как влево, так и вправо регистра.

Недостатком этого реверсивного сдвигового регистра, как и предыдущего, является то, что он имеет сложную структуру и управление, состоит из большого количества транзисторов и вследствие этого при использовании в качестве блока адресации по вертикали в мозаичных фотоприемниках приводит к падению эффективности преобразования изображений в мозаичном фотоприемнике в целом. (Эффективность преобразования изображений - это отношение количества работающих фоточувствительных элементов (ФЧЭ) в мозаичном фотоприемнике к сумме ФЧЭ, потерянных в «слепых зонах» и работающих в мозаичном фотоприемнике).

Известен регистр сдвига на МДП-транзисторах (Авторское свидетельство №1269210, МПК: G11С 19/00 опубликованное 07.11.1986 г.), в котором выход каждого из инверторов, составляющих регистр, через коммутирующие транзисторы соединен с входами последующего и предыдущего инверторов. При этом во время первого такта работы сдвигового регистра образуются триггеры, состоящие из четного и последующего нечетного инверторов, а во время второго такта работы - из четного и предыдущего нечетного инверторов.

Недостатком этого регистра сдвига на МДП-транзисторах является то, что он требует большого количества тактовых шин для управляющих сигналов и сложную диаграмму управляющих сигналов, что усложняет технологию его изготовления, снижает быстродействие, повышает стоимость устройства и существенно понижает эффективность мозаичного фотоприемника в целом.

Известен также сдвиговый регистр, принятый за прототип, приведенный в статье С.Я. Андрюшина, Н.В. Кравченко и др. Состояние разработок микроболометрических матриц в Государственном научном центре РФ «НПО «Орион», Прикладная физика, №5, 2000, стр.9, рис.2. Сдвиговый регистр содержит ячейки, каждая из которых состоит из трех n-МОП транзисторов, двух емкостей, двух тактовых шин питания и шины нулевого потенциала, причем в каждой ячейке исток коммутирующего n-МОП транзистора является входом в ячейку, а в первой ячейке сдвигового регистра и информационным входом сдвигового регистра при сдвиге информации вправо, его затвор соединен с затвором нагрузочного n-МОП транзистора и с первой шиной тактового питания в нечетной ячейке, а в четной ячейке - со второй шиной тактового питания, сток коммутирующего n-МОП транзистора соединен с затвором информационного n-МОП транзистора и обкладкой первой емкости; другая обкладка которой соединена с обкладкой второй емкости и со стоком нагрузочного и с истоком информационного n-МОП транзисторов и является выходом ячейки, а в последней ячейке сдвигового регистра и информационным выходом сдвигового регистра одновременно, исток нагрузочного n-МОП транзистора и другая обкладка второй емкости соединены с шиной нулевого потенциала, сток информационного n-МОП транзистора соединен со второй шиной тактового питания в нечетной ячейке или с первой шиной тактового питания в четной ячейке.

Этот сдвиговый регистр, принятый за прототип, содержит меньшее количество шин и n-МОП транзисторов, выполнен по менее сложной технологии, по сравнению с известными аналогами, но имеет существенный недостаток, а именно, сдвигает информацию только в одну сторону.

Техническим результатом изобретения является:

- расширение функциональных возможностей за счет обеспечения реверсивности сдвига информации внутри сдвигового регистра,

- расширение области применения за счет возможности двунаправленной передачи информации,

- минимизация занимаемой площади кристалла БИС.

Технический результат достигается тем, что в сдвиговом регистре, содержащем ячейки, каждая из которых состоит из трех n-МОП транзисторов, двух емкостей, двух шин тактового питания и шины нулевого потенциала, причем в каждой ячейке исток коммутирующего n-МОП транзистора является входом в ячейку, а в первой ячейке сдвигового регистра и первым информационным входом сдвигового регистра при сдвиге информации вправо его затвор соединен с затвором нагрузочного n-МОП транзистора и с первой шиной тактового питания в нечетной ячейке, а в четной ячейке соединен со второй шиной тактового питания, сток коммутирующего n-МОП транзистора соединен с затвором информационного n-МОП транзистора и обкладкой первой емкости; другая обкладка которой соединена с обкладкой второй емкости и со стоком нагрузочного и с истоком информационного n-МОП транзисторов и является выходом ячейки, а в последней ячейке сдвигового регистра и первым информационным выходом сдвигового регистра одновременно исток нагрузочного n-МОП транзистора и другая обкладка второй емкости соединены с шиной нулевого потенциала, сток информационного n-МОП транзистора соединен со второй шиной тактового питания в нечетной ячейке или с первой шиной тактового питания в четной ячейке, при этом в каждую ячейку введены третья шина тактового питания, второй коммутирующий и второй нагрузочный n-МОП транзисторы, причем исток второго коммутирующего n-МОП транзистора соединен со стоком первого коммутирующего и затвором информационного n-МОП транзисторов; затвор второго коммутирующего n-МОП транзистора соединен с затвором второго нагрузочного n-МОП транзистора и с третьей шиной тактового питания в нечетной ячейке или с затворами первого коммутирующего и первого нагрузочного n-МОП транзисторов в четной ячейке, сток второго коммутирующего n-МОП транзистора соединен с выходом следующей ячейки, а в последней ячейке сдвигового регистра образует второй информационный вход сдвигового регистра при считывании информации справа налево; исток второго нагрузочного n-МОП транзистора соединен с шиной нулевого потенциала в нечетной ячейке, или с выходом своей же ячейки в четной ячейке; его сток соединен с выходом своей ячейки в нечетной ячейке или с третьей шиной тактового питания в четной ячейке, а его затвор в четной ячейке соединен с затвором информационного n-МОП транзистора, выход первой ячейки является одновременно вторым информационным выходом сдвигового регистра при считывании информации справа налево.

Предлагаемый сдвиговый регистр позволяет расширить область его применения за счет возможности двунаправленной передачи информации путем введения в каждую ячейку дополнительно двух n-МОП - транзисторов, третьей шины тактового питания и дополнительных связей.

Минимизация площади кристалла происходит при уменьшении размера ячейки сдвигового регистра перпендикулярно направлению сдвига информации при заданном размере вдоль направления сдвига. Минимизация размера ячейки сдвигового регистра перпендикулярно направлению сдвига информации становится возможной в основном при уменьшении числа тактовых шин в схеме сдвигового регистра.

Сущность изобретения поясняется нижеследующим описанием и прилагаемыми фигурами.

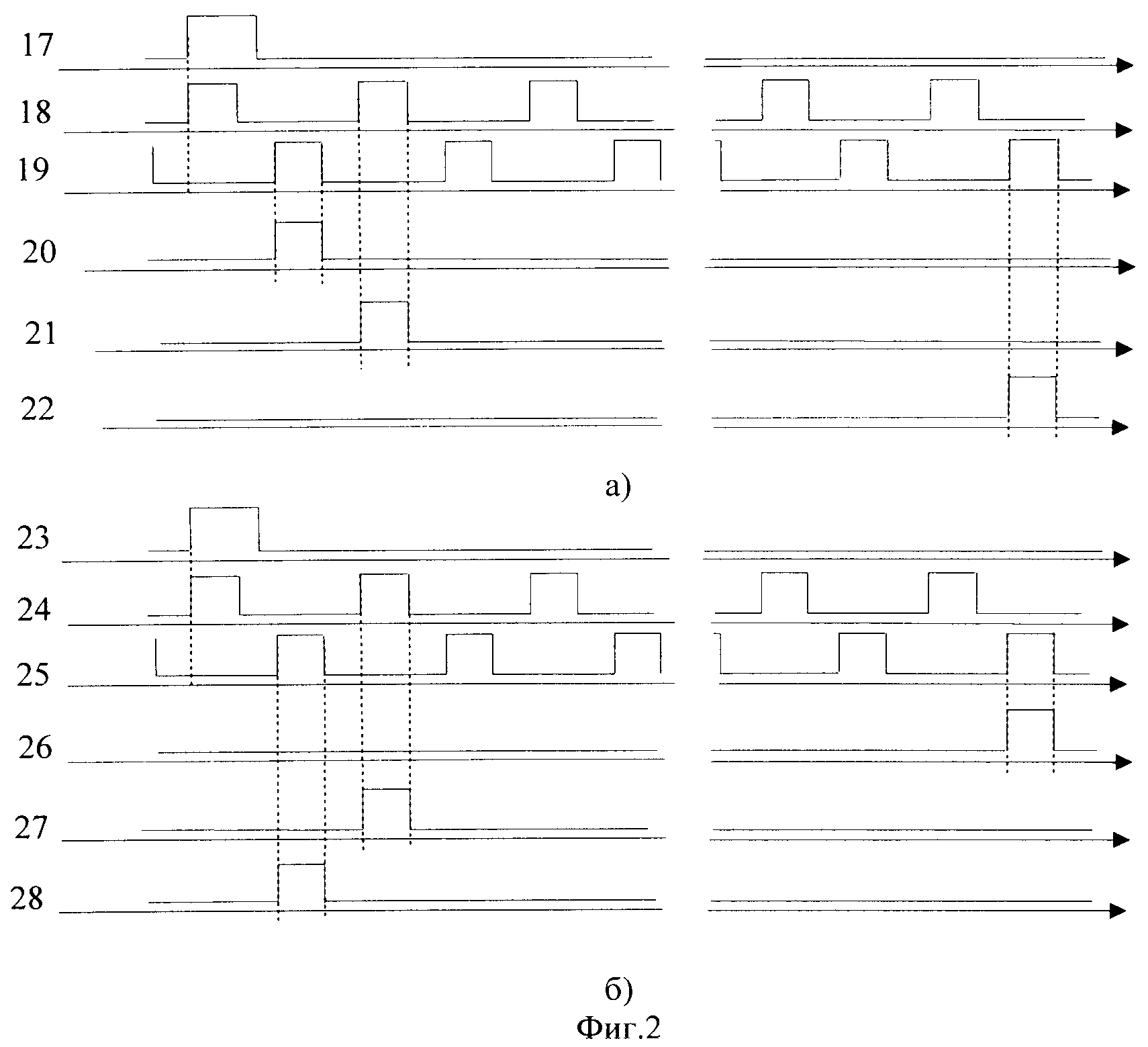

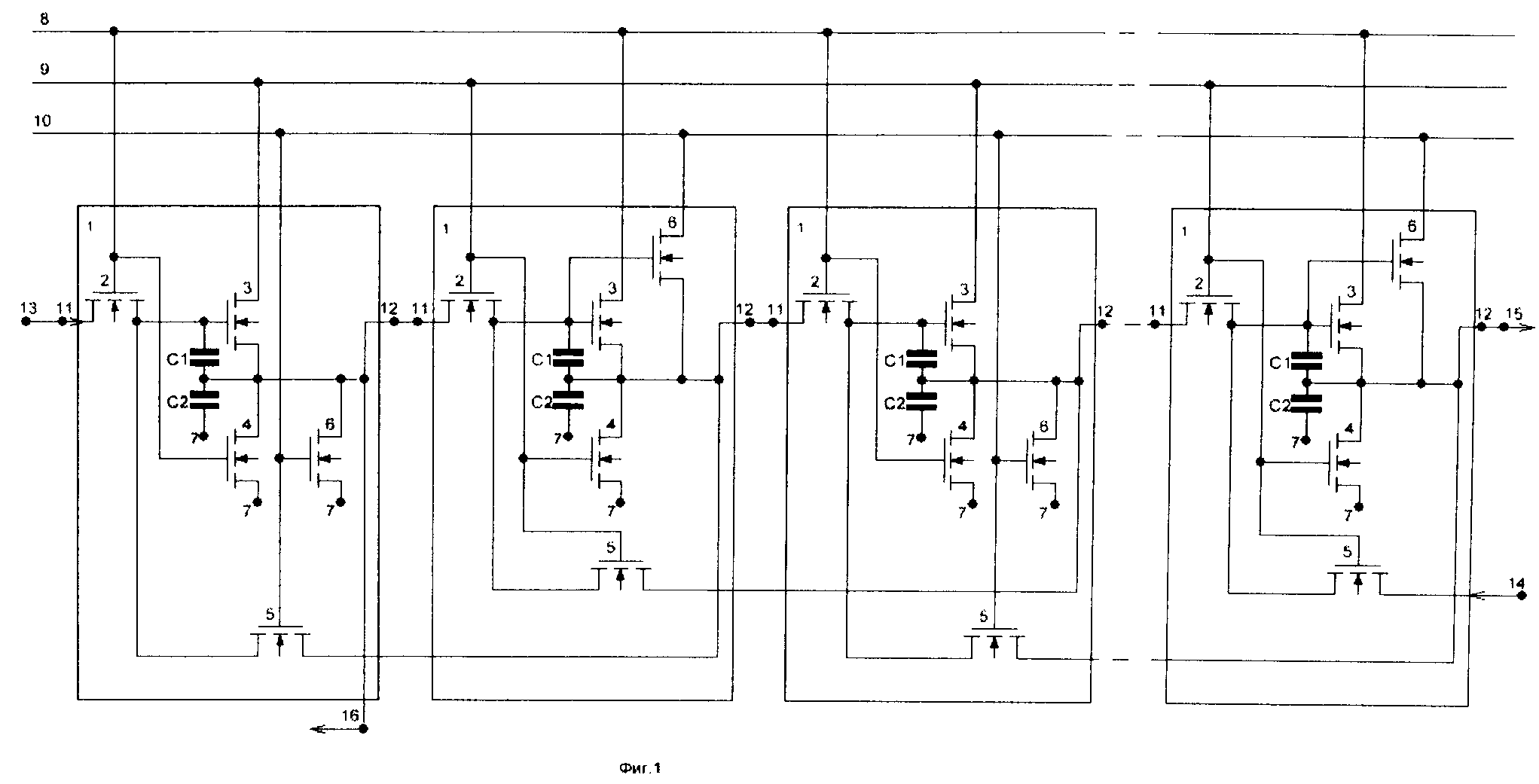

На фиг.1 представлена функциональная схема сдвигового регистра, на фиг.2 приведены временные диаграммы работы сдвигового регистра при выполнении операции сдвига логической единицы вправо (считывание информации слева на право) и влево.

На фиг.1 приняты следующие обозначения: ячейки 1, каждая из которых состоит из первого коммутирующего 2, информационного 3, первого нагрузочного 4, второго коммутирующего 5 и второго нагрузочного 6 n-МОП транзисторов; емкостей первой С1 и второй С2, шины нулевого потенциала 7, первой шины тактового питания 8, второй шины тактового питания 9, третьей шины тактового питания 10, входа 11 и выхода 12 ячейки, первого 13 и второго 14 информационных входов, первого 15 и второго 16 информационных выходов сдвигового регистра.

Предлагаемый сдвиговый регистр осуществляется следующим образом. В каждой ячейке 1 исток первого коммутирующего n-МОП транзистора 2 образует вход в ячейку 11, который в первой ячейке является одновременно и первым информационным входом 13 сдвигового регистра при выполнении операции сдвига логической единицы вправо. Его затвор соединен с затвором первого нагрузочного n-МОП транзистора 4 и с первой шиной тактового питания 8 в нечетной ячейке, а четной ячейке - со второй шиной тактового питания 9. Сток первого коммутирующего n-МОП транзистора 2 соединен с обкладкой первой емкости С1, с затвором информационного n-МОП транзистора 3, сток которого соединен со второй шиной тактового питания 9 в нечетной ячейке или с первой шиной тактового питания 8 в четной ячейке. Исток информационного n-МОП транзистора 3 соединен с общей обкладкой емкостей, со стоком первого нагрузочного n-МОП транзистора 4 и стоком (в нечетных ячейках) или с истоком второго нагрузочного n-МОП транзистора 6 (в четных ячейках) и образует выход 12 ячейки. В первой ячейке выход 12 является одновременно и вторым информационным выходом 16 сдвигового регистра. В последней ячейке выход 12 является также и первым информационным выходом 15 сдвигового регистра. Исток первого нагрузочного n-МОП транзистора 4 и вторая обкладка второй емкости С2 в каждой ячейке соединены с шиной нулевого потенциала 7. Исток второго нагрузочного n-МОП транзистора 6 соединен с шиной нулевого потенциала 7 только в нечетных ячейках, а в четных он соединен с выходом своей ячейки. Затвор второго нагрузочного n-МОП транзистора 6 соединен с затвором второго коммутирующего n-МОП транзистора 5 и с третьей шиной такового питания 10 в нечетной ячейке, или с затвором информационного n-МОП транзистора 3 в четной ячейке. Исток второго коммутирующего n-МОП транзистора 5 соединен со стоком первого коммутирующего n-МОП транзистора 2 и затвором информационного n-МОП транзистора 3. Сток второго коммутирующего n-МОП транзистора 5 соединен с выходом 12 следующей ячейки, а в последней ячейке является вторым информационным входом 14 сдвигового регистра одновременно. В каждой четной ячейке сток второго нагрузочного n-МОП транзистора 6 соединен с третьей шиной тактового питания 10, а затвор второго коммутирующего n-МОП транзистора 5 - с затворами первого коммутирующего n-МОП транзистора 2 и первого нагрузочного n-МОП транзистора 4.

На фиг.2а приведена временная диаграмма операции сдвига логической единицы вправо, где 17 - сигнал на первом информационном входе 13 сдвигового регистра, 18, 19 - сигналы на первой и второй тактовых шинах питания 8, 9 соответственно, 20, 21, 22 - сигналы на выходах 12 первой, второй ячейках и на первом информационном выходе 15 последней четной ячейки сдвигового регистра соответственно.

На фиг.2б приведена временная диаграмма операции сдвига информации влево, где 23 - сигнал на втором информационном входе 14; 24, 25 - сигналы на второй и третьей тактовых шинах питания 9, 10 соответственно; 26, 27, 28 - сигналы на втором информационном выходе 16 первой ячейки, на выходе 12 предпоследней и последней ячеек сдвигового регистра соответственно.

Рассмотрим работу сдвигового регистра.

Сдвиговый регистр работает следующим образом при выполнении операции сдвига логической единицы вправо (считывание информации слева направо, фиг.2а).

В исходном положении на первом и втором информационных входах 13, 14 нулевой потенциал. Первая логическая единица сигнала 18, которая поступает по первой шине тактового питания 8, открывает первый коммутирующий 2 и первый нагрузочный 4 n-МОП транзисторы первой и всех нечетных ячеек. Если на первый информационный вход 13 поступает логическая единица сигнала 17, то на выходе 12 первой ячейки устанавливается логический ноль, т.к. в это время через открытый первый нагрузочный n-МОП транзистор 4 логический ноль его истока, который обеспечивается шиной нулевого потенциала 7, устанавливается на стоке. Когда приходит на вторую шину тактового питания 9 первая логическая единица сигнала 19, она через открытый информационный n-МОП транзистор 3 без ослабления, что обеспечивается за счет емкостей С1 и С2, попадает на выход 12 первой ячейки, образуя сигнал 20, и вход 11 второй ячейки одновременно. Первый коммутирующий 2 и первый нагрузочный 4 n-МОП транзисторы второй ячейки в это время открыты, и на выходе 12 второй ячейки устанавливается логический ноль. Далее, когда на первую шину тактового питания 8 приходит вторая логическая единица сигнала 18, она через открытый информационный n-МОП транзистор 3 без ослабления, что обеспечивается за счет емкостей С1 и С2, попадает на выход 12 второй ячейки, образуя сигнал 21, и вход 11 третьей ячейки одновременно. На выходе 12 последней, например тридцать второй, ячейки единица сигнала 22 совпадет с семнадцатой единицей сигнала 18. Таким образом, логическая единица сигнала 17 с первого информационного входа 13 первой ячейки достигает первого информационного выхода 15 последней четной ячейки, двигаясь слева направо, учитывая, что внесенные для операции считывания справа налево второй коммутирующий 5 и второй нагрузочный 6 n-МОП транзисторы, третья шина тактового питания 10 и второй информационный выход для считывания 16, при операции считывания слева направо не используются.

При операции сдвига информации влево сдвиговый регистр работает аналогично операции сдвига вправо. Временная диаграмма операции сдвига информации влево приведена на фиг.2б.

С приходом по второй шине тактового питания 9 первой логической единицы сигнала 24 открываются первый коммутирующий 2, первый нагрузочный 4 и второй коммутирующий 5 n-МОП транзисторы последней (предположим, она четная) и всех предшествующих четных ячеек. Когда на второй информационный вход 14 поступает логическая единица сигнала 23, то на выходе последней четной ячейки устанавливается логический ноль, т.к. в это время через открытый первый нагрузочный n-МОП транзистор 4 логический ноль его истока, который обеспечивается шиной нулевого потенциала 7, устанавливается на стоке. Далее, когда приходит по третьей шине тактового питания 10 первая логическая единица сигнала 25, она через открытый второй нагрузочный n-МОП транзистор 6 без ослабления, что обеспечивается за счет сформированных емкостей С1 и С2, попадает на выход 12 последней ячейки и одновременно на затвор n-МОП транзистора 3 предпоследней ячейки (сигнал 28). Второй нагрузочный n-МОП транзистор 6 предпоследней ячейки в это время открыт, логический ноль его истока, который обеспечивается шиной нулевого потенциала 7, устанавливается на его стоке и одновременно на выходе 12 предпоследней ячейки. Далее, когда по второй шине тактового питания 9 приходит вторая логическая единица сигнала 24, она через открытый информационный n-МОП транзистор 3 без ослабления, что обеспечивается за счет сформированных емкостей С1 и С2, попадает на выход 12 предпоследней ячейки и одновременно на затвор информационного n-МОП транзистора 3 третьей от конца ячейки через ее открытый второй коммутирующий n-МОП транзистор 5 (сигнал 27). На втором информационном выходе 16 первой ячейки, например сдвигового регистра из двенадцати ячеек, единица сигнала 26 совпадет с седьмой единицей сигнала 24. Таким образом, тактовые импульсы питания сигналов 24, 25 передаются от входа ячейки к ее выходу без ослабления, т.е. из них не вычитается пороговое напряжение, что обеспечивается за счет сформированных емкостей С1 и С2, а логическая единица сигнала 23 со второго информационного входа 14 последней четной ячейки достигает второго информационного выхода 16 первой ячейки, двигаясь справа налево, учитывая, что первая шина тактового питания 8, вход 11 ячейки, первые информационные вход 13 и выход 15 сдвигового регистра предназначены для операции считывания справа налево и при операции считывания слева направо не используются.

Сдвиговый регистр, содержащий ячейки, каждая из которых состоит из трех n-МОП транзисторов и двух емкостей, двух шин тактового питания, шины нулевого потенциала, причем в каждой ячейке исток коммутирующего n-МОП транзистора является входом в ячейку, а в первой ячейке сдвигового регистра и первым информационным входом сдвигового регистра при сдвиге информации вправо его затвор соединен с затвором нагрузочного n-МОП транзистора и с первой шиной тактового питания в нечетной ячейке, а в четной ячейке - со второй шиной тактового питания, сток коммутирующего n-МОП транзистора соединен с затвором информационного n-МОП транзистора и первой обкладкой первой емкости, другая обкладка которой соединена с обкладкой второй емкости и со стоком нагрузочного и с истоком информационного n-МОП транзисторов и является выходом ячейки, а в последней ячейке сдвигового регистра и первым информационным выходом сдвигового регистра одновременно, исток нагрузочного n-МОП транзистора и другая обкладка второй емкости соединены с шиной нулевого потенциала, сток информационного n-МОП транзистора соединен со второй шиной тактового питания в нечетной ячейке или с первой шиной тактового питания в четной ячейке, отличающийся тем, что в каждую ячейку введены третья шина тактового питания, второй коммутирующий и второй нагрузочный n-МОП транзисторы, причем исток второго коммутирующего n-МОП транзистора соединен со стоком первого коммутирующего и затвором информационного n-МОП транзисторов, затвор второго коммутирующего n-МОП транзистора соединен с затвором второго нагрузочного n-МОП транзистора и с третьей шиной тактового питания в нечетной ячейке или с затворами первого коммутирующего и первого нагрузочного n-МОП транзисторов в четной ячейке, сток второго коммутирующего n-МОП транзистора соединен с выходом следующей ячейки, а в последней ячейке сдвигового регистра образует второй информационный вход сдвигового регистра при считывании информации справа налево, исток второго нагрузочного n-МОП транзистора соединен с шиной нулевого потенциала в нечетной ячейке или с выходом своей же ячейки в четной ячейке, его сток соединен с выходом своей ячейки в нечетной ячейке или с третьей шиной тактового питания в четной ячейке, а его затвор в четной ячейке соединен с затвором информационного n-МОП транзистора, выход первой ячейки является одновременно вторым информационным выходом сдвигового регистра при считывании информации справа налево.