Результат интеллектуальной деятельности: СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ

Вид РИД

Изобретение

Изобретение относится к области цифровой техники и может быть использовано при создании высокоскоростных демультиплексоров цифровых потоков.

Необходимость применения высокоскоростных устройств обработки цифровых потоков обусловлена тем, что задача повышения пропускной способности аппаратуры обработки данных в настоящее время является актуальной в связи с постоянным ростом интенсивности информационного обмена.

В [Патент №2122291 от 20.11.1998 г. «Способ обработки цифровых потоков» - 1], взятом за прототип, предложен способ обработки цифровых потоков по модели сигнала, при котором:

- из входного цифрового потока (входного сигнала), сопровождаемого сигналом тактовой синхронизации, селектируют сигналы синхронизации на интервале периодичности цифрового потока (цикле или сверхцикле);

- синтезируют модель сигнала;

- заносят модель в оперативную память;

- по сигналу синхронизации синхронно с цифровым потоком считывают модель сигнала из оперативной памяти;

- формируют тактовые сигналы составляющих частей цифрового потока;

- выделенными тактовыми сигналами селектируют информационные части составляющих цифрового потока (компонентные сигналы).

Основным свойством способа-прототипа является возможность адаптации под произвольную структуру входного сигнала без изменения схемно-технических решений в устройствах обработки цифровых потоков.

Недостатком способа-прототипа является низкая пропускная способность, равная максимальному значению частоты сигнала тактовой синхронизации, при котором устройство, реализующее способ-прототип, сохраняет работоспособность, так как на каждом такте сигнала тактовой синхронизации обрабатывается один бит входного цифрового потока.

За устройство-прототип взято устройство из [1]. Устройство-прототип содержит последовательно соединенные селектор синхросигнала, оперативное запоминающее устройство (ОЗУ) со схемами записи и чтения, регенератор тактов и регенератор информации, а также персональную электронно-вычислительную машину синтеза модели, подключенную к ОЗУ, блок задержки, включенный между селектором синхросигнала и регенератором тактов, и блок задержки, включенный между селектором синхросигнала и регенератором информации. Входами устройства являются входы селектора синхросигнала, а выходами - выходы регенератора информации.

Недостатком устройства-прототипа является низкая пропускная способность, равная максимальному значению частоты сигнала тактовой синхронизации, при котором устройство сохраняет работоспособность.

Целью изобретения является увеличение пропускной способности при сохранении возможности адаптации под произвольную структуру входного сигнала.

Для достижения указанной цели предлагается способ синхронизации и демультиплексирования компонентных сигналов в цифровых потоках, при котором синтезируют модель входного цифрового потока, заносят модель в оперативную память. Согласно изобретению на первом такте сигнала тактовой синхронизации записывают слово из L битов входного сигнала в старшую часть входного регистра, состоящего из 2Z ячеек, пронумерованных 1, 2,…L, L+1,…2L, а именно в ячейки с номерами L+1,…1L, причем в ячейку с меньшим номером записывают бит, пришедший в цифровом потоке раньше, на каждом последующем такте сигнала тактовой синхронизации переписывают слово из старшей части входного регистра - ячеек с номерами L+1,…2L - в младшую его часть - ячейки 1, 2,…L - и записывают слово из следующих L битов входного сигнала в старшую часть входного регистра, тем самым формируют на выходах входного регистра входное слово из 1L битов входного сигнала, пронумерованных 1, 2,…L, L+1,…2L, причем бит, пришедший раньше, имеет меньший номер, формируют из входного слова L слов, именуемых фазами входного сигнала, причем каждая фаза содержит L битов, и l-я фаза, где l=1, 2,…L, содержит биты входного слова с номерами l, l+1,…l+L-1, извлекают из оперативной памяти фрагмент модели входного сигнала, описывающий L следующих подряд битов в пределах цикла входного сигнала, сравнивают каждую из L фаз входного сигнала с фрагментом модели, при этом считают, что фаза совпадает с фрагментом модели, если биты фазы, совпадающие по положению с битами синхропризнака в фрагменте модели, имеют одинаковые с ними значения, затем по результату сравнения принимают решение остаться в прежнем состоянии или перейти в другое состояние, а именно из состояния поиска синхропризнака переходят в состояние входа в синхронизм, из состояния входа в синхронизм переходят в состояние поиска синхропризнака или состояние удержания синхронизации, из состояния удержания синхронизации переходят в состояние поиска синхропризнака, при этом состояние поиска синхропризнака является начальным состоянием, а в состоянии удержания синхронизации производят демультиплексирование компонентных сигналов.

Согласно изобретению для каждого бита цикла входного цифрового потока модель содержит признак принадлежности бита к синхропризнаку и, если бит принадлежит к синхропризнаку, его значение - 0 или 1, а также признак принадлежности бита к демультиплексируемому компонентному сигналу и, если бит принадлежит к компонентному сигналу, номер компонентного сигнала в диапазоне от 1 до N, если требуется демультиплексировать до N компонентных сигналов, модель также содержит размер цикла входного цифрового потока, стартовую позицию в пределах цикла, с которой начинают поиск синхропризнака, порог входа в синхронизм и порог удержания синхронизации.

Согласно изобретению в состоянии поиска синхропризнака на каждом такте сигнала тактовой синхронизации сравнивают фазы сигнала с одним и тем же фрагментом модели, описывающим биты, расположенные со стартовой позиции, при обнаружении совпадения одной или более фаз с фрагментом модели формируют слово совпадений из L двоичных разрядов, где 1-й разряд соответствует l-й фазе сигнала и где отмечают фазы, совпавшие с фрагментом модели, для чего в соответствующие им разряды слова совпадений записывают логические единицы и переходят в состояние входа в синхронизм, а если совпадений не обнаружено, остаются в состоянии поиска синхропризнака.

Согласно изобретению в состоянии входа в синхронизм на каждом такте сигнала тактовой синхронизации сравнивают фазы сигнала с последовательными фрагментами модели, описывающими биты, расположенные с позиции в пределах цикла, полученной путем увеличения на L предыдущей позиции, причем, если вновь рассчитанная позиция достигает или превышает размер цикла, от нее отнимают размер цикла, в слове совпадений отмечают фазы, совпавшие с фрагментом модели, при условии, что эти фазы были отмечены на предыдущем такте сигнала тактовой синхронизации, для чего в разряды слова совпадений, соответствующие не совпавшим фазам, записывают логические нули, и если отмеченных фаз не осталось, переходят в состояние поиска синхропризнака, если осталась одна и более одной отмеченной фазы, остаются в состоянии входа в синхронизм, причем, если осталась единственная отмеченная фаза, начинают считать такты сигнала тактовой синхронизации, и как только число тактов достигнет порога входа в синхронизм, переходят в режим удержания синхронизации.

Согласно изобретению в состоянии удержания синхронизации на каждом такте сигнала тактовой синхронизации сравнивают фазы сигнала с последовательными фрагментами модели как в состоянии входа в синхронизм, и, если совпавших фаз нет или ни одна совпавшая фаза не является отмеченной в слове совпадений, отмечают текущий цикл входного цифрового потока как ошибочный, затем в конце цикла, если цикл был отмечен как ошибочный, увеличивают число ошибочных циклов на единицу, в противном случае устанавливают это число в ноль, и если число ошибочных циклов достигнет порога удержания синхронизации, переходят в режим поиска синхропризнака, в противном случае остаются в режиме удержания синхронизации, при этом концом цикла считают момент, когда позиция начала фрагмента модели достигнет или превысит размер цикла.

Согласно изобретению в состоянии удержания синхронизации демультиплексирование компонентных сигналов производят одновременно по N каналам, для чего в каждом канале подают на адресные входы долговременной памяти фрагмент модели и единственную отмеченную в слове совпадений фазу входного сигнала, снимают с выходов данных долговременной памяти последовательность битов компонентного сигнала и размер b этой последовательности, который может принимать значения от 0 до L, записывают результат демультиплексирования в регистр результата, состоящий из 2L ячеек, пронумерованных 1, 2,…L, L+l,…2L, а именно в ячейки с номерами а+1,…а+b, где а - число ранее демультиплексированных битов, увеличивают число ранее демультиплексированных битов на b и, если число станет равным или большим L, считывают из младшей половины регистра результата, а именно из ячеек 1, 2,…L, слово выходного сигнала из L битов, уменьшают число ранее демультиплексированных битов на L и переписывают содержимое ячеек регистра результата с номерами L+1,…L+c в ячейки с номерами 1,…с, где с - новое значение числа ранее демультиплексированных битов.

Для достижения указанной цели предлагается устройство синхронизации и демультиплексирования компонентных сигналов в цифровых потоках, содержащее оперативное запоминающее устройство - блок хранения модели со входом разрешения инкремента, тактовым входом, выходом сигнала окончания цикла и выходом фрагмента модели. Согласно изобретению устройство содержит входной регистр с L=2K информационными входами, пронумерованными 1, 2,…L, тактовым входом и 2L-1 выходами, пронумерованными 1, 2,…L, L+1,…2L-1, L блоков сравнения с L входами данных, входом фрагмента модели и выходом совпадения каждый, логический мультиплексор с 1L-1 входами данных, управляющими входами и L выходами данных, блок управления синхронизатором с L входами совпадения, входом сигнала окончания цикла, тактовым входом и выходами управления мультиплексором, разрешения инкремента и разрешения демультиплексирования и N блоков каналов демультиплексирования с L входами данных, входом фрагмента модели, входом разрешения демультиплексирования, тактовым входом, L выходами данных, пронумерованными 1, 2,…L, и выходом наличия компонентного сигнала, при этом 1-й, 2-й,… 1-й входы данных l-го блока сравнения, где l=1,2,…L, подключены к выходам входного регистра l, l+1,…l+L-1, вход фрагмента модели каждого блока сравнения подключен к выходу фрагмента модели блока хранения модели, у логического мультиплексора входы данных подключены к выходам входного регистра и управляющие входы подключены к выходам управления логическим мультиплексором блока управления синхронизатором, у блока управления синхронизатором входы совпадения соединены с выходами совпадения блоков сравнения, вход сигнала окончания цикла присоединен к одноименному выходу блока хранения модели, вход разрешения инкремента блока хранения модели подключен к одноименному выходу блока управления синхронизатором, у каждого блока каналов демультиплексирования входы данных присоединены к выходам данных логического мультиплексора, вход фрагмента модели присоединен к выходу фрагмента модели блока хранения модели, вход разрешения демультиплексирования - к одноименному выходу блока управления синхронизатором, при этом все тактовые входы соединены между собой и составляют вход сигнала тактовой синхронизации устройства, информационными входами устройства являются информационные входы входного регистра, информационными выходами устройства являются выходы данных блоков каналов демультиплексирования, и на входы подают слово из L битов входного сигнала в сопровождении сигнала тактовой синхронизации, причем на вход с меньшим номером подают бит, пришедший во входном сигнале раньше, и с выходов снимают слова из L битов компонентных сигналов в сопровождении сигнала тактовой синхронизации и при наличии активных уровней на соответствующих выходах наличия компонентного сигнала, причем с выхода с меньшим номером снимают бит, следующий в компонентном сигнале раньше, чем обеспечивают увеличение пропускной способности до L раз.

Согласно изобретению входной регистр содержит старший регистр из L ячеек и младший регистр из L ячеек, и выходы старшего регистра подключены ко входам младшего регистра, входы старшего регистра являются информационными входами входного регистра, соединенные между собой тактовые входы регистров составляют тактовый вход входного регистра, выходы младшего регистра есть выходы 1, 2,…L входного регистра, первые Z-1 выходов старшего регистра есть выходы L+1,…2L-1 входного регистра, блок хранения модели состоит из генератора адреса со входами размера цикла, стартовой позиции, входом разрешения инкремента адреса, являющимся одноименным входом блока, тактовым входом, являющимся тактовым входом блока, выходом адреса, выходом сигнала окончания цикла, являющимся одноименным выходом блока, и оперативного запоминающего устройства с входом адреса и выходом данных, являющимся выходом фрагмента модели, и у генератора адреса выход адреса подключен ко входу адреса оперативного запоминающего устройства, а на входах размера цикла и стартовой позиции устанавливают соответствующие значения, в оперативное запоминающее устройство заносят модель сигнала, и генератор адреса обеспечивает постоянную адресацию к модели со стартовой позиции, если инкремент адреса запрещен, увеличение адреса на L на каждом такте на тактовом входе в противном случае, а также уменьшение адреса на размер цикла, когда адрес достигает или превышает этот размер, блок сравнения устанавливает на выходе совпадения высокий логический уровень, если состояние входов данных, соответствующих позициям синхропризнака во фрагменте модели, совпадает со значениями битов синхропризнака, а также, если во фрагменте модели позиций синхропризнака нет, логический мультиплексор подключает к своим выходам входы данных а+1, а+2,…a+L, где а - число на его управляющих входах, блок управления синхронизатором состоит из схемы формирования слова совпадений, имеющей L первых входов, L вторых входов и L выходов и устанавливающей на выходах состояния первых входов, если на всех вторых входах низкий уровень, либо поразрядное логическое «И» первых и вторых входов в противном случае, L-разрядного регистра хранения слова совпадения со входом разрешения записи, детектора наличия совпадений с L входами и одним выходом, формирующего на выходе высокий уровень, если имеется высокий уровень хотя бы на одном входе, детектора единственного совпадения с L входами и одним выходом, формирующего на выходе высокий уровень, если имеется высокий уровень только на одном входе, приоритетного шифратора, схемы принятия решения о входе в синхронизм со входом порога, входом разрешения счета, входом сброса, тактовым входом, осуществляющей подсчет тактов на тактовом входе при условии, что на входе сброса низкий логический уровень, а на входе разрешения счета - высокий, и выставляющей на своем выходе высокий логический уровень, когда число тактов достигнет значения, установленного на входе порога, схемы принятия решения о выходе из синхронизма со входом порога, входом разрешения счета, входами ошибки и сигнала окончания цикла, тактовым входом, осуществляющей подсчет импульсов на входе окончания цикла при условии, что на входе разрешения счета установлен высокий логический уровень и что между импульсами окончания цикла были импульсы на входе ошибки, и выставляющей на своем выходе высокий логический уровень, когда число импульсов окончания цикла, отвечающих условию, достигнет значения, установленного на входе порога, логического элемента «ИЛИ», и у схемы формирования слова совпадений первые входы являются входами совпадения, вторые входы присоединены к выходам регистра хранения слова совпадений, а выходы - ко входам того же регистра и входам детекторов наличия совпадений и единственного совпадения, у приоритетного шифратора входы подключены к выходам регистра хранения слова совпадений, а выходы являются выходами управления мультиплексором, у схемы принятия решения о входе в синхронизм вход разрешения счета подключен к выходу детектора единственного совпадения, вход сброса - к выходу схемы принятия решения о выходе из синхронизма, выход является выходом разрешения демультиплексирования, также он подключен к первому входу элемента «ИЛИ» и через инвертор - ко входу разрешения записи регистра хранения слова совпадений и входу разрешения счета схемы принятия решения о выходе из синхронизма, ко второму входу элемента «ИЛИ» подключен выход детектора наличия совпадений, выход элемента «ИЛИ» является выходом разрешения инкремента, у схемы принятия решения о выходе из синхронизма вход ошибки через инвертор присоединен к выходу детектора наличия совпадений, вход сигнала окончания цикла является одноименным входом блока, каждый блок канала демультиплексирования содержит А-разрядный регистр числа битов, первое постоянное запоминающее устройство, у которого первыми адресными входами являются входы данных блока, вторыми адресными входами - вход фрагмента модели и третьими адресными входами - выходы регистра числа битов и которое имеет 2L-1 выходов данных и формирует на них слово вида abc, где а - наименее значащие биты и лидирующие нули в количестве от 0 до L-1, равном числу на третьих адресных входах, b - демультиплексированные биты числом от 0 до L, т.е. состояния первых адресных входов, совпадающих с позициями, отмеченными в фрагменте модели как принадлежащие к данному компонентному сигналу, с - нули заполнения в количестве от 0 до 2L-1, второе постоянное запоминающее устройство, у которого первыми адресными входами является вход фрагмента модели и вторыми адресными входами являются выходы регистра числа битов и которое имеет K+1 выходов данных, первые K из которых подключены ко входам регистра числа битов, и формирует на них слово, равное сумме числа на вторых адресных входах и количества битов b, L логических элементов «ИЛИ», подключенных своими первыми входами к первым L выходам первого постоянного запоминающего устройства, логического элемента «И», у которого первый вход соединен с K+1-м выходом данных второго постоянного запоминающего устройства, второй вход является входом разрешения демультиплексирования, а выход - выходом наличия компонентного сигнала, регистра результата, у которого первые L входов подключены к выходам элементов «ИЛИ», вторые L-1 входов - ко вторым Z-1 выходам первого постоянного запоминающего устройства, и на L-ом входе всегда установлен логический «0», а выходы в количестве L подключены ко вторым входам элементов «ИЛИ» и который состоит из двух L-разрядных регистров, трех логических мультиплексоров двух L-разрядных шин каждый и схемы управления, подключенной своим входом к K+1-му выходу данных второго постоянного запоминающего устройства, а выходом - ко входам управления мультиплексоров и меняющей состояние выхода по сигналу высокого логического уровня на входе, и данные с первых L входов регистра результата подаются на первый вход первого мультиплексора и второй вход второго мультиплексора, данные со вторых L входов регистра результата подаются на второй вход первого мультиплексора и первый вход второго мультиплексора, выход первого мультиплексора подключен ко входам первого регистра, выход второго мультиплексора подключен ко входам второго регистра, выходы первого регистра присоединены к первому входу третьего мультиплексора, выходы второго регистра присоединены ко второму входу третьего мультиплексора, выход третьего мультиплексора является выходами регистра результата, и тактовые входы схемы управления и регистров из состава регистра результата, соединенные с тактовым входом регистра числа битов, являются тактовым входом блока.

Сочетание отличительных признаков и свойства предлагаемых способа и устройства в доступной литературе не обнаружены, поэтому способ и устройство соответствуют критериям новизны и изобретательского уровня.

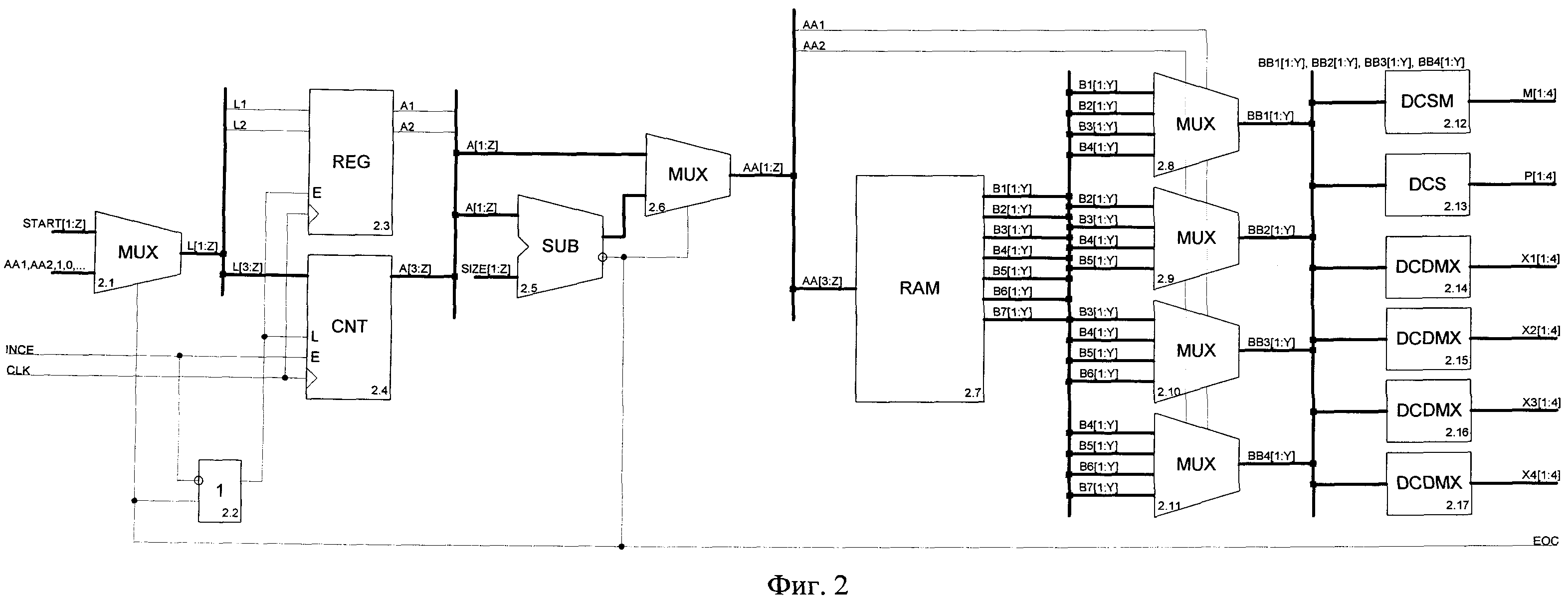

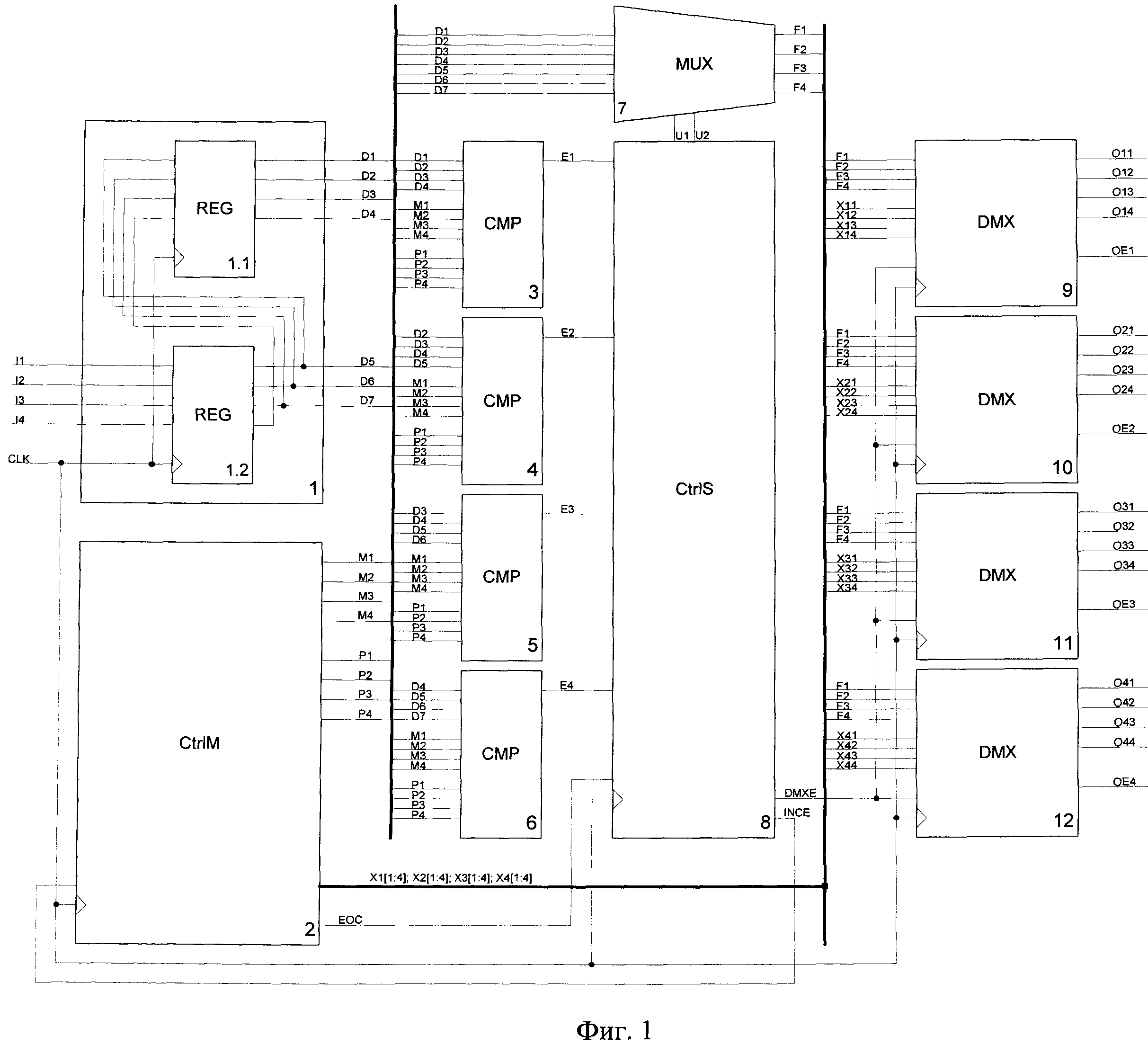

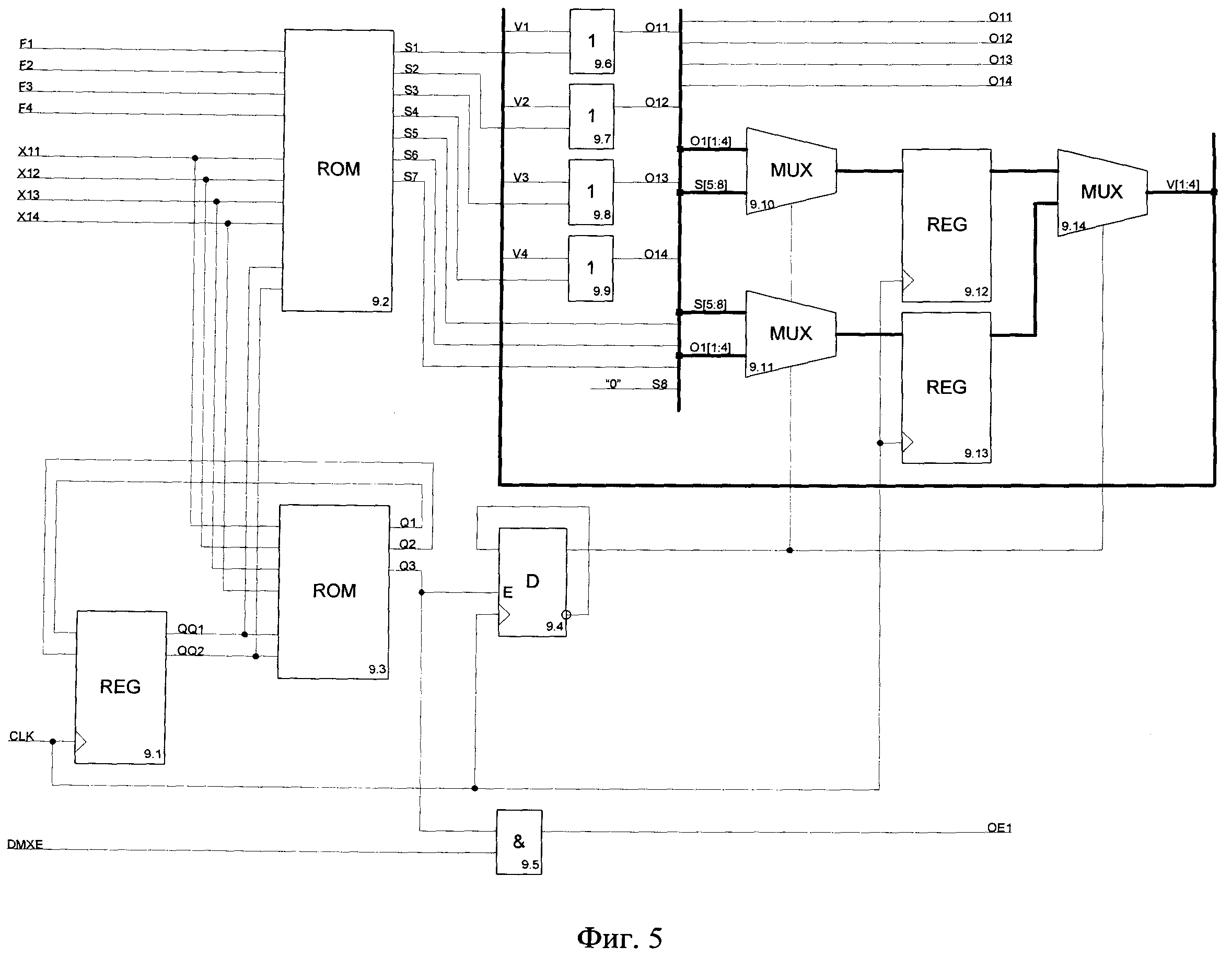

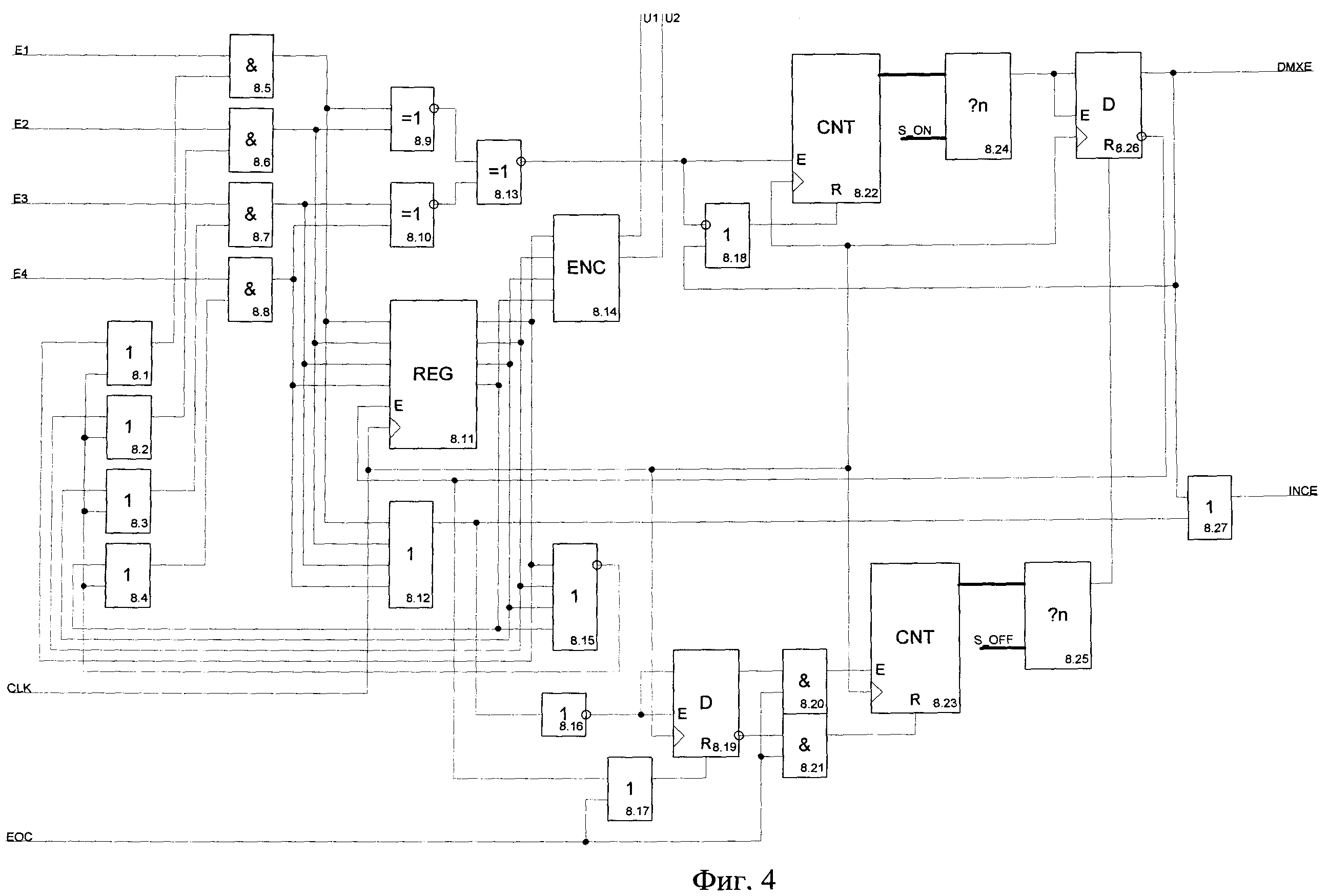

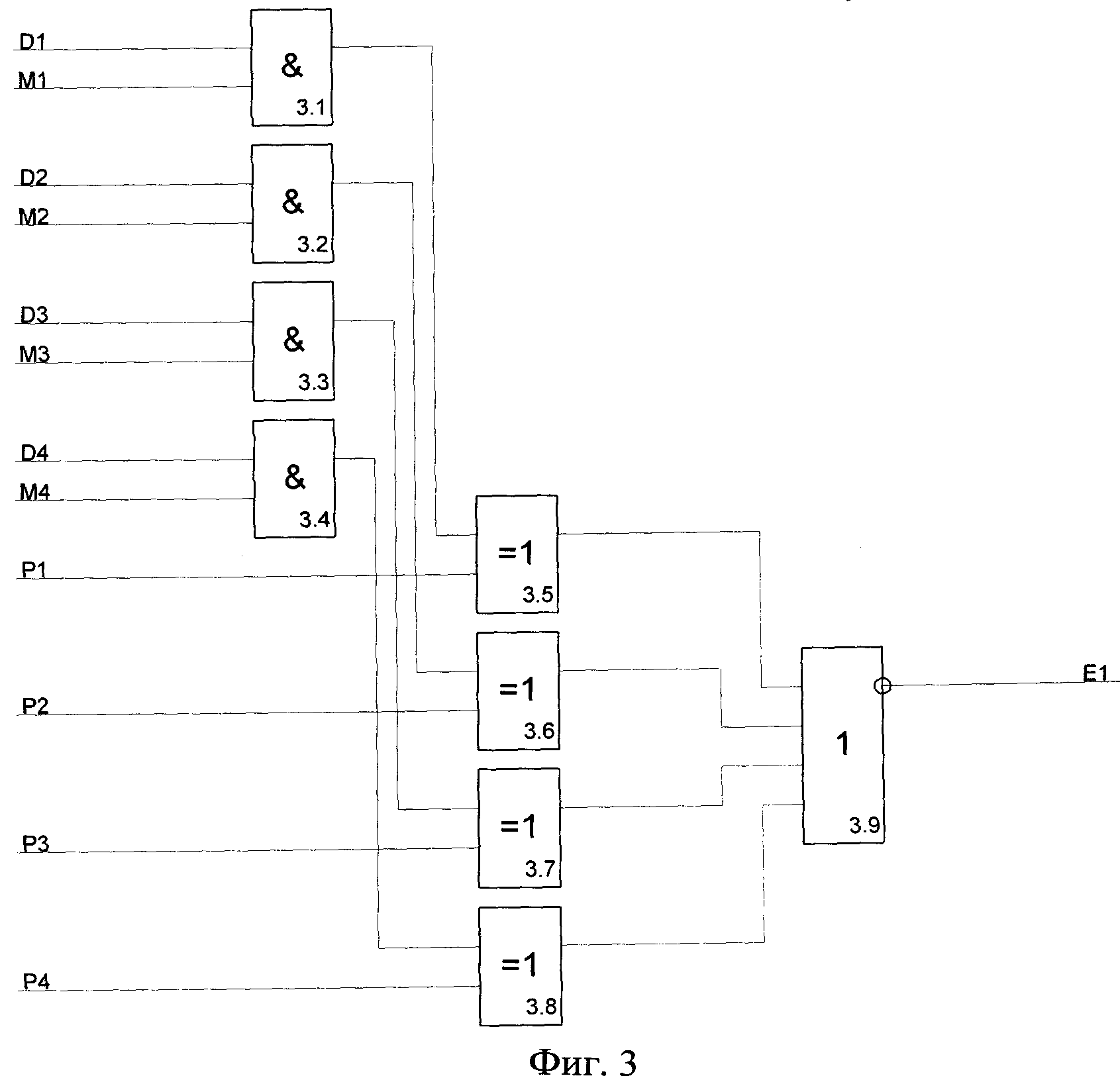

На фиг.1 приведена блок-схема устройства синхронизации и демультиплексирования для L=4 и N=4. На фиг.2-5 приведены схемы составных частей устройства синхронизации и демультиплексирования: на фиг.2 - схема блока хранения модели, на фиг.3 - схема блока сравнения, на фиг.4 - схема блока управления синхронизатором, на фиг.5 - схема блока канала демультиплексирования.

По предложенному способу выполняют следующую последовательность операций:

- синтезируют модель входного сигнала;

- записывают модель в оперативную память и регистры;

- на первом такте сигнала тактовой синхронизации записывают слово из L битов входного сигнала в старшую часть входного регистра, состоящего из 2L ячеек, пронумерованных 1, 2,…L, L+1,…2L, а именно в ячейки с номерами L+1,…2L, причем в ячейку с меньшим номером записывают бит, пришедший в цифровом потоке раньше;

- на каждом последующем такте сигнала тактовой синхронизации переписывают слово из старшей части входного регистра (ячейки с номерами L+1,…2L) в младшую его часть (ячейки 1, 2,…L) и записывают слово из следующих L битов входного сигнала в старшую часть входного регистра, тем самым формируют на выходах входного регистра входное слово из 2L битов входного сигнала, пронумерованных 1, 2,…L, L+1,…2L, причем бит, пришедший раньше, имеет меньший номер;

- формируют из входного слова L слов, именуемых фазами входного сигнала, причем каждая фаза содержит L битов, и 1-я фаза, где l=1, 2,…L, содержит биты входного слова с номерами l, l+1,…l+Z-1;

- извлекают из оперативной памяти фрагмент модели входного сигнала, описывающий L следующих подряд битов в цикле входного сигнала, сравнивают каждую из L фаз входного сигнала с фрагментом модели, при этом считают, что фаза совпадает с фрагментом модели, если биты фазы, совпадающие по положению с битами синхропризнака в фрагменте модели, имеют одинаковые с ними значения;

- по результату сравнения принимают решение остаться в прежнем состоянии или перейти в другое состояние, а именно, из состояния поиска синхропризнака переходят в состояние входа в синхронизм, из состояния входа в синхронизм переходят в состояние поиска синхропризнака или состояние удержания синхронизации, из состояния удержания синхронизации переходят в состояние поиска синхропризнака, при этом состояние поиска синхропризнака является начальным состоянием, а в состоянии удержания синхронизации производят демультиплексирование компонентных сигналов.

В состоянии поиска синхропризнака выполняют следующую последовательность операций:

- на каждом такте сигнала тактовой синхронизации сравнивают фазы сигнала с одним и тем же фрагментом модели, описывающим биты, расположенные со стартовой позиции;

- при обнаружении совпадения одной или более фаз с фрагментом модели формируют слово совпадений из L двоичных разрядов, где l-й разряд соответствует l-й фазе сигнала и где отмечают фазы, совпавшие с фрагментом модели, для чего в соответствующие им разряды слова совпадений записывают логические единицы, и переходят в состояние входа в синхронизм;

- если совпадений не обнаружено, остаются в состоянии поиска синхропризнака.

В состоянии входа в синхронизм выполняют следующую последовательность операций:

- на каждом такте сигнала тактовой синхронизации сравнивают фазы сигнала с последовательными фрагментами модели, описывающими биты, расположенные с позиции в цикле, полученной путем увеличения на L предыдущей позиции, причем, если вновь рассчитанная позиция достигает или превышает размер цикла, от нее отнимают размер цикла;

- в слове совпадений отмечают фазы, совпавшие с фрагментом модели, при условии, что эти фазы были отмечены на предыдущем такте сигнала тактовой синхронизации, для чего в разряды слова совпадений, соответствующие не совпавшим фазам, записывают логические нули;

- если отмеченных фаз не осталось, переходят в состояние поиска синхропризнака;

- если осталась одна и более одной отмеченной фазы, остаются в состоянии входа в синхронизм, причем, если осталась единственная отмеченная фаза, начинают считать такты сигнала тактовой синхронизации, и как только число тактов достигнет порога входа в синхронизм, переходят в режим удержания синхронизации.

В состоянии удержания синхронизации выполняют следующую последовательность операций:

- на каждом такте сигнала тактовой синхронизации сравнивают фазы сигнала с последовательными фрагментами модели, как в состоянии входа в синхронизм;

- если совпавших фаз нет или ни одна совпавшая фаза не является отмеченной в слове совпадений, отмечают текущий цикл как ошибочный;

- в конце цикла, если цикл был отмечен как ошибочный, увеличивают число ошибочных циклов на единицу, в противном случае устанавливают это число в ноль, при этом концом цикла считают момент, когда позиция начала фрагмента модели достигнет или превысит размер цикла;

- если число ошибочных циклов достигнет порога удержания синхронизации, переходят в режим поиска синхропризнака, в противном случае остаются в режиме удержания синхронизации.

В состоянии удержания синхронизации производят демультиплексирование компонентных сигналов одновременно по N каналам, для чего в каждом канале на каждом такте сигнала тактовой синхронизации выполняют следующую последовательность операций:

- подают на адресные входы долговременной памяти фрагмент модели и единственную отмеченную в слове совпадений фазу входного сигнала;

- снимают с выходов данных долговременной памяти последовательность битов компонентного сигнала и размер b этой последовательности, который может принимать значения от 0 до L;

- записывают результат демультиплексирования в регистр результата, состоящий из 2L ячеек, пронумерованных 1, 2,…L, L+1,…2L, а именно в ячейки с номерами а+1,…а+b, где а - число ранее демультиплексированных битов;

увеличивают число ранее демультиплексированных битов на b, и, если число станет равным или большим L, считывают из младшей половины регистра результата, а именно из ячеек 1, 2,…L, слово выходного сигнала из L битов, уменьшают число ранее демультиплексированных битов на L и переписывают содержимое ячеек регистра результата с номерами L+1,…L+c в ячейки с номерами 1,…с, где с - новое значение числа ранее демультиплексированных битов.

Устройство синхронизации и демультиплексирования (фиг.1), реализующее предлагаемый способ, состоит из входного регистра 1, блока хранения модели 2, четырех одинаковых блоков сравнения 3-6, логического мультиплексора 7, блока управления синхронизатором 8, четырех одинаковых блоков каналов демультиплексирования 9-12.

Входной регистр 1 содержит четырехразрядный младший регистр 1.1 и четырехразрядный старший регистр 1.2.

Адресный генератор блока хранения модели 2 (фиг.2) состоит из логического мультиплексора 2.1 двух шин разрядности Z, где 2Z - максимальный размер цикла сигнала в битах, логического элемента «ИЛИ» 2.2 с инверсным входом, двухразрядного регистра 2.3 со входом разрешения записи, загружаемого двоичного счетчика 2.4 разрядности Z-2 со входами разрешения записи и разрешения счета, двоичного вычитателя 2.5 Z-разрядных слов с инверсным выходом заема, логического мультиплексора 2.6 двух шин разрядности Z. Блок 2 также содержит ОЗУ 2.7 объемом 2Z-2 - ячеек разрядности 77, где Y - число битов модели, требуемых для описания одного бита цикла сигнала, логические мультиплексоры 2.8 - 2.11 четырех шин разрядности Y каждый, дешифратор маски синхропризнака 2.12, дешифратор синхропризнака 2.13, дешифраторы масок демультиплексирования 2.14-2.17.

Блок сравнения 3 (фиг.3) содержит логические элементы «И» 3.1-3.4, логические элементы «Исключающее ИЛИ» 3.5-3.8 и логический элемент «ИЛИ-НЕ» 3.9 с четырьмя входами. Блоки 4-6 точно такие же.

Блок управления синхронизатором 8 (фиг.4) состоит из логических элементов «ИЛИ» 8.1-8.4, логических элементов «И» 8.5-8.8, логических элементов «Исключающее ИЛИ» 8.9, 8.10 и 8.13 с инверсными выходами, четырехразрядного регистра 8.11 со входом разрешения записи, логического элемента «ИЛИ» 8.12 с четырьмя входами, приоритетного шифратора 8.14 с четырьмя входами и двумя выходами, логического элемента «ИЛИ-НЕ» 8.15 с четырьмя входами, схемы принятия решения о входе в синхронизм, включающей логический элемент «ИЛИ» 8.18 с инверсным входом, двоичный счетчик 8.22 со входами разрешения счета и синхронного сброса, схему сравнения двух чисел 8.24, триггер 8.26 со входами разрешения записи и синхронного сброса и прямым и инверсным выходами, схемы принятия решения о выходе из синхронизма, включающей инвертор 8.16, логический элемент «ИЛИ» 8.17, триггер 8.19 со входами разрешения записи и синхронного сброса и прямым и инверсным выходами, логические элементы «И» 8.20 и 8.21, двоичный счетчик 8.23 со входами разрешения счета и синхронного сброса, схему сравнения двух чисел 8.25, а также логического элемента «ИЛИ» 8.27.

Блок канала демультиплексирования 9 (фиг.5) содержит двухразрядный регистр 9.1, постоянное запоминающее устройство (ПЗУ) 9.2, имеющее 10 адресных входов и 7 выходов данных, ПЗУ 9.3, имеющее шесть адресных входов и три выхода данных, триггер 9.4 со входом разрешения записи и прямым и инверсным выходами, логический элемент «И» 9.5, логические элементы «ИЛИ» 9.6-9.9, логические мультиплексоры 9.10, 9.11, 9.14 двух четырехразрядных шин каждый, четырехрядные регистры 9.12 и 9.13. Блоки 10-12 точно такие же.

Устройство работает следующим образом.

Предварительно синтезируют модель сигнала так, что каждому биту цикла входного сигнала соответствует отдельное слово описания. Все слова описания состоят из одинакового числа двоичных разрядов Y, зависящего от выбранного формата описания, который не является предметом изобретения. Количество слов описания равно размеру цикла входного сигнала в битах и не должно превышать величины 27, выбранной на этапе проектирования устройства. Порядок следования слов описания соответствует порядку битов входного сигнала в цикле. Записывают модель сигнала в ОЗУ 2.7 таким образом, что в первой ячейке ОЗУ располагаются слова с 1-го по 7-е, во второй - с 5-го по 11-е, в третьей - с 9-го по 15-е и т.д. Если размер цикла К, то заполняются K/4 ячеек, если К кратно 4, или K/4+1 ячеек в противном случае. Причем последняя заполняемая ячейка и, возможно, предпоследняя заполняемая ячейка дополняются до конца описаниями битов с начала цикла. Устанавливают также на входе вычитателя 2.5, соответствующем вычитаемому, двоичное число SIZE - размер цикла, на первом входе логического мультиплексора 2.1 число START - значение стартовой позиции, на втором входе схемы 8.24 число S_ON - порог входа в синхронизм, на втором входе схемы 8.25 число S_OFF - порог выхода из синхронизма. Регистры хранения перечисленных двоичных чисел, схемы записи в них и в ОЗУ на чертежах не показаны, как не относящиеся к предмету изобретения.

Работа устройства начинается с поиска синхропризнака. В начальный момент времени выходы регистра 2.3 и счетчика 2.4 установлены в логический «0», на инверсном выходе заема вычитателя 2.5 имеется низкий уровень, сигнал INCE разрешения инкремента счетчика 2.4 также имеет низкий уровень, соответственно, инкремент счетчика 2.4 запрещен, а запись в регистр 2.3 и в счетчик 2.4 разрешена. На выходе мультиплексора 2.1 оказывается значение START, которое и записывается в регистр 2.3 (два наименее значащих разряда) и в счетчик 2.4 (остальные разряды) по первому фронту сигнала тактовой синхронизации CLK. Это же значение (шина AA[1:Z]) затем подается на входы управления мультиплексорами 2.8-2.11 (два наименее значащих разряда) и адресные входы ОЗУ 2.7 (остальные разряды). Таким образом, из модели сигнала выбираются описания четырех битов цикла входного сигнала, следующих подряд, начиная с позиции START. Дешифраторы 2.12-2.17 преобразуют описания битов к маскам и фрагменту синхропризнака. Каждая маска имеет четыре двоичных разряда, один разряд маски соответствует одному биту цикла входного сигнала и устанавливается в единицу, если бит принадлежит синхропризнаку (маска синхропризнака) или компонентному сигналу с данным номером (маска демультиплексирования). Фрагмент синхропризнака имеет такую же структуру, в нем разряд устанавливается в единицу, если бит принадлежит синхропризнаку и в синхро-признаке имеет значение «1». Реализации дешифраторов зависят от выбранного формата описания битов цикла входного сигнала.

По сигналу CLK содержимое регистра 1.2 переписывается в регистр 1.1, а в регистр 1.2 записываются очередные четыре бита сигнала. Четыре бита с выхода регистра 1.1 D[1:4] и три бита с выхода регистра 1.2 D[5:7] представляют собой семь последовательно пришедших битов входного сигнала.

Из них формируются четыре фазы входного сигнала: первая фаза D[l:4], вторая фаза D[2:5], третья фаза D[3:6], четвертая фаза D[4:7]. Фазы подаются на блоки сравнения 3-6. Блоки 3-6 формируют на своих выходах логические единицы, если биты фаз на позициях, отмеченных единицами в маске синхропризнака М[1:4], совпадают с битами фрагмента синхропризнака Р[1:4]. Выходы блоков 3-6 составляют слово результатов сравнения Е[1:4].

В регистре 8.11 формируется слово совпадений. В начальный момент слово совпадений нулевое, что разрешает, посредством логических элементов 8.15, 8.1 -8.4 и 8.5-8.8, запись в регистр 8.11 слова результатов сравнения Е[1:4] в качестве начального значения слова совпадений. Как только в слове Е[1:4] появляются ненулевые разряды, устройство переходит в режим входа в синхронизм - сигнал INCE устанавливается в единицу (логические элементы 8.12 и 8.27), разрешая инкремент счетчика 2.4, вследствие чего на каждом такте сигнала CLK на входах дешифраторов 2.12-2.17 оказываются описания следующих четырех битов цикла входного сигнала. Также после этого слово совпадений формируется как поразрядное логическое «И» слова Е[1:4] и слова совпадений, сохраненного в регистре 8.11 на предыдущем такте сигнала CLK.

Когда в слове совпадений остается единственный ненулевой разряд, разрешается инкремент счетчика 8.22 из состава схемы принятия решения о входе в синхронизм. Детектор единственности единицы выполнен на логических элементах 8.9, 8.10, 8.13.

Если в режиме входа в синхронизм в слове совпадений не остается разрядов, равных единице, счетчик 8.22 сбрасывается, его инкремент запрещается, сигнал INCE устанавливается в логический «0» и устройство переходит в режим поиска синхропризнака с позиции START в цикле входного сигнала.

Если содержимое счетчика 8.22 достигает значения S_ON, сигнал разрешения демультиплексирования DMXE на прямом выходе триггера 8.26 устанавливается в логическую единицу и устройство переходит в режим удержания синхронизации и демультиплексирования. Счетчик 8.22 сбрасывается и удерживается в состоянии сброса. Запрещается запись в регистр 8.11, тем не менее, слово совпадений формируется на выходах логических элементов 8.5-8.8 на каждом такте сигнала CLK. Разрешается работа схемы принятия решения о выходе из синхронизма.

В режиме удержания синхронизации в случае обнуления слова совпадений устанавливается высокий уровень на прямом выходе триггера 8.19, который удерживается до конца цикла входного сигнала. Тем самым отмечается наличие ошибок в синхропризнаке текущего цикла. По сигналу конца цикла ЕОС содержимое счетчика 8.23 увеличивается на единицу, если на прямом выходе триггера 8.19 высокий уровень, или сбрасывается в ноль в противном случае. Триггер 8.19 также сбрасывается по сигналу ЕОС. Если содержимое счетчика 8.23 достигает значения S_OFF, триггер 8.26 сбрасывается, сигнал INCE устанавливается в логический «0» и устройство переходит в режим поиска синхропризнака с позиции START в цикле входного сигнала.

Сигнал конца цикла ЕОС снимается с инверсного выхода заема вычитателя 2.5. Сигнал ЕОС становится активным, если число на выходной шине A[1:Z] регистра 2.3 и счетчика 2.4 достигнет или превысит значение SIZE. При этом на шине AA[1:Z] устанавливается число, равное разности A[1:Z]-SIZE, которая может принимать значения от 0 до 3. Таким образом, на адресных входах ОЗУ 2.7 устанавливается 0, а на управляющих входах мультиплексоров 2.8-2.11 - новые значения разрядов АА1 и АА2, которые также записываются в регистр 2.3 на следующем такте сигнала CLK. Тогда же вместо инкремента происходит загрузка счетчика 2.4 значением 1.

В режиме удержания синхронизации и демультиплексирования на выходах приоритетного шифратора 8.14 поддерживается номер единственной фазы входного сигнала, по которой был найден синхропризнак и достигнут синхронизм. Этот номер подается на управляющие входы логического мультиплексора 7. В результате вышеозначенная фаза F[1:4] подается на входы блоков каналов демультиплексирования 9-12.

В блоке канала демультиплексирования 9 ПЗУ 9.2 ставит в соответствие фазе F[1:4], маске демультиплексирования X1 [1:4] и количеству QQ[1:2] демультиплексированных битов, сохраненных в регистре результата, слово S[1:8] (бит S8 всегда равен нулю) демультиплексированного сигнала, смещенного в сторону наиболее значащих битов на число QQ[1:2]. ПЗУ 9.3 ставит в соответствие числу QQ[1:2], сохраняемому в регистре 9.1, и маске X1 [1:4] новое количество демультиплексированных битов Q[l:3]. Биты S[5:8] записываются в старшую половину регистра результата. В младшую половину регистра результата записываются биты O1 [1:4] - итог поразрядного логического «ИЛИ» битов S[1:4] и битов V[1:4], сохраненных в младшей половине регистра результата на предыдущем такте сигнала CLK. Биты O1 [1:4] являются также выходом блока 9 и одним из выходов всего устройства. Они представляют действительное значение демультиплексированного сигнала, когда накапливается 4 или более демультиплексированных битов. В этом случае разряд Q3 равен единице и, при наличии высокого логического уровня в цепи DMXE, формируется строб наличия выходного сигнала ОЕ1. Выходной демультиплексированный сигнал считывают с выходов O1 [1:4] по фронту сигнала CLK при наличии высокого уровня на выходе ОЕ1.

Регистр результата собран из регистров 9.12, 9.13, логических мультиплексоров 9.10, 9.11, 9.14 и управляется триггером 9.4. Пусть в начальный момент времени на прямом выходе триггера 9.4 низкий логический уровень. Вследствие этого, на входы регистра 9.12 через мультиплексор 9.10 подаются сигналы O1 [1:4], а на входы регистра 9.13 через мультиплексор 9.11 подаются сигналы S[5:8]. Биты V[1:4] посредством мультиплексора 9.14 снимаются с выхода регистра 9.12. Таким образом, регистр 9.12 является младшей половиной регистра результата, а регистр 9.13 - старшей половиной. Пусть количество демультиплексированных битов в регистре результата стало равным или большим четырех - на выходе Q3 ПЗУ 9.3 появилась логическая единица. Тогда на следующем такте сигнала CLK триггер 9.4 изменит свое состояние и на его прямом выходе установится логическая единица. После чего на входы регистра 9.12 через мультиплексор 9.10 будут поданы сигналы S[5:8], на входы регистра 9.13 через мультиплексор 9.11 - сигналы 01 [1:4], а биты V[1:4] посредством мультиплексора 9.14 будут сниматься с выхода регистра 9.12. То есть, регистр 9.12 станет старшей половиной регистра результата, а регистр 9.13 - младшей половиной с остатком предыдущего результата демультиплексирования. Размер остатка - Q1 и Q2 - будет сохранен в регистре 9.1.

ПЗУ 9.2 имеет 10 адресных входов - четыре двоичных разряда F[l:4], четыре разряда X1 [1:4] и два разряда QQ[1:2]. Следовательно, его объем составляет 210=1024 семиразрядных слов вида abc (a - наименее значащие биты), где а - лидирующие нули в количестве, равном QQ[1:2] (от 0 до 3), b - демультиплексированные биты числом от 0 до 4, т.е. биты из F[1:4] на позициях, отмеченных единицами в X1 [1:4], расположенные подряд, с - нули заполнения в количестве от 0 до 7. ПЗУ 9.3 имеет 6 адресных входов - четыре разряда X1 [1:4] и два разряда QQ[1:2] и его объем равен 26=64 трехразрядных слов, каждое из которых является суммой количества единиц в X1 [1:4] и значения QQ[1:2]. Понятно, что в зависимости выбранной технологии ПЗУ могут быть реализованы разными способами. В частности, при использовании программируемых матриц логических элементов это могут быть синтезированные логические функции в сочетании с мультиплексорами, сумматорами и пр.

Блоки 10-12 функционируют точно так же.

По предложенному способу было построено несколько устройств синхронизации и демультиплексирования с L=4 и L=8. В результате использования способа получен следующий технический эффект: пропускная способность устройств увеличена в 2-4 раза, при том, что частота сигнала тактовой синхронизации была понижена вследствие усложнения устройств.