Результат интеллектуальной деятельности: ЛОГИЧЕСКИЙ ПРОЦЕССОР

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические процессоры (см., например, патент РФ 2260837, кл. G06F 7/38, 2005 г.), которые реализуют шесть простых симметричных булевых функций, зависящих от шести аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических процессоров, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация восьми простых симметричных булевых функций, зависящих от восьми аргументов - входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический процессор (патент РФ 2260205, кл. G06F 7/38, 2005 г.), который содержит вычислительные ячейки и при n=8 реализует восемь простых симметричных булевых функций, зависящих от восьми аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится низкое быстродействие, обусловленное тем, что минимальное время реализации восьми упомянутых функций превышает 8Δtя, где Δtя есть длительность задержки, вносимой вычислительной ячейкой.

Техническим результатом изобретения является повышение быстродействия за счет уменьшения времени реализации восьми простых симметричных булевых функций, зависящих от восьми аргументов - входных двоичных сигналов.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом процессоре, содержащем семь вычислительных ячеек, каждая из которых содержит элемент ИЛИ, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент И, первый, второй входы и выход которого соединены соответственно с ее первым, вторым входами и вторым выходом, особенность заключается в том, что в него дополнительно введены двенадцать аналогичных упомянутым вычислительных ячеек, причем первый, второй входы i-й  и первый, второй входы j=й

и первый, второй входы j=й  вычислительных ячеек подключены соответственно к первым выходам (i+2)-й, (i+4)-й и вторым выходам (j-4)-й, (j-2)-й вычислительных ячеек, первые выходы i-й, j-й и вторые выходы i-й, j-й вычислительных ячеек соединены соответственно с i-ым входом одиннадцатой, вторым входом (j+2)-й и первым входом (i+8)-й, (j-6)-м входом пятнадцатой вычислительных ячеек, первый, второй выходы (i+8)-й, первый, второй входы семнадцатой и первый, второй входы восемнадцатой вычислительных ячеек подключены соответственно к i-ым входам двенадцатой, четырнадцатой, второму выходу тринадцатой, первому выходу четырнадцатой и второму выходу двенадцатой, первому выходу шестнадцатой вычислительных ячеек, i-й вход k-й (k∈{13, 16, 19}) вычислительной ячейки соединен с (3-i)-м выходом (k-3+i)-й вычислительной ячейки, а первые выходы одиннадцатой, тринадцатой, семнадцатой, девятнадцатой и вторые выходы девятнадцатой, восемнадцатой, шестнадцатой, пятнадцатой вычислительных ячеек являются соответственно первым, вторым, третьим, четвертым и пятым, шестым, седьмым, восьмым выходами логического процессора, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого подключены соответственно к первым и вторым входам третьей, пятой, четвертой, шестой вычислительных ячеек.

вычислительных ячеек подключены соответственно к первым выходам (i+2)-й, (i+4)-й и вторым выходам (j-4)-й, (j-2)-й вычислительных ячеек, первые выходы i-й, j-й и вторые выходы i-й, j-й вычислительных ячеек соединены соответственно с i-ым входом одиннадцатой, вторым входом (j+2)-й и первым входом (i+8)-й, (j-6)-м входом пятнадцатой вычислительных ячеек, первый, второй выходы (i+8)-й, первый, второй входы семнадцатой и первый, второй входы восемнадцатой вычислительных ячеек подключены соответственно к i-ым входам двенадцатой, четырнадцатой, второму выходу тринадцатой, первому выходу четырнадцатой и второму выходу двенадцатой, первому выходу шестнадцатой вычислительных ячеек, i-й вход k-й (k∈{13, 16, 19}) вычислительной ячейки соединен с (3-i)-м выходом (k-3+i)-й вычислительной ячейки, а первые выходы одиннадцатой, тринадцатой, семнадцатой, девятнадцатой и вторые выходы девятнадцатой, восемнадцатой, шестнадцатой, пятнадцатой вычислительных ячеек являются соответственно первым, вторым, третьим, четвертым и пятым, шестым, седьмым, восьмым выходами логического процессора, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого подключены соответственно к первым и вторым входам третьей, пятой, четвертой, шестой вычислительных ячеек.

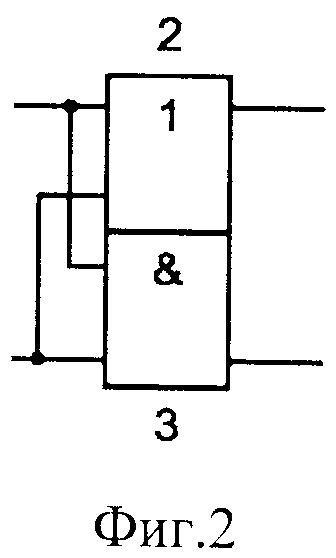

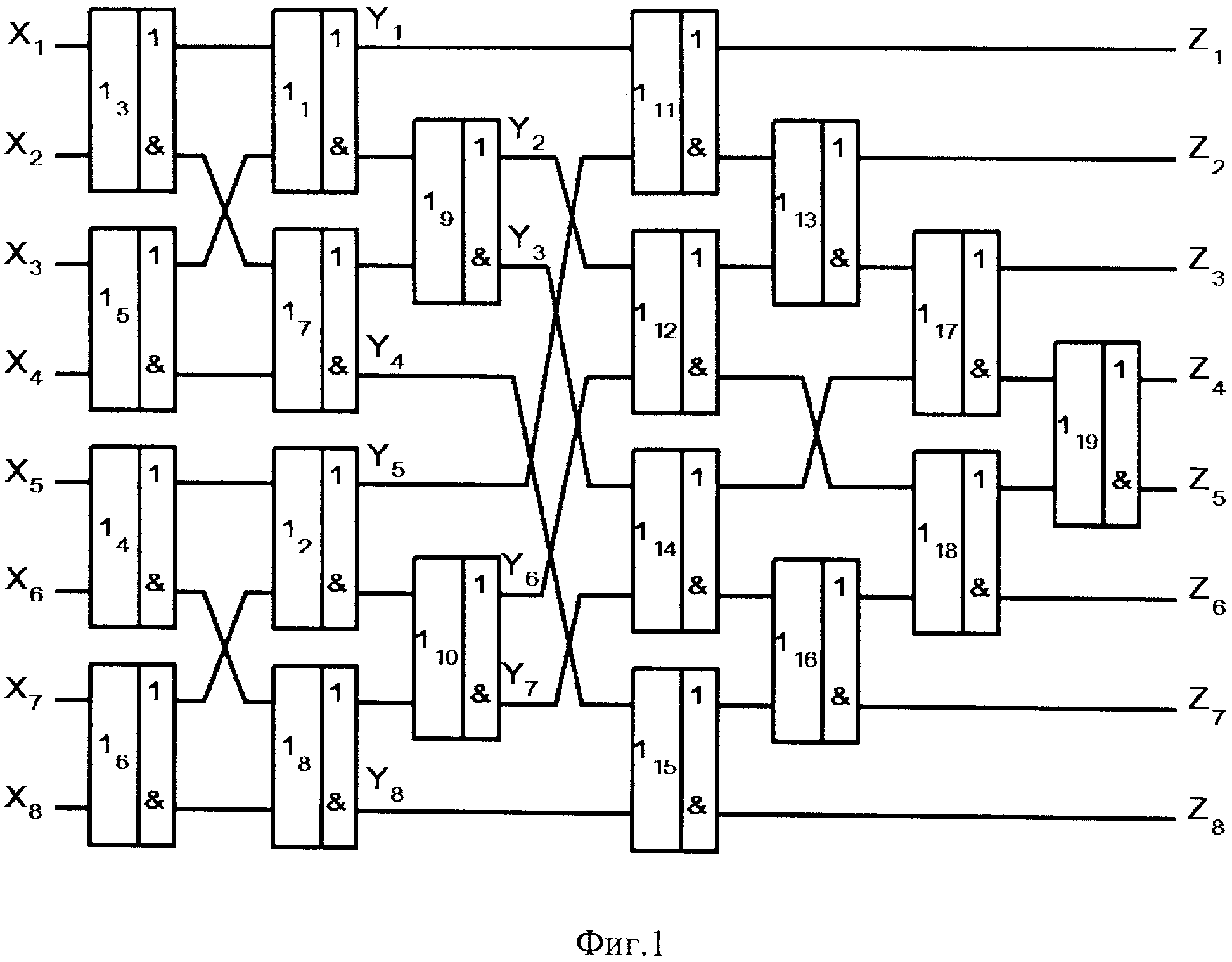

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического процессора и схема вычислительной ячейки, использованной при построении указанного процессора.

Логический процессор содержит вычислительные ячейки 11,…,119. Каждая вычислительная ячейка содержит элемент ИЛИ 2, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент И 3, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу. Первый, второй входы ячейки 1i

и первой, второй входы ячейки j=й

и первой, второй входы ячейки j=й  подключены соответственно к первым выходам ячеек 1i+2, 1i+4 и вторым выходам ячеек 1j-4, 1j-2, первые выходы ячеек 1i, 1j и вторые выходы ячеек 1i, 1j соединены соответственно с i-ым входом ячейки 111, вторым входом ячейки 1j+2 и первым входом ячейки 1i+8, (j-6)-ым входом ячейки 115, первый, второй выходы ячейки 1i+8, первый, второй входы ячейки 117 и первый, второй входы ячейки 118 подключены соответственно к i-ым входам ячеек 112, 114, второму выходу ячейки 113, первому выходу ячейки 114 и второму выходу ячейки 112, первому выходу ячейки 116, i-й вход ячейки 1k(k∈{13, 16, 19}) соединен с (3-i)-ым выходом ячейки 1k-3+i, а первые выходы ячеек 111, 113, 117, 119 и вторые выходы ячеек 119, 118, 116, 115 являются соответственно первым, вторым, третьим, четвертым и пятым, шестым, седьмым, восьмым выходами логического процессора, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого подключены соответственно к первым и вторым входам ячеек 13, 15, 14, 16.

подключены соответственно к первым выходам ячеек 1i+2, 1i+4 и вторым выходам ячеек 1j-4, 1j-2, первые выходы ячеек 1i, 1j и вторые выходы ячеек 1i, 1j соединены соответственно с i-ым входом ячейки 111, вторым входом ячейки 1j+2 и первым входом ячейки 1i+8, (j-6)-ым входом ячейки 115, первый, второй выходы ячейки 1i+8, первый, второй входы ячейки 117 и первый, второй входы ячейки 118 подключены соответственно к i-ым входам ячеек 112, 114, второму выходу ячейки 113, первому выходу ячейки 114 и второму выходу ячейки 112, первому выходу ячейки 116, i-й вход ячейки 1k(k∈{13, 16, 19}) соединен с (3-i)-ым выходом ячейки 1k-3+i, а первые выходы ячеек 111, 113, 117, 119 и вторые выходы ячеек 119, 118, 116, 115 являются соответственно первым, вторым, третьим, четвертым и пятым, шестым, седьмым, восьмым выходами логического процессора, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого подключены соответственно к первым и вторым входам ячеек 13, 15, 14, 16.

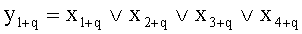

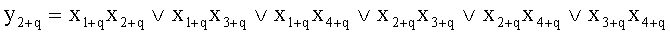

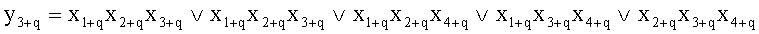

Работа предлагаемого логического процессора осуществляется следующим образом. На его первый,…, восьмой входы подаются соответственно двоичные сигналы х1, …, х8∈{0,1}. Тогда сигналы y1, …, y8 (см. фиг.1) будут определяться выражениями

,

,

,

,

,

,

где q∈{0,4};  есть символы операций ИЛИ, И. В представленной ниже таблице приведены значения сигналов на выходах предлагаемого процессора при всех возможных наборах значений сигналов y1, …, y8.

есть символы операций ИЛИ, И. В представленной ниже таблице приведены значения сигналов на выходах предлагаемого процессора при всех возможных наборах значений сигналов y1, …, y8.

|

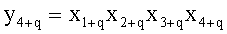

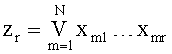

Таким образом, на r-м  выходе предлагаемого процессора имеем

выходе предлагаемого процессора имеем

где xm1, …, xmr∈{x1, …, x8} (1≤m1<…<mr≤8);  есть количество неповторяющихся конъюнкций xm1…xmr, определяемое как число сочетаний из восьми по r. Следовательно, zr=τr, где τr, есть r-я. простая симметричная булевая функция восьми аргументов (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974 г.).

есть количество неповторяющихся конъюнкций xm1…xmr, определяемое как число сочетаний из восьми по r. Следовательно, zr=τr, где τr, есть r-я. простая симметричная булевая функция восьми аргументов (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974 г.).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический процессор обладает более высоким по сравнению с прототипом быстродействием, так как реализует восемь простых симметричных булевых функций, зависящих от восьми аргументов - входных двоичных сигналов, за время, не превышающее 7Δtя, где Δtя - длительность задержки, вносимой вычислительной ячейкой.

Логический процессор, предназначенный для реализации восьми простых симметричных булевых функций, зависящих от восьми аргументов - входных двоичных сигналов, содержащий семь вычислительных ячеек, каждая из которых содержит элемент ИЛИ, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент И, первый, второй входы и выход которого соединены соответственно с ее первым, вторым входами и вторым выходом, отличающийся тем, что в него дополнительно введены двенадцать аналогичных упомянутым вычислительных ячеек, причем первый, второй входы i-й и первый, второй входы j-й вычислительных ячеек подключены соответственно к первым выходам (i+2)-й, (i+4)-й и вторым выходам (j-4)-й, (j-2)-й вычислительных ячеек, первые выходы i-й, j-й и вторые выходы i-й, j-й вычислительных ячеек соединены соответственно с i-м входом одиннадцатой, вторым входом (j+2)-й и первым входом (i+8)-й, (j-6)-м входом пятнадцатой вычислительных ячеек, первый, второй выходы (i+8)-й, первый, второй входы семнадцатой и первый, второй входы восемнадцатой вычислительных ячеек подключены соответственно к i-м входам двенадцатой, четырнадцатой, второму выходу тринадцатой, первому выходу четырнадцатой и второму выходу двенадцатой, первому выходу шестнадцатой вычислительных ячеек, i-й вход k-й (k∈{13, 16, 19}) вычислительной ячейки соединен с (3-i)-м выходом (k-3+i)-й вычислительной ячейки, а первые выходы одиннадцатой, тринадцатой, семнадцатой, девятнадцатой и вторые выходы девятнадцатой, восемнадцатой, шестнадцатой, пятнадцатой вычислительных ячеек являются соответственно первым, вторым, третьим, четвертым и пятым, шестым, седьмым, восьмым выходами логического процессора, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого подключены соответственно к первым и вторым входам третьей, пятой, четвертой, шестой вычислительных ячеек.