УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ

Вид РИД

Изобретение

Предлагаемое устройство относится к формирователям сложных радиолокационных сигналов и может быть использовано в составе импульсной РЛС.

В настоящее время наиболее широко применяемым сложным сигналом является сигнал с линейной частотной модуляцией /ЛЧМ/. Это обусловлено гребнеобразной формой функции неопределенности, при которой значительные допплеровские расстройки мало влияют на амплитуду сжатого сигнала.

Характерной тенденцией развития современных радиолокационных систем является повышение их помехозащищенности. Один из методов борьбы с активными помехами состоит в излучении зондирующего сигнала несколькими передатчиками на различных несущих частотах с последующим выделением в приемном устройстве частотного канала, наименее пораженного помехами /1/. Для сокращения числа передатчиков зондирующего сигнала его излучают одним передатчиком в виде периодически следующих пачек радиоимпульсов с разными несущими частотами. При этом формирование импульсов пачки осуществляется на промежуточной частоте, а разные несущие частоты получаются путем переключения частоты гетеродина при переносе на СВЧ. Кроме борьбы с активными помехами использование пачки радиоимпульсов с разными несущими частотами позволяет построить систему внутрипериодной СДЦ, отличающуюся от традиционной межпериодной СДЦ уменьшением числа зон слепых скоростей и другими преимуществами /2/.

Таким образом, формирование периодических последовательностей пачек радиоимпульсов с ЛЧМ является актуальной задачей и направлено на повышение помехозащищенности РЛС.

Рассмотрим возможности формирования пачек ЛЧМ сигналов известными устройствами.

В качестве первого аналога возьмем пассивный формирователь ЛЧМ сигналов, содержащий последовательно включенные формирователь запускающих импульсов, усилитель мощности, дисперсионную ультразвуковую линию задержки /ДУЛЗ/ и компенсирующий усилитель /3/.

К недостаткам пассивного формирователя относятся большие потери на преобразование электрических колебаний в поверхностно-акустические волны и обратно /-35…-50 дБ/, техническая сложность получения высоких отношений сигнал/шум на выходе формирователя, невозможность регулировки скорости перестройки частоты ЛЧМ сигнала /см. /4/, стр. 37-38/, наличие ложных сигналов, обусловленных прямым прохождением запускающего импульса на выход формирователя, а также переотражениями в ДУЛЗ. Последний недостаток значительно затрудняет качественное формирование пачек ЛЧМ сигналов пассивным методом.

В качестве второго аналога рассмотрим цифровой формирователь ЛЧМ сигнала /см. /4/, стр. 55-57/, содержащий формирователь кода фазы, постоянное запоминающее устройство, два цифроаналоговых преобразователя /ЦАП/ и однополосный модулятор.

Необходимость выполнения сложных операций ограничивает быстродействие данного формирователя, а следовательно, и девиацию частоты формируемого ЛЧМ сигнала, что является недостатком второго аналога как при формировании одиночных ЛЧМ сигналов, так и при формировании их пачек.

В качестве третьего аналога рассмотрим известное устройство формирования сигналов с ЛЧМ. По технической сущности оно является наиболее близким к заявляемому устройству, поэтому выбираем его в качестве прототипа.

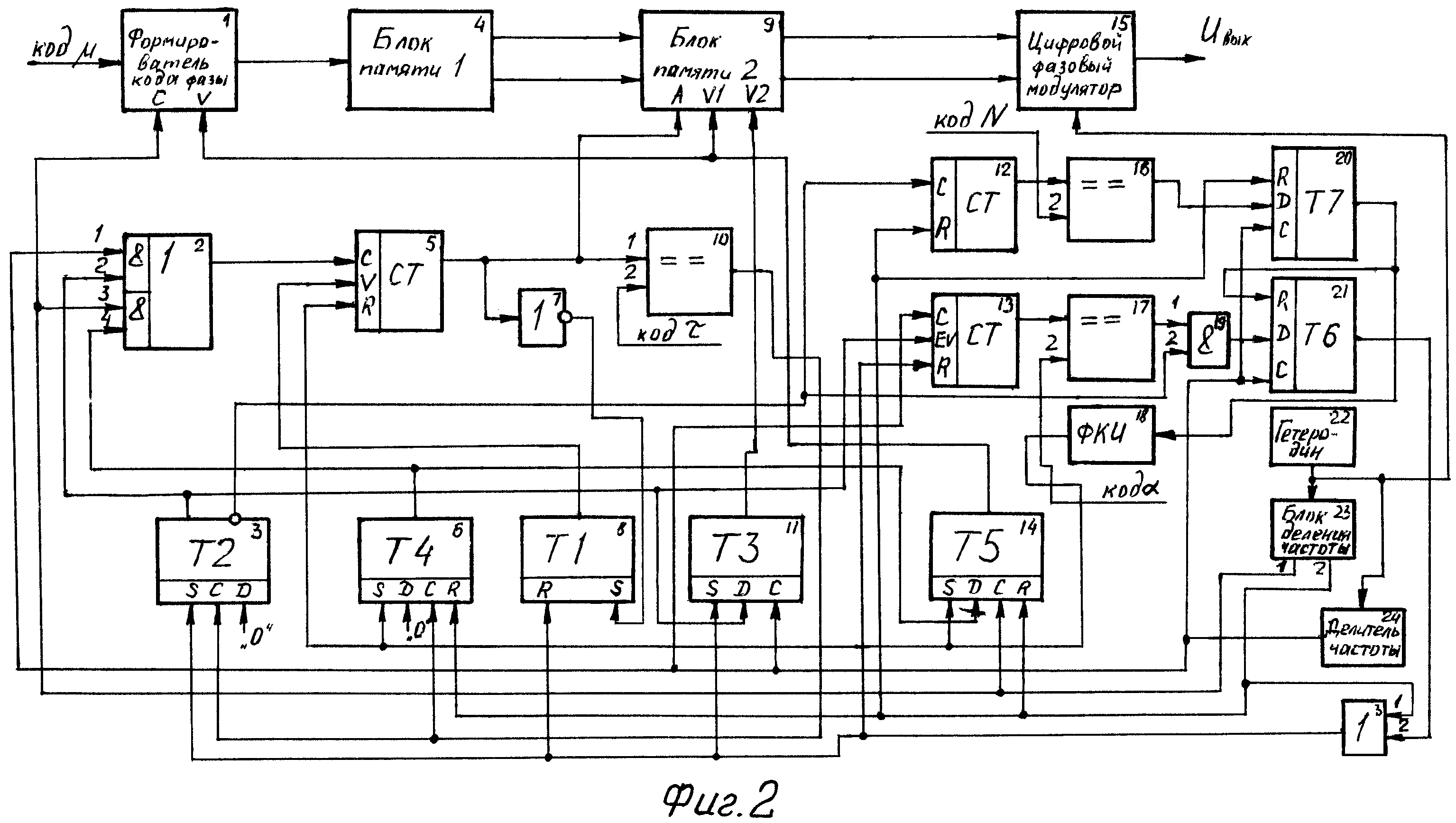

На фиг. 1 представлена функциональная схема прототипа. Устройство содержит первый накопитель 1, второй накопитель 5, цифровой умножитель на два 8, цифровой сумматор 10, выход первого накопителя 1 подключен к информационному входу второго накопителя 5 и первому входу цифрового сумматора 10, а выход второго накопителя 5 через цифровой умножитель на два 8 подключен ко второму входу цифрового сумматора 10, первый блок памяти 11, вход которого соединен с выходом цифрового сумматора 10, второй блок памяти 14, информационные входы которого подключены к выходам первого блока памяти 11, два ЦАП 16, 17, два фильтра 20, 21, два аналоговых перемножителя 23, 24, аналоговый сумматор 27, полосовой фильтр 28, входы ЦАП 16, 17 подключены к выходам второго блока памяти 14, а выходы ЦАП 16, 17 через фильтры 20, 21 подключены к первым входам аналоговых перемножителей 23, 24, выходы которых соединены со входами аналогового сумматора 27, выход которого соединен со входом полосового фильтра 28, гетеродин 25, КФР 22, БДЧ 26, делитель частоты 19, выход гетеродина 25 подключен ко входам БДЧ 26, делителя частоты 19 и КФР 22, вторые входы аналоговых перемножителей 23, 24 соединены с выходами КФР 22, элемент 2-2И-2ИЛИ 3, реверсивный счетчик 6, элемент ИЛИ-НЕ 9, элемент сравнения 13, первый триггер 7, второй триггер 2, третий триггер 12, четвертый триггер 4, пятый триггер 15, ФКИ 18, первый выход БДЧ 26 соединен с С-входом пятого триггера 15, третьим входом элемента 2-2И-2ИЛИ 3 и С-входами накопителей 1, 5, второй выход БДЧ 26 соединен с R-входами первого, четвертого и пятого триггеров и с S-входами второго и третьего триггеров, выход делителя частоты 19 соединен с С-входом третьего триггера 12 и с первым входом элемента 2-2И-2ИЛИ 3, выход которого подключен к С-входу реверсивного счетчика 6, выход которого соединен с адресным входом второго блока памяти 14, с первым входом элемента сравнения 13 и входом элемента ИЛИ-НЕ 9, выход которого подключен к S-входу первого триггера 7, выход которого подключен к V-входу реверсивного счетчика 6, выход элемента сравнения 13 подключен к С-входам второго и четвертого триггеров, на D-входы которых подан уровень логического 0, выход второго триггера 2 подключен ко второму входу элемента 2-2И-2ИЛИ и к D-входу третьего триггера 12, выход которого подключен ко входу режима считывания /V2/ второго блока памяти 14 и к входу ФКИ 18, выход которого подключен к R-входу реверсивного счетчика 6 и к S-входам четвертого и пятого триггеров, выход четвертого триггера 4 соединен с четвертым входом элемента 2-2И-2ИЛИ 3 и с D-входом пятого триггера 15, выход которого подключен к V-входам накопителей 1, 5 и входу режима записи /V1/ второго блока памяти 14, информационный вход первого накопителя 1 является входом кода скорости перестройки частоты ЛЧМ-сигнала, второй вход элемента сравнения 13 - входом кода длительности формируемых сигналов, второй вход БДЧ 26 - входом кода частоты повторения формируемых сигналов, выход полосового фильтра 28 - выходом устройства.

Рассмотрим кратко работу прототипа по функциональной схеме /фиг. 1/.

Принцип работы формирователя основан на вычислении фазы ЛЧМ сигнала φi в дискретные моменты времени ti, где ti=iΔt, i=0, 1, 2, 3 …, а Δt=1/fт, где fт - тактовая частота.

Эта процедура реализуется с помощью накопителей. Схема управления, состоящая из триггеров, счетчика, элемента сравнения, элемента ИЛИ-НЕ, элемента 2-2И-2ИЛИ, делителя частоты, блока деления частоты, формирователя коротких импульсов, формирует управляющие сигналы, обеспечивающие работу устройства.

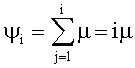

На выходе первого накопителя 1 на i-м такте работы формируется код:  ,

,

где i=0, 1, 2, 3, … τ,

τ - код длительности сигнала.

На выходе второго накопителя 5 на i-м такте работы формируется код:

Код ηi удваивается в цифровом умножителе 9 на два и подается на второй вход цифрового сумматора 10, на выходе которого имеем код фазы ЛЧМ сигнала: φi=ψi+2ηi=µi2

Устройство, объединяющее в своем составе блоки 1, 5, 8, 10 и вырабатывающее код φi, назовем формирователем кода фазы /ФКФ/.

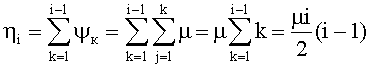

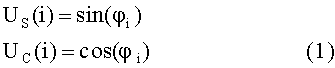

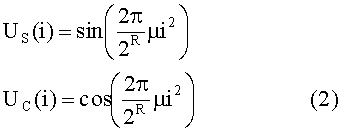

Этот код поступает на адресный вход ПЗУ (первого блока памяти 11), в котором записаны выборки функций:

На выходах первого блока памяти 11 при этом будут выборки:

,

,

где i=0, 1, 2, 3, … τ

Эти выборки записываются на второй блок памяти 14, представляющий из себя ОЗУ, и затем считываются из второго блока памяти по сигналам из схемы управления дважды.

На выходах второго блока памяти 14 будут выборки, аналогичные формулам (2), но i будет изменяться от -τ до τ. Эти выборки поступают на ЦАП 16, 17, а затем на фильтры нижних частот 20, 21. На выходах этих фильтров имеются непрерывные аналоговые сигналы:

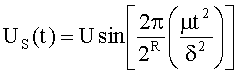

, где

, где

Устройство, реализующее формирование ЛЧМ сигнала на частоте ωо из цифрового квадратурного кода и состоящее из блоков 16, 17, 20, 22, 21, 23, 24, 27, 28, назовем цифровым фазовым модулятором /ЦФМ/.

Сигналы US(t) и UC(t) поступают на аналоговые перемножители 23, 24, где перемножаются с высокочастотными квадратурными колебаниями КФР 22 и суммируются на аналоговом сумматоре 27, так что выходной сигнал ЦФМ:

Uвых(t)=Usin(ωоt+βt2), t∈[-δτ; δτ]

Таким образом, устройство-прототип позволяет формировать периодически повторяющиеся радиоимпульсы с ЛЧМ.

Недостатком устройства-прототипа является невозможность формирования пачек ЛЧМ сигналов, что обусловлено самим построением формирователя (5).

Целью настоящего изобретения является расширение функциональных возможностей устройства-прототипа, выражающееся в обеспечении возможности формирования периодически повторяющихся пачек радиоимпульсов с ЛЧМ. При этом количество импульсов в пачке, а также временной интервал между ними должны быть перестраиваемыми.

Поставленная цель достигается тем, что в известное устройство, содержащее формирователь кода фазы (ФКФ), первый блок памяти, второй блок памяти, цифровой фазовый модулятор, элемент 2-2И-2ИЛИ, реверсивный счетчик, элемент ИЛИ-НЕ, элемент сравнения, первый, второй, третий, четвертый и пятый триггеры, формирователь коротких импульсов, гетеродин, блок деления частоты, делитель частоты, дополнительно введены первый и второй счетчики, второй и третий элементы сравнения, шестой и седьмой триггеры, элемент 2И, элемент 2ИЛИ, первый вход которого подключен ко второму выходу БДЧ, второй вход элемента 2ИЛИ соединен с выходом шестого триггера, выход элемента 2ИЛИ подключен к S-входам второго и третьего триггера и к R-входу первого триггера и ко входу обнуления второго счетчика, счетный вход которого подсоединен к выходу делителя частоты, вход разрешения счета второго счетчика подключен к выходу второго триггера, выход этого счетчика соединен с первым входом третьего элемента сравнения, на второй вход которого подан код длительности паузы между импульсами α, выход третьего элемента сравнения соединен с первым входом элемента 2И, второй вход которого подключен к инверсному выходу второго триггера, выход элемента 2И подключен к D-входу шестого триггера, тактовый вход которого соединен с выходом делителя частоты и R-вход этого триггера соединен с выходом седьмого триггера, к счетному входу первого счетчика подключен инверсный выход второго триггера, а вход обнуления этого счетчика соединен со вторым выходом БДЧ, выход первого счетчика соединен со входом второго элемента сравнения, на второй вход которого подан код количества импульсов в пачке N, выход второго элемента сравнения соединен с D-входом седьмого триггера, тактовый вход которого соединен с выходом делителя частоты и R-вход этого триггера соединен со вторым выходом БДЧ, выход седьмого триггера соединен со входом формирователя коротких импульсов.

Введение первого счетчика позволяет считать импульсы в пачке и формировать текущий код их количества, введение второго элемента сравнения позволяет формировать управляющий импульс для седьмого триггера, а он, в свою очередь, формирует управляющие импульсы для ФКИ, введение второго счетчика позволяет считать импульсы тактовой частоты в течении паузы между импульсами в пачке и формировать текущий код количества тактовых импульсов, введение третьего элемента сравнения позволяет вырабатывать управляющие импульсы для шестого триггера, элемент 2И стробирует эти импульсы, введение шестого триггера позволяет формировать управляющие импульсы для запуска режима, считывания со второго блока памяти, элемент 2ИЛИ суммирует эти импульсы с импульсами со второго выхода БДЧ.

В результате применение заявляемого устройства дает возможность повысить помехозащищенность РЛС путем излучения импульсов в пачке на различных несущих частотах и последующего выделения канала, наименее пораженного активными помехами. Кроме того, использование пачек импульсов дает возможность построения внутрипериодной системы СДЦ, которая позволяет отодвинуть первую слепую скорость за пределы рабочего диапазона скоростей целей и тем самым устранить потери, связанные с введением вобуляции частоты и достигающие 19 дБ /6/.

Авторам не известны технические решения, имеющих совокупность отличительных признаков, присущих предлагаемому устройству.

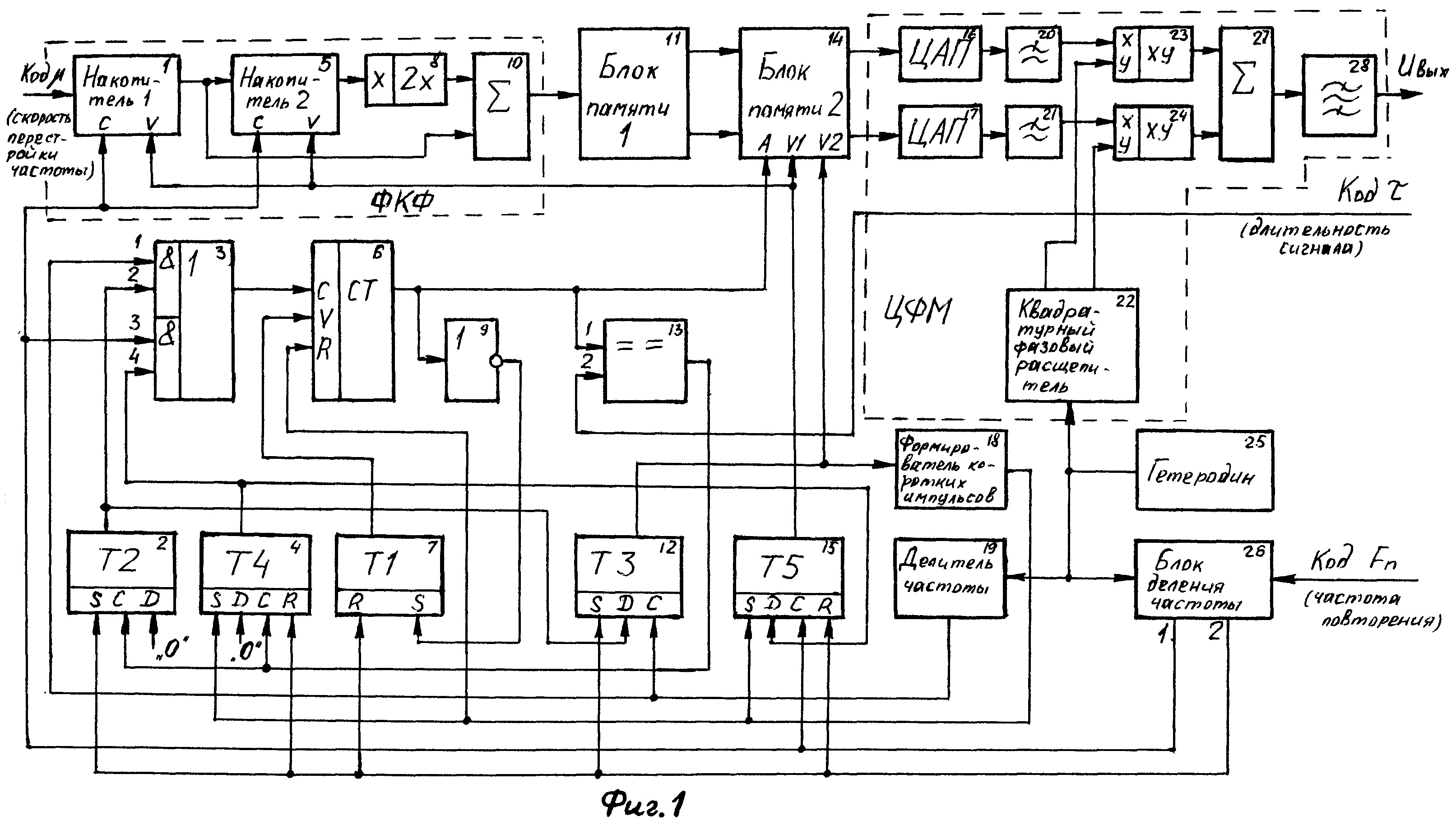

На фиг. 2 приведена функциональная схема предлагаемого устройства.

Устройство состоит из ФКФ 1, элемента 2-2И-2ИЛИ 2, первого блока памяти 4, второго блока памяти 9, ЦФМ 15, реверсивного счетчика 5, элемента ИЛИ-НЕ 17, первого элемента сравнения 10, первого триггера 8, второго триггера 3, третьего триггера 11, четвертого триггера 6, пятого триггера 14, на информационный вход ФКФ 1 подается код ЛЧМ сигнала µ, выход ФКФ 1 подключен к входу первого блока памяти 4, выходы первого блока памяти 4 подключены к информационным входам второго блока памяти 9, выходы второго блока памяти подключены к информационным входам ЦФМ 15, с выхода ЦФМ 15 снимается напряжение сформированного ЛЧМ сигнала, ФКИ 18, гетеродин 22, БДЧ 23, делитель частоты 24, элемент 2ИЛИ 25, выход делителя частоты 24 подключен к С-входу третьего триггера 11 и к первому входу элемента 2-2И-2ИЛИ 2, выход ФКИ 18 подключен к S-входам четвертого и пятого триггеров и к R-входу реверсивного счетчика 5, первый выход БДЧ 23 подключен к С-входам пятого триггера 14 и ФКФ 1 и к третьему входу элемента 2-2И-2ИЛИ 2, второй выход БДЧ 23 подключен к первому входу элемента 2ИЛИ 25 и к R-входам четвертого 6 и пятого 14 триггеров, выход элемента 2ИЛИ 25 подключен к S-входам второго 3 и третьего 11 триггеров и к R-входу первого триггера 8, выход первого триггера 8, подключен к V-входу режима счета реверсивного счетчика 5, счетный вход этого счетчика соединен с выходом элемента 2-2И-2ИЛИ 2, выход реверсивного счетчика 5 подключен к адресному входу А второго блока памяти 9, к первому входу первого элемента сравнения 10 и ко входу элемента ИЛИ-НЕ 7, выход которого подключен к S-входу первого триггера 8, на второй вход первого элемента сравнения 10 подан код длительности импульса в пачке τ, выход этого элемента подключен к С-входам второго 3 и четвертого 6 триггеров, на D-входы которых подано напряжение логического нуля, выход второго триггера 3 подключен ко второму входу элемента 2-2И-2ИЛИ 2 и к D-входу третьего триггера 11, выход которого подключен ко входу разрешения считывания V2 второго блока памяти 9, выход четвертого триггера 6 соединен с четвертым входом элемента 2-2И-2ИЛИ 2 и с D-входом пятого триггера 14, выход которого подключен ко входу разрешения записи V1 второго блока памяти 9 и к V-входу ФКФ 1, выход гетеродина 22 подключен ко входам ЦФМ 15, БДЧ 23 и делитель частоты 24, в устройство также входят первый 12 и второй 13 счетчики, второй 16 и третий 17 элементы сравнения, элемент 2И 19, шестой 20 и седьмой 21, триггеры, счетный вход первого счетчика 12 подключен к инверсному выходу второго триггера 3, R-вход этого счетчика соединен со вторым выходом БДЧ 23, выход счетчика 12 подключен к первому входу второго элемента сравнения 16, на второй вход которого подан код количества импульсов в пачке N, выход второго элемента сравнения подключен к D-входу седьмого триггера 20, С-вход которого подключен к выходу делителя частоты 24, и R-вход этого же триггера подсоединен ко второму выходу БДЧ 23, выход седьмого триггера 20 подсоединен ко входу ФКИ 18 и к R-входу шестого триггера 21, счетный С-вход второго счетчика 13 подключен к выходу делителя частоты 24, R-вход этого счетчика подсоединен к выходу элемента 2ИЛИ 25, выход второго триггера 3 подключен ко входу разрешения счета EV второго счетчика 13, выход этого счетчика подсоединен к первому входу третьего элемента сравнения 17, на второй его вход подан код длительности паузы между импульсами в пачке α, выход третьего элемента сравнения 17 подключен к первому входу элемента 2И 19, второй вход этого элемента подсоединен к инверсному выходу второго триггера 3, выход элемента 2И 19 соединен с D-входом шестого триггера 21, к С-входу этого триггера подключен выход делителя частоты 24, выход шестого триггера 21 подключен ко второму входу элемента 2ИЛИ 25.

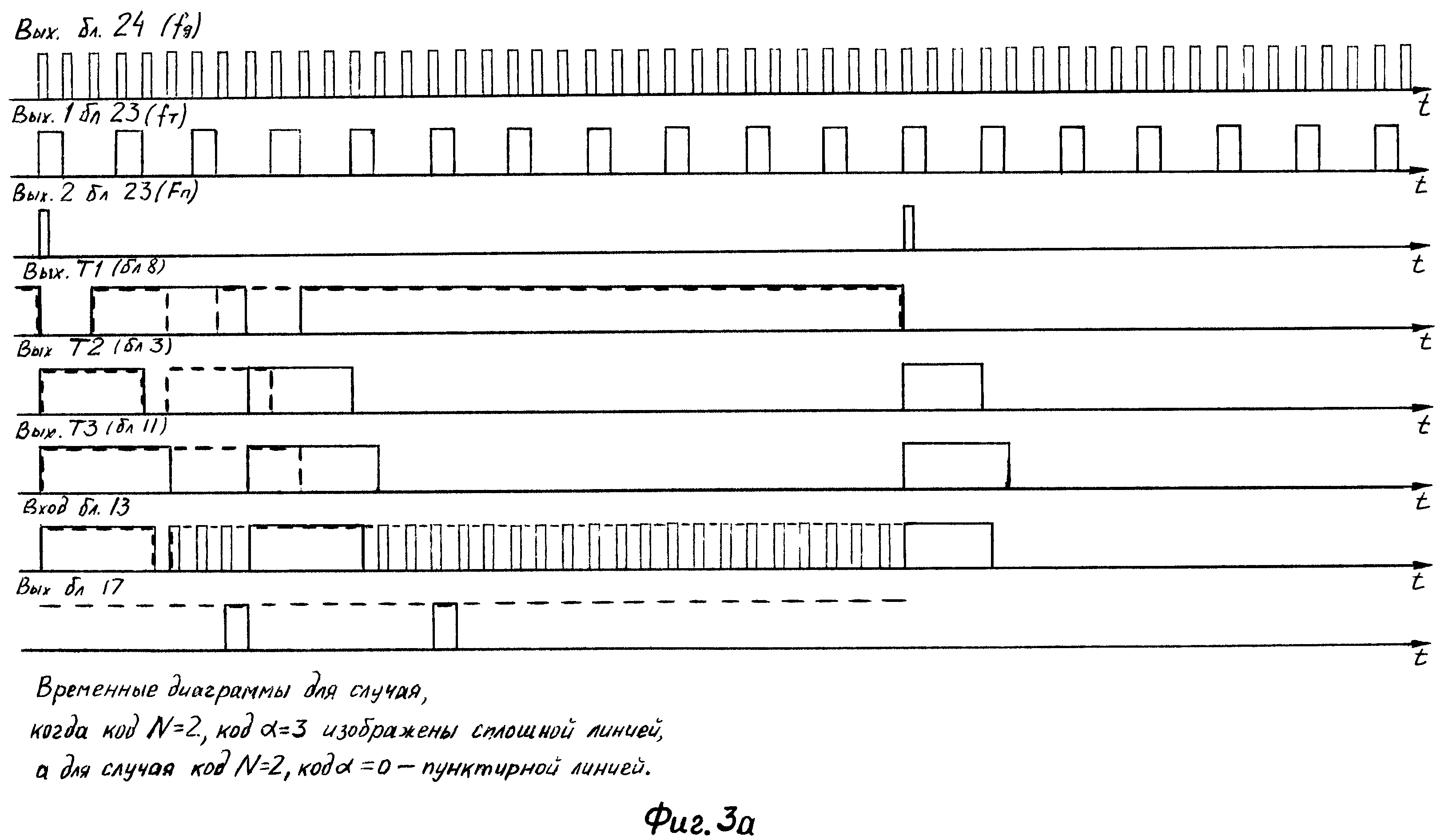

Рассмотрим работу предлагаемого устройства по функциональной схеме /рис. 2/ и временным диаграммам /фиг. 3/.

В исходном состоянии на выходах первого 8 и седьмого 20 триггеров имеется уровень логической единицы, на выходах остальных триггеров - уровень логического нуля. При этом элемент 2-2И-2ИЛИ 2 имеет на выходе уровень 0, так как на его входы 2 и 4 поступают уровни 0 со второго и четвертого триггеров, а реверсивный счетчик 5 находится в состоянии хранения информации, причем на его выходе имеется код длительности сигнала τ, у первого счетчика 12 на выходе находится код количества импульсов в пачке N, полученные в результате работы устройства на предыдущем этапе. У второго счетчика 13 выходное состояние значения не имеет.

На вход режима V ФКФ 1 подается уровень 0 с выхода пятого триггера 14, при этом ФКФ находится в состоянии хранения информации. На входы V1 и У2 второго блока памяти 9 подаются уровни логического 0 с выходов пятого и третьего триггеров, при этом второй блок памяти 9 представляющий из себя оперативное запоминающее устройство, находится в режиме хранения информации.

Импульс запуска, следующий с частотой повторения Fп со второго выхода БДЧ 23, устанавливает первый 8 и седьмой 20 триггеры в состояние логического нуля 0, второй и третий триггеры - в состояние логической 1, четвертый и пятый триггеры дополнительно устанавливает в состояние 0, кроме того, обнуляет первый и второй счетчики.

Когда на выходе второго триггера 3 устанавливается уровень логической 1, он поступает на вход 2 элемента 2-2И-2ИЛИ 2, импульсы fд с выхода делителя частоты 24 через элемент 2-2И-2ИЛИ 2 поступают на вход реверсивного счетчика 5, который начинает работать в режиме вычитания, так как на его V-вход подан уровень 0 с выхода первого триггера 8. При этом код на выходе реверсивного счетчика 5 с приходом каждого импульса частоты fд уменьшается на единицу. Этот код поступает на адресный вход второго блока памяти, который находится в режиме считывания, так как на его вход V2 подан уровень 1 с третьего триггера 11. На выходе появляются выборки сигнала, сформированного на предыдущем периоде повторения и записанные с ячейки с номерами τ, τ-1, τ-2 и так далее.

Когда выходной код реверсивного счетчика 5 достигает значения 0, на выходе элемента ИЛИ-НЕ 7 появляется уровень логической 1, который подается на V-вход реверсивного счетчика, который начинает работать в режима суммирования, коды у него на выходе изменяются, как 0, 1, 2, 3, …. При этом содержимое второго блока памяти 9 считывается вторично в обратной последовательности.

Когда код реверсивного счетчика достигает значения τ, на выходе элемента сравнения 10 появляется импульс уровня логической 1, который своим передним фронтом устанавливает второй триггер 3 в состояние логического 0, так как на его D-входе постоянно присутствует уровень логического нуля. При этом уровень 0 подается на вход 2 элемента 2-2И-2ИЛИ 2 и импульсы частоты fд перестают поступать на счетный вход реверсивного счетчика 5. Уровень 0 со второго триггера 3 поступает на D-вход третьего триггера 11, который также устанавливается в 0 по фронту следующего импульса частоты fд, то есть импульс на выходе третьего триггера будет длиннее импульса второго триггера на период частоты fд, что необходимо для того, чтобы последняя выборка формируемого сигнала с адресом τ успела считаться со второго блока памяти 9. Когда на выходе третьего триггера 11 устанавливается 0, второй блок памяти переходит в режим хранения информации. При этом в зависимости от длительности паузы α возможны два основных режима работы.

Наиболее общий режим работы - когда существует ненулевое значение кода паузы. Тогда по окончании импульса второго триггера 3 начинает считать импульсы fд второй счетчик 13, бывший до этого в состоянии обнуления после поступления импульса Fп через элемент 2ИЛИ 25 на его R-вход и удерживаемый в этом состоянии импульсом с выхода второго триггера 3 по входу разрешения счета EV. При этом первый поступающий на счетчик импульс не изменяет состояния счетчика, так как счетчик начинает работать по окончании импульса второго триггера, а задний фронт этого импульса задержан на время срабатывания триггера относительно соответствующего импульса fд. Когда код на выходе второго счетчика 13, возрастающий на 1 с каждым импульсом fд, достигает значения кода паузы α, на выходе третьего элемента сравнения 17 появляется уровень логической 1, который через элемент 2И 19, стробируемый с импульсами с инверсного выхода второго триггера 3, подается на D-вход шестого триггера 21 и этот уровень 1 через период частоты fд появляется на выходе данного триггера, находившегося в состоянии обнуления после работы на предыдущем периоде повторения. Этот уровень логической 1 через элемент 2ИЛИ 25 поступает на S-входы второго и третьего триггеров, R-вход первого триггера, запуская вновь режим считывания выборок сигнала со второго блока памяти 9. Этот же уровень обнуляет второй счетчик 13, поступая на его R-вход. При этом происходит запрещение счета во втором счетчике 13 импульсом с выхода второго триггера 3, на выходах третьего элемента сравнения 17 и элемента 2И 19 устанавливается уровень 0, который через период частоты fд появляется на выходе шестого триггера 21. Так формируется импульс запуска для повторения режима считывания выборок формируемого сигнала со второго блока памяти 9, и, таким образом, формирования следующего импульса пачки.

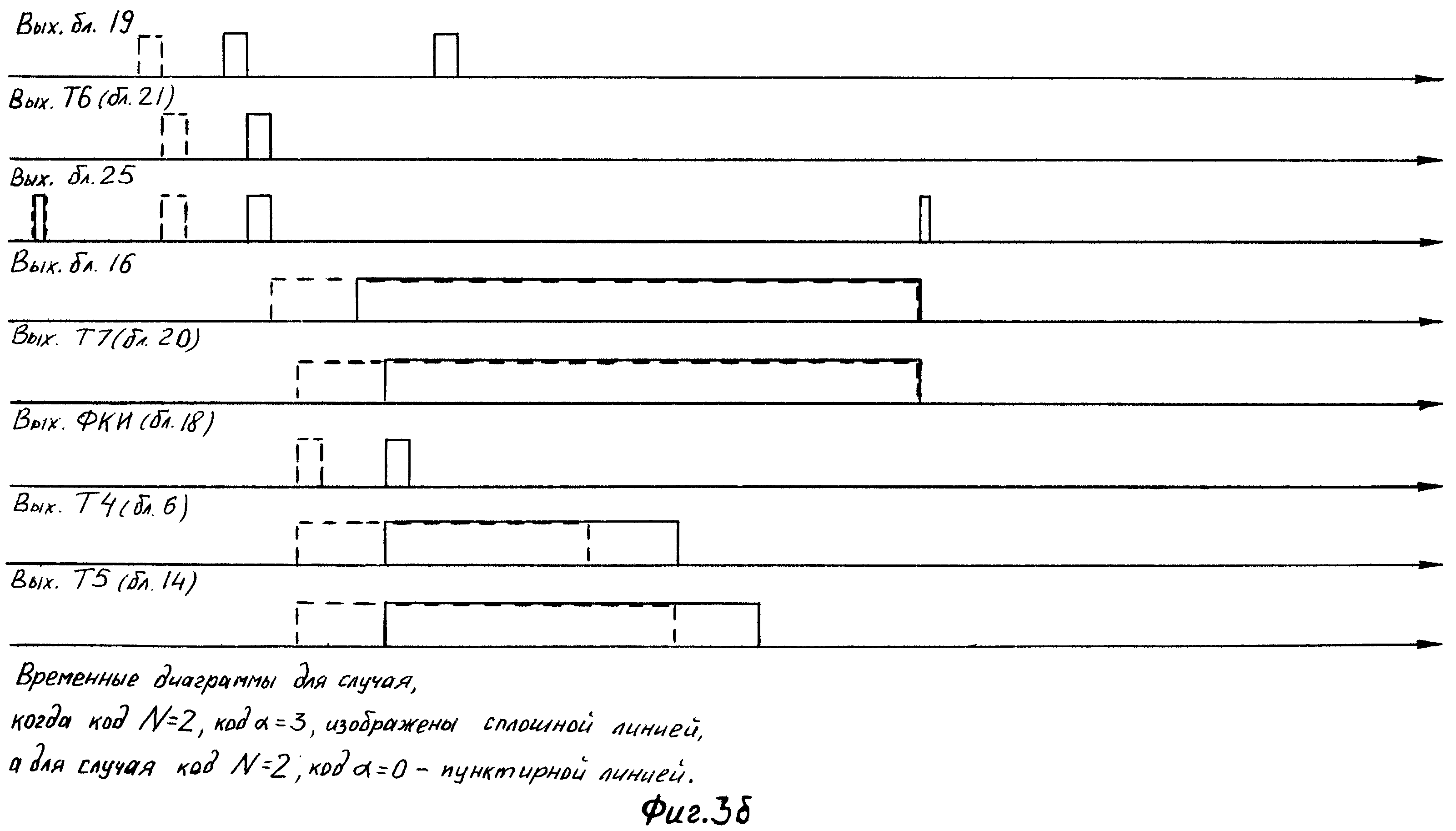

Второй режим работы можно выделить при нулевом коде паузы. При этом на выходе второго счетчика 13 всегда нулевой код и на выходе третьего элемента сравнения 17 всегда существует уровень 1. На выходе элемента 2И 19, стробируемого импульсами с инверсного выхода второго триггера, на протяжении импульса второго триггера существует уровень 0, а по окончании этого импульса устанавливается уровень 1, который через период частоты fд появится на выходе шестого триггера 21 и через элемент 2ИЛИ 25 вновь запускает режим считывания со второго блока памяти 9, причем паузы между импульсами третьего триггера 11 не будет. Импульс с инверсного выхода второго триггера 3 устанавливает на выходе элемента 2И 19 уровень 0, который через период частоты fд появляется на выходе шестого триггера 21. Таким образом, формируется импульс запуска режима считывания выборок сигнала со второго блока памяти 9. В этом режиме на временных диаграммах /фиг. 3/ устройства будут некоторые отличия от основного режима работы. Так, не будет интервала между импульсами третьего триггера и на выходе третьего элемента сравнения 17 постоянно присутствует уровень логической 1. На фиг. 3 этот случаи показан пунктиром. При этом на счетный вход первого счетчика 12, находившегося с начала нового периода повторения в состоянии обнуления, поступают импульсы с инверсного выхода второго триггера и по их переднему фронту код на выходе первого счетчика 12 увеличивается на единицу с приходом каждого импульса. Этот код эквивалентен количеству импульсов в формируемой пачке. При достижении кодом на выходе этого счетчика значения N на выходе второго элемента сравнения 16 возникает уровень 1, подающийся на D-вход седьмого триггера 20, находящегося в состоянии обнуления с момента появления импульса Fп. Через период частоты fд на выходе этого триггера возникает уровень 1, по перепаду уровней 0-1 ФКИ 18 формирует короткий импульс, запускающий режим записи во второй блок памяти 9.

Когда на выходе третьего триггера 11 установится 0, второй блок памяти переходит в режим хранения информации. Импульс с ФКИ 18 поступает на S-входы четвертого и пятого триггеров, устанавливает их в состояние 1 и обнуляет реверсивный счетчик 5, поступая на его R-вход. Уровень логической 1 с выхода четвертого триггера 6 поступает на вход 4 элемента 2-2И-2ИЛИ 2, при этом импульсы частоты fт с первого выхода БДЧ 23 начинают поступать на вход С реверсивного счетчика 5, который по окончании импульса ФКИ 18 начинает работать в режиме суммирования. Одновременно уровень логической 1 с выхода пятого триггера 14 поступает на V-вход ФКФ 1 и на вход режима записи V1 второго блока памяти.

ФКФ реализован по схеме, приведенной на фиг. 1, а принцип работы его рассмотрен при описании прототипа. ФКФ 1 при поступлении на его V-вход уровня 1 начинает вычислять выборки кода фазы ЛЧМ сигнала φi=µi2. Код фазы φi поступает на адресный вход первого блока памяти 4, представляющего из себя постоянное запоминающее устройство, в котором записаны выборки функций (1). На выходах первого блока памяти 4 имеются выборки (2).

Когда код реверсивного счетчика 5 достигает значения τ, на выходе элемента сравнения 10 появляется импульс логической 1, который своим передним фронтом устанавливает четвертый триггер в состояние 0, так как на его D-входе постоянно присутствует уровень логического 0. Уровень логического 0 с выхода четвертого триггера 6 поступает на вход 4 элемента 2-2И-2ИЛИ 2 и импульсы fт с выхода 1 БДЧ 23 перестают поступать на С-вход реверсивного счетчика 5. Кроме того, уровень логического 0 с выхода четвертого триггера 6 поступает на D-вход пятого триггера 14, который переходит в состояние 0 по фронту следующего импульса fт, то есть импульс на выходе пятого триггера 14 будет длиннее импульса на выходе четвертого триггера 6 на период fт, что необходимо для того, чтобы последняя выборка формируемого сигнала с адресом τ успела записаться во второй блок памяти. При этом на выходе шестого триггера постоянно поддерживается уровень 0, принудительно устанавливаемый по его R-входу импульсом с выхода седьмого триггера 20.

Когда импульс на выходе пятого триггера 14 заканчивается, схема приходит в исходное состояние.

Как было показано выше, двукратное считывание сигнала со второго блока памяти 9 происходит N раз, то есть выборки на выходе второго блока памяти каждого парциального импульса будут соответствовать формулам (2), но i будет изменяться от -τ до τ. Считывание происходит с частотой fд в моменты времени ti=iδ, где δ=1/fд, поэтому i=ti/δ и выборки на выходе будут соответствовать формулам (6).

Эти выборки поступают на входы ЦФМ 15. Схема, по которой реализован ЦФМ, приведена на фиг. 1, а принцип работы его рассмотрен при описании прототипа. На выходе ЦФМ будут формироваться ЛЧМ сигналы на промежуточной частоте. Парциальный ЛЧМ сигнал имеет вид:

Uвых=Usin(ωоt+βt2), где t∈[-δτ; δτ].

Число парциальных сигналов равно N, паузы между ними равны αδ.

Рассмотрим реализацию блоков предлагаемого устройства. ФКФ описан в описании прототипа в данной заявке, схема ФКФ приведена на фиг. 1. ФКФ состоит из первого и второго накопителей, цифрового умножителя на два и цифрового сумматора, на вход первого накопителя подается код µ ЛЧМ сигнала, выход первого накопителя соединен со входом второго накопителя и с первым входом цифрового сумматора, выход второго накопителя соединен со входом цифрового умножителя на два, а выход данного умножителя подключен ко второму входу цифрового сумматора, выход этого сумматора является выходом ФКФ, на С-входы накопителей подаются тактовые импульсы fд, на V-входы накопителей подаются управляющие импульсы с выхода пятого триггера.

ЦФМ описан в описании прототипа в данной заявке, схема ЦФМ приведена на фиг. 1. ЦФМ состоит из двух ЦАП, двух фильтров, двух аналоговых перемножителей, аналогового сумматора, полосового фильтра и квадратурного фазового расщепителя, с выхода полосового фильтра снимается выходное напряжение, выход аналогового сумматора подключен ко входу полосового фильтра, к каждому из двух входов аналогового сумматора подключены одинаковые устройства, состоящие из ЦАП, фильтра и аналогового перемножителя, выход ЦАП подключен ко входу фильтра, выход фильтра подключен к первому входу аналогового перемножителя, выход этого перемножителя подключен к одному из входов аналогового сумматора, вход одного из ЦАП подсоединен к выходу второго блока памяти с синусной квадратурной составляющей ЛЧМ сигнала, а ко второму входу аналогового перемножителя, через фильтр соединенного с данным ЦАП, подключен косинусный выход КФР, вход которого ЦАП соединен с выходом второго блока памяти, с косинусной квадратурной составляющей ЛЧМ сигнала, а ко второму входу аналогового перемножителя, через фильтр соединенного с данным ЦАП, подключен синусный выход КФР.

Реализация всех блоков предлагаемого устройства является типовой. Накопители собраны на микросхемах 133 и 134 серий по известной схеме /см. /6/ стр. 741/, умножение на два в двоичном коде осуществляется сдвигом на 1 разряд влево, в качестве первого блока памяти использованы микросхемы 505 РЕ3 со стандартной прошивкой, второй блок памяти выполнен на микросхемах 133 РУ5, остальные цифровые блоки - на микросхемах 133, 530, 533 серий. ФКИ выполнен по схеме, приведенной в /6/, стр. 668. В качестве ЦАП использованы микросхемы К 1118 ПА1, аналоговые перемножители 526 ПС1.

Применение предлагаемого устройства позволяет повысить помехозащищенность радиолокационной системы путем излучения пачки радиоимпульсов на разных несущих частотах с последующим выделением в приемном устройстве канала, наименее пораженного активными помехами, кроме того, использование пачки с разными несущими частотами дает возможность построения системы внутри периодной СДЦ /2/.

Особенностью внутрипериодной системы СДЦ является то, что первая слепая скорость определяется не периодом повторения зондирующего сигнала, а интервалом между импульсами пачки, который может быть сделан значительно меньше периода повторения. Это позволяет обойтись без применения вобуляции частоты зондирующего сигнала, используемой при построении систем межпериодной СДЦ для устранения зон слепых скоростей, и, следовательно, избежать потерь, связанных с введением вобуляции и достигающих 19 дБ /5/.

ЛИТЕРАТУРА

1. Защита от радиопомех. Под ред. Максимова М.В. М., ″Сов. радио″, 1976.

2. ″Внутрипериодная СДЦ″. Березюк В.В. - Судостроительная промышленность, сер. Радиолокация, 1986, вып. 1 с, с. 53-56.

3. Информационный листок ВИМИ, серия ИЛКИА 12-11, №80-0351, Ленинград, ЦНИИ ″Румб″, 1980.

4. В.Н. Кочемасов, Л.А. Белов, В.С. Оконешников. ″Формирование сигналов с линейной частотной модуляцией″. М., ″Радио и связь″, 1983.

5. С.З. Кузьмин. ″Основы проектирования систем цифровой обработки радиолокационной информации″ М., ″Радио и связь″, 1986 г.

6. Справочник по ИМС. Под ред. Тарабрина Б.В. М., ″Энергия″, 1981 г.

Устройство формирования сложных сигналов, содержащее последовательно соединенные формирователь кода фазы, к тактовому входу которого подключен первый выход блока деления частоты, и первый блок памяти, выходы которого подключены к информационным входам второго блока памяти, адресный вход и входы записи и считывания и выходы которого соединены соответственно с выходом реверсивного счетчика, к счетному входу которого подключен выход элемента 2-2И-2ИЛИ, с выходом пятого триггера, который подключен к управляющему входу формирователя кода фазы, с выходом третьего триггера и с информационными входами цифрового фазового модулятора, радиочастотный вход которого соединен с выходом гетеродина и со входами делителя частоты, выход которого подключен к C-входу третьего триггера и к первому входу элемента 2-2И-2ИЛИ, и блока деления частоты, первый и второй выходы которого соединены соответственно с C-входом пятого триггера и с третьим входом элементы 2-2И-2ИЛИ, и с R-входами четвертого и пятого триггеров, к S-входам которых подключен выход формирователя коротких импульсов, который соединен с обнуляющим входам реверсивного счетчика, управляющий вход и выход которого соединены соответственно с выходом первого триггера и с первым входом первого блока сравнения, который подключен ко входу элемента ИЛИ-НЕ, выход которого соединен с S-входом первого триггера, R-вход которого соединен с S-входом третьего триггера и с S-входом второго триггера, выход которого подключен к D-входу третьего триггера и ко второму входу элемента 2-2И-2ИЛИ, четвертый вход которого соединен с выходом четвертого триггера, который подключен к D-входу пятого триггера, D-входы второго и четвертого триггеров являются входами логического нуля устройства, а С-входы второго и четвертого триггеров соединены с выходом первого блока сравнения, второй вход которого является первым кодовым входом устройства, вторым кодовым входом которого является информационный вход формирователя кода фазы, отличающееся тем, что, с целью формирования периодически повторяющихся пачек радиоимпульсов с линейной частотной модуляцией, введены два счетчика, второй и третий блоки сравнения, шестой и седьмой триггеры элемент 2И и элемент 2ИЛИ, первый и второй входы и выход которого соединены соответственно со вторым выходом блока деления частоты, с выходом шестого триггера, к D-входу которого подключен выход элемента 2И и с S-входами второго и третьего триггеров, которые соединены с обнуляющим входом второго счетчика, счетный и разрешающий входы и выход которого соединены соответственно с выходом делителя частоты, с выходом второго триггера и с первым входом третьего блока сравнения, выход которого подключен к первому входу элемента 2И, второй вход которого соединен с инверсным выходом второго триггера, который подключен к счетному входу первого счетчика, обнуляющий вход и выход которого соединены соответственно со вторым выходом блока деления частоты, который подключен к R-входу седьмого триггера, и с первым входом второго блока сравнения, выход которого подключен к D-входу седьмого триггера, С-вход и выход которого соединены соответственно с С-входом шестого триггера, к которому подключен выход делителя частоты, и со входом формирователя коротких импульсов, который подключен к R-входу шестого триггера, причем вторые входы второго и третьего блоков сравнения являются третьим и четвертым кодовыми входами устройства.