Результат интеллектуальной деятельности: Цифровой обнаружитель пачек периодических импульсных сигналов

Вид РИД

Изобретение

Предлагаемое изобретение относится к устройствам цифровой обработки импульсных сигналов, в частности к цифровым обнаружителям периодических импульсных последовательностей, и может быть использовано в устройствах первичной обработки локационной и навигационной аппаратуры.

Известны цифровые обнаружители пачек, содержащих не менее "n" импульсов, представляющие собой сочетание счетчика с дешифратором на "n" единиц (см., например, С.З. Кузьмин "Основы обработки радиолокационных сигналов в АСУ ПВО" изд. АРТА им. Л.А. Говорова, 1964, стр. 56, рис. 2.6, "Теоретические основы радиолокации" под ред. Я.Д. Ширмана, М., "Сов. радио", 1970, стр. 282-288, рис. 552) и осуществляющие выдачу сигнала о наличии пачки при поступлении на счетчик "n" видеоимпульсов. Недостатком таких обнаружителей является низкая помехоустойчивость, т.к. при воздействии импульсных помех, в частности хаотической импульсной помехи (ХИП), создаваемой средствами радиопротиводействия противника, будут иметь место ложные обнаружения за счет накопления помеховых сигналов (импульсов). Для снижения мешающего действия несинхронных импульсных помех на входе устройства обработки включают схемы селекции по периоду повторения обнаруживаемого сигнала, состоящие из цифровых или аналоговых схем задержки на период повторения и схем логического умножения (схем "И"), выделяющие из общего потока сигналов только импульсы, разнесенные на время, равное периоду повторения (стр. 61,82, 66-70, рис. 2.14 указанной выше книги С.З. Кузьмина). Эта типичная структура обнаружителя, представляющая собой цепочку последовательно включенных схемы селекции, счетчика и дешифратора, принята за прототип.

Наличие схемы череспериодного сравнения на входе дискретного накопителя (счетчика) позволяет снизить вероятность ложного обнаружения за счет прохождения на счетчик случайных импульсных помех внутреннего и внешнего происхождения (коммутационных помех, сигналов других РЛС и т.п.), однако при воздействии организованных помех, в частности, ХИП со средней частотой порядка нескольких десятков кГц, однократная селекция по периоду становится малоэффективной, а повышение кратности череспериодного сравнения требует соответствующего увеличения числа схем задержки на период повторения сигнала (единицы мсек), что ведет к резкому увеличению габаритов, сложности и стоимости обнаружителя и снижению его надежности. Это обусловлено тем, что такие схемы (линии) задержки на период, представляющие собой, в частности, многоразрядные регистры сдвига с числом разрядов порядка нескольких тысяч (при использовании элементов серии 186 этому соответствует несколько десятков интегральных микросхем на каждую линию), являются наиболее громоздкими, дорогостоящими и относительно малонадежными узлами обнаружителя. Аналоговые устройства задержки на единицы мсек (ультразвуковые и магнитострикционные линии задержки, магнитные барабаны и др.) в отношении надежности и стоимости имеют показатели одного порядка с цифровыми схемами задержки, а по массе превосходят их, так что указанные выше ограничения остаются в силе и для аналоговых устройств череспериодного сравнения. В связи с этим в цифровых обнаружителях периодических импульсных сигналов по критерию приема "n" импульсов обычно не применяется череспериодное сравнение соответствующей кратности ("n из n"), которая обеспечила бы максимально-возможную для данного критерия помехоустойчивости; в известных технических решениях обычно используется одна-две линии задержки (авт. свид. 499676, пат. США №3508204, патент Великобритании №1272833, схемы рис. 2.14 и 5.54 из упомянутых книг С.З. Кузьмина и Я.Д. Ширмана, соответственно, цифровой фильтр по пат. США №3705358) и, максимально, три линии, что позволяет реализовать критерий селекции "4 из 4-х" (пат. США №3732563). Указанные ограничивающие факторы не позволяют технически реализовать максимально возможную помехоустойчивость в цифровых обнаружителях при "n" больше 3-х - 4-х ввиду резкого ухудшения технико-экономических показателей обнаружителя при увеличении числа линий задержки на период повторения.

Таким образом, недостатком известных обнаружителей периодических импульсных сигналов по критерию приема "n" импульсов является недостаточная помехоустойчивость, ограничиваемая допустимым по технико-экономическим показателям аппаратуры числом линий задержки на период повторения.

Целью предложения является повышение помехоустойчивости обнаружителя путем осуществления череспериодного сравнения по всем "n" сигналам пачки без увеличения числа линий задержки на период повторения.

Указанная цель достигается введением в состав цифрового обнаружителя известной структуры, содержащего счетчик импульсов с дешифратором и входную схему череспериодного сравнения, образованную линией задержки на период повторения "Т" со схемой "И", другой вход которой подключен к входному нормализатору видеосигналов по длительности, ряда дополнительных логических элементов цифровой техники, определенным образом связанных между собой и с элементами известной схемы и обеспечивающих "n-1"-кратную череспериодную селекцию поступающих на счетчик сигналов при использовании одной линии задержки. Согласно предложению выход схемы "И" подключается к счетному входу счетчика через последовательно соединенные схему "ИЛИ", элемент задержки (регистр сдвига) на время, не превышающее T/n, и вторую схему "И", второй вход которой соединен с входом линии задержки на период повторения, выходы нормализатора и регистра сдвига через вторую схему "ИЛИ" подключены к входу линии задержки, а выход второй схемы "И" дополнительно подключен к второму входу первой схемы "ИЛИ" через схему "НЕ-И". Выход дешифратора соединен с инверсным (запрещающим) входом схемы "НЕ-И", а выход первой схемы "И" дополнительно подключен к обнуляющему входу счетчика.

Сущность предложения заключается во введении дискретно нарастающего временного сдвига последовательно принимаемых импульсов обнаруживаемой последовательности с многократной перезаписью сдвинутых импульсов в схеме (линии) задержки после проверки на синхронность с очередным импульсом. Это позволяет обеспечить принадлежность всех "n" импульсов, поступающих в установленный интервал времени на счетчик, к одной периодической последовательности при использовании всего одной линии задержки на период повторения.

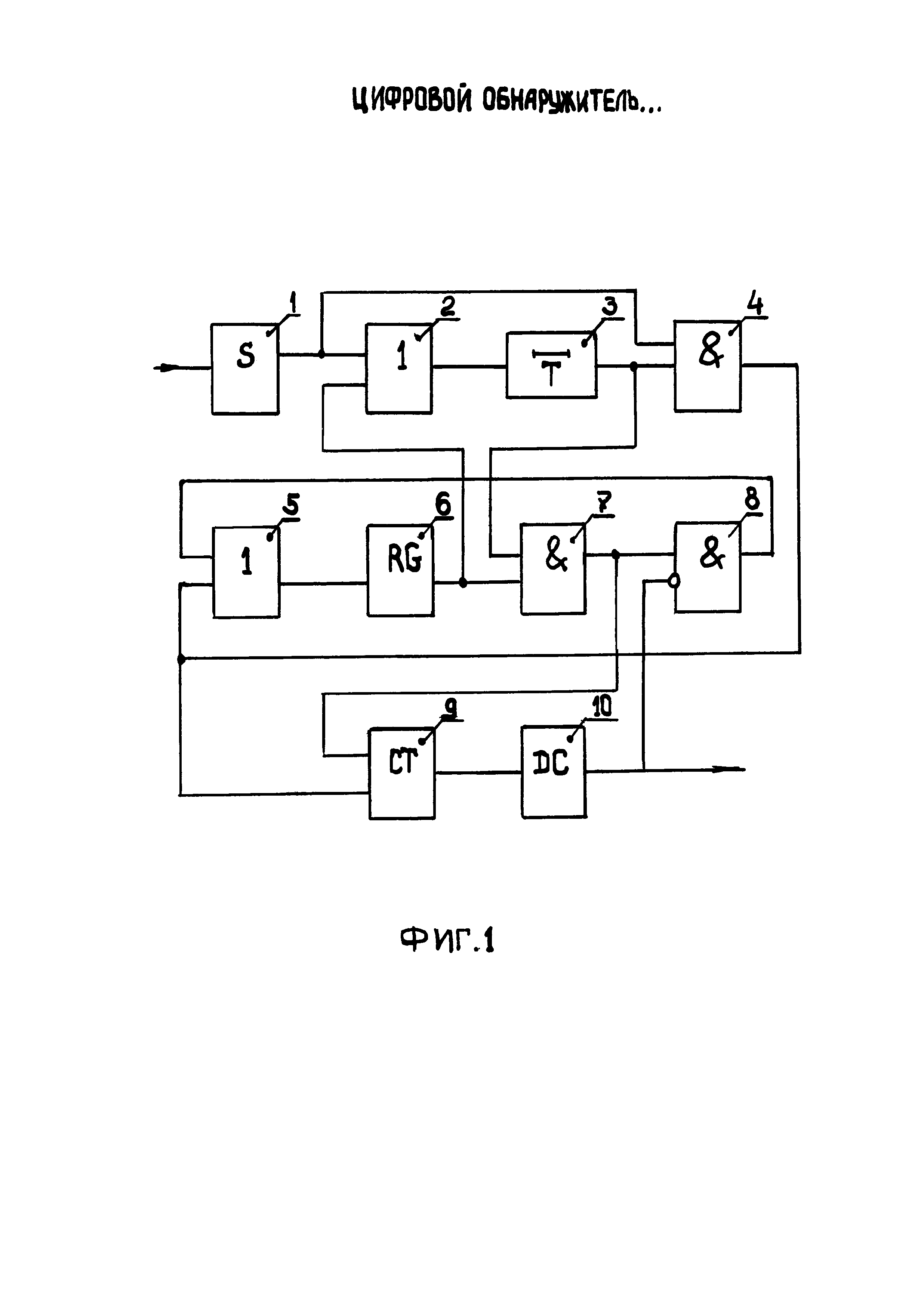

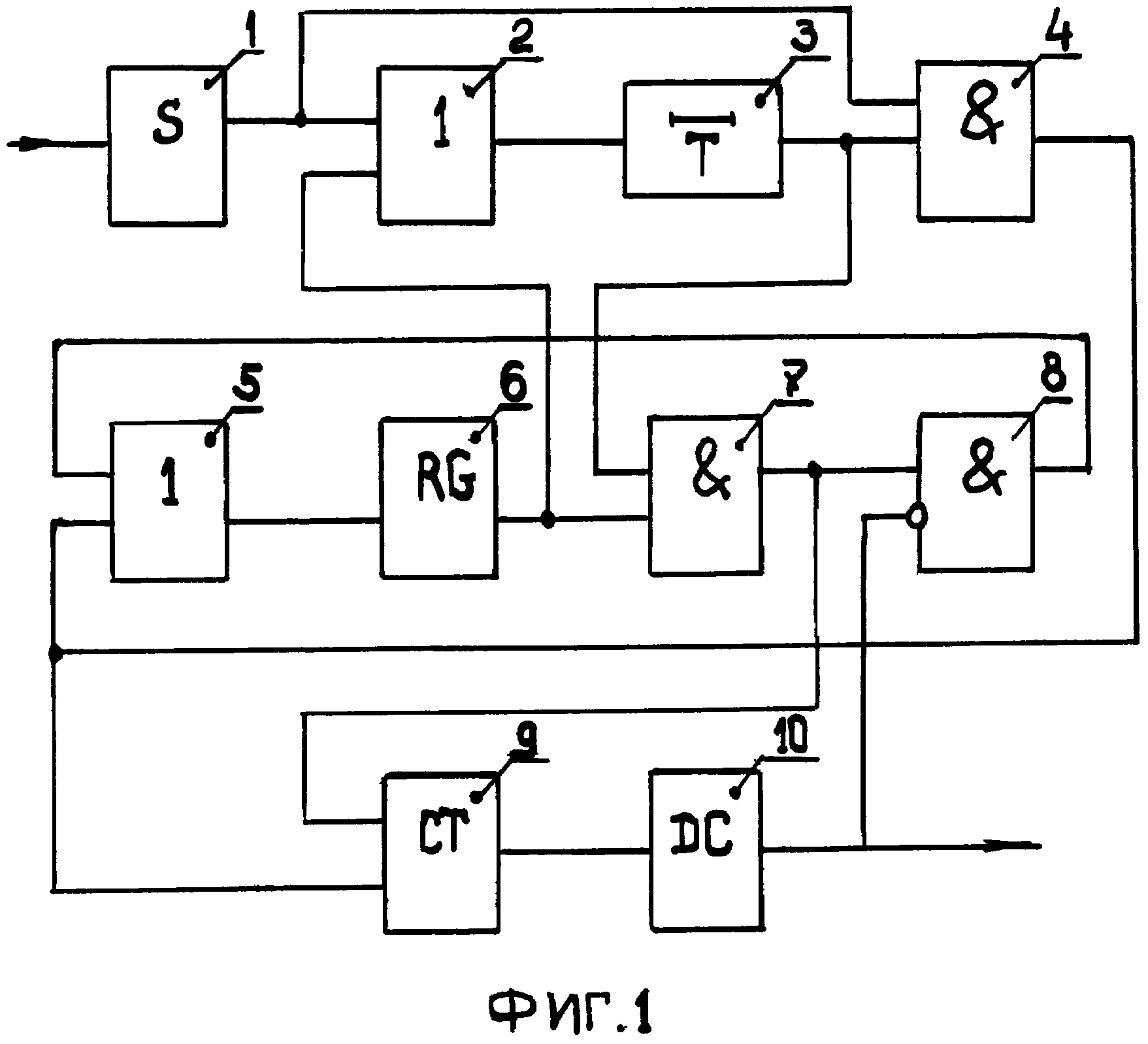

Структура и порядок функционирования предлагаемого обнаружителя поясняются последующим подробным описанием и прилагаемым чертежом (фиг. 1), на котором представлена функциональная схема обнаружителя.

Обнаружитель может быть выполнен полностью на элементах цифровой вычислительной техники и включает в себя последовательно соединенные входной нормализатор видеосигналов по длительности и амплитуде 1 (одновибратор), двухвходовую схему "ИЛИ" 2, линию задержки на период повторения "Т" 3 (многоразрядная цифровая схема задержки с дискретом, соответствующим длительности нормализованного сигнала, магнитострикционная линия задержки и т.п.), двухвходовую схему "И", второй вход которой подключен к выходу нормализатора 1, двухвходовую схему "ИЛИ" 5, регистр сдвига 6 на время, большее длительности нормализованного сигнала, но меньшее, чем T/n, выход которого подключен к второму входу схемы "ИЛИ" 2 и к второй двухвходовой схеме "И" 7, второй вход которой соединен с выходом линии задержки 3, а выход подключен к прямому входу схемы "НЕ-И" 8 и к счетному входу счетчика 9, обнуляющий вход которого соединен с выходом первой схемы "И" 4, а выход подключен к дешифратору 10. Выход дешифратора 10, являющийся выходом обнаружителя, соединен с инверсным входом схемы "НЕ-И" 8, выход которой подключен к второму входу схемы "И" 5.

Рассмотрим работу обнаружителя при поступлении на его вход пачки из "n" импульсов, следующих через период Т.

Первый импульс пачки, поступающей на вход обнаружителя, после нормализации по длительности до установленной величины (например, 0,6÷0,8 мкс), с выхода нормализатора 1 через схему "ИЛИ" 2 подается на вход линии задержки 3 и через интервал времени, равный периоду повторения сигнала Т, поступает на схему "И" 4, на другой вход которой в этот момент с выхода нормализатора 1 поступает второй импульс пачки. Выходной импульс схемы "И" 4 обнуляет счетчик 9 и через схему "ИЛИ" 5 поступает на элемент задержки (регистр сдвига) 6, где он задерживается на интервал времени τ, больший, чем длительность нормализованного импульса, но меньший, чем величина T/n; величина τ может составлять, например, 2÷5 мкс. С выхода регистра сдвига 6 импульс поступает на вход схемы "И" 7 и через схему "ИЛИ" 2 - на линию задержки 3, куда ранее поступил второй импульс пачки. Таким образом, на втором периоде повторения в линии задержки 3 оказались запомненными два сигнала - второй импульс пачки и отстающий от него на время сдвига τ выходной импульс регистра сдвига 6. На выход схемы "И" 7 сдвинутый второй импульс не проходит, т.к. на другом ее входе в этот момент сигнал отсутствует.

Третий импульс пачки, так же, как и предыдущие, с выхода нормализатора 1 через схему "ИЛИ" 2 поступает на линию задержки 3, где запоминается. Одновременно третий импульс подается на схему "И" 4, на другой вход которой с выхода линии 3 поступает задержанный на период Т второй импульс пачки. С выхода схемы 4 импульс через схему "ИЛИ" 5 подается на регистр сдвига 6, задерживается в нем на время τ и поступает на вход линии задержки 3 (через схему "ИЛИ" 2) и на схему "И" 7, на второй вход которой в этот момент с выхода линии 3 приходит сдвинутый на время τ второй импульс. С выхода схемы 7 импульс через открытую схему "НЕ-И" 8 и схему "ИЛИ" 5 возвращается на вход регистра сдвига 6, с выхода которого этот импульс, дополнительно сдвинутый на время τ, через схему 2 поступает на вход линии задержки 3, куда перед этим уже последовательно поступили два импульса (третий импульс пачки и сдвинутый относительно него на время τ сигнал с выхода регистра 6). Таким образом, на третьем периоде в линии задержки 3 оказываются запомненными уже три сигнала, отстоящие друг от друга на время τ.

Выходной сигнал схемы "И" 7 поступает также на счетный вход счетчика 9 и регистрируется счетчиком, однако, если критерий срабатывания (порог) дешифратора 10 больше чем единица, дешифратор не срабатывает и схема "НЕ-И" 8 остается открытой.

Четвертый импульс, совпадающий во времени с третьим, задержанным на период Т, аналогично предыдущим проходит через схему "И" 4, обнуляет счетчик 9 и поступает через схему 5 на регистр сдвига 6, с выхода которого задержанный на время τ импульс поступает на вход линии задержки 3 (через схему 2) и на схему "И" 7, на другой вход которой с выхода линии 3 в этот момент приходит третий, дополнительно сдвинутый на время τ импульс. Выходной импульс схемы 7 регистрируется в счетчике 9 и через схемы "НЕ-И" 8 и "ИЛИ" 5 поступает на вход регистра 6, сдвигается на время τ и вновь поступает на линию задержки 3 и на схему "И" 7, на второй вход которой при этом с выхода линии 3 поступает третий импульс, дважды задержанный на время τ. Выходной сигнал схемы 7 регистрируется счетчиком 9, в котором теперь оказывается записанным число "2", и возвращается через схемы 8 и 5 на вход регистра 6, сдвигается еще на время τ и опять поступает на линию задержки 3 и на схему "И" 7, но не проходит через нее, т.к. последовательность сигналов, запомненных на линии 3 в предыдущем периоде, окончилась и на второй вход схемы 7 уже не поступает сигнал, совпадающий во времени с выходным импульсом регистра 6.

Обработка последующих импульсов пачки в схеме обнаружителя происходит аналогичным образом, при этом после приема пятого импульса в счетчике 9 будет записано число "3", после шестого - "4" и так далее до того импульса, при котором будет выполнен установленный в дешифраторе 10 критерий обнаружения, после чего дешифратор выдает сигнал обнаружения пачки. При этом на инверсный вход схемы "НЕ-И" 8 подается постоянный сигнал, закрывающий эту схему на оставшуюся часть периода повторения. При приеме каждого последующего импульса ("n+1"-го, "n+2"-го и т.д.) счетчик 9 обнуляется и затем вновь накапливает число, соответствующее критерию обнаружения, в результате чего дешифратор 10 выдает сигнал обнаружения по каждому из этих последующих импульсов.

При окончании пачки очередной импульс через период Т не поступает на обнаружитель; при этом предыдущий запомненный на линии 3 сигнал не проходит через схему "И" 4 и не поступает на вход второй схемы "И" 7, в результате чего накопленные на предыдущих периодах в линии задержки 3 импульсы не проходят на счетчик 9 и не поступают вновь на вход линии 3. При воздействии на вход обнаружителя импульсного потока, содержащего серии импульсов с периодом Т, но с числом импульсов в каждой серии, меньшим, чем установленный критерий обнаружения (например, случайных серий, образованных сигналами ХИП) накопление импульсов на счетчике 9 прервется до срабатывания дешифратора 10; после непоступления очередного импульса через период Т линия задержки 3 очистится от накопленных в ней ранее импульсов и схема обнаружителя возвратится в исходное состояние.

Из приведенного описания видно, что взаимодействие известных и дополнительно введенных в схему обнаружителя элементов обеспечивает накопление на счетчике только импульсов, принадлежащих одной непрерывной импульсной последовательности с заданным периодом Т за счет череспериодного сравнения по всем импульсам пачки. Это существенно снижает вероятность накопления импульсов помехи путем и тем самым повышает помехоустойчивость обнаружителя; как видно из описания, повышение кратности череспериодного сравнения в предлагаемой схеме достигается без увеличения числа линий задержки на период повторения.

Для предлагаемой схемы обнаружителя произведена расчетная оценка степени повышения помехоустойчивости по критерию вероятности ложной тревоги при различных интенсивностях ХИП; в частности, для принятых типовых исходных данных (число импульсов в пачке n=5 и средняя частота ХИП до 20-30 кГц) средняя частота ложных тревог снижается на два-три порядка.

Разработаны и проверены схемы основных узлов на элементах дискретной техники (цифровая линия задержки на единицы мсек, выполненная на элементах серии "Радикал", и регистр сдвига на несколько мкс, выполненный на элементах "Логика-2"); остальные функциональные узлы выполняются на типовых логических элементах, в основном, серии "Логика-2".

Положительный эффект предложения заключается в повышении помехоустойчивости обнаружителя при несущественном усложнении его схемы. Так, для конкретного варианта выполнения цифрового обнаружителя с линией задержки на нескольких десятках интегральных микросхем 1ИР864 общее число микросхем, необходимых для реализации схемы прототипа составляет около 90-100 (с учетом генератора тактовых импульсов); при реализации предложенной схемы к этому добавляется еще до 10-12 микросхем. Таким образом, объем схемы обнаружителя увеличивается не более чем на 15%, в то время как частота ложных тревог при работе в условиях ХИП снижается не менее чем на два-три порядка (для указанного выше критерия обнаружения n=5). Для того чтобы получить тот же эффект путем повышения кратности череспериодного сравнения в известной схеме обнаружителя, необходимо увеличить число линий задержки на период повторения до 4-х, т.е. увеличить объем схемы более чем вдвое. Это привело бы к значительному ухудшению технико-экономических показателей схемы обнаружителя (массогабаритных характеристик, стоимости, надежности).

В предлагаемой схеме сигнал обнаружения выдается не синхронно с поступающим на вход "n"-ным и последующими импульсами, а с постоянным сдвигом относительно них на (n-1)τ. В ряде случаев этот сдвиг несущественен для работы последующих устройств; при необходимости, он может быть скомпенсирован обычным техническим путем - включением схемы задержки на время Т-(n-1)τ на выходе обнаружителя.

Цифровой обнаружитель пачек периодических импульсных сигналов, содержащий счетчик с дешифратором и элемент И, к входам которого подключены выходы нормализатора видеосигналов и линии задержки, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены первый элемент ИЛИ и соединенные последовательно второй элемент ИЛИ, регистр сдвига, второй элемент И и элемент НЕ-И, при этом первый вход первого элемента ИЛИ соединен с выходом нормализатора видеосигналов, второй вход соединен с выходом регистра сдвига, а выход соединен со входом линии задержки, к выходу которой подключен второй вход второго элемента И, выход которого соединен со входом счетчика с дешифратором, вход сброса которого подключен к выходу первого элемента И и соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом элемента НЕ-И, инверсный вход которого подключен к выходу счетчика с дешифратором.